1 1

Изобретение относится к вычислиельной технике и предназначено для спользования в системах цифровой бработки информации.

Цель изобретения - уменьшение апаратных затрат за счет обеспечения озможности вычисления на одном суматоре и умножителе двух сумм часичных произведений.

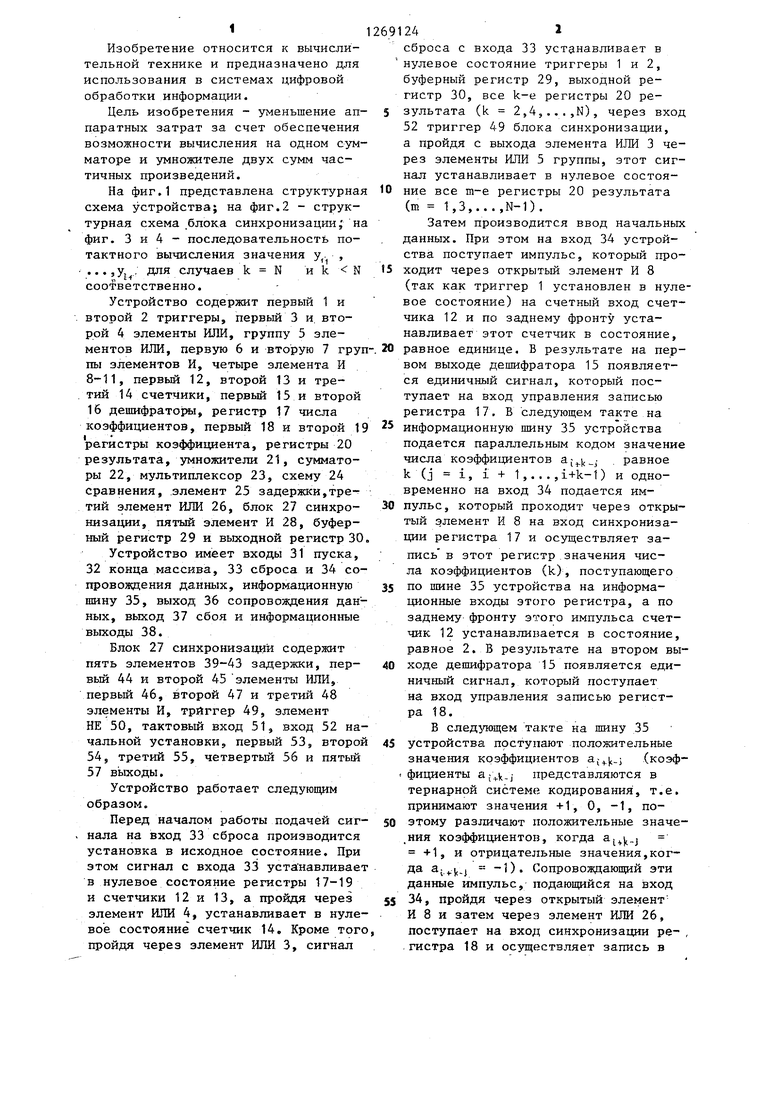

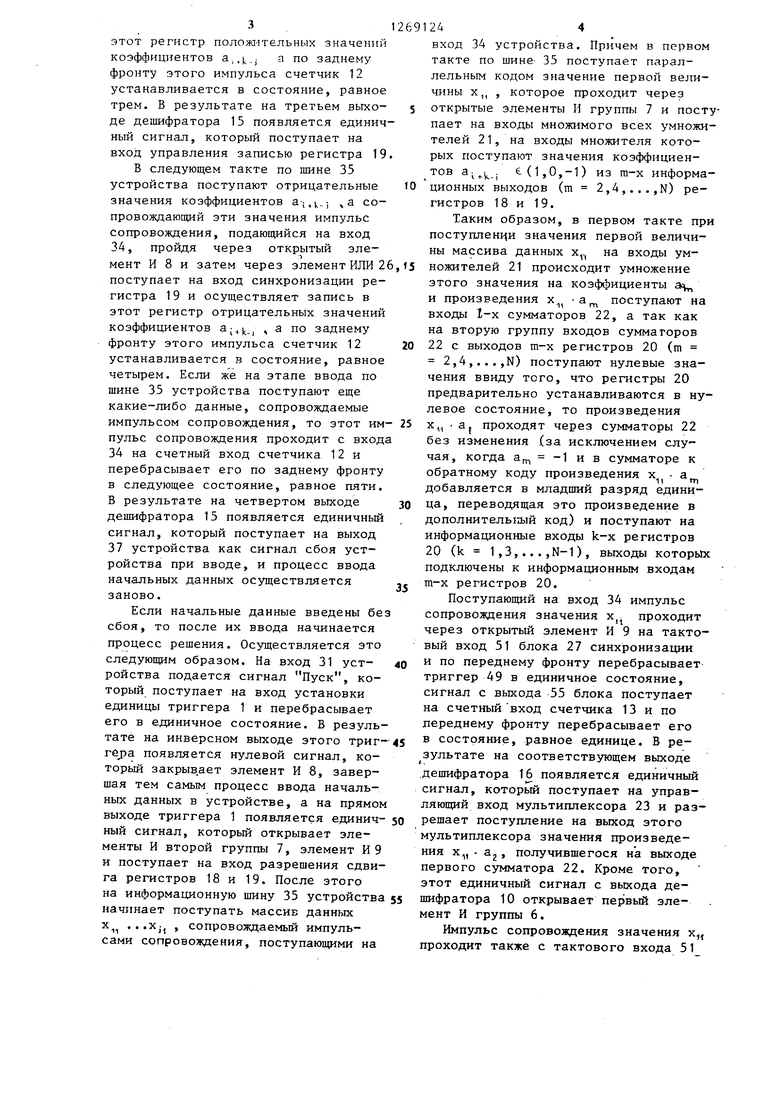

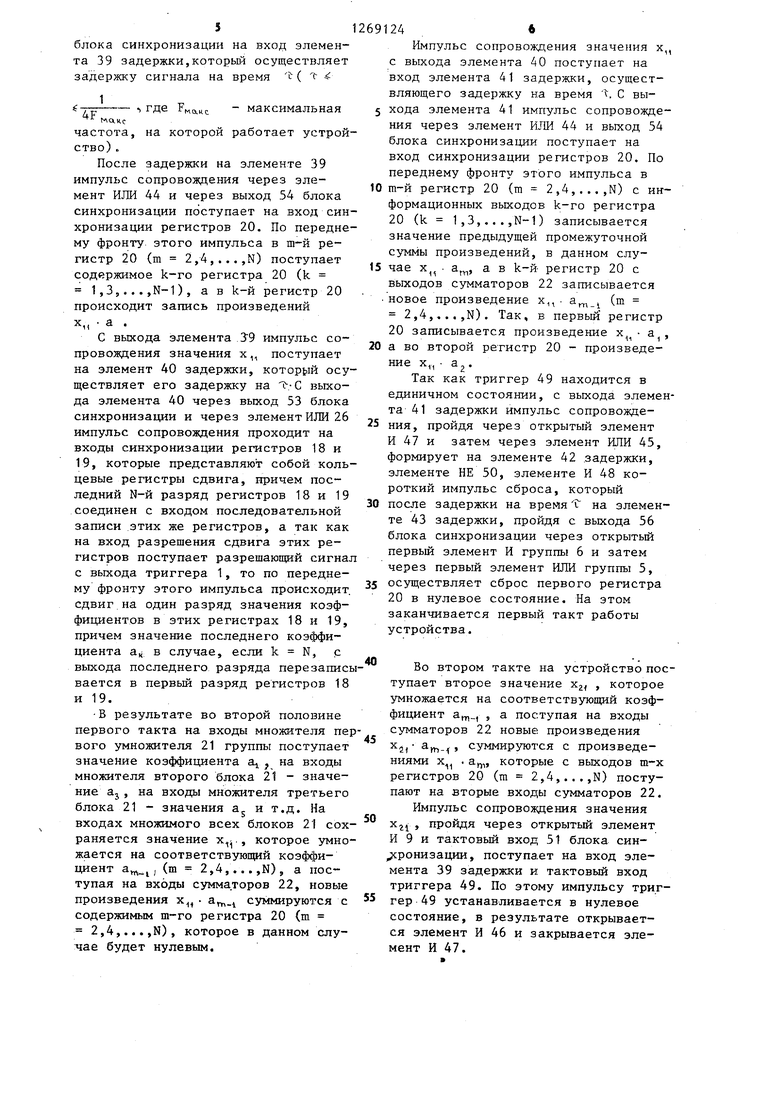

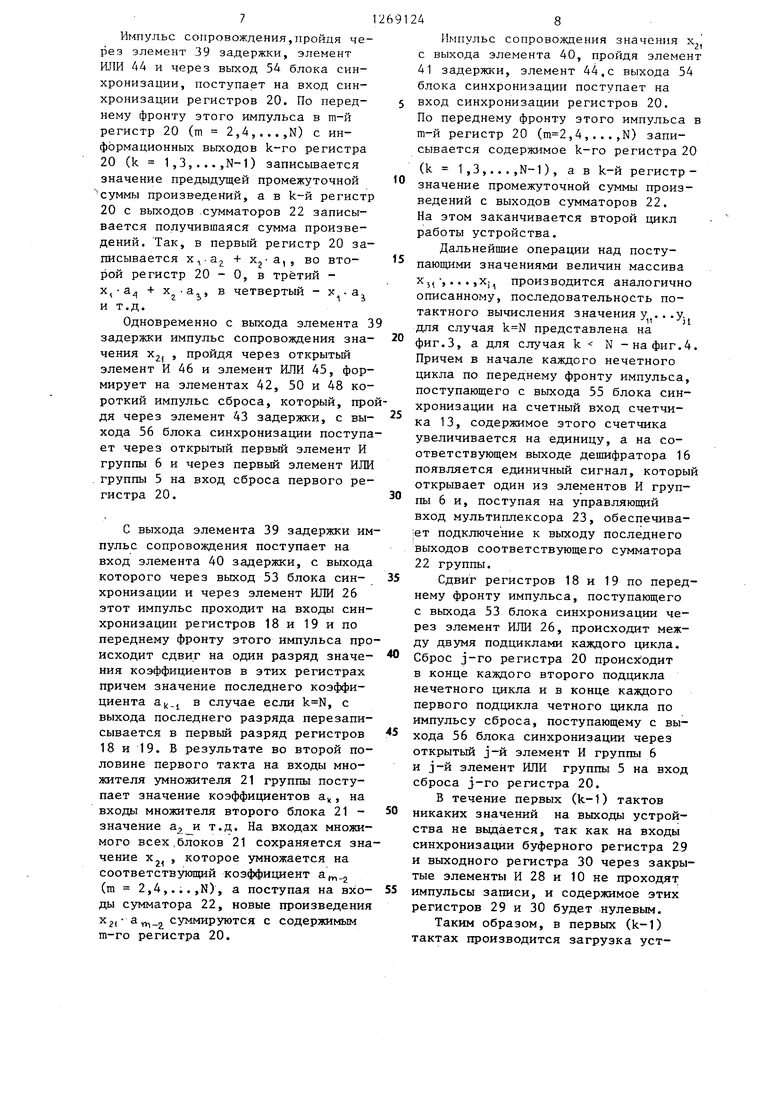

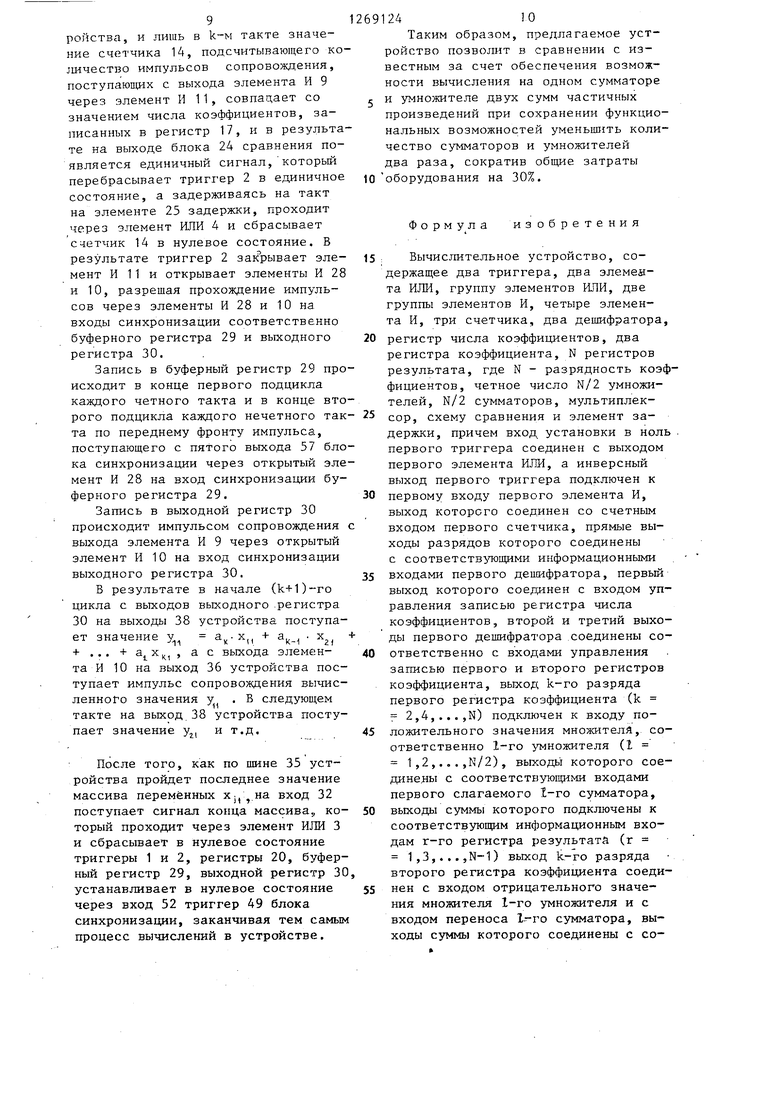

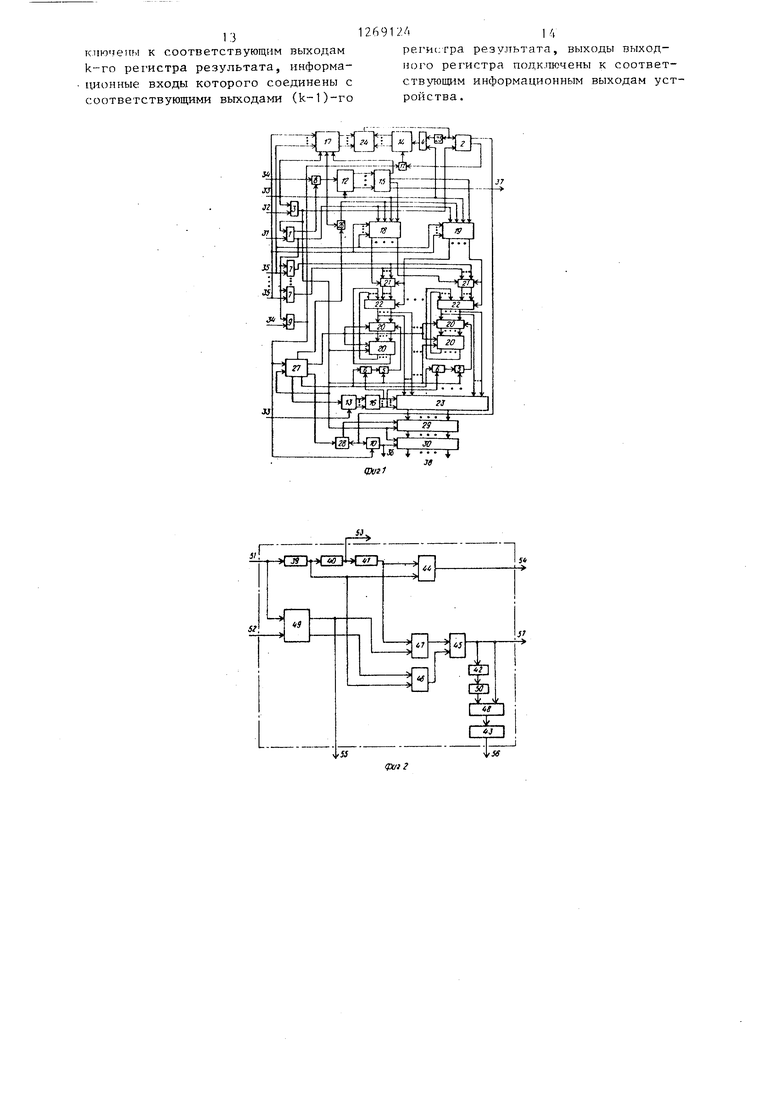

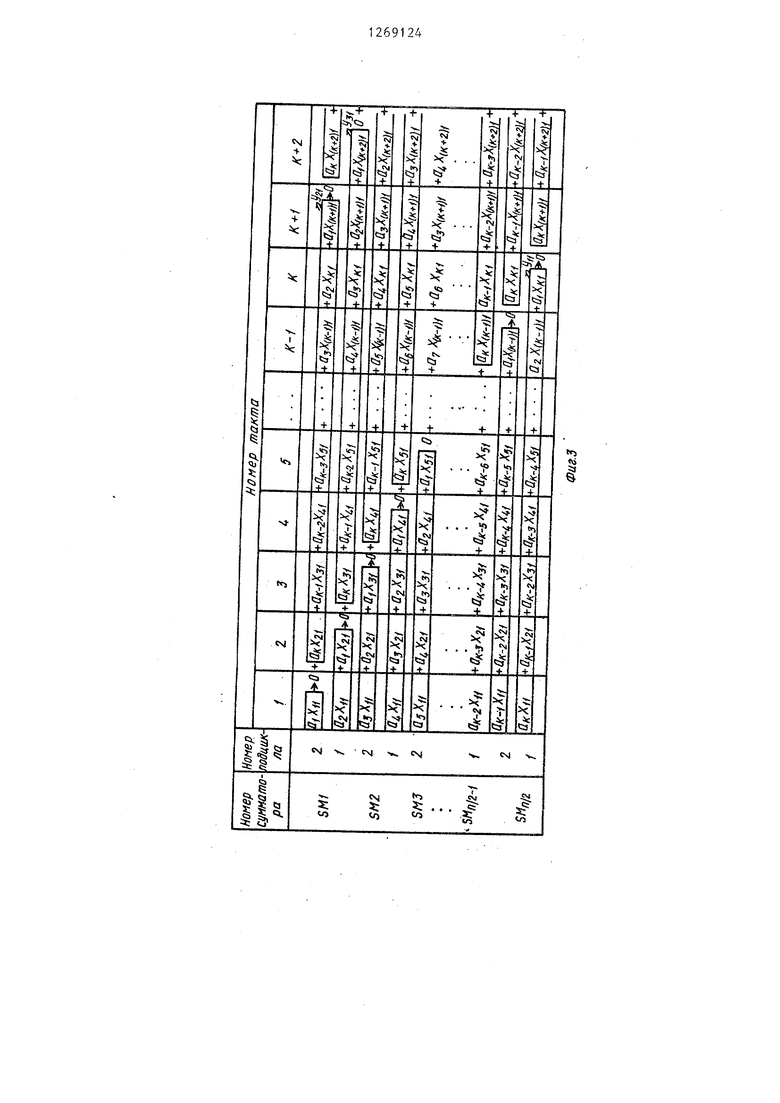

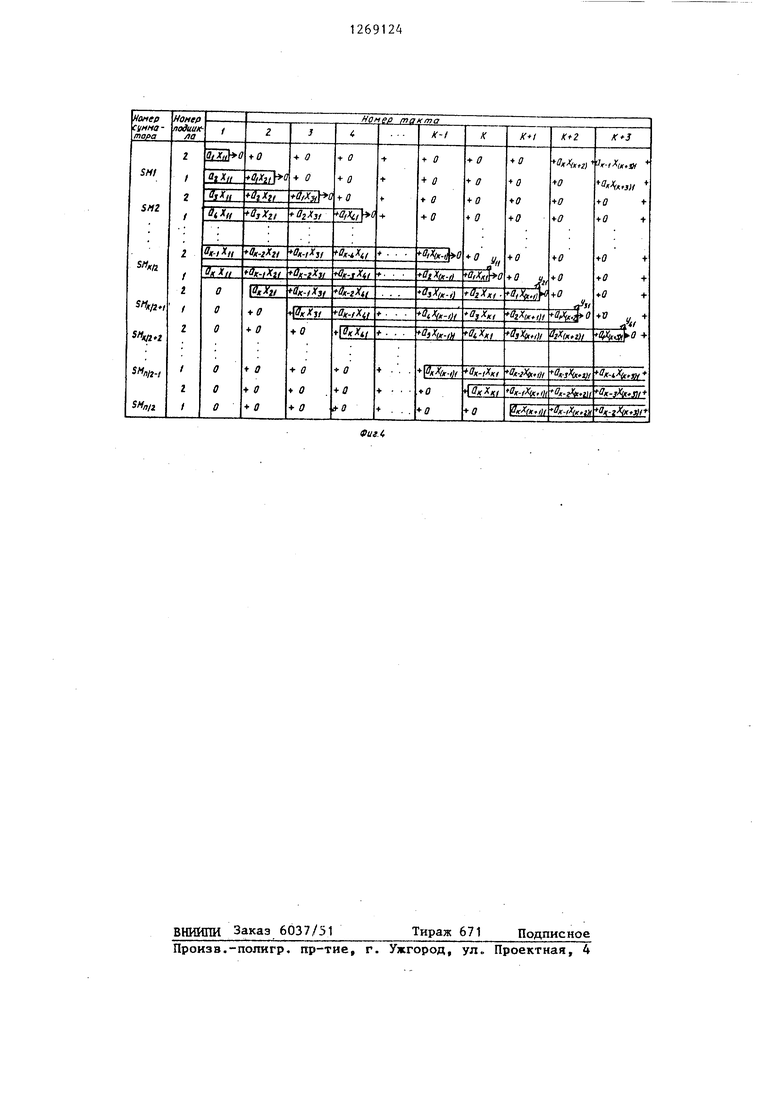

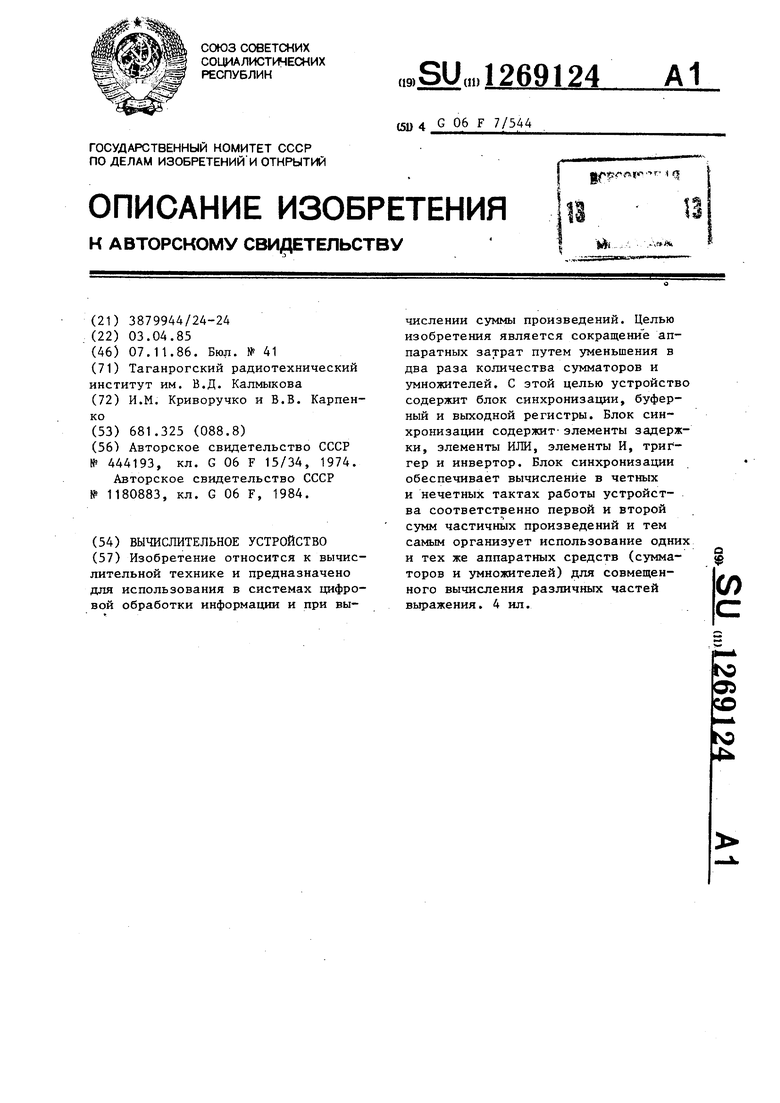

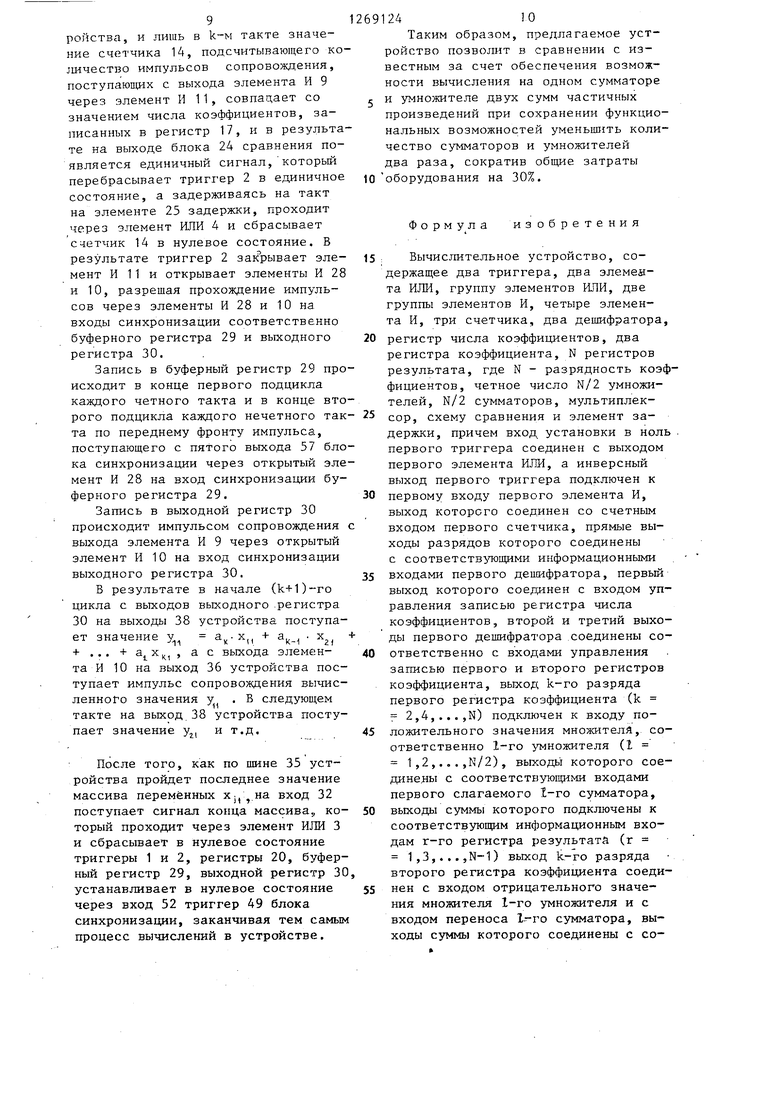

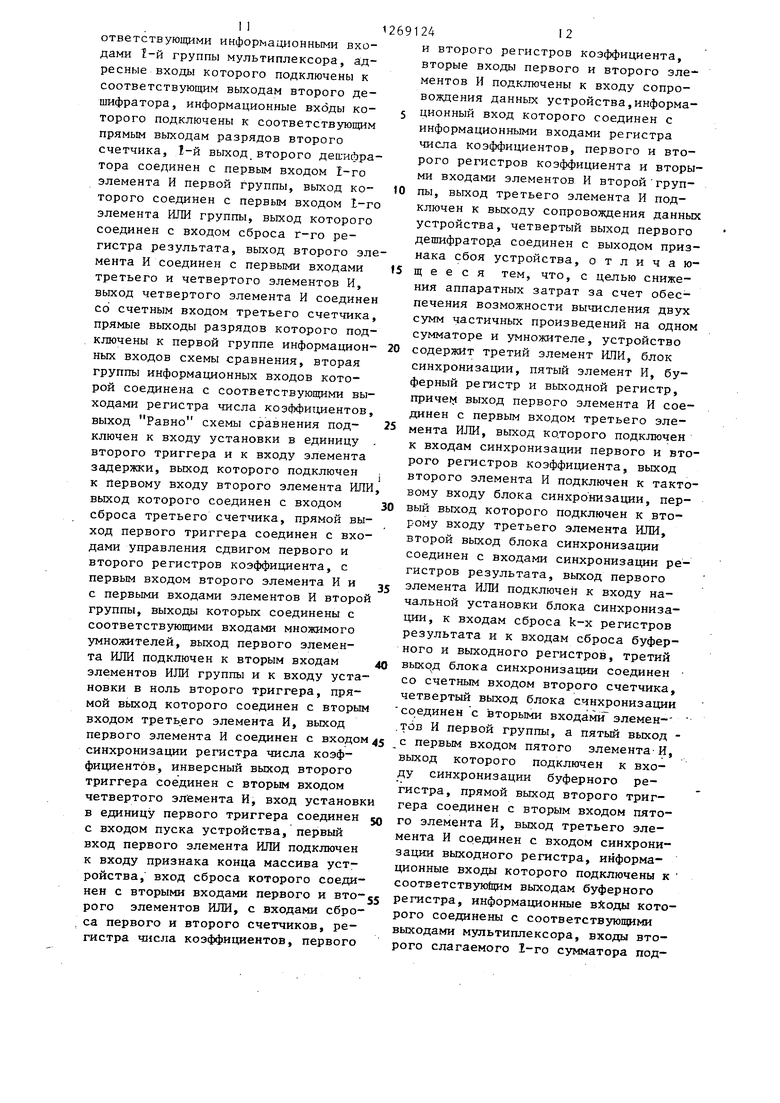

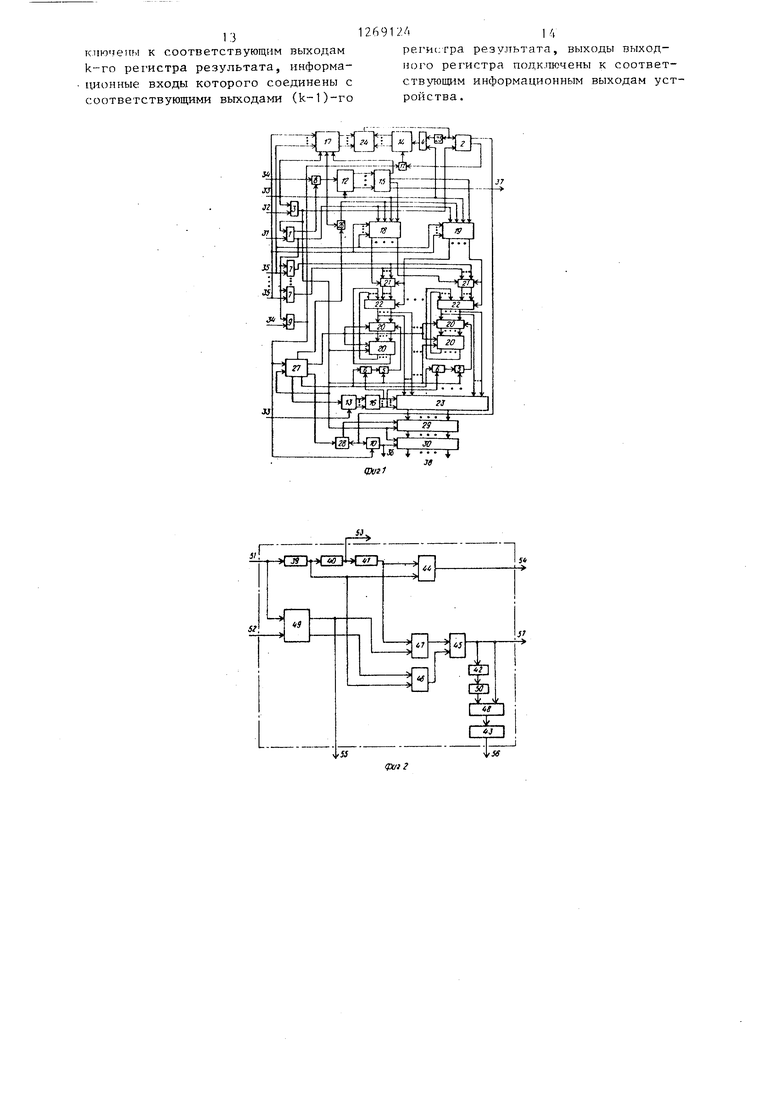

На фиг.1 представлена структурная схема устройства; на фиг.2 - струкурная схема блока синхронизации; на иг. 3 и 4 - последовательность потактного вычисления значения у. , ... ,у, ., для случаев k N и k N соответственно.

Устройство содержит первый 1 и второй 2 триггеры, первый 3 и второй 4 элементы ИЛИ, группу 5 элементов ИЛИ, первую 6 и вторую 7 группы элементов И, четыре элемента И 8-11, первый 12, второй 13 и третий 14 счетчики, первый 15 и второй 16 дешифратори), регистр 17 числа коэффициентов, первый 18 и второй 19 регистры коэффициента, регистры 20 результата, умножители 21, сумматоры 22, мультиплексор 23, схему 24 сравнения, .элемент 25 задержки,третий элемент ИЛИ 26, блок 27 синхронизации, пятый элемент И 28, буферный регистр 29 и выходной регистр 30.

Устройство имеет входы 31 пуска, 32 конца массива, 33 сброса и 34 сопровождения данных, информационную пину 35, выход 36 сопровождения данных, выход 37 сбоя и информационные выходы 38.

Блок 27 синхронизации содержит пять элементов 39-43 задержки, первый 44 и второй 45 элементы ИЛИ, первый 46, второй 47 и третий 48 элементы И, триггер 49, элемент НЕ 50, тактовый вход 51, вход 52 начальной установки, первый 53, второй 54, третий 55, четвертьй 56 и пятый 57 вьЕходы.

Устройство работает следующим образом.

Перед началом работы подачей сигнала на вход 33 сброса производится установка в исходное состояние. При этом сигнал с входа 33 устанавливает в нулевое состояние регистры 17-19 и счетчики 12 и 13, а пройдя через элемент ИЛИ 4, устанавливает в нулевое состояние счетчик 14. Кроме того пройдя через элемент ИЛИ 3, сигнал

691241

сброса с входа 33 устанавливает в нулевое состояние триггеры 1 и 2, буферный регистр 29, выходной регистр 30, все k-e регистры 20 ре5 зультата (k 2,4,...,N), через вход 52 триггер 49 блока синхронизации, а пройдя с выхода элемента ИЛИ 3 через элементы ИЛИ 5 группы, этот сигнал устаня-вливает в нулевое состоя10 ние все ш-е регистры 20 результата (т 1,3,...,N-1).

Затем производится ввод начальных данных. При этом на вход 34 устройства поступает импульс, который проtS ходит через открытый элемент И 8

(так как триггер 1 установлен в нулевое состояние) на счетный вход счетчика 12 и по заднему фронту устанавливает этот счетчик в состояние, 20 равное единице. В результате на первом выходе дешифратора 15 появляется единичный сигнал, который поступает на вход управления записью регистра 17. Б следующем такте на 25 информационную шину 35 устройства подается параллельным кодом значение числа коэффициентов равное k (J i, i + 1,...,i+k-O и одновременно на вход 34 подается им30 пульс, который проходит через открытый элемент И 8 на вход синхронизации регистра 17 и осуществляет запись в этот регистр значения числа коэффициентов (k), поступающего 35 по шине 35 устройства на информационные входы этого регистра, а по заднему фронту этого импульса счетчик 12 устанавливается в состояние, равное 2. В результате на втором вы40 ходе дешифратора 15 появляется единичный сигнал, который поступает на вход управления записью регистра 18.

В след тащем такте на шину 35 45 устройства поступают положительные

значения коэффициентов ,; (коэф фициенты a;.) представляются в тернарной системе кодирования, т.е. принимают значения +1, О, -1, по50 этому раз1шчают положительные значе ния коэффициентов, когда .j +1, и отрицательные значения,когда а;..(,.| -1). Сопровождающий эти данные импульс, подающийся на вход 55 34, пройдя через открытый элемент И 8 и затем через элемент ИЛИ 26, поступает на вход синхронизации ре- , -гистра 18 и осуществляет запись в

3

этот регистр положительных значений коэффициентов а,.|,.. а по заднему фронту этого импульса счетчик 12 устанавливается в состояние, равное трем. В результате на третьем вьгходе дешифратора 15 появляется единичный сигнал, который поступает на вход управления записью регистра 19

В следующем такте по шине 35 устройства поступают отрицательные значения коэффициентов а--,,,.; ,а сопровождающий эти значения импульс сопровождения, подающийся на вход 34, пройдя через открытый элемент И 8 и затем через элемент ИЛИ 26 поступает на вход синхронизации регистра 19 и осуществляет запись в этот регистр отрицательных значений коэффициентов , а по заднему франту этого импульса счетчик 12 устанавливается в состояние, равное четырем. Если же на этапе ввода по шине 35 устройства поступают еще какие-либо данные, сопровождаемые импульсом сопровождения, то этот импульс сопровождения проходит с входа 34 на счетный вход счетчика 12 и перебрасывает его по заднему фронту в следующее состояние, равное пяти. В результате на четвертом выходе дешифратора 15 появляется единичный сигнал, который поступает на выход 37 устройства как сигнал сбоя устройства при вводе, и процесс ввода начальных данных осуществляется заново.

Если начальные данные введены бе сбоя, то после их ввода начинается процесс решения. Осуществляется это следующим образом. На вход 31 устройства подается сигнал Пуск, который поступает на вход установки единицы триггера 1 и перебрасывает его в единичное состояние. В результате на инверсном выходе этого триг- гера появляется нулевой сигнал, который закрыв.ает элемент И 8, завершая тем самым процесс ввода начальных данных в устройстве, а на прямом выходе триггера 1 появляется единичный сигнал, который открывает элементы И второй группы 7, элемент И 9 и поступает на вход разрешения сдвига регистров 18 и 19. После этого на информационную шину 35 устройства начинает поступать массив данных х ...Xjj , сопровождаемый импульсами сопровождения, поступающими на

1244

вход 34 устройства. Причем в первом такте по шине 35 поступает параллельным кодом значение первой величины X,, , которое проходит через открытые элементы И группы 7 и постпает на входы множимого всех умножителей 21, на входы множителя которых поступают значения коэффициентов a.j. (1,0,-1) из га-х информационных выходов (т 2,4,...,N) регистров 18 и 19.

Таким образом, в первом такте пр поступлении значения первой величины массива данных х,., на входы умножителей 21 происходит умножение этого значения на коэфс)ициенты а и произведения х -а поступают на входы 1-х сумматоров 22, а так как на вторую группу входов сумматоров 22 с выходов т-х регистров 20 (т 2,4,...,N) поступают нулевые значения ввиду того, что регистры 20 предварительно устанавливаются в нулевое состояние, то произведения X,, aj проходят через сумматоры 22 без изменения (за исключением случая, когда а -1 и в сумматоре к обратному коду произведения х а добавляется в младший разряд единица, переводящая это произведение в дополнительный код) и поступают на информационные входы k-x регистров 20 (k 1,3,...,N-1), выходы которых подключены к информационным входам т-х регистров 20.

Поступающий на вход 34 импульс сопровождения значения х проходит через открытый элемент И 9 на тактовый вход 51 блока 27 синхронизации и по переднему фронту перебрасывает триггер 49 в единичное состояние, сигнал с выхода 55 блока поступает на счетныйвход счетчика 13 и по переднему фронту перебрасывает его в состояние, равное единице. В результате на соответствующем выходе .дешифратора 16 появляется единичный сигнал, который поступает на управляющий вход мультиплексора 23 и разрешает поступление на выход этого мультиплексора значения произведения X,, . а, получившегося на выходе первого сумматора 22. Кроме того, этот единичный сигнал с выхода дешифратора 10 открывает первый элемент И группы 6.

Импульс сопровождения значения х проходит также с тактового входа 51 5 блока синхронизации на вход элемента 39 задержки,который осуществляет задержку сигнала на время , где FMCLKC максимальная частота, на которой работает устройство) . После задержки на элементе 39 импульс сопровождения через элемент ИЛИ 44 и через выход 54 блока синхронизации поступает на вход син хронизации регистров 20. По передне му фронту этого импульса в ш-й регистр 20 (т 2,4,...,N) поступает содержимое k-ro регистра 20 (k 1,3,...,N-1), а в k-й регистр 20 происходит запись произведений х„ а . С выхода элемента импульс сопровождения значения х „ поступает на элемент 40 задержки, который осу ществляет его задержку на Т-С выхода элемента 40 через выход 53 блока синхронизации и через элемент ИЛИ 26 импульс сопровождения проходит на входы синхронизации регистров 18 и 19, которые представляют собой коль цевые регистры сдвига, причем последний N-й разряд регистров 18 и 19 соединен с входом последовательной записи этих же регистров, а так как на вход разрешения сдвига этих регистров поступает разрешающий сигна с выхода триггера 1, то по переднему фронту этого импульса происходит сдвиг на один разряд значения коэффициентов в этих регистрах 18 и 19, причем значение последнего коэффициента а в случае, если k N, с выхода последнего разряда перезапис вается в первый разряд регистров 18 и 19. В результате во второй половине первого такта на входы множителя пе вого умножителя 21 группы поступает значение коэффициента а j на входы множителя второго блока 21 - значение aj, на входы множителя третьего блока 21 - значения а и т.д. На входах множимого всех блоков 21 сох раняется значение х., которое умно жается на соответствующий козфс1)и- циент а , (т 2,4,...,N), а поступая на входы сумматоров 22, новые произведения х, а. суммируются с содержимым т-го регистра 20 (т 2,4,...,N), которое в данном случае будет нулевым. 244 Импульс сопровождения значения х,, с выхода элемента 40 поступает на вход элемента 41 задержки, осуществляющего задержку на время . С выхода элемента 41 импульс сопровождения через элемент ИЛИ 44 и выход 54 блока синхронизации поступает на вход синхронизации регистров 20. По переднему фронту этого импульса в т-й регистр 20 (га 2,4,...,N) с информационных выходов k-ro регистра 20 (k 1,3,...,N-1) записывается значение предыдущей промежуточной суммы произведений, в данном случае х . а, а в k-й регистр 20 с выходов сумматоров 22 записывается новое произведение х,, а (т 2,4,,..,N). Так, в первый регистр 20 записывается произведение х а , а во второй регистр 20 - произведение X,, а. Так как триггер 49 находится в единичном состоянии, с выхода элемента 41 задержки импульс сопровождеНИН, пройдя через открытый элемент И 47 и затем через элемент ИЛИ 45, формирует на элементе 42 задержки, элементе НЕ 50, элементе И 48 короткий импульс сброса, который после задержки на время С на элементе 43 задержки, пройдя с выхода 56 блока синхронизации через открытый первый элемент И группы 6 и затем через первый элемент ИЛИ группы 5, осуществляет сброс первого регистра 20 в нулевое состояние. На этом заканчивается первый такт работы устройства. Во втором такте на устройство поступает второе значение Х2 , которое умножается на соответствующий коэффициент afn, , а поступая на входы сумматоров 22 новые произведения X J, а , суммируются с произведениями х . а,, которые с выходов т-х регистров 20 (т 2,4,...,N) поступают на вторые входы сумматоров 22. Импульс сопровождения значения пройдя через открытый элемент И 9 и тактовый вход 51 блока син сронизации, поступает на вход элемента 39 задержки и тактовьш вход триггера 49. По этому импульсу триггер 49 устанавливается в нулевое состояние, в результате открывается элемент И 46 и закрывается элемент И 47. 7 Импульс сопровождения,пройдя через элемент 39 задержки, элемент ИЛИ 44 и через выход 54 блока синхронизации, поступает на вход синхронизации регистров 20. По переднему фронту этого импульса в т-й регистр 20 (т 2,4,...,N) с информационных выходов k-ro регистра 20 (k 1,3,...,N-1) записьшается значение предыдущей промежуточной суммы произведений, а в k-й регистр 20 с выходов .сумматоров 22 записывается получившаяся сумма произведений. Так, в первый регистр 20 записывается Хд.а + Xj-a,, во второй регистр 20-0, в третий X,а + X -а , в четвертый - х а и т.д. Одновременно с выхода элемента 3 задержки импульс сопровождения значения х , пройдя через открытый элемент И 46 и элемент ИЛИ 45, формирует на элементах 42, 50 и 48 короткий импульс сброса, который, про дя через элемент 43 задержки, с выхода 56 блока синхронизации поступа ет через открытый первый элемент И группы 6 и через первый элемент ИЛИ группы 5 на вход сброса первого регистра 20. С выхода элемента 39 задержки им пульс сопровождения поступает на вход элемента 40 задержки, с выхода которого через выход 53 блока синхронизации и через элемент ИЛИ 26 этот импульс проходит на входы синхронизации регистров 18 и 19 и по переднему фронту этого импульса про исходит сдвиг на один разряд значения коэффициентов в этих регистрах причем значение последнего коэффициента ai.j в случае если , с выхода последнего разряда перезаписывается в первый разряд регистров 18 и 19. В результате во второй по ловине первого такта на входы множителя умножителя 21 группы поступает значение коэффициентов а, на входы множителя второго блока 21 значение а,и т.д. На входах множи мого всех,блоков 21 сохраняется зн чение х- , которое умножается на соответствующий коэффициент (т 2,4,...,N), а поступая на вхо ды сумматора 22, новые произведени X2, а суммируются с содержимым т-го регистра 20. 48 Импульс сопровождения значения х, с выхода элемента 40, прогЧдя элемент 41 задержки, элемент 44,с выхода 54 блока синхронизации поступает на вход синхронизации регистров 20. По переднему фронту этого импульса в т-й регистр 20 (,4,...,N) записывается содержимое k-ro регистра 20 (k 1,3,...,N-1), а в k-й регистрзначение промежуточной суммы произведений с выходов сумматоров 22. На этом заканчивается второй цикл работы устройства. Дальнейщие операции над поступающими значениями величин массива X,,-,...,Xj, производится аналогично описанному, последовательность потактного вычисления значения у. . .у. для случая представлена на фиг.З, а для случая k N -на фиг. 4. Причем в начале каждого нечетного цикла по переднему фронту импульса, поступающего с выхода 55 блока синхронизации на счетный вход счетчика 13, содержимое этого счетчика увеличивается на единицу, а на соответствующем выходе дешифратора 16 появляется единичный сигнал, который открывает один из элементов И группы 6 и, поступая на управляющий вход мультиплексора 23, обеспечива:ет подключение к выходу последнего выходов соответствующего сумматора 22 группы. Сдвиг регистров 18 и 19 по переднему фронту импульса, поступающего с выхода 53 блока синхронизации через элемент ИЛИ 26, происходит между двумя подциклами каждого цикла. Сброс j-ro регистра 20 происх одит в конце каждого второго подцикла нечетного цикла и в конце каждого первого подцикла четного цикла по импульсу сброса, поступающему с выхода 56 блока синхронизации через открытый j-й элемент И группы 6 и j-й элемент ИЛИ группы 5 на вход сброса j-ro регистра 20. В течение первых (k-1) тактов никаких значений на выходы устройства не выдается, так как на входы синхронизации буферного регистра 29 и выходного регистра 30 через закрытые элементы И 28 и 10 не проходят импульсы записи, и содержимое этих регистров 29 и 30 будет нулевым. Таким образом, в первых (k-1) тактах производится загрузка устройства, и лишь в k-м такте значение счетчика 14, подсчитывающего ко;шчество импульсов сопровождения, поступающих с выхода элемента И 9 через элемент Н 11, совпадает со значением числа коэффициентов, записанных в регистр 17, и в результате на выходе блока 24 сравнения появляется единичный сигнал,который перебрасывает триггер 2 в единичное состояние, а задерживаясь на такт на элементе 25 задержки, проходит через элемент ИЛИ 4 и сбрасывает счетчик 14 в нулевое состояние. В результате триггер 2 зак рывает элемент И 11 и открывает элементы И 28 и 10, разрешая прохождение импульсов через элементы И 28 и 10 на входы синхронизации соответственно буферного регистра 29 и выходного регистра 30.

Запись в буферный регистр 29 происходит в конце первого подцикла каждого четного такта и в конце второго подцикла каждого нечетного такта по переднему фронту импульса, поступающего с пятого выхода 57 блока синхронизации через открытый элемент И 28 на вход синхронизации буферного регистра 29.

Запись в выходной регистр 30 происходит импульсом сопровождения с выхода элемента И 9 через открытый элемент И 10 на вход синхронизации выходного регистра 30.

В результате в начале (k+1)-ro цикла с выходов выходного .регистра 30 на выходы 38 устройства поступа кн ет значение у

11

+ ... + , а с выхода элемента И 10 на выход 36 устройства поступает импульс сопровождения вьпшсВ следующем

ленноГо значения у

такте на вькрд 38 устройства поступает значение у,,, и т.д.

После того, как по шине 35 устройства пройдет последнее значение массива переменных Xj, ,на вход 32 поступает сигнал конца массива,, который проходит через элемент ШШ 3 и сбрасывает в нулевое состояние триггеры 1 и 2, регистры 20, буферный регистр 29, выходной регистр 30, устанавливает в нулевое состояние через вход 52 триггер 49 блока синхронизации, заканчивая тем самым процесс вычислений в устройстве.

Таким образом, предлагаемое устройство позволит в сравнении с известным за счет обеспечения возможности вычисления на одном сумматоре и умножителе двух сумм частичных произведений при сохранении функциональных возможностей уменьшить количество сумматоров и умножителей два раза, сократив общие затраты оборудования на 30%.

Формула изобретения

Вычислительное устройство, содержащее два триггера, два элемента ИЛИ, группу элементов ИЛИ, две группы элементов И, четыре элемента И, три счетчика, два дешифратора регистр числа коэффициентов, два регистра коэффициента, N регистров результата, где N - разрядность коэфициентов, четное число N/2 умножителей, N/2 сумматоров, мультиплексор, схему сравнения и элемент задержки, причем вход, установки в нол первого триггера соединен с выходом первого элемента ИЛИ, а инверсный выход первого триггера подключен к первому входу первого элемента И, выход которого соединен со счетным входом первого счетчика, прямые выходы разрядов которого соединены с соответствующими информационными входами первого дешифратора, первый выход которого соединен с входом управления записью регистра числа коэффициентов, второй и третий выходы первого дешифратора соединены соответственно с входами управления записью первого и второго регистров коэффициента, вькод k-ro разряда первого регистра коэффициента (k 2,4,.,.,N) подключен к входу положительного значения множители,, соответственно 1-го умножителя (1 1,2,...,N/2), вьгкодь которого соединед1ы с соответствующими входами первого слагаемого 1-го сумматора, выходы суммы которого подключены к соответствующим информационным входам г-го регистра результата (г 1,3,...,N-1) выход k-ro разряда второго регистра коэффициента соединен с входом отрицательного значения множителя 1-го умножителя и с входом переноса Ъ-го сумматора, выходы суммы которого соединены с со111

ответствующими информационными входами 1-й группы мультиплексора, адресные входы которого подключены к соответствующим выходам второго дешифратора, информационные входы которого подключены к соответствз щим прямым выходам разрядов второго счетчика, 1-й выход второго дешифратора соединен с первым входом 1-го элемента И первой группы, выход которого соединен с первым входом 1-го элемента ИЛИ группы, вьпсод которого соединен с входом сброса г-го регистра результата, выход второго элемента И соединен с первыми входами третьего и четвертого элементов И, выход четвертого элемента И соединен со счетным входом третьего счетчика, прямые выходы разрядов которого подключены к первой группе информационных входов схемы сравнения, вторая группы информационных входов которой соединена с соответствующими выходами регистра числа коэффициентов, выход Равно схемы сравнения подключен к входу установки в единицу . второго триггера и к входу элемента задержки, выход которого подключен к Первому входу второго элемента ИЛИ выход которого соединен с входом сброса третьего счетчика, прямой выход первого триггера соединен с входами управления сдвигом первого и второго регистров коэффициента, с первым входом второго элемента Ни с первыми входами элементов И второй группы, выходы которых соединены с соответствующими входами множимого умножителей, выход первого элемента ИЛИ подключен к вторым входам элементов ИЛИ группы и к входу установки в ноль второго триггера, прямой выход которого соединен с вторым входом третьего элемента И, выход первого элемента И соединен с входом синхронизации регистра числа коэффициентов, инверсный выход второго триггера соединен с вторым входом четвертого элемента И, вход установк в единицу первого триггера соединен с входом пуска устройства, первый вход первого элемента ИЛИ подключен к входу признака конца массива устройства, вход сброса которого соединен с вторыми входами первого и BTOрого элементов ИЛИ, с входами сброса первого и второго счетчиков, регистра числа коэффициентов, первого

12412

и второго регистров коэффициента, вторые входы первого и второго элементов И подключены к входу сопровождения данных устройства,информационный вход которого соединен с информационными входами регистра числа коэффициентов, первого и второго регистров коэффициента и вторыми входами элементов И второйгруппы, выход третьего элемента И подключен к выходу сопровождения данны устройства, четвертый выход первого дешифратора соединен с выходом признака сбоя устройства, отличающееся тем, что, с целью снижения аппаратных затрат за счет обеспечения возможности вычисления двух сумм частичных произведений на одно сумматоре и змножителе, устройство содержит третий элемент ИЛИ, блок синхронизации, пятый элемент И, буферный регистр и выходной регистр, причем выход первого элемента И соединен с первым входом третьего элемента ИЛИ, выход которого подключен к входам синхронизации первого и втрого регистров коэффициента, выход второго элемента И подключен к тактвому входу блока синхронизации, первый выход которого подключен к второму входу третьего элемента ИЛИ, второй выход блока синхронизации соединен с входами синхронизации регистров результата, выход первого элемента ИЛИ подключен к входу начальной установки блока синхронизации, к входам сброса k-x регистров результата и к входам сброса буферного и выходного регистров, третий блока синхронизации соединен со счетным входом второго счетчика, четвертый выход блока синхронизации соединен с вторыми входами элемен. тов И первой группы, а пятый выход с первым входом пятого элемента-И, выход которого подключен к входу синхронизации буферного регистра, прямой выход второго триггера соединен с вторым входом пятого элемента И, выход третьего элемента И соединен с входом синхронизации выходного регистра, информационные входы которого подключены к соответствующем выходам буферного регистра, информационные которого соединены с соответствующими выходами мультиплексора, входы второго слагаемого 1-го сумматора под- ,3 ключе1п,1 к соответствующим выходам k-ro регистра результата, ннформационные входы которого соединены с соответствующими выходами (k-l)-ro 126912А14 регисггра результата, выходы выходнего регистра подключены к соответствующим информационным выходам устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Вычислительное устройство | 1987 |

|

SU1444759A1 |

| Устройство для вычисления выражения @ | 1985 |

|

SU1357949A1 |

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| Вычислительное устройство | 1985 |

|

SU1320804A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Устройство для цифровой обработки сигналов | 1988 |

|

SU1575203A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации и при вычислении суммы произведений. Целью изобретения является сокращение аппаратных затрат путем уменьшения в два раза количества сумматоров и умножителей. С этой целью устройство содержит блок синхронизации, буферный и выходной регистры. Блок синхронизации содержит-элементы задержки, элементы ИЛИ, элементы И, триггер и инвертор. Блок синхронизации обеспечивает вычисление в четных и нечетных тактах работы устройства соответственно первой и второй сумм частичных произведений и тем самым организует использование одних I и тех же аппаратных средств (сумматоров и умножителей) для совмещен(Л ного вычисления различных частей выражения. 4 ил.

Г

i

« vi

| Устройство для вычисления выражений вида | 1973 |

|

SU444193A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1985-04-03—Подача