10

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении стохастических и специализированных вычислительных машин, Цель изобретения - расширение функциональных возможностей за счет исключения периодичности формируемой последовательности. Генератор содержит регистры, элементы И, триггеры, блок памяти, мультиплексоры, сумматоры по модулю, генератор импульсов, шинный формирователь, элементы ИЛИ, блок управления, содержащий регистр адреса, узел памяти микрокоманд, регистр микрокоманды, триггер запуска, элемент И и генератор тактовых импульсов. 1 з.п. ф-лы 7 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении стохастических и специализированных вычислительных машин и устройств.

Цель изобретения - расширение функциональных возможностей генератора путем обеспечения возможности формирования случайных чисел на основе физической неопределенности.

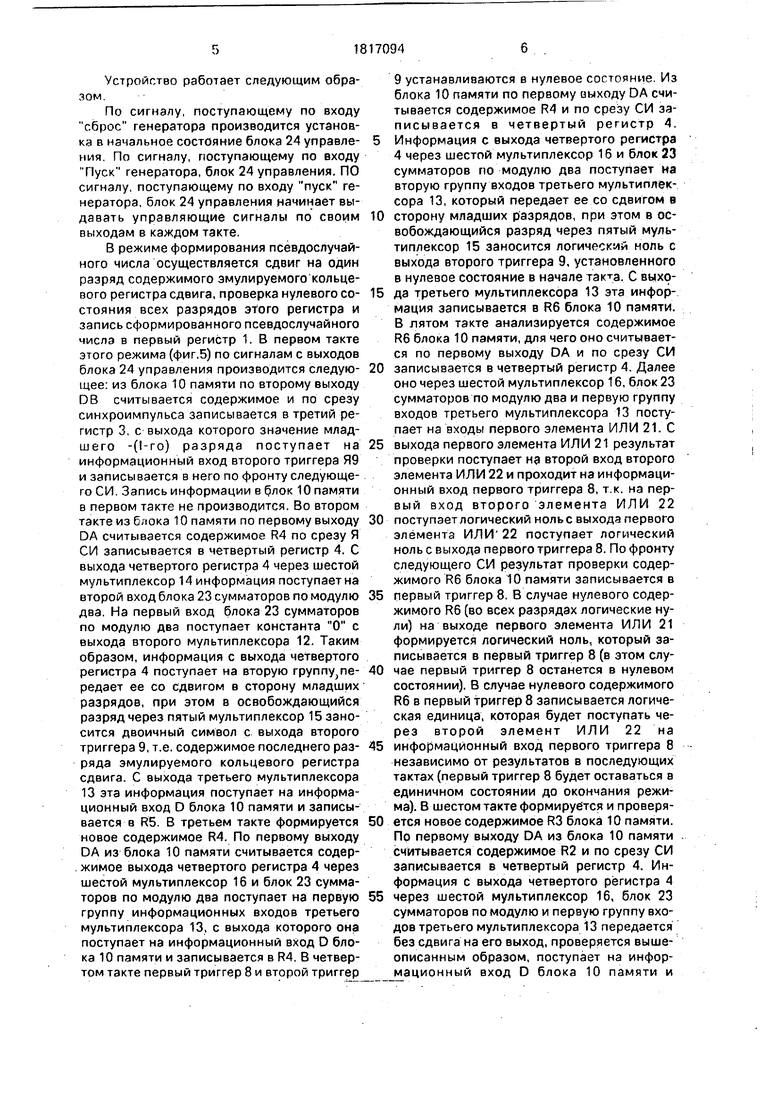

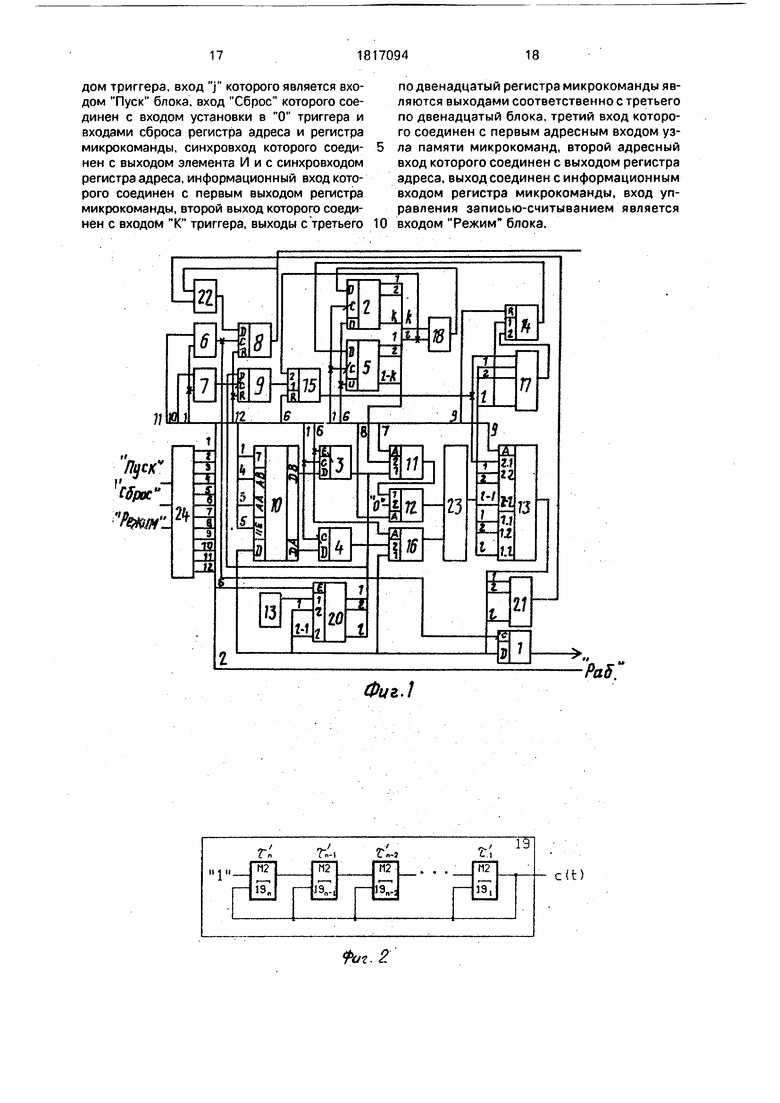

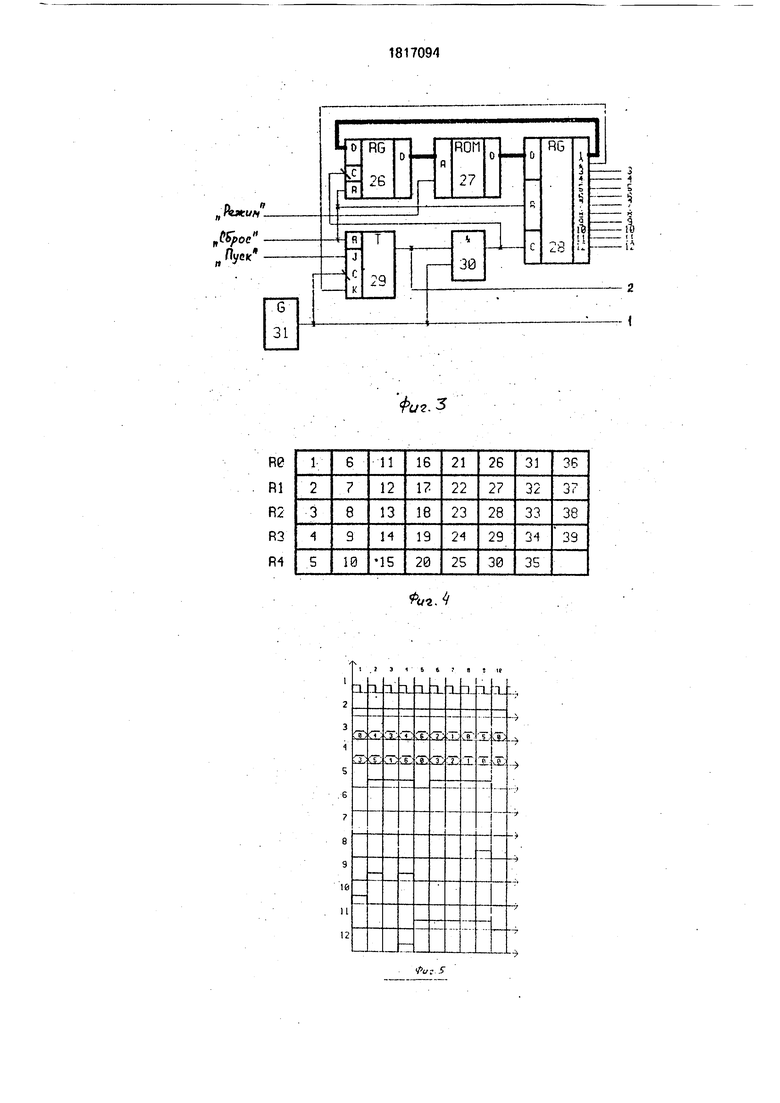

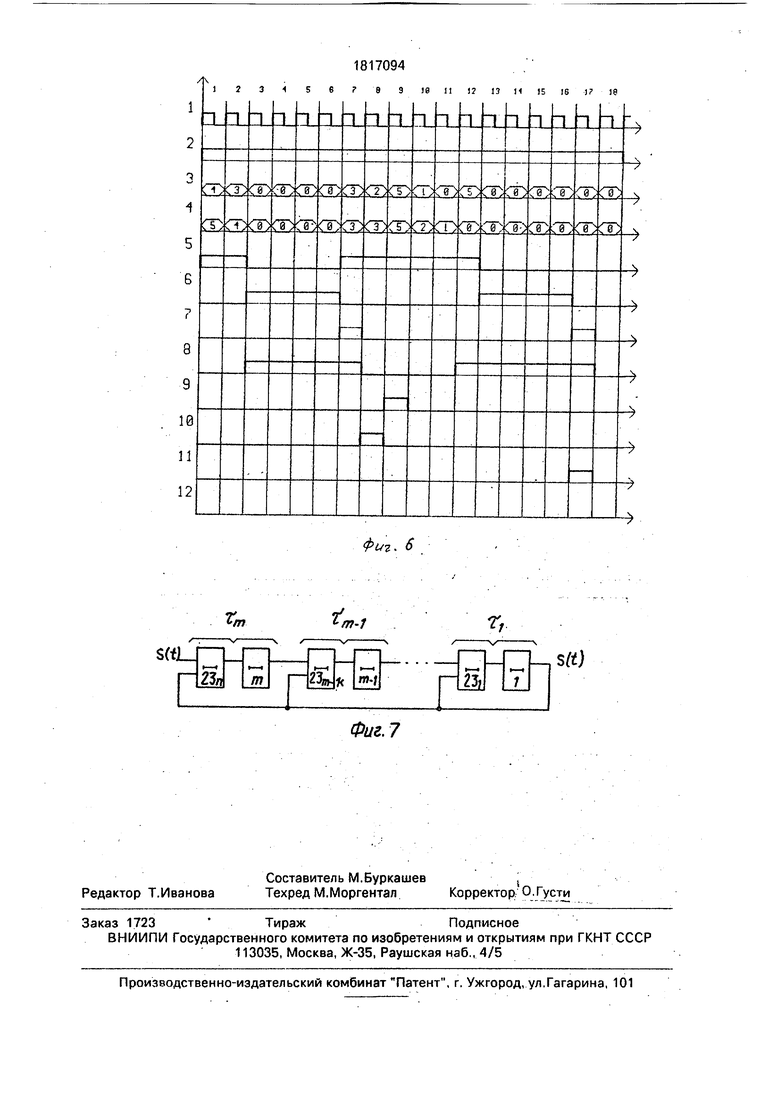

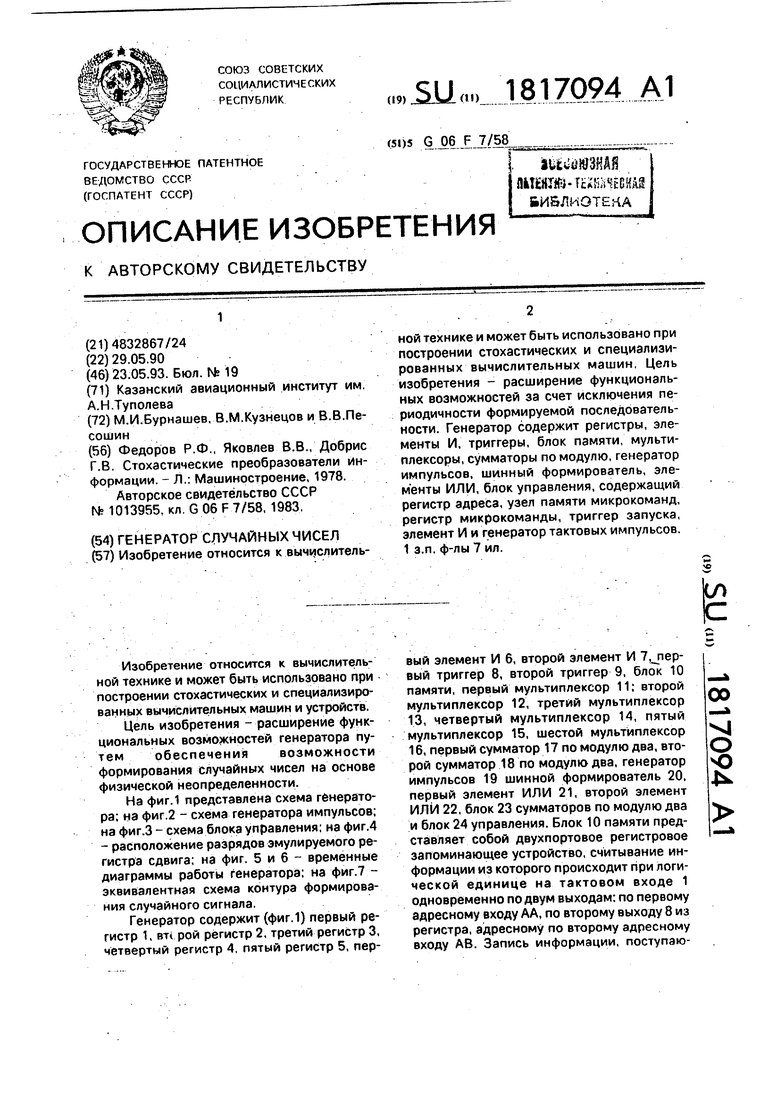

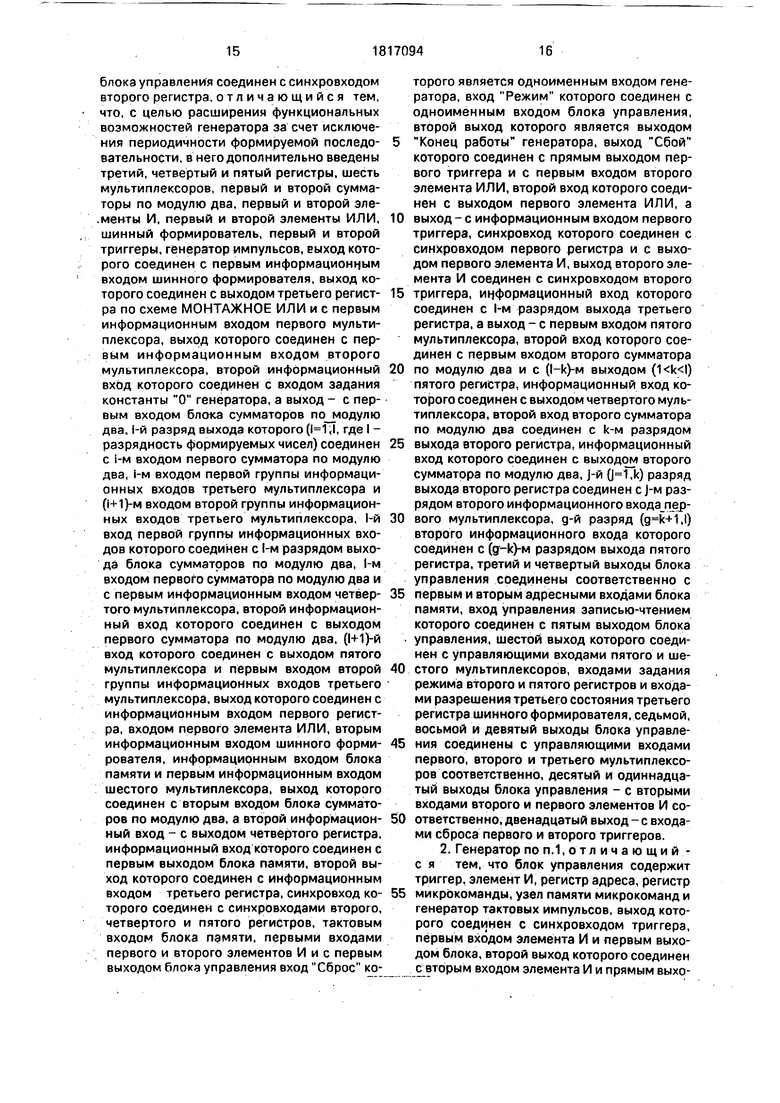

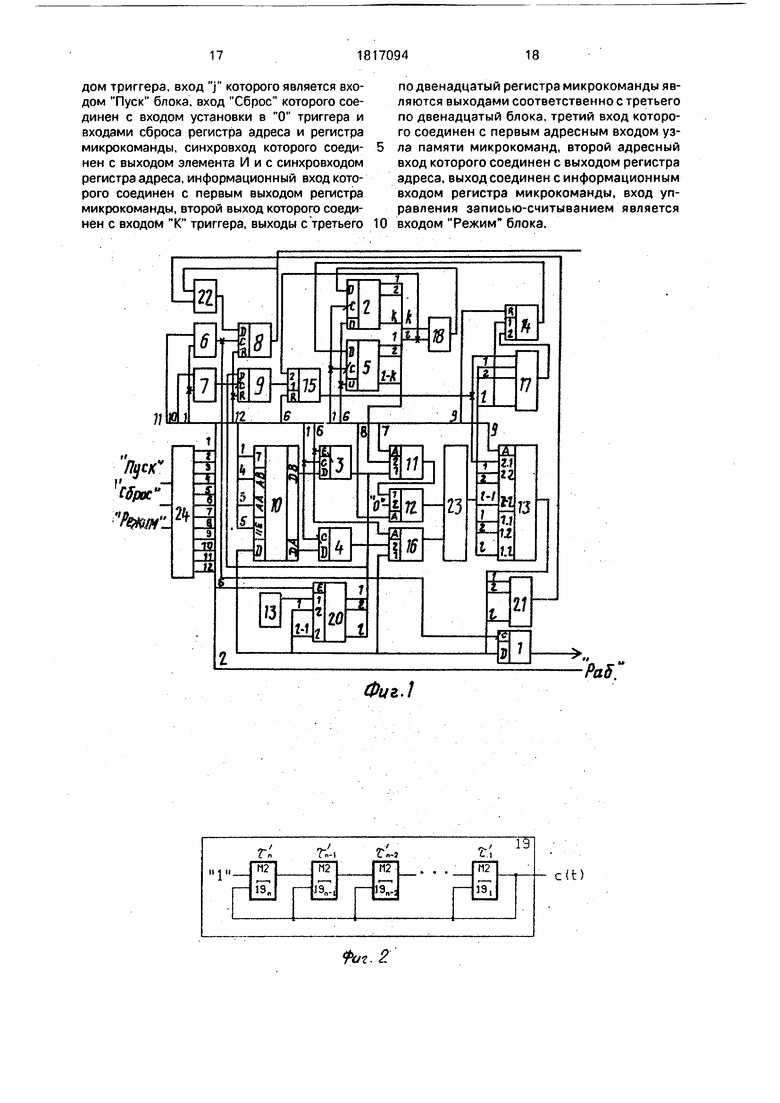

На фиг.1 представлена схема генератора; на фиг.2 - схема генератора импульсов; на фиг.З - схема блока управления; на фиг.4 - расположение разрядов эмулируемого регистра сдвига; на фиг. 5 и 6 - временные диаграммы работы генератора; на фиг.7 - эквивалентная схема контура формирования случайного сигнала.

Генератор содержит (фиг.1) первый регистр 1, вт рой регистр 2, третий регистр 3, четвертый регистр 4, пятый регистр 5, первый элемент И 6, второй элемент И 7чпер- вый триггер 8, второй триггер 9, блок 10 памяти, первый мультиплексор 11; второй мультиплексор 12, третий мультиплексор 13, четвертый мультиплексор 14, пятый мультиплексор 15, шестой мультиплексор 16, первый сумматор 17 по модулю два, второй сумматор 18 по модулю два, генератор импульсов 19 шинной формирователь 20, первый элемент ИЛИ 21, второй элемент ИЛИ 22, блок 23 сумматоров по модулю два и блок 24 управления. Блок 10 памяти представляет собой двухпортовое регистровое запоминающее устройство, считывание информации из которого происходит при логической единице на тактовом входе 1 одновременно по двум выходам: по первому адресному входу АА, по второму выходу 8 из регистра, адресному по второму адресному входу АВ. Запись информации, поступаю00

VJ

О

2

щей на вход блока 10 памяти осуществляется в регистр, адресуемый по второму адресному входу АВ при логическом нуле на тактовом входе 1 и логической единице на входе WE управления записью-чтением.

Генератор импульсов 19 (фиг.2) содержит группу сумматоров 19i-19n по модулю два.

Блок 24 управления (фиг.З) содержит регистр 26 адреса, узел 27 задания микрокоманд, выполненный в виде блока памяти, регистр 29 микрокоманды, триггер 29 запуска, элемент И 30 и генератор 31 тактовых импульсов. Назначение выходов блока 24 управления следующее:

по первому выходу передаются синхроимпульсы (СИ);

по второму выходу блок 24 управления сигнализирует о формировании очередного числа (логическая единица на этом выходе) либо о завершении формирования числа (логический ноль);

по третьему выходу передается адрес на первый адресный вход АА блока 10 памяти;

по четвертому выходу передается адрес на второй адресный вход АВ блока 10 памяти;

по пятому выходу передается сигнал на вход управления записью-чтением блока 10 памяти;

по шестому выходу передается сигнал, который управляет передачей данных через пятый мультиплексор 15 (логический ноль обеспечивает передачу данных с первого входа, логическая единица - со второго входа), управляет передачей данных через шестой мультиплексор 16 (логический ноль обеспечивает передачу данных со второго входа, логический единица - с первого входа), управляет режимом работы второго регистра 2 и пятого регистра 5 (логический ноль задает режим хранения, логическая единица - режим сдвига), осуществляет мультиплексирование данных, поступающих на первый вход первого мультиплексора 11 (логический ноль переводит выходы шинного формирователя 20 в третье состояние и на первый вход первого мультиплексора 11 поступают данные с выхода третьего регистра 3, логическая единица переводит выходы третьего регистра 3 в третье состояние и на первый вход первого мультиплексора 11 поступают данные с выхода буферного элемента 20);

по седьмому выходу передается сигнал, управляющий передачей данных через первый мультиплексор 11 (логический ноль обеспечивает передачу данных с первого

входа, логическая единица - со второго входа);

по восьмому выходу передается сигнал, управляющий передачей данных через второй мультиплексор 12 на первый вход блока 23 сумматоров по модулю два (логический ноль обеспечивает передачу константы О со второго входа, логическая единица - передачу данных с первого входа второго

мультиплексора 12);

по девятому выходу передается сигнал, управляющий передачей данных с выхода блока 23 сумматоров по модулю два через третий мультиплексор 13 (логический ноль

5 обеспечивает передачу.данных с первой группы входов, т.е. без сдвига, логическая единица - со второй группы входом, т.е. со сдвигом на один разряд в сторону младших разрядов с занесением в освобождающийся

0 разряд информации с выхода пятого мультиплексора 15 (и управляющий ноль обеспечивает передачу данных со второго входа, логическая единица - с первого входа); по десятому выходу передается сигнал

5 разрешения записи во второй триггер 9 (логическая единица обеспечивает прохождение ЧИ через второй элемент И 7 на синхровход второго триггера 9);

по одиннадцатому выходу передается

0 сигнал разрешения записи в первый регистр 1 и в первый триггер 8 (логическая единица обеспечивает прохождение СИ через первый элемент И 6 на синхровходы первого регистра 1 и первого триггера 8);

5 по двенадцатому выходу передается сигнал установки в нулевое состояние первого триггера 8 и второго триггера 9 (при логической единице).

Работу устройства рассмотрим на конк0 ретном примере. Пусть f(x) Xgf x8tp1 - образующий полином М-последовательности, разрядность формируемых чисел - 8 (), k 4. В регистрах блока 10 памяти эмулируется кольцевой регистр сдвига, состояний из

5 31 D-триггера и 8 Т-триггеров, Расположение разрядов эмулируемого регистра сдвига в регистрах блока 10 памяти показано на фиг.4. Т-триггеры располагаются в нулевом регистре (обозначенном как RO), D-триггеры

0 - в остальных. Дополнительно используются регистры R 5 и R 6 блока 10 памяти. Для упрощения цепи занесения в блок 10 памяти начального состояния эмулируемого кольцевого регистра сдвига не показаны.

5

Устройство имеет два режима обработки: режим формирования псевдослучайного числа и режим формирования случайного числа. Режим работы задается по входу режим генератора.

Устройство работает следующим образом.

По сигналу, поступающему по входу сброс генератора производится установка в начальное состояние блока 24 управле- ния. По сигналу, поступающему по входу Пуск генератора, блок 24 управления. ПО сигналу, поступающему по входу пуск генератора, блок 24 управления начинает выдавать управляющие сигналы по своим выходам в каждом такте.

В режиме формирования псевдослучайного числа осуществляется сдвиг на один разряд содержимого эмулируемого кольцевого регистра сдвига, проверка нулевого со- стояния всех разрядов этого регистра и запись сформированного псевдослучайного числа в первый регистр 1. В первом такте этого режима (фиг.5) по сигналам с выходов блока 24 управления производится следую- щее: из блока 10 памяти по второму выходу DB считывается содержимое и по срезу синхроимпульса записывается в третий регистр 3, с выхода которого значение младшего -(1-го) разряда поступает на информационный вход второго триггера Я9 и записывается в него по фронту следующего СИ. Запись информации в блок 10 памяти в первом такте не производится. Во втором такте из блока 10 памяти по первому выходу DA считывается содержимое R4 по срезу Я СИ записывается в четвертый регистр 4. С выхода четвертого регистра 4 через шестой мультиплексор 14 информация поступает на второй вход блока 23 сумматоров по модулю два. На первый вход блока 23 сумматоров по модулю два поступает константа О с выхода второго мультиплексора 12. Таким образом, информация с выхода четвертого регистра 4 поступает на вторую группу е- редает ее со сдвигом в сторону младших разрядов, при этом в освобождающийся разряд через пятый мультиплексор 15 заносится двоичный символ с выхода второго триггера 9, т.е. содержимое последнего раз- ряда эмулируемого кольцевого регистра сдвига. С выхода третьего мультиплексора 13 эта информация поступает на информационный вход D блока 10 памяти и записывается в R5. В третьем такте формируется новое содержимое R4. По первому выходу DA из блока 10 памяти считывается содер- . жимое выхода четвертого регистра 4 через шестой мультиплексор 16 и блок 23 сумматоров по модулю два поступает на первую группу информационных входов третьего мультиплексора 13, с выхода которого она поступает на информационный вход D блока 10 памяти и записывается в R4. В четвертом такте первый триггер 8 и второй триггер

9 устанавливаются в нулевое состояние. Из блока 10 памяти по первому выходу DA считывается содержимое R4 и по срезу СИ записывается в четвертый регистр 4. Информация с выхода четвертого регистра 4 через шестой мультиплексор 16 и блок 23 сумматоров по модулю два поступает на вторую группу входов третьего мультиплексора 13, который передает ее со сдвигом в сторону младших разрядов, при этом в освобождающийся разряд через пятый мультиплексор 15 заносится логический ноль с выхода второго триггера 9, установленного в нулевое состояние в начале такта. С выхода третьего мультиплексора 13 эта информация записывается в R6 блока 10 памяти. В лятом такте анализируется содержимое R6 блока 10 памяти, для чего оно считывается по первому выходу DA и по срезу СИ записывается в четвертый регистр 4. Далее оно через шестой мультиплексор 16, блок 23 сумматоров по модулю два и первую группу входов третьего мультиплексора 13 поступает на входы первого элемента ИЛИ 21. С выхода первого элемента ИЛИ 21 результат проверки поступает на второй вход второго элемента ИЛИ 22 и проходит на информационный вход первого триггера 8, т.к. на первый вход второго элемента ИЛИ 22 поступает логический ноль с выхода первого элемента ИЛИ 22 поступает логический ноль с выхода первого триггера 8. По фронту следующего СИ результат проверки содержимого R6 блока 10 памяти записывается в первый триггер 8. В случае нулевого содержимого R6 (во всех разрядах логические нули) на выходе первого элемента ИЛИ 21 формируется логический ноль, который записывается в первый триггер 8 (в этом случае первый триггер 8 останется в нулевом состоянии). В случае нулевого содержимого R6 в первый триггер 8 записывается логическая единица, которая будет поступать через второй элемент ИЛИ 22 на информационный вход первого триггера 8 независимо от результатов в последующих тактах (первый триггер 8 будет оставаться в единичном состоянии до окончания режима). В шестом такте формируется и проверяется новое содержимое R3 блока 10 памяти. По первому выходу DA из блока 10 памяти . считывается содержимое R2 и по срезу СИ записывается в четвертый регистр 4. Информация с выхода четвертого регистра 4 через шестой мультиплексор 16, блок 23 сумматоров по модулю и первую группу входов третьего мультиплексора 13 передается без сдвига на его выход, проверяется вышеописанным образом, поступает на информационный вход D блока 10 памяти и

записывается в 3. В седьмом и восьмом тактах аналогично формируется и проверяется новое содержимое R2 и R1 из содержимого R1 и RO соответственно. В девятом такте из блока 10 памяти считывается содержимое R5 по первому выходу DA и содержимое RO по второму выходу В. По срезу СИ эта информация записывается в четвертый регистр 4 и третий регистр 3 соответственно. С выхода третьего регистра 3 содержимое RO через первый мультиплексор 11 м второй мультиплексор 12 поступает на первый вход блока 23 сумматоров по модулю два, на второй вход которого через шестой мультиплексор 16 поступает содержимое R5 с выхода четвертого регистра 4. Результат поразрядного сложения по модулю два через первую группу входов третьего мультиплексора 13 поступает без сдвига на его выход, проверяется вышеописанным образом и за- писывается в RO блока 10 памяти. По фронту следующего СИ этот результат записывается в первый регистр 1 и поступает на информационный выход генератора в качестве очередного псевдослучайного чис- ла. По фронту этого же СИ в первый триггер 8 записывается окончательный результат проверки нулевого состояния, который с выхода первого триггера 8 поступает на выход сбой генератора, В десятом такте режима формирования псевдослучайного числа блок 24 управления останавливается. На выход раб генератора поступает логический ноль, свидетельствующий об окончании режима. Логический ноль на выходе сбой генератора при заданном формировании псевдослучайных чисел свидетельствует о нулевом состоянии всех разрядов эмулируемого кольцевого регистра сдвига.

В режиме формирования случайного числа осуществляется сдвиг на один разряд содержимого эмулируемого кольцевого регистра сдвига введением случайного символа в цепь обратной связи, формирование случайного числа путем суммирования по модулю два псевдослучайного числа и случайного кода и запись его в первый регистр 1. В первом такте этого режима (фиг.6) на блоке 10 памяти считывается содержимое R4 и по срезу СИ записывается в четвертый регистр 4, информации с выхода которого через шестой мультиплексор 16 поступает на второй вход блока 23 сумматоров по модулю два. На первый вход блока 23 сумматора по модулю два. На первый вход блока 23 сумматоров по модулю два поступает константа О с выхода второго мультиплексора 12, Таким образом, содержимое R4 поступает на первую группу входов третьего мультиплексора 13, передается на втором

такте аналогично формируется новое содержимое R4 блока 10 памяти из содержимого R3, В следующих k тактах режима формирования случайного числа устройство формирует 1-разрядный случайный код, который записывается на второй регистр 2 и пятый регистр 5 (для рассматриваемого случая , ). В третьем, четвертом, пятом и шестом тактах блок 24 управления формирует управляющие сигналы, обеспечивающие одновременную реализацию трех функций:

формирование асинхронного (непрерывного по времени) случайного сигнала;

преобразование асинхронного случайного сигнала, в синхронизатор (тактированную) последовательность случайных символов;

выравнивание статистических характеристик случайного кода.

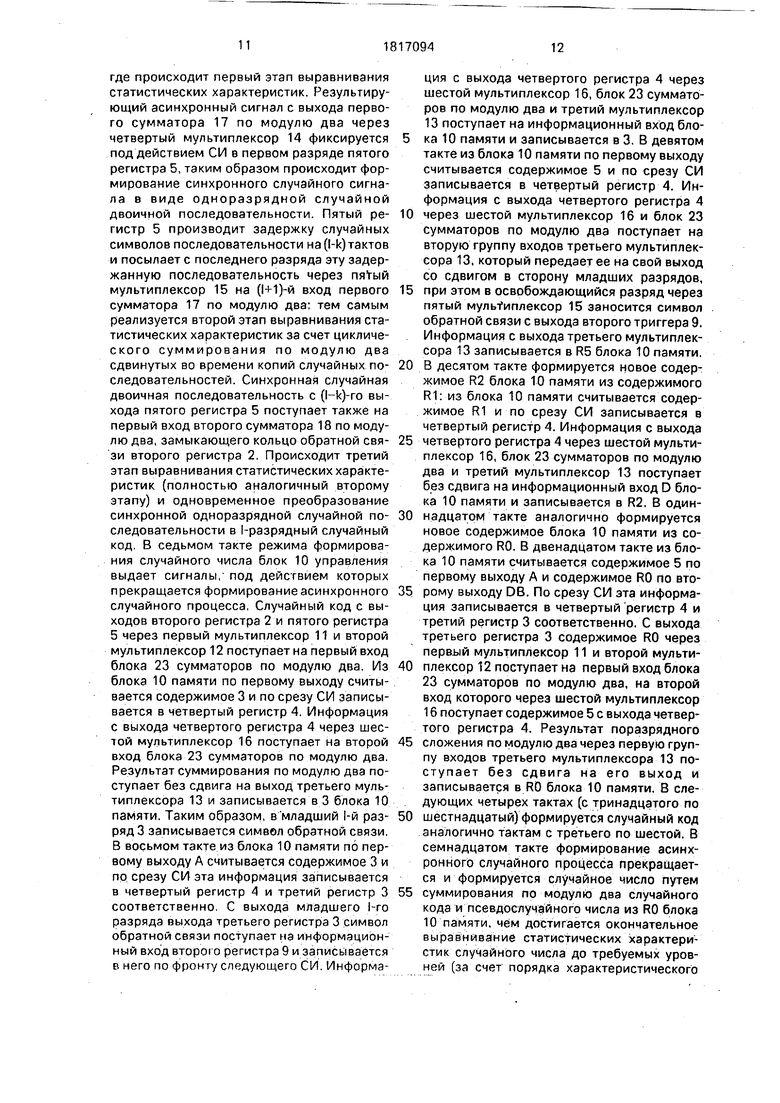

Источником физической случайности является цепь из m I последовательно соединенных сумматоров 23J по модулю два из блока 23 сумматоров по модулю два и m элементов, поразрядно выделенных из мультиплексоров 11, 12, 13, 16 и буферного элемента 20, выполняющих в этом случае функции логических повторителей с задержками. Эта цепь охвачена множеством обратных связей по свободным входам сумматоров 23J по модулю два. Задержки элементов 11,12, 13, 16 и 20 как повторителей сосредоточим по выходам сумматоров по модулю два. Схема образованного таким путем контура представлена на фиг.7. Процесс s(t) на выходе цепи определяется рекуррентным выражением:

s(t)-« s(t- I rj)®c(f)

где tj - суммарная задержка j-го сумматора 23j по модулю и j-ro повторителя;

c(t) - внешний сигнал возбуждения (с выхода генератора импульсов 19):

t- непрерывное время работы контура;

CD 2 © символы суммирования по модулю два.

Это выражение при постоянных параметрах rj и c(t) описывает процесс формирования псевдослучайного сигнала. Однако задержки TI , TZ ,.., , тт реальных логических элементов как непрерывные величины всегда флуктуируют во времени, т.е. задержки одного и того же элемента от срабаты- вания к срабатыванию несколько отличаются друг от друга. Выходной процесс в этом случае теряет детерминированный характер (как псевдослучайный) и будет

представлять собой временную совокупность случайных по длительности отрезков псевдослучайных последовательностей различных структур. В рабочем диапазоне температур любые реальные логические элементы (например, сумматоры по модулю два и повторители в схеме по фиг.Т) характеризуются относительными флюктуациями в форме вариации задержки порядка тысячных и десятитысячных долей единицы. Не- смотря на такие малые уровни временных флюктуации контур по фиг.7 при достаточно большом формирует случайный процесс s(t)€ 0,1 телеграфного типа с предельным значением коэффициента вариации. Как по- казывают многочисленные опыты и практически применения подобных контуров, построенных на ТТЛ-элементах, широкополосный случайный процесс телеграфного типа формируется при m 8...10. Малое значение m приводит к явлению автосинхронизма, вследствие чего процесс s(t) вырождается в детерминированный (периодический). Сигнал c(t) при достаточно большом m на стохастичность поведения контура не влияет. Однако его значение определяет устойчивость (и стационарность) формирования случайного процесса s(t) в смысле отсутствия статически устойчивых (неизменных во времени) состояний. Уело- вием устойчивости процесса в этом смысле является, например, нечетность числа m при постоянном c(t) 1. Малые значения требуют воздействия на кбнтур изменяющегося во времени сигнала возбуждения, т.е. c(t) - как процесс. При этом четность или нечетность m принципиальной роли не играет. Такое внешнее воздействие на контур препятствует возникновению эффекта автосинхронизма и установки в статически ус- тойчивое состояние. В случаях редкой фиксации случайных символов, снимаемых с контура (при малых скоростях работы всего устройства, например, для ТТД-элемен- тов - 10 кГц и ниже) допустимо формирование периодического сигнала возбуждения c(t) с длительностью импульсов Г4 и паузой тп. Необходимо лишь выполнить

условие

тах{ Г4 , Т4 } :Ј 2/ ri

чтобы длительное время не возникали логически устойчивые состояния контура.

Для более качественной работы и в случае предельного быстродействия целесообразно формировать сигнал c(t) как случайный сигнал телеграфного типа.

Все вышеописанные режимы устойчивой работы контура как основного источника физической случайности обеспечивается структурой генератора импульсов 19, схема которого приведена на фиг.2. Процесс c(t) описывается аналогично (1) для s(t), т.е. г ...j

cCt)- © )®,

(3)

где rj - задержка J-ro сумматора.

Описание работы генератора импульсов 19 полностью аналогично описанию функционирования рабочего контура. Оли- шем три типичных варианта использования генератора импульсов 19.

®1.сО-1ч )-о

получим c(t) 1.

В устройстве реализуются следующие известные способы выравнивания статистических характеристик исходного случайного процесса:

- одновременное суммирование по модулю два нескольких исходных случайных процессов;

- суммирование по модулю два случайной двоичной последовательности со сдвинутой во времени (например, с помощью задержки)своей же копией.

С контура формирования первичного случайного сигнала асинхронных случайных процессов поступают на входы с первого по m-й первого сумматора 11 по модулю два.

где происходит первый этап выравнивания статистических характеристик. Результирующий асинхронный сигнал с выхода первого сумматора 17 по модулю два через четвертый мультиплексор 14 фиксируется под действием СИ в первом разряде пятого регистра 5, таким образом происходит формирование синхронного случайного сигнала в виде одноразрядной случайной двоичной последовательности. Пятый регистр 5 производит задержку случайных символов последовательности на (l-k) тактов и посылает с последнего разряда эту задержанную последовательность через пятый мультиплексор 15 на (1+1)-й вход первого сумматора 17 по модулю два: тем самым реализуется второй этап выравнивания статистических характеристик за счет циклического суммирования по модулю два сдвинутых во времени копий случайных последовательностей. Синхронная случайная двоичная последовательность с (l-k)-ro выхода пятого регистра 5 поступает также на первый вход второго сумматора 18 по модулю два, замыкающего кольцо обратной связи второго регистра 2. Происходит третий этап выравнивания статистических характеристик (полностью аналогичный второму этапу) и одновременное преобразование синхронной одноразрядной случайной последовательности в 1-разрядный случайный код. В седьмом такте режима формирования случайного числа блок 10 управления выдает сигналы,- под действием которых прекращается формирование асинхронного случайного процесса, Случайный код с выходов второго регистра 2 и пятого регистра 5 через первый мультиплексор 11 и второй мультиплексор 12 поступает на первый вход блока 23 сумматоров по модулю два. Из блока 10 памяти по первому выходу считывается содержимое 3 и по срезу СИ записывается в четвертый регистр 4. Информация с выхода четвертого регистра 4 через шестой мультиплексор 16 поступает на второй вход блока 23 сумматоров по модулю два. Результат суммирования по модулю два поступает без сдвига на выход третьего мультиплексора 13 и записывается в 3 блока 10 памяти. Таким образом, в младший 1-й разряд 3 записывается символ обратной связи. В восьмом такте из блока 10 памяти по первому выходу А считывается содержимое 3 и по срезу СИ эта информация записывается в четвертый регистр 4 и третий регистр 3 соответственно. С выхода младшего 1-го разряда выхода третьего регистра 3 символ обратной связи поступает на информационный вход второго регистра 9 и записывается в него по фронту следующего СИ. Информация с выхода четвертого регистра 4 через шестой мультиплексор 16, блок 23 сумматоров по модулю два и третий мультиплексор 13 поступает на информационный вход блока 10 памяти и записывается в 3. В девятом такте из блока 10 памяти по первому выходу считывается содержимое 5 и по срезу СИ записывается в четвертый регистр 4. Информация с выхода четвертого регистра 4

0 через шестой мультиплексор 16 и блок 23 сумматоров по модулю два поступает на вторую группу входов третьего мультиплексора 13, который передает ее на свой выход со сдвигом в сторону младших разрядов,

5 при этом в освобождающийся разряд через пятый мультиплексор 15 заносится символ обратной связи с выхода второго триггера 9. Информация с выхода третьего мультиплексора 13 записывается в R5 блока 10 памяти,

0 В десятом такте формируется новое содержимое R2 блока 10 памяти из содержимого R1: из блока 10 памяти считывается содержимое R1 и по срезу СИ записывается в четвертый регистр 4. Информация с выхода

5 четвертого регистра 4 через шестой мультиплексор 16, блок 23 сумматоров по модулю два и третий мультиплексор 13 поступает без сдвига на информационный вход D блока 10 памяти и записывается в R2. В один0 надцатом такте аналогично формируется новое содержимое блока 10 памяти из содержимого RO. В двенадцатом такте из блока 10 памяти считывается содержимое 5 по первому выходу А и содержимое RO по вто5 рому выходу DB. По срезу СИ эта информация записывается в четвертый регистр 4 и третий регистр 3 соответственно, С выхода третьего регистра 3 содержимое RO через первый мультиплексор 11 и второй мульти0 плексор 12 поступает на первый вход блока 23 сумматоров по модулю два, на второй вход которого через шестой мультиплексор 16 поступает содержимое 5 с выхода четвертого регистра 4. Результат поразрядного

5 сложения по модулю два через первую группу входов третьего мультиплексора 13 поступает без сдвига на его выход и записывается в RO блока 10 памяти. В следующих четырех тактах (с тринадцатого по

0 шестнадцатый) формируется случайный код аналогично тактам с третьего по шестой, В семнадцатом такте формирование асинхронного случайного процесса прекращается и формируется случайное число путем

5 суммирования по модулю два случайного кода и псевдослучайного числа из RO блока 10 памяти, чём достигается окончательное выравнивание статистических характеристик случайного числа до требуемых уровней (за счет порядка характеристического

полинома). Из RO блока 10 памяти считывается по первому выходу DA считывается псевдослучайное число и по срезу СИ записывается в четвертый регистр 4, с выхода которого через шестой мультиплексор 16 оно поступает на второй вход блока 23 сумматоров по модулю два, Случайный код из второго регистра 2 и пятого регистра 5 через первый мультиплексор 11 и второй мультиплексор 12 поступает на первый вход блока 23 сумматоров по модулю два, с выхода которого сформированное случайное число передается без сдвига через третий мультиплексор .13 на информационный вход первого регистра 1 и записывается в него по фронту следующего СИ. Запись в блок 10 памяти в семнадцатом такте не производится. В восемнадцатом такте блок 24 управления останавливается. На выход раб генератора поступает логический ноль, свидетельствующий о завершении режима.

По следующему сигналу пуск блок 24 управления инициирует либо режим формирования псевдослучайного числа, либо режим формирования случайного числа в зависимости от вида формируемых чисел, задаваемого по входу режим генератора.

Блок 24 управления работает следующим образом.

По сигналу сброс, поступающему на второй вход блока 24 управления, триггер 29 запуска, регистр 26 адреса и регистр 28 микрокоманды устанавливаются в нулевое состояние. Элемент И 30 блокирует прохождение СИ с выхода генератора 31 тактовых импульсов на синхровходы регистра 26 адреса и регистра 28 микрокоманды. На входы J и К триггера 29 запуска 29 запуска поступают логические нули, а триггер остается в нулевом состоянии до прихода сигнала пуск по первому входу блока 24 управления на вход J триггера 29 запуска. По срезу СИ триггер 29 запуска устанавливается в единичное состояние и на второй выход блока 24 управления поступает логическая единица. Следующие СИ через элемент И 30 поступают на синхровходы регистра 26 адреса и регистра 28 микрокоманды, причем запись в регистр 28 микрокоманды производится при логической единице на его синхровходе, а запись в регистр 26 адреса - по срезу импульса на его синхровходе. Таким образом, в начале каждого такта на выходы регистра 28 микрокоманды выдается очередная микрокоманда, С выхода регистра 28 микрокоманды адрес следующей микрокоманды поступает на информационный вход регистра 26 адреса и записывается в него по среду СИ. Этот адрес с выхода регистра 26 адреса поступает

на второй адресный вход узла 27 задания микрокоманд в качестве младших разрядов адреса следующей микрокоманды. Старший разряд адреса следующей микрокоманды 5 поступает на первый адресный вход узла 27 задания микрокоманд с третьего входа блока 24 управления. Таким образом формируется полный адрес следующей микрокоманды, которая поступает с выхода

10 узла 27 задания микрокоманд на информационный вход регистра 28 микрокоманд, записывается в него и выдается в качестве очередной микрокоманды. По адресу 00..,0 в узле 27 задания микрокоманд записана

15 микрокоманда, соответствующая первому такту режима формирования псевдослучайного числа, а по адресу 10...О - соответствующая первому такту режима формирования случайного числа. Останов блока 24 управ0 ления производится следующим образом, В микрокомандах, соответствующих такту останова, на вход К триггера 29 запуска посту- пает логическая единица, а на информационный вход регистра 26 адреса

5 передается нулевой адрес. По срезу СИ нулевой адрес записывается в регистр 26 адреса, а триггер 29 запуска устанавливается в нулевое состояние. Логический ноль с выхода триггера 29 запуска блокирует прохож0 дение СИ на синхровходы регистра 26 адреса и регистра 28 микрокоманды, а также поступает на второй выход блока 24 управления, сигнализируя о завершении формирования очередного числа. С прихо5 дом следующего сигнала пуск на входах J и Ктриггера 29 запуска одновременно будут присутствовать логические единицы, поэтому по срезу СИ триггер 29 запуска установится в единичное состояние. Далее блок 24

0 управления работает аналогично. Генератор может быть реализован, например на основе микропроцессорных секций К1804ВС2, причем функции второго мультиплексора 12 и блока 23 сумматоров по моду5 людва реализуются в арифметико-логическом устройстве используемых секций.

Преимуществом предлагаемого генератора по сравнению с известным является то,

0 что он позволяет формировать случайные числа на основе физической неопределенности.

Формула изобретения

блока управления соединен с синхровходом второго регистра, отличающийся тем, что, с целью расширения функциональных возможностей генератора за счет исключения периодичности формируемой последовательности, в него дополнительно введены третий, четвертый и пятый регистры, шесть мультиплексоров, первый и второй сумматоры по модулю два, первый и второй эле- .менты И, первый и второй элементы ИЛИ, шинный формирователь, первый и второй триггеры, генератор импульсов, выход которого соединен с первым информационным входом шинного формирователя, выход которого соединен с выходом третьего регистра по схеме МОНТАЖНОЕ ИЛИ и с первым информационным входом первого мультиплексора, выход которого соединен с первым информационным входом второго мультиплексора, второй информационный вход которого соединен с входом задания константы О генератора, а выход - с первым входом блока сумматоров по модулю два, i-й разряд выхода которого (, где I - разрядность формируемых чисел) соединен с i-м входом первого сумматора по модулю два, i-м входом первой группы информационных входов третьего мультиплексора и 0+1)-м входом второй группы информационных входов третьего мультиплексора, 1-й вход первой группы информационных входов которого соединен с 1-м разрядом выхода блока сумматоров по модулю два, 1-м входом первого сумматора по модулю два и с первым информационным входом четвертого мультиплексора, второй информационный вход которого соединен с выходом первого сумматора по модулю два, (1+1)-й вход которого соединен с выходом пятого мультиплексора и первым входом второй группы информационных входов третьего мультиплексора, выход которого соединен с информационным входом первого регистра, входом первого элемента ИЛИ, вторым информационным входом шинного формирователя, информационным входом блока памяти и первым информационным входом шестого мультиплексора, выход которого соединен с вторым входом блока сумматоров по модулю два, а второй информационный вход - с выходом четвертого регистра, информационный вход которого соединен с первым выходом блока памяти, второй выход которого соединен с информационным входом третьего регистра, синхровход которого соединен с синхровходами второго, четвертого и пятого регистров, тактовым входом блока памяти, первыми входами первого и второго элементов И и с первым выходом блока управления вход Сброс которого является одноименным входом генератора, вход Режим которого соединен с одноименным входом блока управления, второй выход которого является выходом

Конец работы генератора, выход Сбой которого соединен с прямым выходом первого триггера и с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ, а

0 выход - с информационным входом первого триггера, синхровход которого соединен с синхровходом первого регистра и с выходом первого элемента И, выход второго элемента И соединен с синхровходом второго

5 триггера, информационный вход которого соединен с i-м разрядом выхода третьего регистра, а выход - с первым входом пятого мультиплексора, второй вход которого соединен с первым входом второго сумматора

0 по модулю два и с (l-k)-M выходом () пятого регистра, информационный вход которого соединен с выходом четвертого мультиплексора, второй вход второго сумматора по модулю два соединен с k-м разрядом

5 выхода второго регистра, информационный вход которого соединен с выходом второго сумматора по модулю два, j-й ,k) разряд выхода второго регистра соединен с j-м разрядом второго информационного входа пер0 вого мультиплексора, g-й разряд (,l) второго информационного входа которого соединен с (g-k)-M разрядом выхода пятого регистра, третий и четвертый выходы блока управления соединены соответственно с

5 первым и вторым адресными входами блока памяти, вход управления записью-чтением которого соединен с пятым выходом блока управления, шестой выход которого соединен с управляющими входами пятого и ше0 стого мультиплексоров, входами задания режима второго и пятого регистров и входами разрешения третьего состояния третьего регистра шинного формирователя, седьмой, восьмой и девятый выходы блока управле5 ния соединены с управляющими входами первого, второго и третьего мультиплексоров соответственно, десятый и одиннадцатый выходы блока управления - с вторыми входами второго и первого элементов И со0 ответственно, двенадцатый выход - с входами сброса первого и второго триггеров.

5 микрокоманды, узел памяти микрокоманд и генератор тактовых импульсов, выход которого соединен с синхровходом триггера, первым входом элемента И и первым выходом блока, второй выход которого соединен с вторым входом элемента И и прямым выходом триггера, вход j которого является входом Пуск блока, вход Сброс которого соединен с входом установки в О триггера и входами сброса регистра адреса и регистра микрокоманды, синхровход которого соединен с выходом элемента И и с синхровходом регистра адреса, информационный вход которого соединен с первым выходом регистра микрокоманды, второй выход которого соединен с входом К триггера, выходы с третьего

Фаг. 2

по двенадцатый регистра микрокоманды являются выходами соответственно стретьего по двенадцатый блока, третий вход которого соединен с первым адресным входом узла памяти микрокоманд, второй адресный вход которого соединен с выходом регистра адреса, выход соединен с информационным входом регистра микрокоманды, вход управления записью-считыванием является входом Режим блока.

Фиг.1

Т

о о

со

a «J

00

ЙЧюCV

c

iS-. rxl

Cil -i CN СЧ 4tr cc cc cc o:

ьт

т-1

Фиг 6

Ъ UTT-,sffJ

Фиг. 7

| Федоров Р.Ф., Яковлев В.В., Добрис Г.В | |||

| Стохастические преобразователи информации | |||

| - Л.: Машиностроение, 1978 | |||

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

Авторы

Даты

1993-05-23—Публикация

1990-05-29—Подача