| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управляемой задержки импульсов | 1985 |

|

SU1290503A1 |

| Устройство для синхронизации М-последовательности | 1985 |

|

SU1322429A2 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ | 1992 |

|

RU2025048C1 |

| Сенсорная клавиатура | 1988 |

|

SU1555851A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1396277A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1345322A1 |

| Устройство кадровой синхронизации | 1990 |

|

SU1737745A1 |

| Устройство для измерения длительности импульсов | 1986 |

|

SU1405021A1 |

| Формирователь радиоимпульсов | 1990 |

|

SU1748221A1 |

| Устройство допускового контроля девиации частоты линейно-частотно-модулированного сигнала | 1985 |

|

SU1315911A1 |

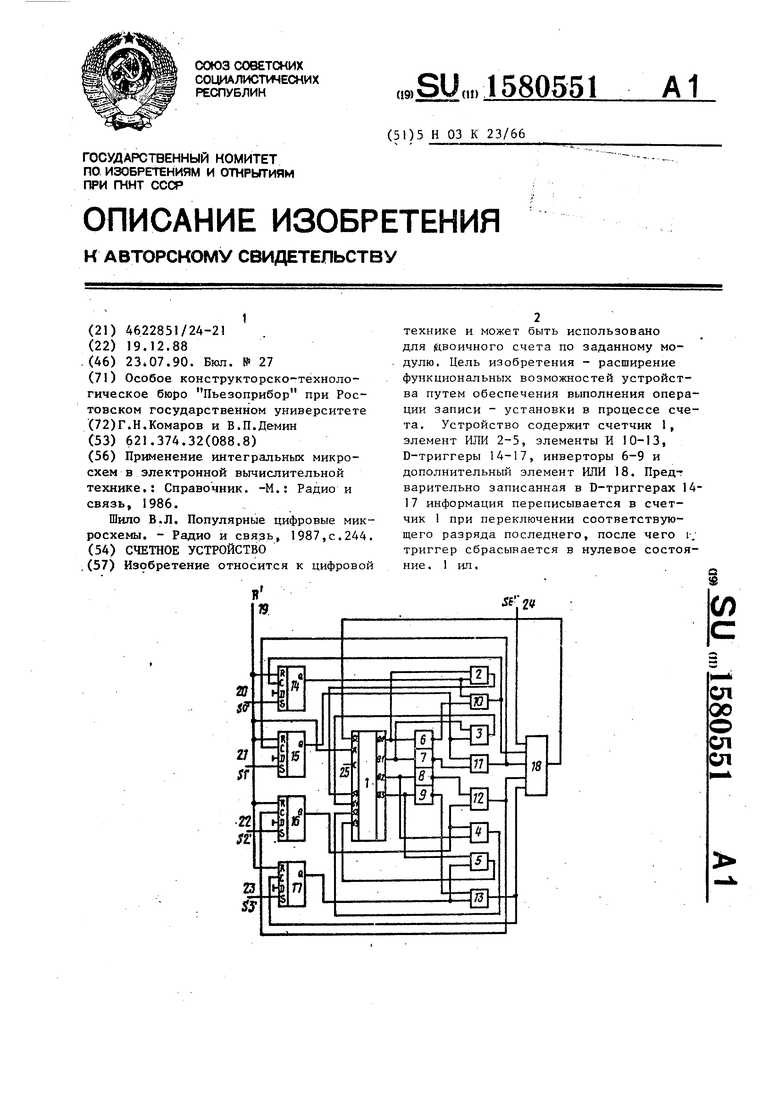

Изобретение относится к цифровой технике и может быть использовано для двоичного счета по заданному модулю. Цель изобретения - расширение функциональных возможностей устройства путем обеспечения выполнения операции записи - установки в процессе счета. Устройство содержит счетчик 1, элемент ИЛИ 2-5, элементы И 10-13, D-триггеры 14-17, инверторы 6-9 и дополнительный элемент ИЛИ 18. Предварительно записанная в D-триггерах 14-17 информация переписывается в счетчик 1 при переключении соответствующего разряда последнего, после чего триггер сбрасывается в нулевое состояние. 1 ил.

| Применение интегральных микросхем в электронной вычислительной технике.: Справочник | |||

| -М.: Радио и связь, 1986 | |||

| Шило В.Л | |||

| Популярные цифровые микросхемы | |||

| - Радио и связь, 1987,с.244. |

Авторы

Даты

1990-07-23—Публикация

1988-12-19—Подача