11

Изобретение относится к импульсной технике и может быть использовано в системах автоматической обработки данных,

Целью изобретения является повышение надежности и расширение функциональных возможностей за счет увепиче ния длины формируемых кодовых последвательностей.

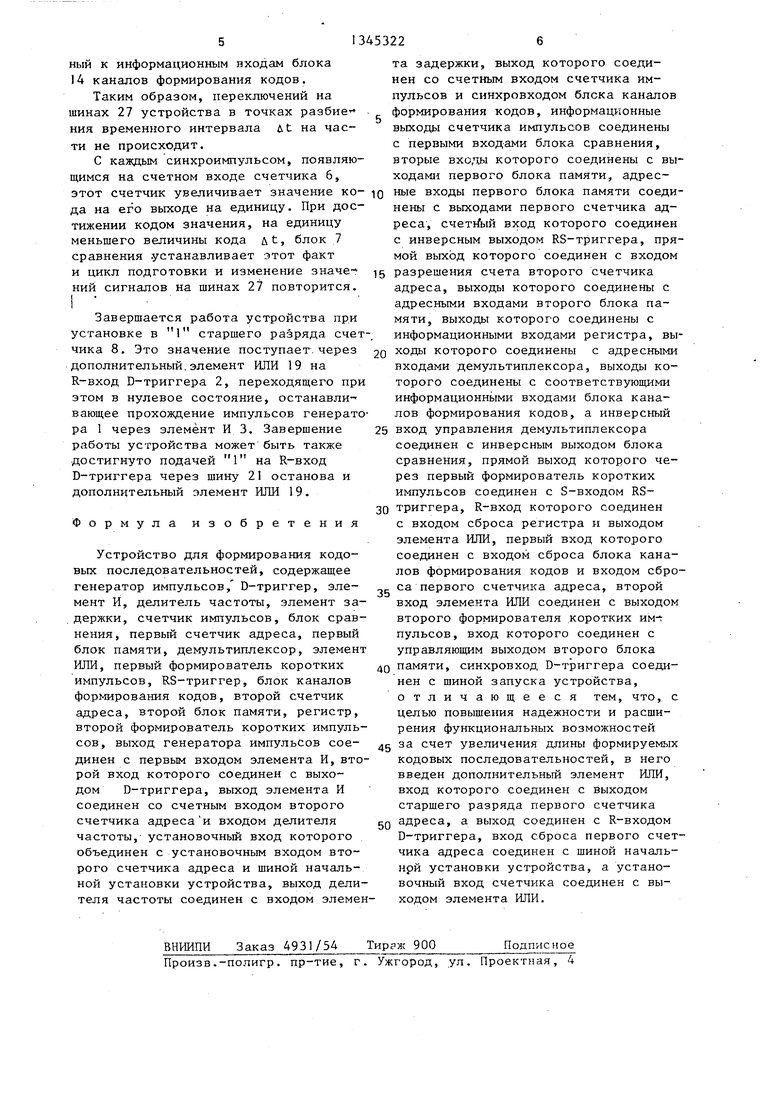

На чертеже представлена.структурная схема устройства для формирования кодовых последовательностей.

Устройство содержит генератор 1 импульсов, D-триггер 2, элемент И 3, делитель 4 частоты, элемент 5 задержки, счетчик 6 импульсов, блок 7 срав , первый счетчик 8 адреса, первый блок 9 памяти, демультиплексор 10,элемент ИЛИ 11, первый формирователь 12 коротких импульсов, RS-триг- гер 13, блок 14 каналов формирования кодов, второй счетчик 15 адреса, второй блок 16 памяти, регистр 17, вто

рой формирователь 18 коротких импуль- 25 ход соединен с R-зходом D-триггера

сов, дополнительный элемент ИЛИ 19, шину 20 запуска, шину 21. останова, шину 22 начальной установки, шины 23, 24, данных, адресные шины 25, 26, выходные шины 27, причем выход генератора 1 соединен с первым входом элемента ИЗ, второй вход которого соединен с выходом D-триггера 2, выход элемента И 3 соединен со счетным входом счетчика 15 и входом делителя 4, установочный вход которого объединен с установочным входом счетчика 15 и шиной 22, выход делителя А сое- .динен с входом элемента 5, выход которого соединен со счетным входом счет- чика 6 и синхровходом блока 14, информационные выходы счетчика 6 соединены с первыми входами блока 7, вто

Если временной интервал 4t бол ше максимального значения J , прини маемого счётчиком 6 ( 2. - 1 ,

рые входы которого соединены с выходами первого блока 9 памяти, информа- 45 Д разрядность счетчика 6), то ционны е входы которого соединены с этот временной интервал разбивается шиной 24 данных, адресные входы первого блока 9 памяти соединены с адресна минимальное количество интервалов не превьш1ающих по величине кода J . Например, при п 4, Jf 15 вреной шиной 26 и с выходами счетчика 8, счетный .вход которого соединен с инверсным выходом RS-триггера 13, прямой Выход которого соединен с входом разрешения счета счетчика 15, вьпсоды.которого соединены с адресной шиной 25 и адресными входами блока 16 памяти, информационные входы которого соединены с шиной 23 данных, а выходы соединены с информационными входами регистра 17, выходы которого

соединены с адресными входами демуль- типлексора 10, выходы которого с первого по соединены с соответствующими информационными входами блока 14, а инверсный вход управления де- мультиплексора 10 соединен с инверсным выходом блока 7 сравнения, прямой выход которого через формирователь 12 соединен с S-входом RS-триг- гера 13, R-вход которого соединен с

входом сброса регистра 17, установочным входом счетчика 6 и выходом элемента ИЛИ 1, первый вход которого соединен с входом сброса блока 14 каналов, входом сброса счетчика 8 и

шиной 22 начальной установки, второй вход элемента ИЛИ 11 соединен с выходом формирователя 18, вход которого соединен с управляющим выходом блока 16 памяти, выход старшего разряда счетчика В соединен с входом элемента ИЛИ 19, другой вход которого соединен с шиной 21 останова, а вы30

40

2, синхровход которого соединен с шиной 20, выходы блока 14 являются выходными шинами 27 устройства.

Каждый канал -блока 14 содержит в себ,е последовательно соединенные Т- триггеры и D-триггер.

Устройство работает следующим образом.

Предварительно в блок 9 памяти через 35 пшну 24 данных записывается последовательность кодов временных интервалов ut между соседними переключениями выходов устройства. Запись осуществляется, начиная с нулевого адреса (код адреса поступает через адресную шину 26).

Если временной интервал 4t больше максимального значения J , принимаемого счётчиком 6 ( 2. - 1 ,

45 Д разрядность счетчика 6), то этот временной интервал разбивается

Д разрядность счетчика 6), то этот временной интервал разбивается

на минимальное количество интервалов, не превьш1ающих по величине кода J . Например, при п 4, Jf 15 временной интервал иt 35 разбивается на три интервала; 15, 15 и 5.

В блок 16 ламяти через шину 23 дан- ных записываются последовательно группы из i кодов, i 1,п. Каждая

группа содержит коды номеров каналов блока 14 (или-, что то же самое,номеров выходных шин 27),изменяющих свои состояния в момент времени, на который указывает соответствующий времен313

ной интервал At. Если временной интервал ut разбивается на части, то всем полученным интервалам, кроме последнего, становятся в соответствие группы, состоящие из одного нулевого кода. В группе кодов номера каналов перечисляются в произвольном порядке. Код номера канала содержит дополни

тельный разряд, принимающий в послед- 10 тываются коды номеров каналов группы

нем коде каждой группы единичное значение и нулевое значение в других кодах. Этот признак окончания группы кодов считывается с управляющего выхода блока 16 памяти.

Перед пуском устройства сигналом Начальная установка, поступающим на шину 22, сбрасывается в ноль счетчик 8, триггеры блока 14 каналов (выходные шины 27), устанавливаются в единичное значение триггеры делителя 4 и счетчика 15, а через элемент ИЛИ 11 сбрасывается в ноль также регистр 17, КЗ-триггер 13 и устанавливаются в 1 все триггеры счетчика 6.

Импульс запуска, поступающий по шине 20 на вход установки D-триггера 2; устанавливает его в единичное состояние, разрешая прохождение импульсов с генератора 1 через элемент И 3 на счетный вход счетчика 15 и через делитель 4 на вход элемента 5 задержки, с выхода которого задержанные импульсы одновременно поступают на синхро- вход блока 14 и на счетный вход счетчика 6. Первый импульс с выхода элемента 5 переводит все триггеры счетчика 6 в следующее, нулевое,состояние. Код с выходов счетчика 6 поступает на первые.входы блока 7 сравнения. Б это время блок 9 памяти считывает по нулевому адресу, поступающему с выходов счетчика 8, первый код временного интервала t. Этот код поступает на вторые входы блока 7 сравнения, который уменьшает значение кода на единицу младшего разряда и сравнивает полученный результат с кодом счетчика 6. При совпадении сравниваемых кодов сигнал О инверсного выхода блока 7 сравнения поступает на. инверсный вход управления демультиплек- сора 10, а единичный сигнал с прямого выхода блока 7 сравнения поступает на формирователь 12. При этом формируется короткий единичный импульс, устанавливающий по S-входу RS-триг- гер 13 в единичное состояние. Единичный сигнал с прямого выхода RS-триггера подается на вход разрешения счета счетчика 15, который под действием синхроимпульсов, поступающих на его счетный вход, начинает изменять свое состояние, формируя на адресном входе блока 16 последовательность значений адреса. По этим- адресам с выхода блока 16 через регистр 17 счина адресный вход демультиплексора 10, обеспечивая последовательную установку в инверсное состояние соответствующих Т-триггеров блока 14 (че- 5 рез информационные входы блока 14).

Одновременно со считыванием из бло ка 16 последнего кода номера канала блока 14 с управляющего выхода бло0 ка 16 памяти снимается единичный сиг- нал признака окончания группы. Этот сигнал поступает на вход формирователя 18, с выхода которого короткий импульс поступает через элемент ИЛИ I1

5 на вход сброса регистра 17, R-вход RS-триггера 13 и на вход установки счетчика 6.. При этом происходит обнуление регистра 17, установка в ноль RS-триггера и установка триггеров счетчика 6 в 1. Сигналы с прямого и инверсного выходов RS-триггера 13 соответственно останавливают изменение состояний счетчика 15 и переводят в следующее состояние счетчик 8. При этом из блока 9 памяти считывается следующий код временного интервала it. Этот код сравнивается блоком 7 сравнения- с кодами, сменяющимися на выходах счетчика 6 под действием синхросигналов с. выхода делителя 4.

Следующий синхроимпульс, появляю-- щийся на выходе - элемента 5 задержки, поступает на синхровход блока 14 каналов формирования кодов, обеспечивая перепись информации из его входных Т-триггеров в выходные D-тригге0

5

0

5

ры, с выходов которых сформированные сигналы поступают на шины 27 устройства.

Если временной интервал ut разбит на несколько интервалов, то для кажого из полученных интервалов, исключая последний, из блока 16 памяти считывается группа кодов, состоящая из одного нулевого кода. Под действием этого кода, переписанного в ре- - гистр 17, демультиплексор 10 изменяет свой нулевой выход, неподключенный к информационным входам блока 14 каналов формирования кодов.

Таким образом, переключений на шинах 27 устройства в точках раэбие ния временного интервала it на части не происходит.

С каждым синхроимпульсом, появляющимся на счетном входе счетчика 6,

этот счетчик увеличивает значение ко- IQ ные входы первого блока памяти соеди- да на его выходе на единицу. При достижении кодом значения, на единицу меньшего величины кода д t, блок 7 сравнения устанавливает этот факт и цикл подготовки и изменение значе- 5 НИИ сигналов на шинах 27 повторится.

нены с выходами первого счетчика адреса, счеткйш вход которого соединен с инверсным выходом RS-триггера, прямой выход которого соединен с входом разрешения счета второго счетчика адреса, выходы которого соединены с адресными входами второго блока паЗавершается работа устройства при установке в 1 старшего разряда счетчика 8. Это значение поступает.через дополнительный, элемент ИЛИ 19 на R-вход D-триггера 2, переходящего при этом в нулевое состояние, останавливающее прохождение импульсов генератора 1 через элемент И 3. Завершение работы устройства может быть также

достигнуто подачей 1 на R-вход D-триггера через шину 21 останова и дополнительный элемент ИЛИ 19.

Формула изобретения

Устройство для формирования кодовых последовательностей, содержащее генератор импульсов, D-триггер, элемент И, делитель частоты, элемент задержки, счетчик импульсов, блок сравнения, первый счетчик адреса, первый блок памяти, демультиплексор, элемент ИЛИ, первый формирователь коротких импульсов, RS-триггер, блок каналов формирования кодов, второй счетчик адреса, второй блок памяти, регистр, второй формирователь коротких импульсов, выход генератора импульсов соединен с первым входом элемента И, второй вход которого соединен с выходом D-триггера, выход элемента И соединен со счетным входом второго счетчика адреса и входом делителя частоты, установочный вход которого объединен с установочным входом второго счетчика адреса и шиной начальной установки устройства, выход делителя частоты соединен с входом элеменвниипи

Заказ 4931/54 Тиррж 900

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

та задержки, выход которого соединен со счетным входом счетчика импульсов и синхровходом блока каналов формирования кодов, информационные выходы счетчика импульсов соединены с первыми входами блока сравнения, вторые входы которого соединены с выходами первого блока памяти, адресные входы первого блока памяти соеди-

нены с выходами первого счетчика адреса, счеткйш вход которого соединен с инверсным выходом RS-триггера, прямой выход которого соединен с входом разрешения счета второго счетчика адреса, выходы которого соединены с адресными входами второго блока па

информационными входами регистра, выходы которого соединены с адресными входами демультиплексора, выходы которого соединены с соответствующими информационными входами блока каналов формирования кодов, а инверсный

вход управления демультиплексора соединен с инверсным выходом блока сравнения, прямой выход которого через первый формирователь коротких импульсов соединен с S-входом RSтриггера, R-вход которого соединен с входом сброса регистра и выходом элемента ИЛИ, первый вход которого соединен с входом сброса блока каналов формирования кодов и входом сброса первого счетчика адреса, второй вход элемента ИЛИ соединен с выходом второго формирователя коротких им- пульсов, вход которого соединен с управляющим выходом второго блока

памяти, синхровход D-триггера соединен с шиной запуска устройства, отличающееся тем, что, с целью повышения надежности и расширения функциональных возможностей

за счет увеличения длины формируемых кодовых последовательностей, в него введен дополнительный элемент ИЛИ, вход которого соединен с выходом старшего разряда первого счетчика адреса, а выход соединен с R-входом D-триггера, вход сброса первого счетчика адреса соединен с шиной началь- нрй установки устройства, а установочный вход счетчика соединен с выходом элемента ИЛИ.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1499438A2 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1439744A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1406736A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Устройство для формирования кодовых последовательностей | 1983 |

|

SU1231584A1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство отсчета интервалов времени | 1982 |

|

SU1103228A1 |

| Устройство отсчета интерваловВРЕМЕНи | 1979 |

|

SU807286A1 |

Изобретение может быть использовано в системах автоматической обработки данных. Цель изобретения - повышение надежности и расширение 26 2 функциональных возможностей устройства. Устройство содержит генератор 1 импульсов, D-триггер 2, элемент И 3, делитель частоты, элемент 5 задержки, счетчик 6 импульсов, блок 7 сравнения и счетчики 8 и 15 адреса. Кроме того, устройство включает блоки 9 и 16 памяти, демультиплексор 10, элемент ИЛИ 11, формирователи 12 и 18 коротких импульсов, RS-триггер 13, блок 14 каналов формирования кодов и регистр 17. Введение элемента ИЛИ 19 и образование новых функциональных связей увеличивают длину формируемых кодовых последовательностей. I ил. 27 со 4 ел со ISO гчэ

| Устройство для формирования кодовых последовательностей | 1983 |

|

SU1231584A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-15—Публикация

1986-04-16—Подача