Изобретение относится к вычислительной технике и может быть использовано для преобразования биполярного трехуровневого последовательного кода в однополярный параллельный код.

Известно устройство для преобразования последовательного кода в параллельный [1], содержащее два делителя напряжения, два усилителя-ограничителя, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента НЕ, регистр сдвига, два триггера и два элемента И. К недостаткам этого устройства следует отнести большое количество сопровождающих обмен интерфейсных сигналов, что затрудняет использование его при больших расстояниях между передатчиком и приемником информации. Кроме того, увеличение помехоустойчивости канала связи достигается посредством запроса повторения передаваемого слова, что снижает скорость передачи данных.

Наиболее близким по технической сущности и достигаемому результату к заявляемому техническому решению является преобразователь последовательного кода в параллельный [2], выбранный за прототип. Устройство-прототип содержит согласующий трансформатор, первый и второй однополупериодные выпрямители, сдвиговый регистр, счетчик, дешифратор, первый элемент И, счетчик по модулю два. Эти признаки совпадают с существенными признаками заявляемого технического решения. Устройство содержит также первый и второй элементы задержки, второй элемент И, третий элемент И, триггер, элемент ИЛИ, первый и второй таймеры. К недостаткам прототипа следует отнести наличие элементов задержки на время То/4, где To - время битового интервала, что требует паузы в передачи информационных сигналов на время, >То/4 для восстановления устройства. Кроме того, искажение формы (разрывы), как в первой четверти, так и во второй четверти информационного сигнала То вследствие воздействия помех приводит к неправильному декодированию информации (многократной записи в сдвиговый регистр). Случайный импульс на входе устройства запускает второй таймер и время восстановления устройства составляет тогда целое слово n.To, где n - число информационных бит в слове.

Целью изобретения является повышение скорости передачи информации за счет сокращения времени передачи информационного бита.

Кроме того, предложенное техническое решение позволяет снизить вероятность потери информации в канале связи за счет повышения помехозащищенности устройства. Это является дополнительной целью изобретения.

Поставленная цель достигается тем, что устройство преобразования последовательного кода в параллельный содержит согласующий трансформатор, первый и второй однополупериодные выпрямители, сдвиговый регистр, счетчик, счетчик по модулю два, дешифратор и элемент И, выход которого является выходом устройства. Вход согласующего трансформатора является входом устройства. Первый и второй выходы согласующего трансформатора соединены с входами соответственно первого и второго однополупериодных выпрямителей. Первые входы счетчика и счетчика по модулю два объединены соответственно с входами С и сдвигового регистра, группа выходов которого является группой выходов устройства. Группа выходов счетчика соединена с группой входов дешифратора, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом счетчика по модулю два. Эти признаки являются общими для прототипа и заявляемого технического решения.

Устройство содержит также первый и второй элементы НЕ, первый, второй, третий, четвертый и пятый элементы ИЛИ-НЕ, таймер, первый и второй D-триггеры, R-входы которых объединены со вторыми входами счетчика и счетчика по модулю два и соединены с выходом таймера. Выход первого однополупериодного выпрямителя через первый элемент НЕ соединен с первым входом первого элемента ИЛИ-НЕ, первым входом таймера и первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом первого D-триггера, прямой выход которого соединен со вторым входом первого элемента ИЛИ-НЕ, выход которого соединен с S-входом второго D-триггера, прямой выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, выход которого соединен с S-входом первого D-триггера. Выход второго однополупериодного выпрямителя через второй элемент НЕ соединен со вторым входом третьего элемента ИЛИ-НЕ, вторым входом таймера и первым входом четвертого элемента ИЛИ-НЕ, второй вход которого объединен с D-входом сдвигового регистра и соединен с инверсным выходом второго D-триггера, С-вход которого объединен с С-входом первого D-триггера, первым входом счетчика и соединен с выходом пятого элемента ИЛИ-НЕ, первый и второй входы которого соединены с выходами соответственно второго и четвертого элементов ИЛИ-НЕ. Эти признаки присущи только заявляемому устройству.

Совокупность приведенных выше существенных признаков по сравнению с прототипом позволяет в два раза сократить паузу между информационными импульсами, т. о. на 25% сократить время битового интервала, что эквивалентно повышению скорости передачи данных на 25%.

Наличие двух D-триггеров, кроме того, делает устройство нечувствительным к искажениям (провалам до уровня 0 вольт) формы сигнала в первой трети битового интервала, обусловленным воздействием помех, так как такие искажения не приводят к изменению состояния D-триггеров. Наличие двухвходового таймера, анализирующего временной интервал, представленный уровнем 0 вольт на входе устройства, ко всему прочему, позволяет переводить устройство в исходное состояние, если указанный временной интервал превышает времени Т3 (где Т - время битового интервала), что исключает накопление информации в сдвиговом регистре по шумам и по сравнению с прототипом в n раз сокращает время восстановления устройства после воздействия импульсной помехи, где n-число бит в слове. Указанные особенности приводят к снижению вероятности потери информации в канале связи.

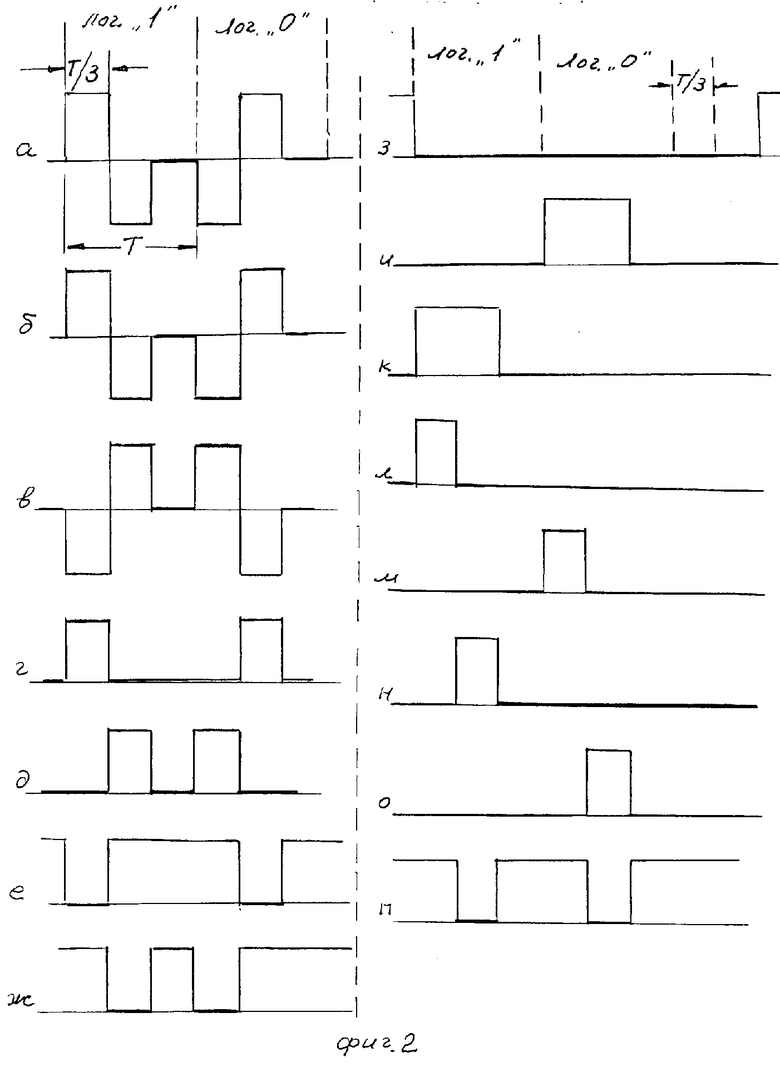

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - временные диаграммы работы устройства.

Устройство преобразования последовательного кода в параллельный содержит согласующий трансформатор 1, первый и второй однополупериодные выпрямители 2 и 3, первый и второй элементы НЕ, 4 и 5, первый элемент ИЛИ-НЕ 6, таймер 7, первый D-триггер 8, второй D-триггер 9, второй элемент ИЛИ-НЕ 10, третий элемент ИЛИ-НЕ 11, четвертый элемент ИЛИ-НЕ 12, пятый элемент ИЛИ-НЕ 13, сдвиговый регистр 14, дешифратор 15, счетчик 16, счетчик 17 по модулю два, элемент И 18, вход 19 устройства, группу 20 выходов устройства, выход 21 устройства. Первый выход согласующего трасформатора 1 через первый однополупериодный выпрямитель 2 и первый элемент НЕ 4 соединен с первым входом первого элемента ИЛИ-НЕ 6, первым входом таймера 7 и первым входом второго элемента ИЛИ-НЕ 19, второй вход которого соединен с инверсным выходом первого D-триггера 8, прямой выход которого соединен с вторым входом первого элемента ИЛИ-НЕ 6, выход которого соединен с S-входом второго D-триггера 9, прямой выход которого соединен с первым входом третьего элемента ИЛИ-НЕ 11, выход которого соединен с S-входом первого D-триггера 8.

Второй выход согласующего трансформатора 1 через второй однополупериодный выпрямитель 3 и второй элемент НЕ соединен с вторым входом третьего элемента ИЛИ-НЕ 11, вторым входом таймера 7 и первым входом четвертого элемента ИЛИ-НЕ 12. Первый и второй входы пятого элемента ИЛИ-НЕ 13 соединены с выходами соответственно второго элемента ИЛИ-НЕ 10 и четвертого элемента ИЛИ-НЕ 12. Выход пятого элемента ИЛИ-НЕ 13 соединен с С-входами первого и второго триггеров 8 и 9, первым входом счетчика 16 и С-входом сдвигового регистра 14. Инверсный выход второго D-триггера 9 соединен со вторым входом четвертого элемента ИЛИ-НЕ 12, D-входом сдвигового регистра 14 и первым входом счетчика 17 по модулю два. Выход таймера 7 соединен с R-входами первого и второго D-триггеров 8 и 9, вторым входом счетчика 16 и вторым входом счетчика 17 по модулю два. Группа выходов счетчика 16 соединена с группой входов дешифратора 15, выход которого соединен с первым входом элемента И 18, второй вход которого соединен с выходом счетчика 17 по модулю два. Вход согласующего трансформатора 1 является входом 19 устройства. Группа выходов сдвигового регистра 14 является группой 20 выходов устройства, выход элемента И 18 является выходом 21 устройства.

Устройство преобразования последовательного кода в параллельный работает следующим образом.

В исходном состоянии при включении питания и отсутствии сигналов на входах элементов НЕ 4 и 5 таймер 7 принудительно удерживает D-триггеры 8 и 9, а также счетчики 16 и 17 в состоянии установки в ноль. Информационное слово подается на вход 19 устройства последовательно бит за битом, начиная с первого разряда слова. При этом входные сигналы определяются тремя уровнями напряжения: +U, -U, 0. Информация в течение бит-интервала Т представляется двухполярными импульсами (фиг.2, а). Информационный бит "1" кодируется как последовательное состояние уровней +U, -U, 0. Информационный бит "0" кодируется как последовательное состояние уровней -U, +U, 0. Двухполярный импульс бита подается на вход согласующего трансформатора 1, который формирует на его первом выходе прямое значение напряжения входного бита, а на втором выходе - инверсное значение напряжений входного бита (фиг.2, б, в). Эти напряжения подаются на входы соответствующих однополупериодных выпрямителей 2 и 3, которые формируют на своих выходах однополярные импульсы длительностью Т/3, причем импульс на выходе первого однополупериодного выпрямителя 2 соответствует положительной части входного бита, а импульс на выходе однополупериодного выпрямителя 3 - отрицательной части бита (фиг.2, г, д). С выходов однополупериодных выпрямителей 2 и 3 импульсы поступают на входы соответствующих элементов НЕ 4 и 5, выходые сигналы которых приведены на фиг. 2, е, ж соответственно. Эти сигналы поступают на соответствующие входы таймера 7 и переводят его на время, большее Т/3, в состояние, при котором его выходной сигнал (фиг.2, з) разрешает прием входных информационных сигналов D-триггерам 8 и 9, счетчикам 16 и 17.

Кроме того, сигнал с выхода первого элемента НЕ 4 поступает на первые входы первого и второго элементов ИЛИ-НЕ 6 и 10, а сигнал с выхода второго элемента НЕ 5 поступает на входы третьего и четвертого элементов ИЛИ-НЕ 11 и 12. На второй вход первого элемента ИЛИ-НЕ 6 поступает потенциал логического "0" с прямого выхода D-триггера 8 (фиг.2, и), а на другой вход третьего элемента ИЛИ-НЕ 11 поступает потенциал логического "0" с прямого выхода D-триггера 9 (фиг. 2, к). На выходах элементов ИЛИ-НЕ 6 и 11 происходит выделение сигналов, управляющих S-входами D-триггеров 9 и 8 (фиг.2, л, м) соответственно. При поступлении бита, соответствующего логической "1", первым формируется сигнал, поступающий на S-вход D-триггера 9, что приводит к его синхронному переключению в состояние логической "1". Это переключение запрещает прохождение импульса на S-вход D-триггера 8. Переключение D-триггера 9 разрешает прохождение импульса с первого входа четвертого элемента ИЛИ-НЕ 12 на его выход (фиг.2, н) и далее через соответствующий вход пятого элемента ИЛИ-НЕ 13 на его выход (фиг.2, п). Сигнал с выхода элемента ИЛИ-НЕ 13, воздействуя на синхронные входы D-триггеров 8 и 9 и сдвигового регистра 14, обеспечивают запись логической "1" в регистр 14 и сброс D-триггеров 8 и 9 в исходное нулевое состояние.

При поступлении на вход устройства бита информации, соответствующего логическому "0", первым формируется сигнал, поступающий на S-вход D-триггера 8, что приводит к его переключению в состояние логической "1". Это переключение запрещает прохождение импульса на S-вход D-триггера 9 и разрешает прохождение импульса с первого входа второго элемента ИЛИ-НЕ 10 на его выход (фиг.2, о) и далее через соответствующий вход пятого элемента ИЛИ-НЕ 13 на его выход (фиг.2, п). Сигнал с выхода элемента ИЛИ-НЕ 13 обеспечивает запись логического "0" в сдвиговый регистр 14 и сброс D-триггеров 8 и 9 в исходное нулевое состояние.

Таким образом происходит накопление и сдвиг кодовых импульсов в сдвиговом регистре 14.

Кроме того, импульсы с выхода пятого элемента ИЛИ-НЕ 13 подаются на счетный вход счетчика 16. Состояние счетчика 16 декодируется дешифратором 15. При достижении в счетчике 16 числа, разного числу бит входного слова, на выходе дешифратора 15 фоpмируется сигнал, соответствующий приему всех бит входного слова. Этот сигнал подается на соответствующий вход элемента И 18.

Информационные импульсы с инверсного выхода D-триггера 9 подаются на счетный вход счетчика 17 по модулю два. При поступлении в течение информационного слова нечетного числа логических "1", конечное состояние счетчика 17 будет единичным, что соответствует правильному приему слова. При поступлении в течение информационного слова четного числа логических "1", конечное состояние счетчика 17 будет нулевым, что соответствует неправильному приему слова.

При наличии сигналов исправности с выходов счетчика 17 и дешифратора 15, поступающих на соответствующие входы элемента И 18, на его выходе формируется сигнал исправности, который подается на выход 21 устройства и свидетельствует о правильности преобразования кода. Пользователь считывает параллельный код с выходов 20 сдвигового регистра 14 при наличии сигнала на выходе элемента И 18.

По окончании преобразования входного слова отсутствие информации на входе 19 устройства в течение времени ≥ Т/3 переводит таймер 7 в состояние, при котором он устанавливает в ноль D-триггеры 8, 9, счетчики 16 и 17. Устройство готово к преобразованию следующего слова.

При наличии ошибок, сбоев, потери бит и т.п. счетчики 16 и 17 не формируют сигналы правильности преобразования, элемент И 18 остается закрытым и сигнал исправности на выходе 21 устройства отсутствует.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1229968A1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Генератор кодового слова | 1989 |

|

SU1755269A1 |

| ДЕКОДЕР ФАЗОМОДУЛИРОВАННОГО СИГНАЛА | 2010 |

|

RU2453991C1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1453598A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Селектор импульсов заданной кодовой комбинации | 1987 |

|

SU1457169A1 |

Устройство преобразования последовательного кода в параллельный относится к вычислительной технике и может быть использовано для преобразования биполярного трехуровневого последовательного кода в однополярный параллельный код. Изобретение позволяет повысить скорость передачи информации за счет сокращения времени передачи информационного бита. Для этого устройство содержит согласующий трансформатор, два однополупериодных выпрямителя, два элемента НЕ, два D-триггера, пять элементов ИЛИ - НЕ, таймер, счетчик, счетчик по модулю два, дешифратор, элемент И и сдвиговый регистр. Наличие двух D-триггеров и таймера позволяет снизить вероятность потери информации в канале связи за счет повышения помехозащищенности устройства. 2 ил.

УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащее согласующий трансформатор, вход которого является входной шиной, а первый и второй выходы соединены с входами соответственно первого и второго однополупериодных выпрямителей, счетчик и счетчик по модулю два, счетные входы которых объединены соответственно с C- и D-входами сдвигового регистра, инверсные выходы которого являются первой выходной шиной устройства, второй выходной шиной которого является выход элемента И, первый и второй входы которого соединены соответственно с выходом счетчика по модулю два и выходом дешифратора, входы которого соединены с соответствующими выходами счетчика, вход установки в "0" которого объединен с одноименным входом счетчика по модулю два и подключен к выходу таймера, отличающееся тем, что в него введены два элемента НЕ, пять элементов ИЛИ - НЕ, два D-триггера, R-входы которых соединены с выходом таймера, выход первого однополупериодного выпрямителя через первый элемент НЕ соединен с первым входом первого элемента ИЛИ - НЕ, первым входом таймера и первым входом второго элемента ИЛИ - НЕ, второй вход которого объединен с D-входом сдвигового регистра и соединен с инверсным выходом первого D-триггера, прямой выход которого соединен с вторым входом первого элемента ИЛИ - НЕ, выход которого соединен с S-входом второго D-триггера, прямой выход которого соединен с первым входом третьего элемента ИЛИ - НЕ, выход которого соединен с S-входом первого D-триггера, выход второго однополупериодного выпрямителя через второй элемент НЕ соединен с вторым входом третьего элемента ИЛИ - НЕ, вторым входом таймера и первым входом четвертого элемента ИЛИ - НЕ, второй вход которого соединен с инверсным выходом второго D-триггера, C-вход которого объединен с C-входом первого D-триггера, счетным входом счетчика и подключен к выходу пятого элемента ИЛИ - НЕ, первый и второй входы которого соединены с выходами соответственно второго и четвертого элементов ИЛИ - НЕ.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1229968A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-12-15—Публикация

1992-12-28—Подача