ел

00

о

Сл

о

Изобретение относится к вычисли- тельной технике и может быть использовано в отказоустойчивых системах обработки данных.Целью изобретения является повышение быстродействия.

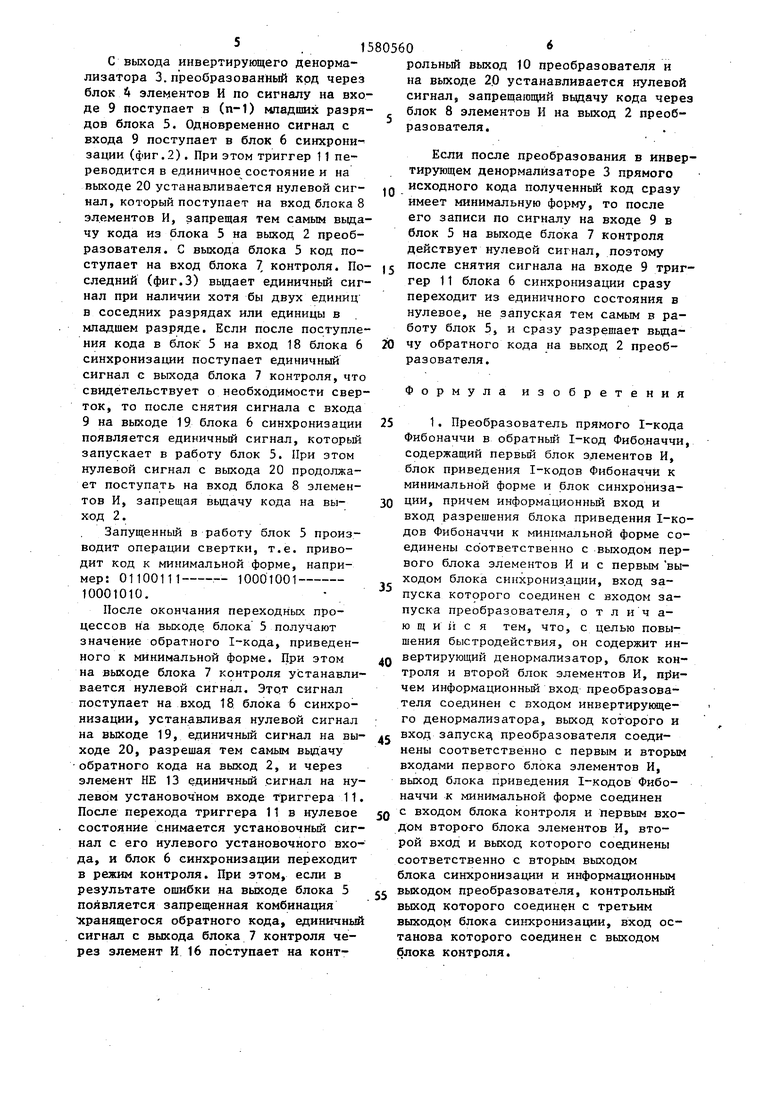

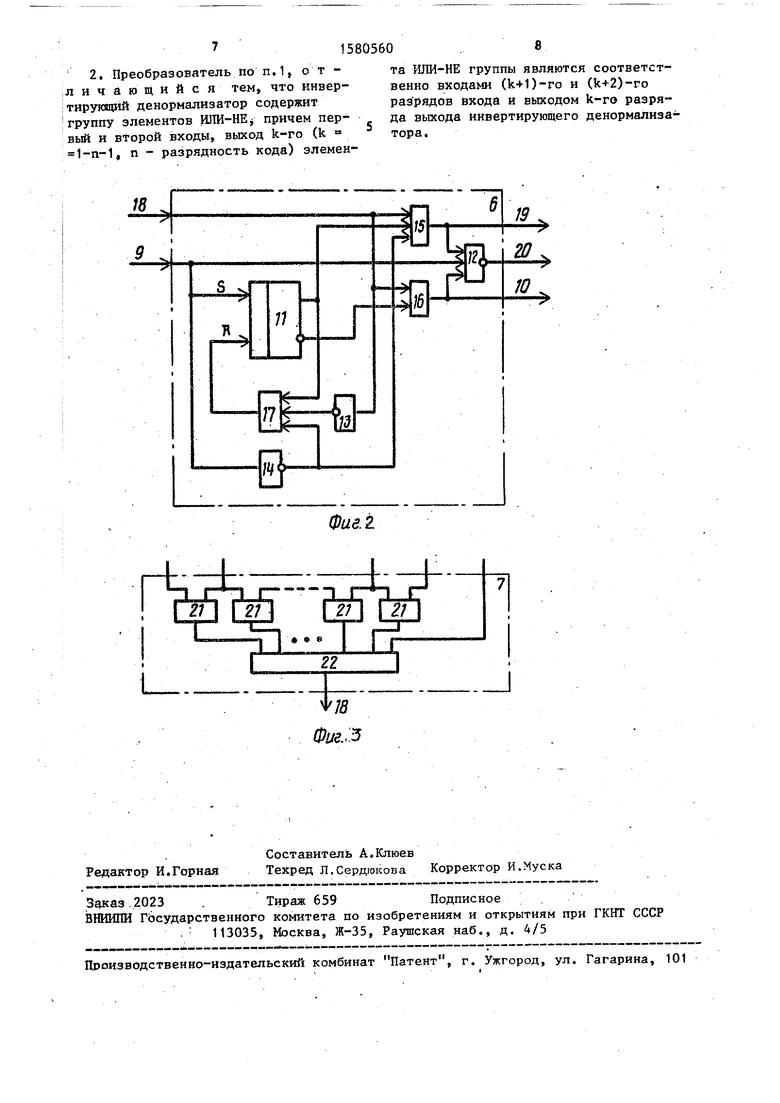

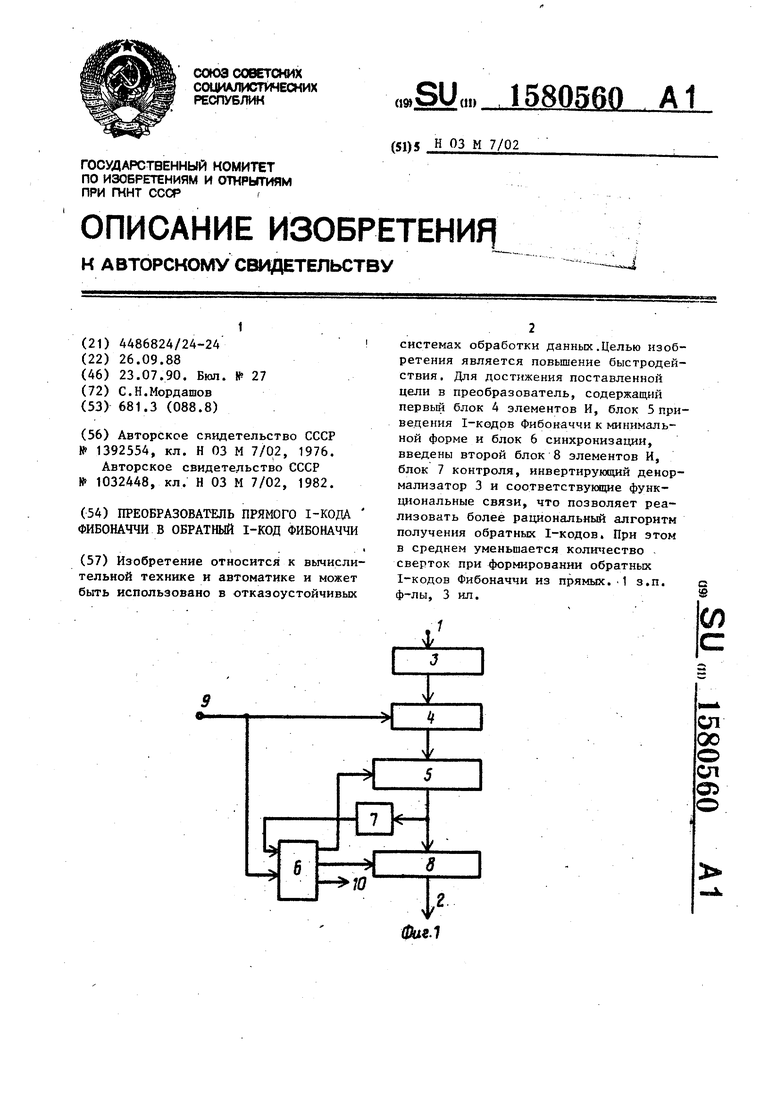

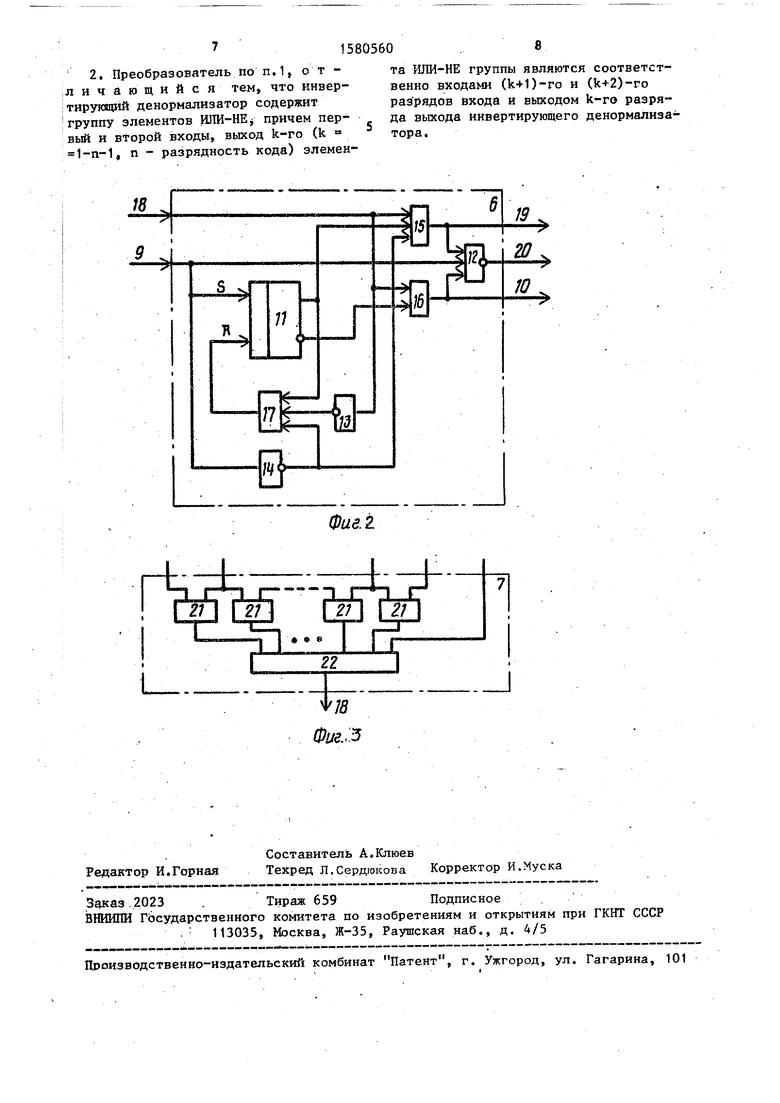

,На фиг.1 представлена схема преобразователя прямого I-кода Фибоначчи в обратный I-код Фибоначчи; на фиг.2- JQ схема блока, синхронизации; на фиг.З - схема блока контроля.

Преобразователь (фиг.1) содержит информационный вход 1 преобразова- теля, информационный выход 2 преобра- 15 зователя, инвертирующий денормализа- тор 3, первый блок 4 элементов И, блок

5приведения I-кодов Фибоначчи к минимальной форме, блок 6 синхронизации, блок 7 контроля, второй блок 8 20 элементов И, вход 9 запуска преобразователя и контрольный выход 10 преобразователя.

Блок 6 синхронизации (фиг.2) содержит триггер 11, элемент ШТИ-НЕ 12, 25 первый 13 и второй 14 элементы НЕ, с первого по третий элементы И 15-17, вход 18 останова блока 6 синхронизации, первый 19 и второй 20 выходы блока 6 синхронизации, причем вход зо запуска блока 6 синхронизации соединен с входом установки в единицу триггера 11 и с входом второго элемента НЕ 14, вход 18 останова блока

6синхронизации соединен с первыми входами первого 15 и второго 16 элементов И и входом первого элемента НЕ 13,- прямой выход триггера 11 соединен со вторым входом элемента И 15 и первым входом третьего элемента И 17, до выход которого соединен с входом установки в нуль триггера 11, инверсный выход которого соединен со вторым йх.одом элемента И 16, выход элемента

И 15, вход запуска блока 6 синхрони- 45 зации и выход элемента И 16 соединены соответственно с входами элемента ИЛИ-НЕ 12, выходы элемента И 15, элемента ИЛИ-НЕ 12 и элемента И 16 являются соответственно выходами с перво- JQ го по третий блока 6 синхронизации, выход элемента НЕ 13 соединен со вторым входом элемента И 17, третий вход которого соединен с третьим входом элемента И 15 и выходом элемента НЕ 14

Блок 7 контроля (фиг.З) содержит группу элементов И 21 и элемент ИЛИ 22, причем входы разрядов со второго по (п-1)-й входа блока 7 контроля соединены соответственно с первыми входами элементов И 21 группы, выходы которых и вход первого разряда входа блока 7 контроля соединены соответственно с входами элемента ИЛИ 22, выход которого является выходом блока 7 контроля, входы разрядов с третьего по n-й входа которого соединены соответственно со вторыми входами элементов И 21 группы (п - разрядность кода).

Инвертирующий денормализатор 3 предназначен для частичной развертки прямого I-кода Фибоначчи и выдачи инверсных (п-1) младших разрядов развернутого таким образом кода через первый блок 4 элементов И на входы (п-1) младших разрядов блока 5. Инвертирующий денормализатор 3 может быть реализован посредством группы из (п-1) элемента ИЛИ-НЕ.

Блок 5 приведения I-кодов Фибоначи к минимальной форме предназначен ля осуществления операции свертки I-кодов. Блок 6 синхронизации предназначен для управления работой преобразователя. Блок 7 контроля предназначен для контроля кода в блоке 5 на минимальность формы, т.е. на отсутствие одновременно двух единиц в соседних разрядах или единицы в младшем разряде. Совместно с блоком 7 контроля блок 6 синхронизации опредеяет момент окончания сверток, а таке формирует сигнал ошибки при ее возникновении во время хранения кода в блоке 5.

Блок 8 элементов И предназначен ля разрешения выдачи обратного кода, приведенного к минимальной форме, и прекращения его выдачи во время свертки или- при возникновении ошибки при хранении в блоке 5 свернутого кода.

Преобразователь работает следующим образом (фиг.1).

Исходный прямой I-код Фибоначчи с входа 1 поступает в инвертирующий денормализатор 3, где происходит частичная развертка исходного кода, т.е. каждая единица в k-м разряде представляется двумя единицами в (k-1)-M и (k-2)-M разрядах, и инвертирование (п-1) разрядов развернутого таким образом кода. Например: 10010000 - прямой код, 1101100 - развернутый код, 001001-1 - проинвертированный развернутый код.

С выхода инвертирующего денорма- лизатора 3.преобразованный код через блок $ элементов И по сигналу на входе 9 поступает в (п-1) младших разрядов блока 5. Одновременно сигнал с входа 9 поступает в блок 6 синхронизации (фиг.2). При этом триггер 1 1 переводится в единичное состояние и на выходе 20 устанавливается нулевой сигнал, который поступает на вход блока 8 элементов И, запрещая тем самым выдачу кода из блока 5 на выход 2 преобразователя. С выхода блока 5 код поступает на вход блока 7 контроля. Последний (фиг.З) выдает единичный сигнал при наличии хотя бы двух единиц в соседних разрядах или единицы в младшем разряде. Если после поступления кода в блок 5 на вход 18 блока 6 синхронизации поступает единичный сигнал с выхода блока 7 контроля, что свидетельствует о необходимости сверток, то после снятия сигнала с входа 9 на выходе 19 блока 6 синхронизации появляется единичный сигнал, который запускает в работу блок 5. При этом нулевой сигнал с выхода 20 продолжает поступать на вход блока 8 элементов И, запрещая выдачу кода на выход 2.

Запущенный в работу блок 5 производит операции свертки, т.е. приводит код к минимальной форме, например: 0110011110001001

10001010.

После окончания переходных процессов на выходе блока 5 получают значение обратного I-кода, приведенного к минимальной форме. При этом на выходе блока 7 контроля устанавливается нулевой сигнал. Этот сигнал поступает на вход 18 блока 6 синхронизации, устанавливая нулевой сигнал на выходе 19, единичный сигнал на выходе 20, разрешая тем самым выдачу обратного кода на выход 2, и через элемент НЕ 13 единичный сигнал на нулевом установочном входе триггера 11. После перехода триггера 11 в нулевое состояние снимается установочный сигнал с его нулевого установочного входа, и блок 6 синхронизации переходит в режим контроля. При этом, если в результате ошибки на выходе блока 5 появляется запрещенная комбинация хранящегося обратного кода, единичный сигнал с выхода блока 7 контроля через элемент И 16 поступает на конт0

5

0

5

0

5

0

S

0

5

рольный выход 10 преобразователя и на выходе 20 устанавливается нулевой сигнал, запрещающий выдачу кода через блок 8 элементов И на выход 2 преобразователя.

Если после преобразования в инвертирующем денормализаторе 3 прямого исходного кода полученньй код сразу имеет минимальную форму, то после его записи по сигналу на входе 9 в блок 5 на выходе блока 7 контроля действует нулевой сигнал, поэтому после снятия сигнала на входе 9 триггер 11 блока 6 синхронизации сразу переходит из единичного состояния в нулевое, не запуская тем самым в работу блок 5, и сразу разрешает выдачу обратного кода на выход 2 преобразователя.

Формула изобретения

1. Преобразователь прямого 1-кода Фибоначчи в обратный I-код Фибоначчи, содержащий первый блок элементов И, блок приведения I-кодов Фибоначчи к минимальной форме и блок синхронизации, причем информационньй вход и вход разрешения блока приведения 1-ко- дов Фибоначчи к минимальной форме соединены соответственно с выходом первого блока элементов И и с первым выходом блока синхронизации, вход запуска которого соединен с входом запуска преобразователя, о т л и ч а- ю щ и и с я тем, что, с целью повышения быстродействия, он содержит инвертирующий денормализатор, блок контроля и второй блок элементов И, чем информационный вход преобразователя соединен с входом инвертирующего денормализатора, выход которого и вход запуска, преобразователя соединены соответственно с первым и вторым входами первого блока элементов И, выход блока приведения I-кодов Фибоначчи к минимальной форме соединен с входом блока контроля и первым входом второго блока элементов И, второй вход и выход которого соединены соответственно с вторым выходом блока синхронизации и информационным выходом преобразователя, контрольный выход которого соединен с третьим выходом блока синхронизации, вход останова которого соединен с выходом блока контроля.

2. Преобразователь по п.1, отличающийся тем, что инвертирующий денормализатор содержит группу элементов ИЛИ-НЕ, причем первый и второй входы, выход k-го (k 1-n-1, n - разрядность кода) элемента ИЛИ-НЕ группы являются соответственно входами (k-H)-ro и (k+2)-ro разрядов входа и выходом k-ro разряда выхода инвертирующего денормалиэа- тора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

| Устройство для приведения р-кодов фибоначчи к минимальной форме | 1976 |

|

SU662930A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1983 |

|

SU1149262A1 |

| Устройство для преобразования формы кода Фибоначчи | 1987 |

|

SU1418910A1 |

| Устройство для приведения I-кодов фибоначчи к минимальной форме | 1981 |

|

SU1005024A1 |

| Устройство для приведения 1-кодов Фибоначчи к нормальной форме | 1981 |

|

SU1008728A1 |

| Устройство для приведения р-кодов Фибоначчи к минимальной форме | 1988 |

|

SU1547074A1 |

| Устройство для контроля 3-кода Фибоначчи | 1987 |

|

SU1478217A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано в отказоустойчивых системах обработки данных. Цель изобретения является повышение быстродействия. Для достижения поставленной цели в преобразователь , содержащий первый блок 4 элементов И, блок 5 приведения 1-кодов Фибоначчи к минимальной форме и блок 6 синхронизации, введены второй блок 8 элементов И, блок 7 контроля, инвертирующий денормализатор 3 и соответствующие функциональные связи, что позволяет реализовать более рациональный алгоритм получения обратных 1-кодов. При этом в среднем уменьшается количество сверток при формировании обратных 1-кодов Фибоначчи из прямых. 1 з.п.ф-лы, 3 ил.

Фиг. 2.

| Устройство для приведения кодов Фибоначчи к минимальной форме | 1986 |

|

SU1392554A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь прямого кода в обратный | 1982 |

|

SU1032448A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-09-26—Подача