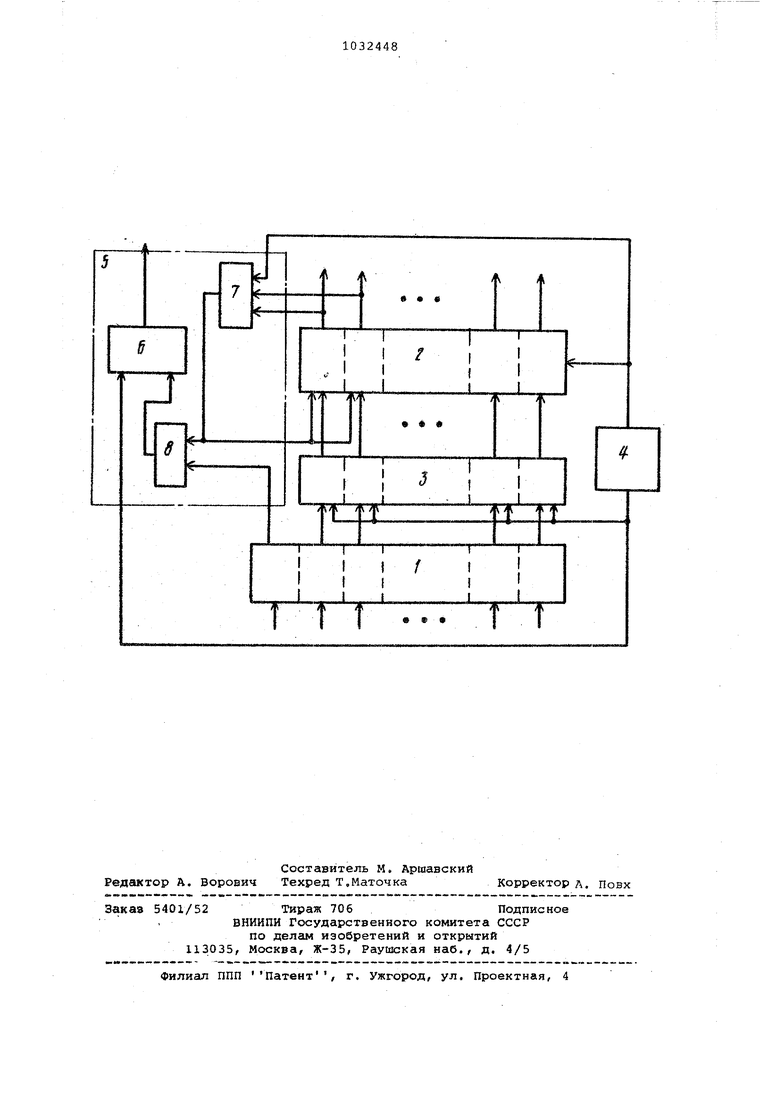

Изобретение относится к автоматике и вычислительной технике и может , быть использовано в процессорах отказоустойчивых вычислительных систем Известен преобразователь прямого двоичного кода в обратный, содержащий регистр, единичные входы и инверсные выходы которого являются соответственно входами и. выходами уст ройства 1} . Недостатком данного устройстаа является невозможность получения обратного . р-кода Фибоначчи из прямого р-кода. ; Наиболее близким к предлагаемому По технической сущности является пре Ьбразователь прямого кода в обратный содержащий ,v-разрядный регистр, пер Ьый и второй блоки приведения р-коitoB Фибоначчи к минимальной форме и распределитель импульсов, причем ед йичные выходы регистра соединены с информационными входами первого лоКа приведения, младшие (И-р) инверс Нне информационные выходы первого блока приведения соединены с младши ми (И-р) входами второго блока приведения, первый и второй выходы распределителя импульсов соединены Соответственно с управляющими входам Первого и второго блоков приведения L2 Недостатком данного устройства являются большие временные и аппара турные затраты для преобразования прямого Э -кода Фибоначчи в обратный 3-код, Что связано с осуществлением сначала полной развертки исходного Прямого .3-кода в первом блоке приведения, а затем осуществлением инвертирования (И-1) младших разрядов и передачей.полученного кода во .второй блок приведения, где происхо дит его свертка. Цель изобретения - повышение быст родействия и упрощение преобразователя . . Поставленная цель достигается: Тем, что в преобразователь прямо го кода в обратный, содержащий и -разрядный регистр, информационные входы которого являются входами преобразователя, распределитель импульсов, блок приведения кодов Фибоначчи к минимальной форме, управляющий вход которого соединен с первым выходом распределителя импульсов, введены группа из (rt-l)-ro элемента И и блок определения старшего разряда, вход сброса которого соединен с вторым выходом распределителя импульсов и Первыми входами элементов И группы, вторые входы которых соединены соответственно с выходами {И-1) млад щих разрядов У1 -разрядного регистра, выход старшего разряда которого соединен с входом установки блока определения старшего разряда, тактовый вход которого соединен с первым выходом распределителя импульсов, первый и второй информационные входы блока определения старшего разряда соединены соответственно с выходами двух старших разрядов блока приведения роДов Фибоначчи к минимальной форме, первые информационные входы которого соединены соответственно с выходами элементов И группы, а выходы являются информационными выходами преобразователя, знаковый выход -которого соединен с выходом знака блока определения старшего разряда, выход коррекции которого соединен с вторыми информационными входами двух старших разрядов блока приведения кодов Фибоначчи к минимальной форме, Кроме того, блок определения старшего разряда содержит триггер, первый и второй элементы И, первые входы которых являются соответственно тактовым и установочным входами блока определения старшего разряда,знаковый выход которого соединен с выходом триггера, вход сброса которого является входом сброса блока определения старшего разряда, первый и второй информационные входы которого соединены соответственно с вторым и третьим входами первого,элемента И/ выход которого являетсявыходом коррекции блока определения старшего разряда и соединен с вторым входом второго элемента И, выход которого соединен с установочным входом триггера. На чертеже приведена блок-схема преобразователя. Преобразователь содержит и -разрядный регистр 1,-блок 2 приведения кодов Фибоначчи к минимальной форме, группу 3 элементов И, распределитель 4 импульсов, .блок 5 определения старшего разряда, который содержит триггер б и элементы И 7 и 8, Регистр 1 предназначен для приема прямого 3 -кода Фибоначчи, подлежащего преобразованию в обратный 3-код, и выдачи инверсных значений принятого кода через элементы И группы 3 на входы блока 2 приведения кодов Фибоначчи к минимальной форме, который предназначен для осуществления операций свертки J -кодов и содержит (И-1) схем свертки ЦзЗ. Распределитель 4 импульсов предназначен для управления работой преобразователя. Влек 5 определения старшего разряда позволяет определить зннчение старшего разряда обратного tJ-кода Фибоначчи на основании анализа содержимого двух старших разрядов блока 2 йс аршёгс разряда регистра 1. ОН состоит из триггера 6 и элементов И 7 и 8,

Преобразователь работает следующим образом.

Исходный прямой .J-К.ОД Фибоначчи поступает в л-разрядный регистр 1. По первому управляющему сигналу от распределителя 4 импульсов поступающему на элементы и группы 3, осуществляется, выдача в соответствующие разряды блока 2 инверсных эн чениЙ th-i) младших разрядов регистра 1 и одновременно устанавливается в нулевое значение триггер б блока 5 определения старшего разряда. По второму сигналу от распределителя 4 импульсов, поступающему на тактовый вход блока 2f происходит свертка -кода.

Если при этом выходы двух старших разрядов блока 2 оказываются в единичном состоянии то.тот же сигнал от распределителя 4 импульсов через элемент И 7, поступив на входы данных разрядов, устанавливает их в

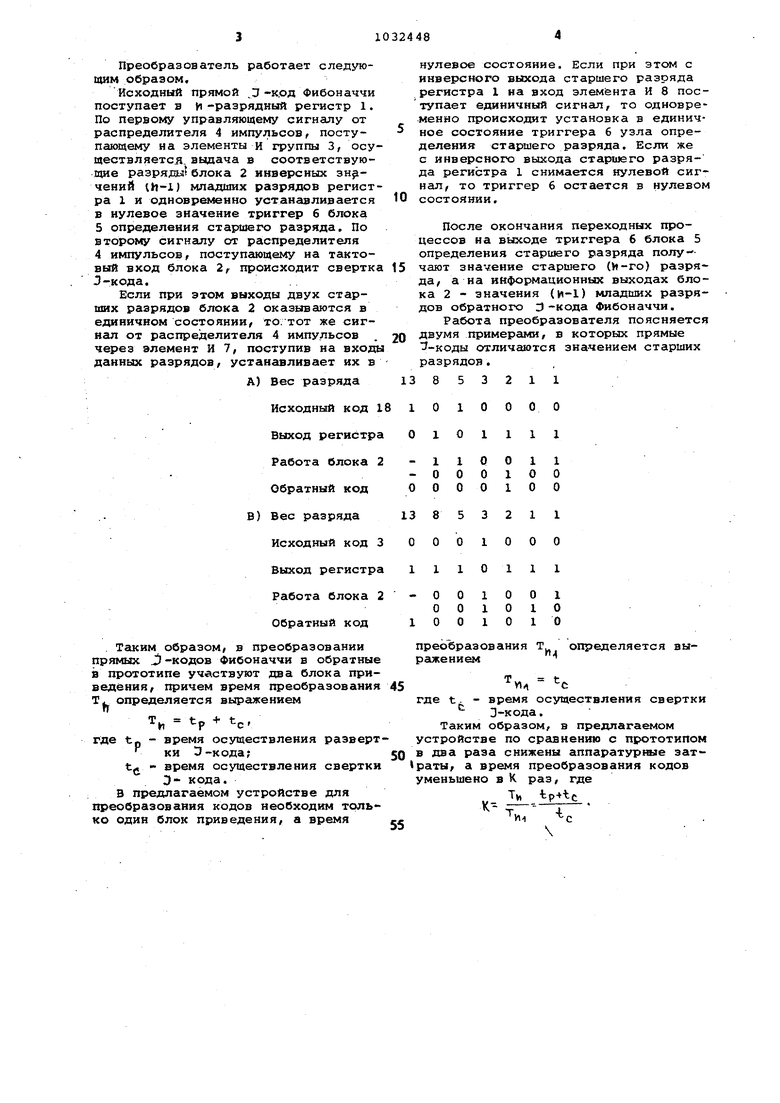

А) Вес разряда

Исходный код 18 1 О 1

010 13 8532 11 0001000

Выход регистра Работа блока 2

Обратный код

Таким образом/ в преобразовании прямых j-кодов Фибоначчи в обратные а прототипе участвуют два блока приведения, причем время преобразования Т. определяется выражением

tp + Ч,

где tp - время осуществления разверт ки Э-кода; t - время осуществления свертки

Э- кода.

В предлагаемом устройстве для преобразования кодов необходим только один блок приведения, а время

нулевое состояние. Если при этом с инверсного выхода старшего разряда регистра I на вход элемента И 8 поступает единичный сигнал, то одновременно происходит установка в единичное состояние триггера 6 узла определения старшего разряда. Если же с инверсного выхода старшего разряда регистра 1 снимается нулевой сигнал, то триггер 6 остается в нулевом состоянии.

После окончания переходных процессов на выходе триггера 6 блока 5 определения старшего разряда полу-чают значение старшего (И-го) разряда, а на информационных выходах блока 2 - значения (и-1) младших разрядов обратного d-кода Фибоначчи.

Работа преобразователя поясняется

двумя примерами, в которых прямые -коды отличаются значением старших разрядов.

8 5 3 2 1 1

-110011 -000100 0000100

о 1 1

о о о

О

1 о о

О

О

преобразования т определяется

раикением

t /

45«I -с

- время осуществления свертки

где t

З-кода.

Таким образом, в предлагаемом устройстве по сравнению с прототипом 50 в два раза снижены аппаратуршле зат(раты, а время преобразования кодов уменьшено в К раз, где

., К -г .1

HI

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь прямого кода Фибоначчи в обратный | 1984 |

|

SU1164891A1 |

| Устройство для нормализации кодов Фибоначчи | 1980 |

|

SU951291A1 |

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Электропривод постоянного тока | 1983 |

|

SU1100697A1 |

| Устройство для приведения 1-кода Фибоначчи к минимальной форме | 1989 |

|

SU1665515A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

1, ПРЕОБРАЗОВАТЕЛЬ ПРЯМОГО КОДА В ОБРАТНЫЙ, содержагадй И -разрядный регистр, информационные входы которого являются входами преобразователя, распределитель импульсов, блок приведения кодов Фибоначчи к минимальной форме, управляющий вход которого соединен с первым выходом распределителя импульсов, о т л и ч а ющ и и с я тем, что, с целью повышения быстродействия и упрощения в него введены группа из (n-D-ro элемента И и блок определения старшего разряда, вход сброса которого соединен с вторым выходом распределителя импульсов и первыми входами элементов И группы, вторые входы которых соединены соответственно с выходами (h-1) младших разрядов Л1 -разрядного регистра, выход старшего разряда когторого соединен с входом установки блока определения старшего разряда, .тактовый вход которого соединен с первым выходом распределителя импульсов, первый и второй информационные входы блока определения старшего разряда соединены соответственно с выходами двух старших разрядов блока приведения кодов Фибоначчи к минимальной форме, первые информационные входы которого соединены соответственно с выходами элементов И группы, а выходы являются информационными выходами преобразователя, знаковый выход которого соединен с выходом знака блока определения старшего разряда, выход коррекции которого соединен с вторыг и информационными входами двух старших разрядов блока приведения кодов Фибоначчи к минимальной форме. § 2. Преобразователь по п. 1, о тличающийся тем, что в нем блок определения старшего разряда содержит триггер, первый и второй элементы И, первые входы которых являются соответственно тактовым и установочным входами блока определения старшего разряда, знаковый выход которого соединен с выходом триггера, вход сброса которого является входом сброса блока определения старшего разряда, первый и второй информацией ные входы которого соединены соответственно с вторым и третьим входами первого элемента И, выход которого является выходом коррекции блока определения старшего разряда и соединен с вторым входом второго элемента И, выход которого соединен с установочным входом триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Папернов А.А | |||

| Логические основы ЦВТ | |||

| М,, Советское радио , 1972, с | |||

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь прямого кода в обратный | 1976 |

|

SU662931A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для приведения р-кодов фибоначчи к минимальной форме | 1976 |

|

SU662930A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-07-30—Публикация

1982-04-05—Подача