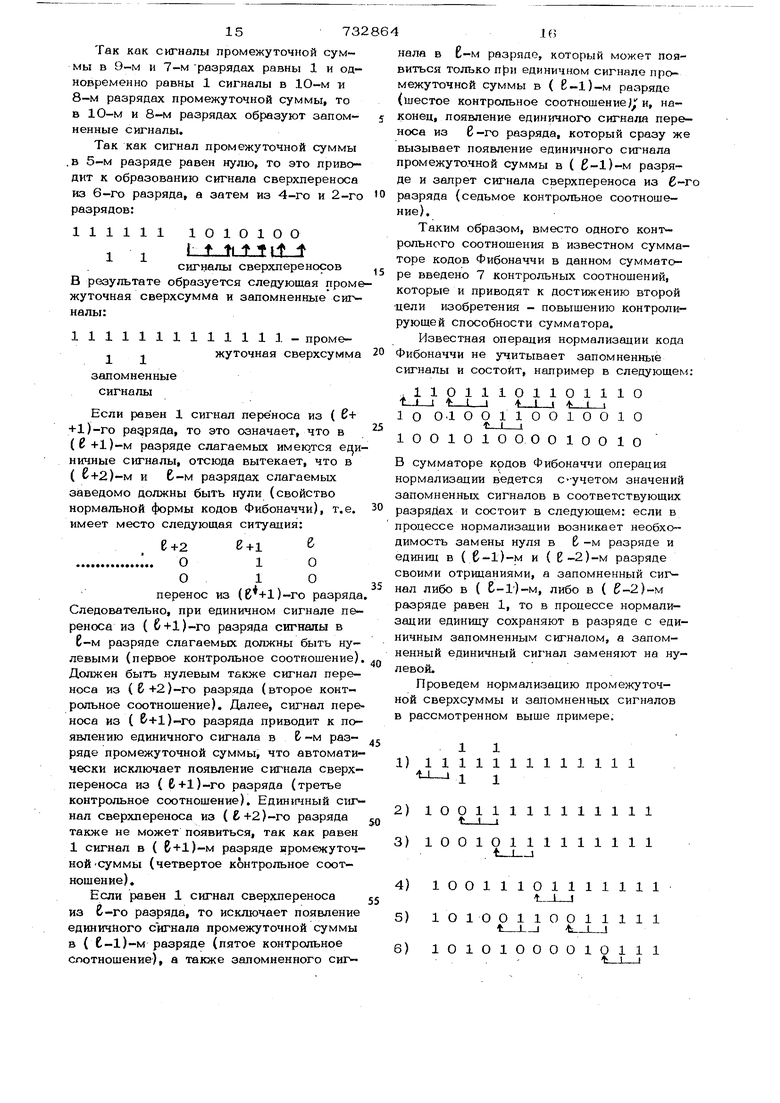

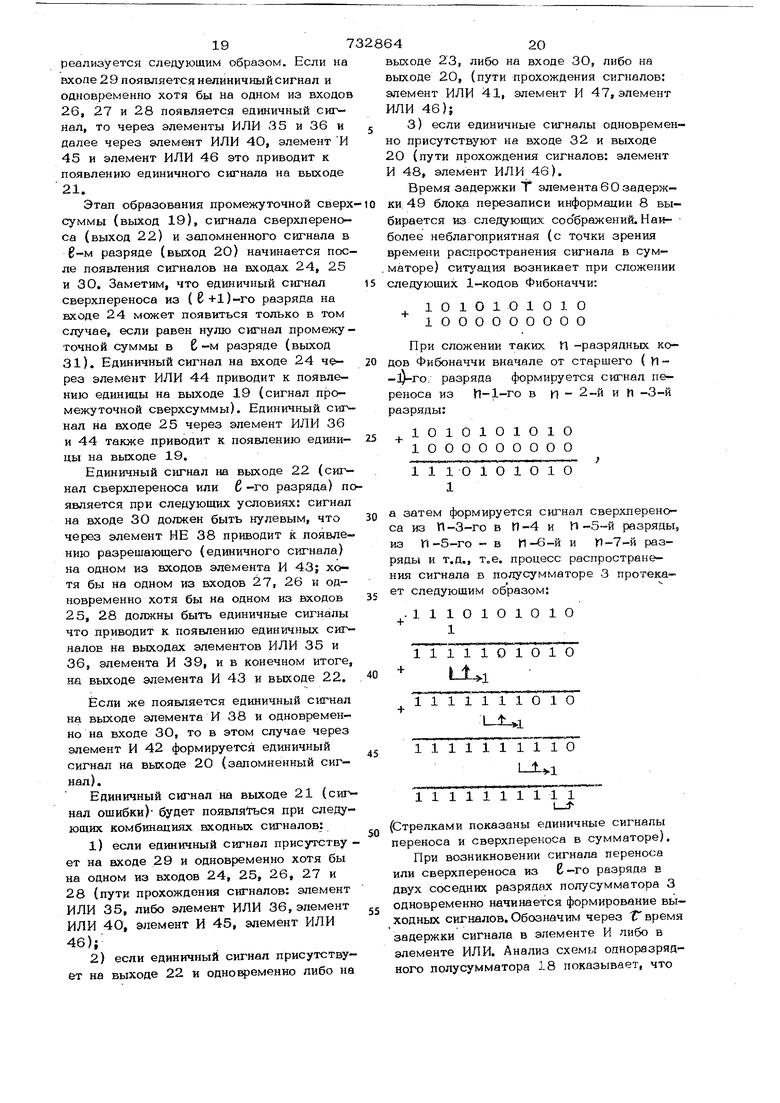

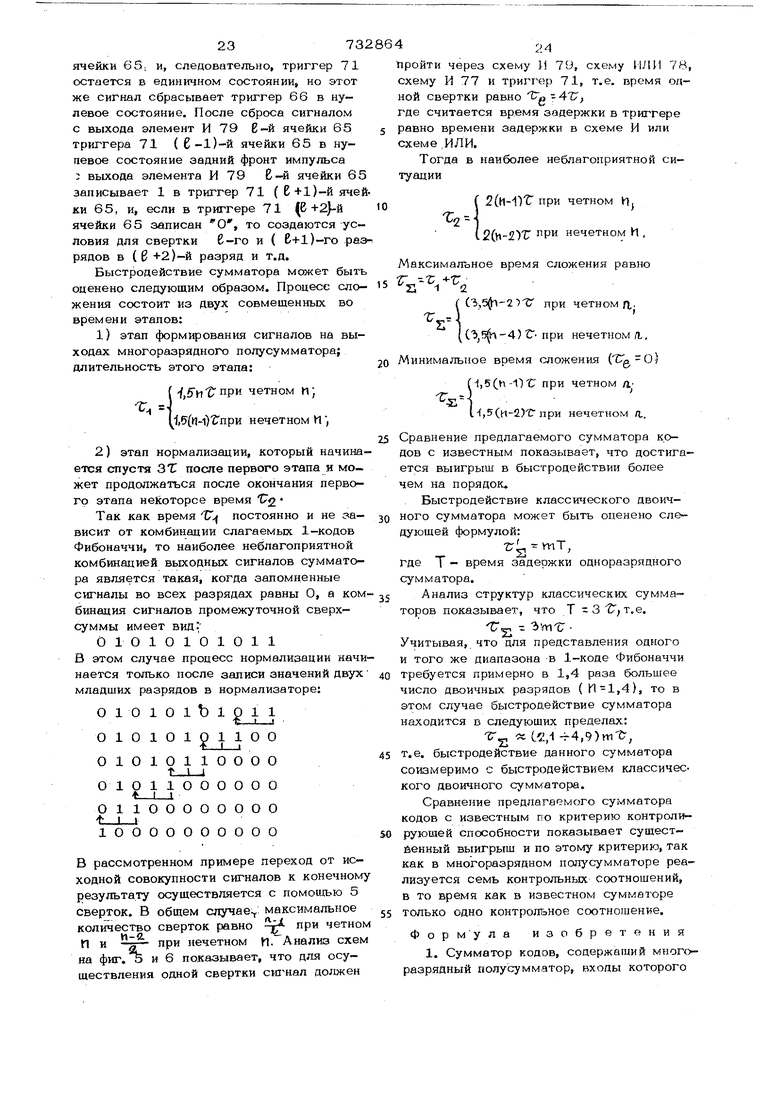

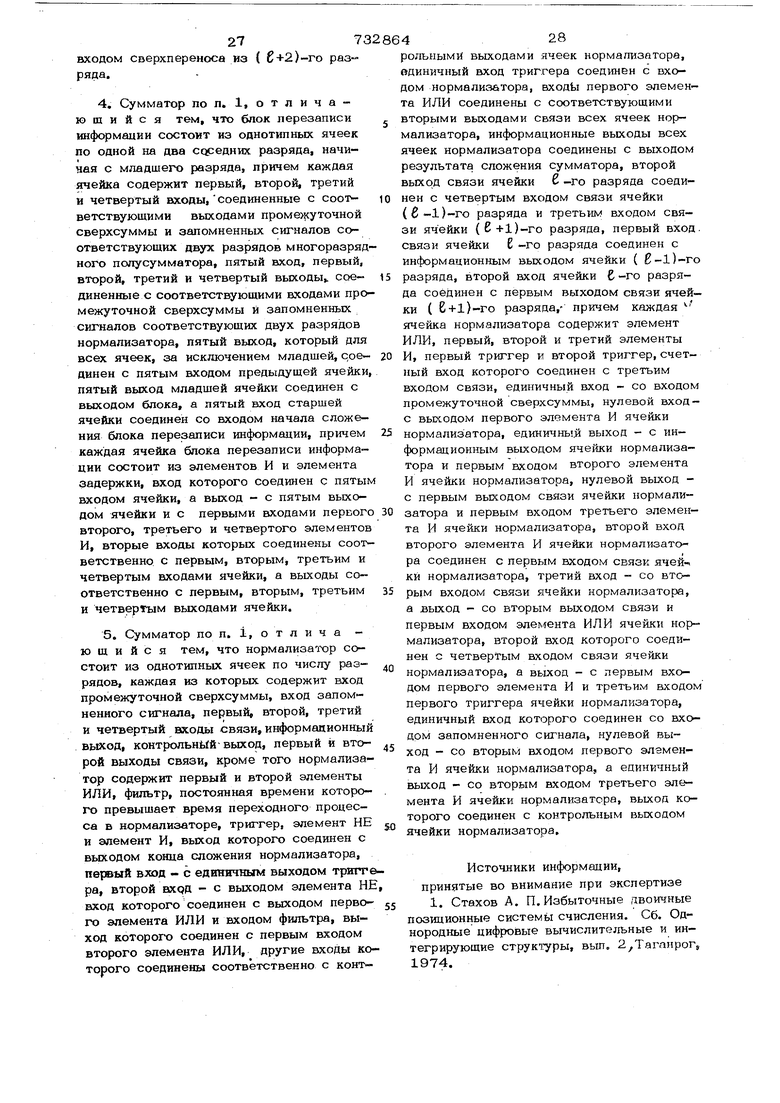

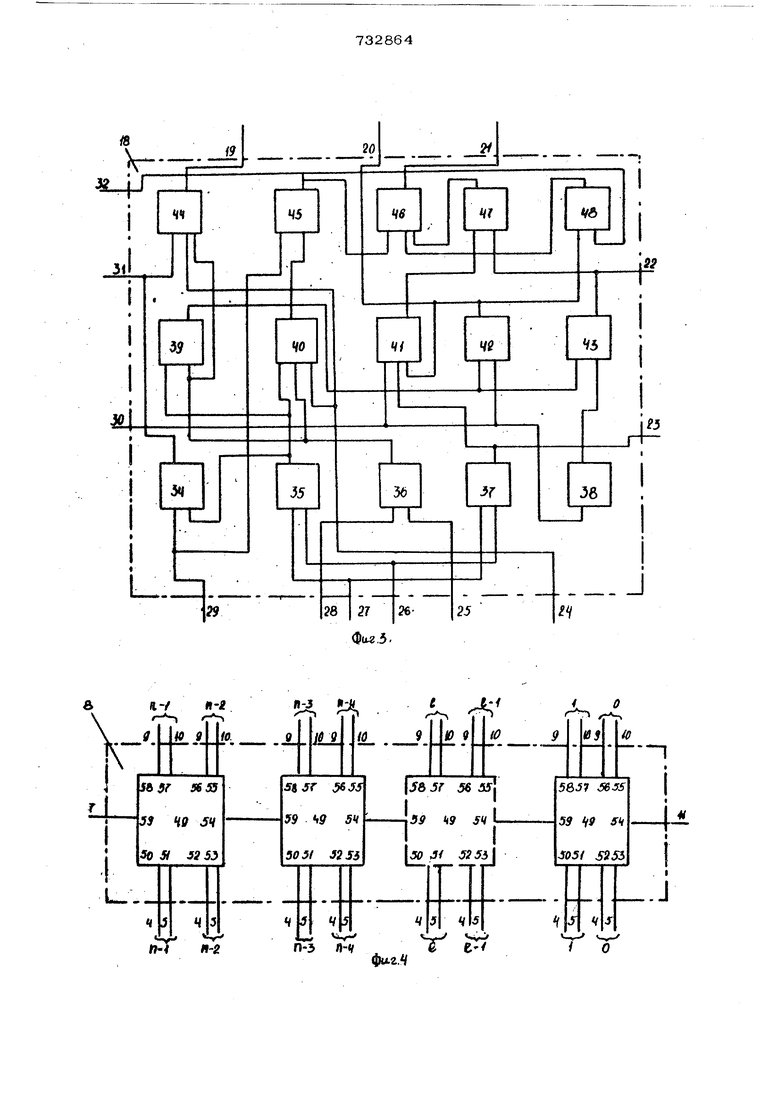

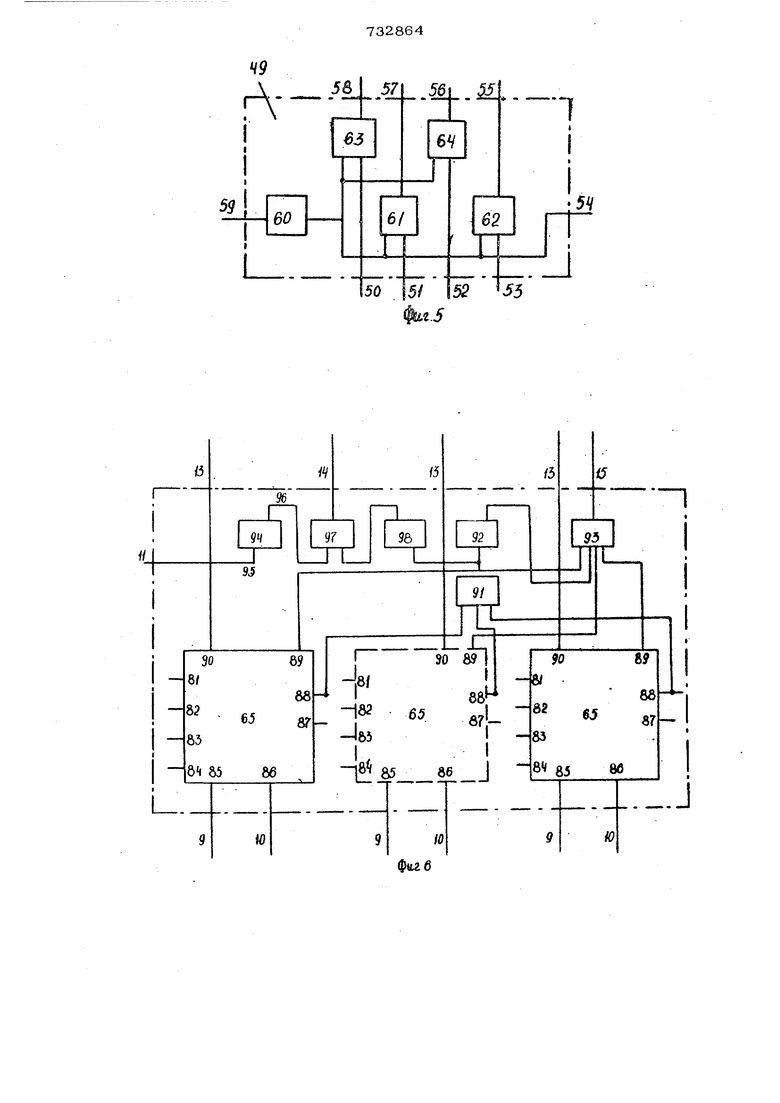

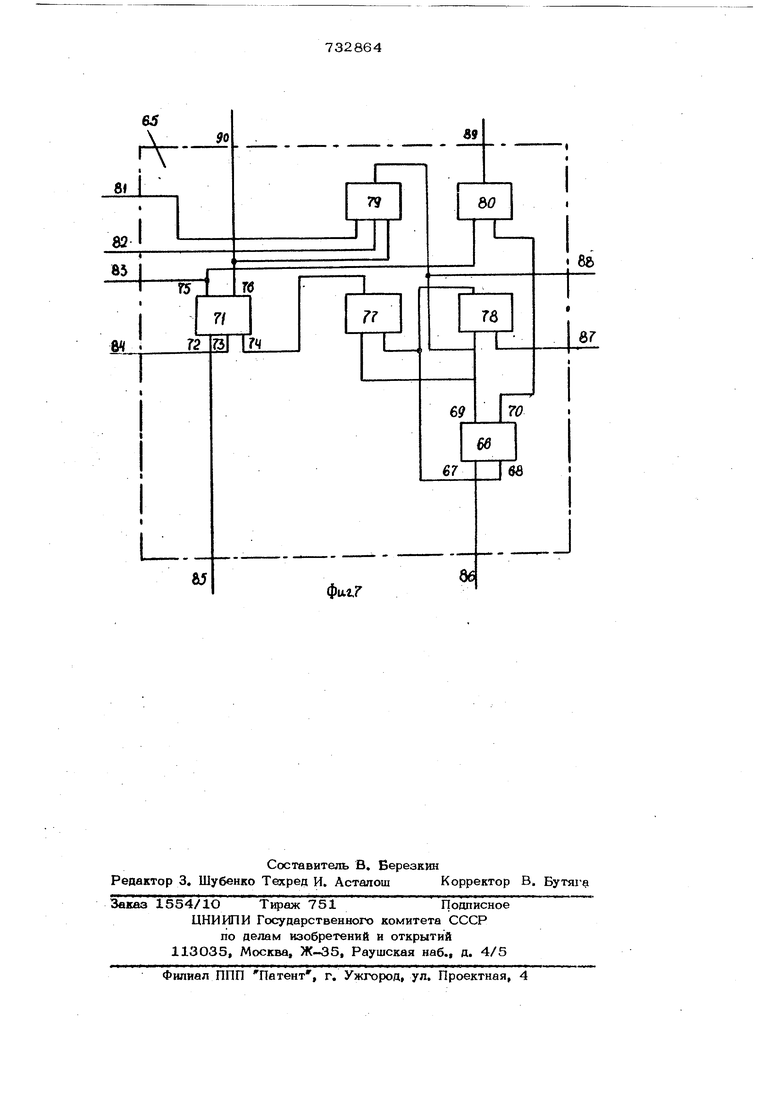

Изобретение относится к вычислительной технике и может быть использовано в арифметическом устройстве ЦВМ. Известны сумматоры кодов Фибоначчи, построенные на основе алгоритма сложения кодов Фибоначчи р., 2J и з. Недостатком таких сумматоров является большое количество 6 среднем циклов сложения, что приводит к снижению быстродействия сумматора. Наиболее близким к предлагаемому является сумматор кодов Фибоначчи, содержащий многоразрядный полусумматор, входы которого соединены со входами слагаемых сумматора и элемент ИЛИ, выход которого подключен к контрольному выходу сумматора r4J. Недостатком такого сумматора являет- .ся большое количество в среднем циклов слсокения, что приводит к снижению быстродействия сумматора, и невысокая КОНТРролирующая способность сумматора, .так как в сумматоре проверяется только одно контрольное соотношение. Цель изобретения - повышение быстродействия сумматора и повышение контролирующей способности сумматора. Для достижения этой цели сумматор содержит нормализатор и блок перезаписи информации, входы которого соединены со входом начала сложения и выходами промежуточной сверхсуммы и запомненных сигналов многоразрядного полусумматора, а выходы - со входами нормализатора, выходы нормализатора соединены с выходами результата сложения сумматора, окончания сложения сумматора и первым входом элемента И ЛИ, второй вход которого подклк « чен к контрольному выходу мрогоразрядного полусумматора. Кроме этого многоразрядный полусумматор содержит П однотипных ояноразрядг ных полусумматоров { Я - количество разрядов) и элемент ИЛИ, выход которого подключен к контрольному выходу многоразрядного полусумматора, а входы - к контрольным выходам одноразрядных полусумматоров, входы слагаемых 6 -го од373поразрядного полусумматора ( С 1, ..., П ) подключены ко входам 2 -го разряда многоразрядного полусумматора, выходы промежуточной с&ерхсуммы и запомненного сигнала Е-го одноразрядного полусум матора подключены к выходам 6-го разряда промежуточной сверхсуммы и запомненного сигнала многоразрядногчэ полусумматора, выход запомненного сигнала 6-го одноразрядного полусумматора подключен ко входу запомненного сигнала ( g-l)-ro одноразрядного полусумматора, выход пер носа 6 -го одноразрядного полусумматора подключен ко входу переноса ( -1)-го и { С-2)-го одноразрядных полусумматоров, входы переноса 6-го одноразрядного полусумматора подключены к: выходам переноса (6+1)-го и ( К+2)го однораз™ рядных полусумматоров, выход сверхпереноса -го одноразрядного полусумматора подключен ко входам сверхпереноса ( Е-1)-го и ( С-2)-го одноразрядных полусумматоров, входы сверхпереноса -го одноразрядного полусумматора подключены к выходам сверхпереноса {6+1)-го и ( 6+2)го одноразрядных полусумматоров, выход промежуточной суммы -го одноразрядного полусумматора подключен ко входу промежуточной суммы ( Б+1)-го одноразрядного полусумматора, вход промежу точной суммы 6-го одноразрядного полусумматора подключен к выходу промежуточной суммы ( 6-1)-го одноразрядного по лусумматора, выходы переноса, сверхпереноса и промежуточной суммы первого одноразрядного полусумматора подключены ко входам элемента ИЛИ, При этом одноразрядный полусумматор состоит из элементов И, ИЛИ и НЕ, причем, вход элемента НЕ соединен со входом промежуточной суммы и первыми вхо.дами первого элемента И и nepsoiTi элемента ИЛИ, а выход - с первым входом второго элемента И, второй вход которого соединен со вторым входом первого элемента И и выходом третьего элемента И, а выход - с выходом сверхпереноса и первым входом четвертого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - с входом второго элемента ИЛИ, выход -которого соединен с контрольным выxoacMvf, второй вход - с выходом пятого элемента И, а третий вход - с выходом . шестого элемента И, первый вход лоторого соединен с выходом третьего элемен- та ИЛИ, а второй вход - со входом пер-энсхза ЕЗ ( 6+1)-гчэ разряда и первым вхо4ДОМ четвертого элемента ИЛИ, выход которого соединен с выходом промежуточной суммы и первым входом пятого элемента ИЛИ, а второй вход - с первым входом третьего элемента И, первым входом третьего элемента ИЛИ и выходом шестого элемента ИЛИ, первый вход которого соединен со входом первого слагаемого и первым входом седьмого элемента И, а второй вход - со входом второго слагаемого и вторым входом седьмого элемента И, выход которого соединен с выходом переноса и вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, выходом запомненного и первым входом пятого элемента И, второй вход которого соединен с входом запомненного сигнала, вход сверхпереноса из ( 6+1)-го разряда соединен со вторым входом третьего элемента ИЛИ и вторым входом пятого элемента ИЛИ, выход которого соединен с выходом промежуточной сверхсуммы, а третий вход - со вторым входом третьего элемента И, третьим входом третьего элемента ИЛИ и выходом седьмого элемента ИЛИ, первый вход которого соединен со входом переноса из ( 6+2)-го разряда, а . второй вход со входом сверхпереноса из (0+2)-го разряда. Кроме roroj блок перезаписи информации состоит из однотипных ячеек по одной на два соседних разряда, начиная с младшего разряда, причем каждая ячейка содержит первый, второй, третий и четвертый Bxonbis соединенные с соответствующими вькодами промежуточной сверхсум- мы и запомненных сигналов соответствующих двух разрядов многоразрядного полусумматора, пятый вход, первый, второй, третий и четвертый выходы, соединенные с соответствуюшими входами промежуточной сверхсуммы и запомненных сигналов соответствующих двух разрядов нормализатора, пятый выход, который для ячеек, за исключением младшей, соединен с пятым входом предыдущей ячейки, пятый выход младшей ячейки соединен с выходом блока, а пятый кход старшей ячейки соединен со входом .начала сложения блока перезаписи информации, причем каждая ячейка блока перезаписи информации состоит из элементов И и элемента задержки, вход которого соединен с пятым входом ячейки, а выход - с пятым выходом 5гчейки - и с первыми входами первого, второго, третьего и четвертого элементов И, вторые входы которых соедияены соответственно с первым, вторым, третьим и четвертым входами ячейки, а выходы со -ответственно с первым, вторым, третьим и четвертым выходами ячейки. Кроме того, нормализатор состоит из однотипных ячеек по числу разрядов, каждая из которых содержит вход промежуточной сверхсуммы, вход запомненного сигнала, первый, второй, третий и четвертый входы связи, информационный вы- ход, контрольный выход, первый и второй выходы связи, кроме того нормализатор содержит первый и второй элементы ИЛИ, фильтр, постоянная времени которого превышает время переходного процесса в нор мализатбре, триггер, элемент НЕ и элемент И, выход которого соединен с выходом конца сложения нормализатора, первый вход - с единичным выходом триггера, второй вход - с выходом элемента НЕ, вход которого соединен с выходом первого элемента ИЛИ и входом фильтра, выход которого соединен с первым входом второго элемента ИЛИ, другие входы которого соединены соответственно с контрольными выходами ячеек нормализатора, единичный вход трнгтера соединен с входом нормализатора, входы первого элемен та ИЛИ соединены с соответствующими вторыми вьгходами связи всех ячеек нормализатора, информационные выходы всех ячеек нормализатора соединены с выходом результата сложения сумматора, второй выход связи ячейки в-го разряда соеди - нен с четвертым входом связи ячейки (Е -1} -го разряда и третьим входом связи ячейки (В+1)-го разряда, первый вход связи 5гчейки 6 -го разряда соединен с информационным выходом ячейки ( 6-1)-го разряда, второй вход ячейки -го разряда соединен с первым выходом связи ячейки (В+1)-го разряда, причем каждая ячейка нормализатора содержит элемент ИЛИ, первый, второй и третий элементы И, первый триггер и второй триггер, счетный вход которого соединен с третьим входом связи, единичный вход - со входом промежуточной сверхсуммы, нулевой вход - с выходом первого элемента И ячейки нормализатора, единичный выход - с информационным выходом ячейки нормализатора и первым входом второго элемента И ячейки нормализатора, нулевой выход - с первым выходом связи ячейки нормализатора и первым входом третьего элемента И ячейки нормализатора, второй вход второго элемента И ячейки нормали затора соединен с первым входом связи чейки нормализатора, третий вход - с вторым входом связи ячейки нормализатора, а выход - со вторым выходом связи и первым входом элемента ИЛИ ячейки нормализатора, второй вход которого соединен с четвертым входом связи ячеКи нормализатора, а выход - с первым входом первого элемента И и третьим входом первого триггера ячейки нормализатора, единичный вход которого соединен со входом запомненного сигнала, нулевой выход - со вторым входом первого элемента И ячейки нормализатора, а единичный выход - со вторым входом третьего элемента И ячейки нормализатора, выход которого соединен с контрольным выходом ячейки нормализатора. На фиг, 1 приведена структурная схе- ма сумматора кодов Фибоначчи; на фиг, 2 - Схема многоразрядного полусумматора; на фиг. 3 - схема одноразрядного полусумматора на фиг. 4-схемаблока перезаписи информации; на фиг, 5 - схема ячейки блока перезаписи информации; на фиг. 6 - Схема нормализатора; на фиг, 7 - схема ячейки нормализатора. Сумматор кодов Фибоначчи содержит вход 1 первого слагаемого, вход 2 второго слагаемого, многоразрядный полусумматор 3, выход 4 промежуточной сверхсуммы, выход 5 запомненных сигналов, конт рольный выход 6 полусумматора 3, вход 7 начала сложения, блок 8 перезаписи информации, выход 9 промежуточной суммы ока 8 перезаписи информации, выход 10 запомненных сигналов блока 8 перезаписи информации, выход 11 сигнала окон чания процесса перезаписи информации, нормализатор 12, выход 13 результата сложения, выход 14 окончания сложения, контрольный выход 15 нормализатора 12, элемент ИЛИ 16, контрольный выход 17 сумматора. Входы многоразрядного полусумматора 3 соединены со входами 1 и 2 слагаемых, а выходы 4 промежуточной сверхсуммы и запомненных сигналов 5 подключены к входам 11 блока перезаписи информации, к которым также подключен вход 7 начала сложения. Выходы 9 промежуточной суммы и запомненных сигналов 10 и выход 11 сигнала окончания процесса перезаписи информации блока 8 перезаписи информации подключены ко входам нормализатора 12, имеющем выходы 13 результата сложения, окончания сложения 14 и контрольный выход 15. Контрольный выход 15 нормализатора 12 и контрольный выход 6 полусумматора 3 подклк 773чены ко входам элемента ИЛИ 16, выход которого подключен к контрольному выходу сумматора 17. Многоразрядный полусумматор 3$ содержит П ( h - количество разрядов) одноразрядных сумматоров 18; .6 - ый из которьи имеет ( Е-1. .... М ) выход 19 .промежуточной сверхсуммы, выход 2О- заломненного сигнала,, контрольный выход 21, выход 22 сверхпереноса, выход 23 переноса, вход 24 сверхпереноса из g + + 1-го разряда, вход 25 сверхпереноса из ( б + 2)-го разряда, ЕОСОДЫ 26 и 27 слагаемых, вход 28 переноса из ( 8+2)-го разряда, вход 29 переноса из ( 6+1-)-го разряда, вход ЗО промежуточной суммы, выход 31 промежуточной суммы, вход 32 запомненного сигнала. Многоразрядный полусумматор 3 содержит кроме того элемент ИЛИ 33. При этом выходы 19 всех одноразрядных полусумматоров 18 соединены с соответствующими выходами 4 многоразрядного полусумматора 3; выходы 2О всех одноразрядных полусумматоров 18 соединены с соответствующими выходами 5 мно 1Х)разрядного полусумматора 3; входы 26 и 27 всех одноразрядных полусумматоров 18 соединены с соответствующими входами 1 и 2 многоразрядного полусумматора 3; контрольные выходы 21 всех одноразрядных полусумматоров 18, а также выходы 2 О, 22, 23 и 31 одноразрядного полусумматора 18 младшего разряда соединены со входами элемента ИЛИ 33, выход которого соединен с контрольным выходом 6 многоразрядного полусумматора 3; выход 22 одноразрядного полусумматора 18 6-го разряда соединен со входом 24 одноразрядного полусумматора 18 ( е-1)-го разряда и входом 28 одноразрядного полусумматора 18 ( 2-2)-го разряда; вход 30 одноразрядного полусумматора 18 6-го разряда соединен с выходом 31 одноразрядного полусумматора 18 ( &-1)-го разряда; выход 2О одноразрядного полусумматора 18 6-го разряда соединен со входом 32 одноразрядного ( Е-1)-го разряда. Одноразрядный полусумматор 18, содержит элементы ИЛИ 34, 35 и 36, элемент И 37, элемент НЕ 38, элемент И 39, элементы ИЛИ 40 и 41, элементы И 42 и 43, элемент ИЛИ 44, элемент И 45, элемент ИЛИ 46, элементы И 47 и 48. При этом вход элемента НЕ 38 соедииен со входом ЗО промежуточной суммы 4 и первыми входами элементов ИЛИ 41 и 42, а выход - с первым входом элемента И 43, второй вход которого соединен со вторым входом элемента И 42 и выхо ° элемента И 39, а выход - с выходом 22 сверхпереноса и входом элемента ц 47, другой вход которого подключен к выходу элемента ИЛИ 41. Выход элемента И 47 подключен ко входу элемента ИЛИ 46, выход которого соединен с контрольным выходом 21, второй вход - с выходом элемента И 48, а третий вход с выходом элемента И 45, первый вход которого соединен с выходом элемента ИЛИ 40, а второй вход - со входом переноса из ( 6+1)-го р 1зряда 29 и первым входом элемента ИЛИ 34, выход которого соединен с выходом 31 промежуточной суммы и первым входом элемента ИЛИ 44, а второй вход - с первым входом элемента И 39, элемента ИЛИ 4О и выходом элемента ИЛИ 35. Входы элемента ИЛИ 35 соединен1з1 со входами 26 и 27 слагаемых, которые подключены так. входам элемента И 37, выход которого соединен с выходом 23 переноса и вторым входом элемента.ИЛИ 41, третий ход которого соединен с выходом элемента И 42, выходом 2 О запомненного сиг первым входом элемента И 48, второй вход которого соединен со входом запомненного сигнале 32. Вход сверхпереноса из (f+1)-го разряда 24 соединен со вторыми входами элементов ИЛИ Q 4, д элемента ИЛИ 44 подключен к выходу 19 промежуточной сверхсуммы, р соединен со вторым входом элемента И 39, тре.л.им входом элемен выходом элемента ИЛИ 36, первый вход которого соединен со входом 28 переноса из { б+2.)-го разряда, а второй вход - со входом 25 сверхпереноса из (б+2)-го разряда 25. Блок 8 перезаписи информации состоит из однотипных ячеек 49 каждая из которых связана с двумя разрядами многоразрядного полусумматора 3 и содержит входы 5О, 51, 52, 53 и 54, вьосоды 55, 56, 57,-58 и 59, элемент 60 задержки, элементы И 6-1, 62, 63 и 64. При этом входы 50, 51, 52 и 53 coeavr нены с соответствующими выходами 4 промежуточной сверхсуммы и запомненных сигналов 5 двух соседних разрядов многоразрядного полусумматора 3; выходы 55, 56, 57 и 58 соединены с выУ2Дами 9 промежуточной суммы и запом97ценных скгнапов соответствующих разрядов блока перезаписи информации 8f выход 54 П-ой ячейки 49 блока 8 перезаписи информации соединен со входом 59 VI -1-ой ячейки 49j выход 54 младшей.ячейки 49 соединен с выходом 11 сигнала окончания процесса перезаписи информации, вход 59 старшей ячейки подключен ко входу 7 начала сложения. Вход элемента 60 задержки подкгаочен ко входу 59 ячейки 49 а выход - к выходу 54 ячейки 49 и ко входам элементов И 61j 62, 63 и 64, вторые входы которых подключены соответственно ко входам 51, 53, 5О и 52 ячейки 49, а выходы - к выходам 57, 55, 58 и 56 ячейки 49. Нормализатор 12 содержит Я однотипных ячеек 6 5j каждая из которых Бключа ет первый триггер 66, с единичным и нулевым входами 67 и 68 и нулевым и единичным выходами 69 и 7О, второй триггер 71, с единичным входом 72, счетным входом 73 с запуском по заднему фронту нулевым входом 74, нулевым входом 75, единичным выходом 76, элемент И 77, элемент ИЛИ 78, элементы И 79 и 80; первый вход 81-связи, второй вход 82 свя зи, первый выход 83 связи, третий вход 84 связи, вход 85 промежуточной сверх- 0 суммы, вход 86 запомненного сигнала, четвертый вход 87 связи, второй вьосод 88 связи, контрольный выход 89, информационный выход 90. Кроме того, нормализатор 12 содержит элемент ИЛИ 91, фильтр 92, постоянная времени которого превышает время переходного процесса в нормализато- . ре 12, элемент ИЛИ 93, триггер 94, с единичным входом 95 и единичным 96, элемент И 97 и элемент НЕ 98. При этом в нормализаторе 12 второй выход 88 связи ячейки 65 6 -го разряда соединен с четвертым входом 87 связи ячейки 65 ( С-1)-го разряда, третьим входом связи 84 ячейки 65 ( 6+1)-го рааряда и одним лз входов элемента ИЛИ 91; первый вход 81 связи ячейки 65 f-ro разряда соединен с информационным выходом 9О ячейки 65 ( В-1)-го разряда; второй вход 82 связи ячейки 65 6го разряда соединен с первым выходом 83 связи ячейки 65 ( 6+1)-го разряда; вход 11 сигнала окончания процесса перезаписи информации соедшен с единичным входом 95 триггера 94, единичныйвыход 96 которого соединен с одним из входов элемента И 97; выход элемента ИЛИ 91 4 Соединен со входом элемента НЕ 98, выход которого через элемент И 97 соединен с выходом 14 окончания сложения. Выходы 88 всех ячеек нормализатора соединены через элемент ИЛИ В1 с фильтром 92 и далее через элемент ИЛИ 93 с контрольным выходом 15, Эта цепь соединений вьшопняет контрольные функции в нормализаторе. После нормализации на всех выходах 88 должны быть нулевые сигналы. Единичные сигналы на этих выходах появляются кратковременно, пока идет переходной процесс в нормализаторе. Фильтр 92 не пропускает кратковременные сигналы на выходах 88 на контрольный выход 15. Если же на одном из выходов 88 появляется устойчивый единичный сигнал, то это приводит к появлению сигнала на контрольном выходе 15, Выход элемента ИЛИ 91 соединен со входом элемента НЕ 98, а через элемент И 97 с выходом 14 окончания сложения. Эта цепь соединений вместе с триггером 94 и- входом 11 играет следующую роль. До тех пор, пока длится переходной.процесс в нормализаторе, на вьосоде элемента ИЛИ 91 будет единетный сигнал, который через элемент НЕ 96 запрещает появление единичного сигнала на выходе 14. Как только на входе 11 появляется единичный сигнал (что свидетельствует об окончании первого этапа и перезаписи информации в нормализатор 12), он приводит к переходу триггера 94 в единичное состояние и появлению разрешающего сигнала на соответствующем входе элемента И 97. После окончания переходного процесса в нормализаторе на выходе 14 появляется единичный сигнал. При устойчивом отказе нормализатора 12 на выходе 15 единичный (разрешающий) сигнал появиться не может. В каждой ячейке нормализатора 65 триггер 71 своим счетным входом 73 подключен к третьему входу 84 связи, единичным входом 72 - ко входу 85 промежуточной сверхсуммы, нулевым входом 74 - к выходу элемента И 77. Единичный выход 76 триггера 71 подключен к инфopмaциoннo fy выходу 9О и к входу элемента И 79, а нулевой выход 75 - к первому выходу 83 связи и входу эяемента И 80, другой вход которохх) подключен к единичному выходу 70 триггера 66, а выход - к контрольному выходу 89. Второй и третий входы элемента И 79 цодключены соответственно к первом и второму входам 81 и 82 связи, а выход ко второму выходу 88 связи и входу элемента ИЛИ 78, другой вход которого соедш1ен с четвертым входом 87. связи, а выход - со входом элемента И 77 и нулевым входом 68 триггера 66, единичный вход 67 которого соединен со входом 86 запомненного сигнала, а нулевой выход 69 - с другим входом элемента И 77. Существо алгоритма сложения кодов Фибоначчи состоит в следующем. Слагаемые числа представляются в ви де нормальных кодов Фибоначчи (в нормальном коде Фибоначчи две единицы под ряд в коде не встречаются) и затем над нормальными кодами Фибоначчи осуществляются следующие операции. 1. Образование промежуточной суммы переносов, запомненных сигналов и сигна лов контроля сложения в каждом разряде, Сигнал 6-го разряда промежуточной сум мы и сигналы перецрсов из -го разряда в ( Б-1)ь1й и ( 6-2)-и разряды образуются на основе следующей таблицы сло жения одноразрядных чисел в коде Фибоначчи. О + О О 0+ 0 1 1+ 0 1 1 + 1 111 В указанном алгоритме сложения сигнал переноса из -го разряда в ( 6-1)-й разряд сразу же помещается в ( Е-1-)й разряд промежуточной суммы, а сигнал переноса в ( 2 )-й разряд является запомненным сигналом в (&-2)-м разряде. Таким образом, в процессе сложения в каждом разряде ( 6-м) анализируются четыре сигнала: сигналы в & -м разряде слагаемых и сигналы переноса из ( +1)-го и ( 6+2)-го разрядов в 6 -и разряд. При этом одновременно вьшолняется четыре операции: а)операция образования сигнала промежуточной суммы. Сиг-нал промежуточной суммы в -м разряде принимается равном 1, если равен 1 хотя бы один из сигналов в 0-м разряде слагаемых или сигнал переноса из ()-го разряда, к нулю в противном случае; б)операцш образования сигнала пере носа, вз 6-го разряда. Сигнал переноса из -го разряда принимается равным 1 если равны 1 одновременно оба сигнала в 2 -м разряде слагаемых; в)операция образования запомненного сигнала в & -м разряде. Запомненный сигнал в 6 -м разряде совпадает с си налом переноса из { К +2)-го разряда. Операция образования запомненных сигналов по существу совпадает с операцией образования переносогц г) стерация контроля сложения. Сигнал контроля сложения в 6-м разряде равен 1, если одновременно равны 1 сигналы переносов из ( Е+1)-го и ( В+2)-го разрядов. 2. Пром.ежуточная сумма приводится к нормальной форме и над нормальным кодом Фибоначчи промежуточной суммы и комбинацией запомненных сигналов выполняют п. 1, 2 алгоритма до образования нулевой комбинации запомненных сигналов. Пример 1. Сложить два числа 46 и 41 в 1 - коде Фибоначчи. 1. Представление чисел 46 и 41 в нормальных 1 - кодах Фибоначчи; 1)34 21 13 8 5 3 2 1 1 О10101О .0.0010100 2,Выполнение п, 1 алгоритма: 2)1 О О 1 О 1 О 1 О lOOOlOlOO 11О11111 1 Так как двух единичных переносов одновременно в один разряд не произощло, то по п. 1 алгоритма выполнен правильно. 3. Выполнение п. 2 алгоритма (нормализация промежуточной суммы): 3) t ; I Q I I 1110 1ОО10О111О 1001010010 4) 10О1О10010 00 01000010 1001 1 1 о о 1 о 1 о 9 1 1. 10010 1 о 1 6 d 1 о о 1 о 1010010010 0000010000 1010011 7)1 о 1 о g J. 1 010 1 о 1 о 100 о 1 о 8) 1010100010 0000000100 1010100110 Сложное закончено Сокращение времени сложения и повышение быстродействия сумматора, а также повышение контролирующей способности сумматора мохут быть достигнуты, если дополнительно к известным операц№ям образования промежуточной суммы в -м разряде и образования переноса из 6-го в ( 6-1)-й и ( Б-2)- разряды ввес ти операцию образования сигнала промежуточной сверхсуммы в Е.-М разряде, операцию образования сверхпереноса из К-го в { 6-1)-й и ( К-2)-й разряды, опе рацию образования запомненного сигнала и операцию образования сигнала контроля сложения, В предлагаемом сумматоре кодов Фибоначчи в каждом разряде ( 6-м) анализируются семь сигналов: сигналы в 6-м разряде слагаемых.сигналы переносов из(+1 )vrf и { +2;-го разрядов в разряд, налы сверхпереносов из { 6+1)-го и ( 6 + +2)-го разрядов в &-й разряд и сигнал промежуточной сверхсуммы из ( 6-1)-го разряда; при этом в каждом разряде выполняются одновременно шесть операций: а)операция образования сигнала промежуточной суммы в 6 -м разряде, кото рая совпадает с аналогичной операцией в известном способе и состоит в следующем: сигнал промежуточной суммы прини мают равным 1, если равен 1 хотя бы один из сигналов в & -м разряде слагаемых, или сигнал переноса из Б -го разряда, и нулю в противном случае; б)операция образования переноса из ( е+1)-го в ( е-1)-й и ( Е -2)-й разряды, которая совпадает с аналогичной опе рацией в известном способе и состоит в следующем: сигнал переноса из 6 -го разряда принимают равным 1, если равны 1 одновременно оба сигнала в 6 -м разряде слагаемых, и нулю в противном случае; в)операция образования сигнала промежуточной сверхсуммы в В -м разряде сигнал промежуточной сверхсуммы принимают равным 1, если равен 1 хотя бы один из следующих сигналов: сигнал промежуточной суммы в 6-м разряде, сигнал переноса из ( 6+2)-го разряда, сиг нал сверхпереноса из { 6+1)-го либо из ( +2)-го разряда, и нулю в противном случае; 414 г) операция образования сигнала сверхереноса из 6 -го разряда в ( 6-1)-й И { --2)-и разряды: сигнал сверхпереноса из 6 -го разряда принимают равным 1, еоти равен нулю сигнал промежуточной суммы в { С-1)-м разряде и одновременно равен единице хотя бы один кз сигналов переноса или сверхпереноса из { 6+2)-го разряда в 6 -и разряд, и нулю в противном случае; ц) операция образования запомненного сигнала в 6-м разряде: запомненный сигнал в &-М разряде принимают равным 1; если одновременно равны 1 следующие сигналы: сигнал промежуточной суммы в ( )-м разряде, хотя бы один из СИРналов в 8 -м разряде слагаемых и хотя бы один из сигналов переноса и сверхпереноса из В +2-ГО разряда и нулю в противном случае; е) операция образования сигнала конт роля; сигнал контроля принимают равным 1 (сигнал ошибки), если равен 1 сигнал переноса из ( Е+1)-го разряда и одновре- . мен но равен 1 хотя бы ОД1Ш из следующих сигналов: сигнал в 6 -м разряде первого слагаемого, сигнал в 6 -м разряде второго слагаемого, сигнал переноса из { 6+2)-го разряда, сигнал сверхпереноса из ( &+1)-го разряда, сигнал сверхпереноса из ( Е+2)-го разряда, либо равен 1 сигнал сверхпереноса из С -го разряда и одновременно равен 1 хотя бы один из следующих сигналов: сигнал переноса из 6 -го разряда, сигнал промежуточной суммы в ( 6-1)-м разряде, запомненный сигнал в В -м разряде, С учетом введенных операций образование промежуточной сверхсуммы и запомненных сигналов приведены в примере 2. Пример 2. Образовать промежуточную сверхсумму и запомненные с 1гналы при сложении следующих 1-кодов Фибоначчи:12 11 1О 9 8 7 6 5 4 3 2 1 О - номера разрядов 1 О 10100О1О100 1О 1О101010ООО сигналы переносов из соответствующих разрядов О 1 О 1 О О - проме1111 111 жуточная сумма 1 сигналы переносов из ( € +2)-го разряда. 15732 Так как сигналы промежуточной сум мы в 9-м и 7-мразрядах равны 1 и одновременно равны 1 сигналы в 1О-м и 8-м разрядах промажугочной суммы, то в 1О-М и 8-м разрядах образуют запомненные сигналы. Так как сигнал промежуточной суммы .в 5-м разряде равен нулю, то это приводит к образованию сигнала сверхпереноса из 6-го разряда, а затем из 4-го и 2-го разрядов: 111111 1010100 3 I f tl t tit сигналы сверхпереносов В результате образуется следующая проме жуточная сверхсумма и запомненные сигналы:11111- проме11111111жуточная сверхсумма запомненные сигналы Если равен 1 сигнал переноса из ( S+ +1)-го радряда, то это означает, что в (6 +1)-м разряде слагаемых имею.тся ничные сигналы, отсюда вытекает, что в ( +2)-м и -м разрядах слагаемых 3)аведомо должны быть нули (свойство нормальной формы кодов Фибоначчи), т.е. имеет место следующая ситуация: е+2 в+1 „. о10 о1 о перенос из (6+1)-го разряда Следовательно, при единичном сигнале переноса из ( 6+1)-го разряда сигналы в 6-м разряде слагаемых должны быть нулевыми (первое контрольное соотношение) Должен быть нулевым также сигнал переноса из (6+2)-го разряда (второе контрольное соотношение). Далее, сигнал пере носа из ( &+1)-го разряда приводит к появлению единичного сигнала в К -м раз- ряде промежуточной суммы, что автомати чески исключает появление сигнала сверхпереноса из ( 6+1)-го разряда (третье контрольное соотношение). Един1гчный сиг нал сверхпереноса из (+2)-го разряда также не может появиться, так как равен 1 сигнал в ( 6+1 )-м разряде промежуточ нойСуммы (четвертое кбнтрольное соотношение) Если равен 1 сигнал сверхпереноса из б-го разряда, то исключает появление единичного сигнала промежуточной суммы в ( С-1)-м разряде (пятое контрольное слотношение), а также запомненного сигнала в 6-м разряде, который может появиться только при единичном сигнале промежуточной суммы в ( 6-1)-м разряде (шестое контрольное соотношение jj; и, наконец, появление единичного сигнала переноса из 6 -го разряда, который сразу же вызывает появление единичного сигнала промежуточной суммы в ( -1)-м разряде и запрет сигнала сверхпереноса из б-го разряда (седьмое контрольное соотношение). Таким образом, вместо одного контрольного соотношения в известном сумматоре кодов Фибоначчи в данном сумматоре введено 7 контрольных соотношений, которые и приводят к достижению второй цели изобретения - повышению контролирующей способности сумматора. Известная операция нормализации кода Фибоначчи не учитывает запомненные сигналы и состоит, например в следующем: 1011101101110 О.1ОО110О10О10 100101ОО0010010 в сумматоре кодов Фибоначчи операция нормализации ведется с -учетом значений запомненных сигналов в соответствующих разрядах и состоит в следующем: если в процессе нормализации возникает необходимость замены нуля в 6-м разряде и единиц в ( 6-1)-м и ( 6-2)-м разряде своими отрицаниями, а запомненный сигнал либо в ( 6-Г)-м, либо в ( -2)-м разряде равен 1, то в процессе нормализации единицу сохраняют в разряде с единичным запомненным сигналом, а запомненный единичный сигнал заменяют на нулевой. Проведем нормализацию промежуточной сверхсуммы и запомненных сигналов в рассмотренном выше примере. 1) 1 1 1111 J. 111 1О011111111111 10010111111111 10011101111111 1О1О0110О11111 1О101О0001О111 7) 101010 8) 101010 OOIOIOIOрезуль1ат сложения Работа сумматора кодов Фибоначчи протекает следующим образом. Сигналы на входах слагаемых 1 и 2 появляются одновременно с сигналом на входе 7 начала сложения. При этом начинается процесс формирования сигнала в многоразрядном полусумматоре 3 (как будет показано ниже, сигнал переноса в полусумматоре распространяется от старших разрядов к младшим). Блок 8 перезаписи информации представляет собой линию задержки с отводами в каждом разряде. Сигнал в блоке 8 перезаписи информации также распространяется от старших разрядов к. младшим, и, начиная со старших разрядов, последовательно переписывает информацию с полусумматора 3 в нормализатор 12. Сигнал в нормализаторе 12 распространяется в направлении от младших разрядов к старшим. Поэтому нормализация старших разрядов начинается раньше, чем закончился переходной процесс в полусумматоре 3. За счет параллельной организации работы полусумматора 3 и нормализатора 12 удается в среднем повысить быстродействие сумматора. Появление сигнала на выходе 11 свидетельствует об окончании процесса перезаписи информации. Если хотя бы на одном из выходов 6 или 15 появляется сигнал ошибки, то через элемент ИЛИ 16 он поступает на контрольный выход 17 сумматора. После появления сигнала на выходе 11 и. после окончания переходного процесса в нормализаторе 12 на выходе 14 появляется сигнал окончания сложения разрешающий считывание информации с сумматора. Наличие сигнала окончания сложения также приводит к повышению в среднем быстродействия сумматора. Работу многоразрядного полусумматор 3 удобнее объяснить, если ввести как бы два этапа обработки информации в одноразрядном полусумматоре: этап образования промежуточной суммы (выход 31) и переноса (выход 23) и этап образования промежуточной сверхсуммы (выход 3.9), сверхлереноса (выход 22) и запомненного сигнала в ,-м разряде (выход 2О). На первом этапе сигналы могут появляться только на входах 26, 27, 28 и 29. Если хотя бы на одном из входов 26 27 и 29 появляется единичный сигнал, то через элементы ИЛИ 35-34 это пркво 7 64 дит к появлению сигнала на выходе 31, а через элемент ИЛИ 44 - на выходе 19. Если единичный сигнал появляется на входе 28, то через элементы ИЛИ 36 и 44 это приводит к появлению сигнала на вы ходе 19. Если на входах 27 и 26 одновременно Появляются единичные сигналы, то через элемент И 37 это приводит к появлению сигнала на выходе 23. Первый этап обработки информации в полусумматоре хорошО контролируется. При сложении нормальных 1-кодов Фибоначчи из 16 кодовых комбинаций на входах 26, 27, 28 и 29 семь кодовых комбинаций являются запрещенными, а именно: Появление единичного сигнала переноса из (П+1)-го разряда (вход 29) означает, что в ( 8+1)-м разряде слагаемых находятся единицы и, следовательно, в {iE+2)-м и Е-м разрядах слагаемых заведомо должны быть нули: е+2 е+1 -перенос Следовательно наличие переноса из (€+1)-го разряда и наличие хотя бы одной единицы на входах 26, 27 и 28 является признаком ошибки. В схеме одноразрядного полусумматора 18 эта идея контроля полусумматора на первом этапе обработки информации реализуется следующим образом. Если на входе 29 появляется нелиничныйсигнал и одновременно хотя бы на одном из входов 26, 27 и 28 появляется единичный сигнал, то через элементы ИЛИ 35 и 36 и далее через элемент ИЛИ 4О, элемент И 45 и элемент ИЛИ 46 это приводит к появлению единичного сигнала на выходе 21. Этап образования промежуточной сверх суммы (выход 19), сигнала сверхпереноса (выход 22) и запомненного сигнала в -м разряде (выход 20) начинается пос ле появления сигналов на входах 24, 25 и 30. Заметим, что единичный сигнал сверхпереноса из (6+1)-го разряда на входе 24 может появиться только в том случае, если равен нулю сигнал промежу - точной суммы в 6-м разряде (выход 31). Единичный сигнал на входе 24 через элемент ИЛИ 44 приводит к появлению единицы на выходе 19 (сигнал промежуточной сверхсуммы). Единичный сигнал на входе 25 через элемент ИЛИ 36 и 44 также приводит к появлению единицы на выходе 19. Единичный сигнал на выходе 22 (сигнал сверхпереноса или 6 -го разряда) по является при следующих условиях: сигнал на входе ЗО должен быть нулевым, что через элемент НЕ 38 приводит к появлению разрешающего (единичного сигнала) на одном из входов элемента И 43; хотя бы на одном из входов 27, 26 и одновременно хотя бы на одном из входов 25, 28 должны быть единичные сигналы что приводит к появлению единичных сигналов на выходах элементов ИЛИ 35 и 36, элемента И 39, ив конечном итоге, на выходе элемента И 43 и выходе 22. Если же появляется единичный сигнал на выходе элемента И 38 и одновременно на входе 30, то в этом случае через элемент И 42 формируется единичный сигнал на выходе 20 (запомненный сигнал). Единичный сигнал на выходе 21 (сигнал ощибки)- будет появляться при следующих комбинацией, входных сигналов: 1)если единичный сигнал присутству ет на входе 29 и одновременно хотя бы на одном из входов 24, 25, 26, 27 и 28 (пути прохождения сигналов: элемент ИЛИ 35, либо элемент ИЛИ 36, элемент ИЛИ 40, элемент И 45, элемент ИЛИ 46)j2)если единичный сигнал присутствует на выходе 22 и одновременно либо на выходе 23, либо на входе 30, либо на выходе 20, (пути прохождения сигналов: элемент ИЛИ 41, элемент И 47, элемент ИЛИ 46); 3) если единичные сигналы одновременно присутствуют на входе 32 и выходе 20 (пути прохождения сигналов: элемент И 48, элемент ИЛИ 46). Время задержки Т элемента 60 задержки 49 блока перезаписи информации 8 выбирается из следующие; соображеннй.Наиболее неблагоприятная (с точки зрения времени распространения сигнала в сумматоре) ситуация возникает при сложении следующих 1-кодов Фибоначчи: 1010101010 1ООО 000000 При сложении таких М -разрядных кодов Фибоначчи вначале от старшего ( . разряда формируется сигнал переноса из Я-1-го в п - 2-й и (1 -3-й разряды: 10101О1О1 1ОООООООО 1 о 1 о 1 о а затем формируется сигнал сверхпереноса из П -3-го в П -4 и П разрядыэ из И-5-го - в Н-€)-й и разряды и т.д., т„е. процесс распространения сигнала в полусумматоре 3 протекает следующим образом: О 1 О 1 О 1 О (Стрелками показаны единичные сигналы переноса и сверхпереноса в сумматоре). При возникновении сигнала переноса или сверхпереноса из 6-го разряда в двух соседних разрядах полусумматора 3 одновременно начинается формирование выходных сигналов. Обозначим через Т время задержки сигнала в эпементе И либо в элементе ИЛИ. Анализ схемы одноразрядного полусумматора 18 показывает, что 217 наиболее длительными являются процессы формирования либо сигнала сверхпереноса, (цепь прохождения сигнала: элементы ИЛИ 36, И 39, И 43), лиСо запомненного сигнала (цепь прохождения сигнала: элементы ИЛИ 36, И 39, И 43), либо запомненного сигнапа (цепь нахождения сигнала: элементы ИЛИ 36, И 39, И 42}, либо сигнала промежуточной сверхсуммы (цеп Прохождения сигнала; элементы ИЛИ 35, ИЛИ 34, ИЛИ 44). Время формирования каждого из этих сигналов равно 3 Таким образом, при возникновении сит нала сверхпереноса из 6-го разряда время формирования всех выходных сигналов в двух соседних полусумматорах не тревышает ЗС-. Выберем время задержки Т - ЪС w рассмотрим работу схемы блока 8 перезаписи информации. В момент начала сложе- кия на входе 7 и на всех входах 1 и 2 слагаемых полусумматора 3 одновременно появляются соответствующие сигналы. Рас смотрим различные разрешенные Комбинации входных сигналов на входах 1 и 2 И -1-го и П-2-ГО полусумматоров. Таких комбинаций девять; Нетрудно проследить, что в любой ситуации выходные сигналы Ц -1-го и И -2-го полусумматора формируются за вре мя . Через время ЗТ появляется сигнал на выходе элемента задержки 6 О. Этбт сигнал через элементы И 61-64 приводит к записи информации в два старших разряда нормализатора 12 и с этого момента начинается процесс нормализации результата, сложения. Сигнал на вы ходе задержки 60 старшего разряда приводит к запуску элемента задержки следу ющей ячейки 49 и т.д. Через ЗтС, где In - число ячеек 49 в блоке 8 перезаписи информации сигнал появляется на выходе 11, что свидетельствует об окончании первого этапа сложения. Так как И - при четном f I - при нечетном h ; 64 то время, затрачиваемое на выполноше первого этапа сложения, равно ( 1,5иС при четном h t -bwXi 1Дн-1)1лри нечетном h. В схеме ячейки 65 нормализатора 12 И 77 и 79, ИЛИ 78 и триггеры 66 и 71 осуществляют операцию нормализации, а элемент И 80 выполняет контрольные функции. Из рассмотренного выше метода сложения вытекает, что единичный запомненный сигнал в 6-м разряде сумматора поступающий на вход 36, может появиться только вместе с единичным сигналом в 6-м разряде промежуточной сверхсуммы, поступающий на вход 85 (первое контрольное соотношение). Если в результате помех или отказов в схеме окажется, что на нулевом выходе 75 триггера 71 и единичном выходе 7О триггера 66 появляются единичные сигналы, то это приводит к появлению единичного сигнала на выходе элемента И 80 и на контрольном выходе 89 ячейки 65 Е.-ГО разряда. Если на входы 85 двух соседних ячеек 65 (6-й и(&-1)-1)-й нормализатора 12 поступают единичные сигналы, на входы 86 этих ячеек - нулевые сигналы и на вход 85 ячейки 65 6 разряданулевой сигнал, то это приводит к тому, что на все входы элемента И 79 В -и ячейки 65 поступают единичные сигналы и на; его выходе появляется единичный сигнал, который, пройдя через элементы ИЛИ 78 и И 77 на нулевой вход 74 триггера 71 6-й ячейки 65, а также через выход 88 6-й ячейки 65, вход 87 ( 6-1)-й ячейки 65, элемент ИЛИ 78 и элемент И 77 на нулевой вход 74 триггера 71 ( В-1)-й ячейки 65, приводит к сбросу триггеров 66 и 71 этих ячеек 65 в нулевое положение. Это приводит к тому, что на выходе элемента И 79 С -и ячейки 65 происходит формирование заднего фронта импульса (переход 1 - О), что через выход 88 6-И ячейки 65 и вход 84 ( 6+1)-и ячейки 65 приводит к записи 1 в триггер 71 (6+1)-и ячейки 65. Предположим, что на вход .86 одной из ячеек 65 ( 6-1 )-й или (6-й) поступает единичный сигнал (два сигнала одновременно поступать не могут). Пусть, например, единичный сигнал поступает на вход 86 8-и ячейки 65. В этом случае элемент И 77 6-й ячейки 65 закрыт и сигнал с выхода элемента ИЛИ 79 6-й ячейки 65 проходит на вход триггера 71 6-й 2373 ячейки 65; и, следовательно, триггер 71 остается в единичном состоянии, но этот же сигнал сбрасывает триггер 66 в нулевое состояние. После сброса сигналом с выхода элемент И 79 6-й ячейки 65 триггера 71 ( 6-1)-й ячейки 65 в нупевое состояние задний фронт импульса : выхода элемента И 79 6- ячейки 65 записывает 1 в триггер 71 {С+1)-йячей ки 65, и, если в триггере 71 6+2}-й ячейки 65 записан О, то создаются условия для свертки 6-го и { В+1)-го раз рядов в (6 +2)-и разряд и т.д. Быстродействие сумматора может быть оценено следующим образом. Процесс еложения состоит из двух совмещенных во времени этапов: 1) этап формирования сигналов на выходах многоразрядного полусумматора; длительность этого этапа: (-/ДиСпри четном и; J,5(ii-l)tnpH нечетном М , 2) этап нормализации, который начина ется спустя 3t после первого этапа и может продолжаться после окончания первого этапа нейоторсе время tTg Так как время V постоянно и не зависит от комбинации слагаемых 1-кодов Фибоначчи, то наиболее неблагоприятной комбинацией выходных сигналов сумматора является такая, когда запомненные сигналы во всех разрядах равны О, а ком бинация сигналов промежуточной сверхсуммы имеет вид; 01О10101011 в этом случае процесс нормализации нач нается только после записи значений двух младших разрядов в нормализаторе: 1 Ъ 1 11 1010 1 g 1 1 О О 1010 101011ОООО О11ОООООО 1 оооооооо оооооооо в рассмотренном примере переход от исходной совокупности сигналов к конечном результа.ту осуществляется с помошъю 5 сверток. В общем случае максимальное количество сверток равно -j при четно П и при нечетном Ц.Анализ схем на фиг. о и 6 показывает, что для осуществления одной свертки должен 4 Лройти через схему И 79, скему ИЛИ 78, схему И 77 и триггер 71, т.е. время онной свертки равно С., - 4V, где считается время задержки в триггере равно времени задержки в схеме И или схеме ,ИЛИ. Тогда в наиболее неблагоприятной ситуацииSCh-DT при четном Hj 2(-2.)Х РИ нечетном И , Максимальное время сложения равно (.-2) при четном П, (5,) tT-при нечетном/L, Минимальное время :у1ожен1ш () ,5(п-1)Т при четном л-(,5(и-2)Спри нечетном п. Сравнение предлагаемого сумматора кодов с известным показывает, что достигается выигрыш в быстродействии более чем на порядок Быстродействие классического двоичного сумматора может быть оценено следующей формулой: , где Т - время задержки одноразрядного сумматора. Анализ структур классических сумматоров показывает, что Т -ЗС т.е. Т г ЗтТ Учитывая, что для представления одного и того же диапазона в 1-коде Фибоначчи требуется примерно в 1,4 раза большее число двоичных разрядов (,4), то в этом случае быстродействие сумматора находится в следующих пределах: Т (..,1-f4,9)mtr, т.е. быстродействие данного сумматора соизмеримо с быстродействием классического двоичного сумматора. Сравнение предлагаемого сумматора кодов с известным по критерию контролирующей способности показывает существенный выигрыш и по этому критерию, так как в многоразрядном полусумматоре реализуется семь контрольных соотношений, в то время как в известном сумматоре только одно контрол1ьное соотношение. Формула изобретения 1. Сумматор кодов, содержащий многоразрядный полусумматор, входы которого соединены с входами слагаемых сумматора и элемент ИЛИ, выход которого подключен к контрольному выходу сумматора, отличающийся тэм, что, с целью повышения быстродействия и контролирующей способности сумматора, он содержит нормализатор и блок перезаписи информац{йс, входы которого соединены со входом начала сложения и выходами промежуточной сверхсуммы и запомненных сигналов многоразрядного полусумматора, а выходы - со входами нормализатора, выходы нормализатора соединены с выходами результата сложения сумматора, окон чания сложения сумматора и первым входом элемента ИЛИ, второй вход которого подключен к контрольнок у выходу многоразрядного полусумматора. 2, Сумматор по п. 1, о т л и ч а ю щ и и с я тем, что многоразрядный полусумматор содержит М однотипных одноразрядных полусумматоров (И - количество разрядов) и элемент ИЛИ, выход которого подключен к- контрольному выходу многоразрядного полусумматора, а входы - к контрольным рыходам одноразрядных полусумматоров, входы слагаемых 6 -го одноразрядного полусумматора ( 6 1, .,., п ) подключены ко входам 6-го разряда многоразрядного полусумматора, выходы промежуточной сверхсум- мы и запомненного сигнала 6 го одноразрядного полусумматора подключены к выходам В -го разряда промежуточной сверхсуммы И запомненного сигнала мно горазрядного полусумматора, выход запом ненного сигнала В-го одноразрядного полусумматора подключен ко входу запомненного сигнала ( Е-1)-го одноразрядного полусумматора, выход переноса 6-го одноразрядного полусумматора подключен ко входу переноса ( S-l)-ro и ( 6-2)-го одноразрядных полусумматоров, входы переноса 6 -го одноразрядного полусумма - тора подключены к выходам переноса ( В+1)-го и (6+2)-го одноразрядных полусумматоров, вьрсод сверхпереноса 6-го одноразрядного полусумматора подключен ко входам сверхпереноса (6-1)-го и { -2)-го одноразрядных полусумматоров входы сверхпереноса 6-го одноразрядного полусумматора подключены к выходам сверхпереноса (6+1)-го и ( 6+2)-г одноразрядных полусумматоров, выход P межуточной суммы Б -го одноразрядно го полусумматора подключен ко входу пр межуточной суммы ( б+1)-го одноразряд ного полусумматора, вход промежуточной суммы ё-го одноразрядного полусумматора подключен к выходу промежуточной суммы ( 6-1)-го одноразрядного полусумматора, выходы переноса, сверхпереноса и прся ежуточной суммы первого одноразрядного полусумматора подключены ко входам элемента ИЛИ, 3. Сумматор по п. 2, отличающий с, я тем, что одноразрядный полусумматор состоит из элементов И, ИЛИ и НЕ, причем вход элемента НЕ соединен со входом промежуточной Суммы и первыми входами первого элемента И и первого элемента ИЛИ, а в(лход - с первым входом второго элемента И, второй вход которого соединен со вторым входсм первого элемента И и выходом третьего элемента И, а выход - с выходом сверхпереноса и первым входом четвертого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, а выход - с первым входом второго элемента ИЛИ, выход которого соединен с контрольным быходом, второй вход - с выходом пятого элемента И, а третий вход - с выходом шестого элемента И, первый вход KOToporxj соединен с выходом третьего элемента ИЛИ, а второй вход - со входом переноса из ( 6+1)-го разряда и первым входом четвертого элемента ИЛИ, выход которого соединен с выходом промежуточной суммы и первым входом пятого элемента ИЛИ, а второй вход - с первым входом третьего элемента И, первым входом третьего элемента ИЛИ и выходом шестого элемента ИЛИ, первый вход которого соединен со входом первого слагаемого и первым входом седьмого элемента И, а второй вход - со входом второго слагаемого и вторым входом седьмого элемента И, выход которого соединен с выходом переноса и вторым входом первого элемента ИЛИ, третий вход .которого соединен с выходом первого элемента И, выходом запомненного сигнала и первым входом пятого элемента И, второй вход которого соединен с входом запомненного сигнала, вход сверхпереноса вз ( 6+1)-го разряда соединен со вторым входом третьего элемента ИЛИ и вторым , входом пятого элемента ИЛИ, выход которого соединен с йыходом промежуточной сверхсуммы, а третий вход - со вторым входом третьего элемента И, третьим входом третьего элемента ИЛИ и выходом седьмого элемента ИЛИ, первый вход которого соединен со входом переноса нз ( и+2)-го разряда, а второй вход - со входом сверхпереноса из { б+2)-го разряда. 4. Сумматор по п. 1, о т л и ч а ю ш и и с я тем, что блок перезаписи информации состоит из однотипных ячеек по одной на два соседних разряда, начичая с младшего разряда, причем каждая ячейка содержит первый, второй, третий и четвертый входы, соединенные с соот ветствующими выходами проме 5{уточной сверхсуммы и запомненных сигналов соответствующих двух разрядов многоразряд ного полусумматора, пятый вход, первый, второй, третий и четвертый вькоды соединенные с соответствующими входами про межуточной сверхсуммы и запомненных сигналов соответствующих двух разрядов нормализатора, пятый выход, который для всех ячеек, за искшочением младшей, ерединен с пятым входом предыдущей ячейки пятый выход младшей ячейки соединен с выходом блока, а пятый вход старшей ячейки соединен со входом начала сложения блока перезаписи информации, причем каждая ячейка блока перезаписи информа- ции состоит из элементов И и элемента задержки, вход которого соединен с пятым входом ячейки, а выход - с пятым выхо- дом ячейки и с первыми входами первого второго, третьего и четвертого элементов И, вторые входы которых соединены соответственно с первым, вторым, третьим и четвертым входами ячейки, а выходы соответственно с первым, вторым, третьим и четвертым выходами ячейки. 5. Сумматор поп. 1,отлича - ю щ и и с я тем, что нормализатор состоит из однотипных ячеек по числу разрядов, каждая из которых содержит вход промежуточной сверхсуммы, вход запомненного сигнала, первый, второй, третий и четвертый входы связи, информационный вькод, контрольный- выход, первый и второй выходы связи, кроме того нормализатор содержит первый и второй элементы ИЛИ, фильтр, постоянная времени которого превышает время переходного продесса в нормализаторе, триггер, элемент НЕ И элемент И, выход которого соединен с выходом конца сложения нормализатора, первый вход - с единичным выходом тригте ра, второй вхрд - с выходом элемента НЕ вход которого соединен с выходом первого элемента ИЛИ и входом фильтра, выход которог-о соединен с первым входом второго элемента ИЛИ, другие входы ко торого соединены соответственно с контрольными выходами ячеек нормапизатора, единичный вход триггера соединен с входом нормапизатора, входЫ первого элемента ИЛИ соединены с соответствующими вторыми выходами связи всех ячеек нормализатора, информационные выходы всех ячеек нормализатора соединены с выходом результата сложения сумматора, второй выход связи ячейки 6 -го разряда соедииен с четвертым входом связи ячейки (6-1)-го разряда и третьим входом связи ячейки (6+1)-го разряда, первый вход. связи ячейки Е -го разряда соединен с информационным выходом ячейки ( 6-1)-го разряда, второй вход ячейки 6-го разряда соединен с первым выходом связи ячей- ки ( 6+1)-го разряда,- причем каждая ячейка нормализатора содержит элемент ИЛИ, первый, второй и третий элементы И, первый триггер и второй триггер, счетиый вход которого соединен с третьим входом связи, единичный вход - со входом промежуточной сверхсуммы, нулевой вход - с вькодом первого элемента И ячейки нормализатора, единичный выход - с информадионным выходом ячейки нормализатора и первым входом второго элемента И ячейки нормализатора, нулевой выход с первым выходом связи ячейки нормали- затора и первым входом третьего элемента И ячейки нормализатора, второй вход второго элемента И ячейки нормализатора соединен с первым входом связи ячей-, кй нормализатора, третий вход - со вторь1м входом связи ячейки нормализатора, а выход - со вторым выходом связи и первым входом элемента ИЛИ ячейки нормализатора, второй вход которого соединен с четвертым входом связи ячейки нормализатора, а выход - с первым входом первого элемента И и третьим входом первого триггера ячейки нормализатора, единичный вход которого соединен со входом запомненного сигнала, нулевой выход - со вторым входом первого элэмента И ячейки нормализатора, а единичный выход - со вторым входом третьего элемента И ячейки нормализатора, выход соединен с контрольным выходом ЯЧ8ЙКИ нормализатора. СТТГС ЙГГТГ f f QTf Q Источники информации, принятые во внимание при экспертизе 1. Стахов А. П. Избыточные двоичные позиционные системы счисления. Сб. Однородные цифровые вычислительные и интегрирующие струкп:уры, вьш. 2,Таганроге 1974.

2973286430

2.Стахов А. П. Использование естест-Сб. Кодирование и передача дискретных венной избыточности Фибоначчиевых си-сообщений в системах связи, М.,Наука, стем счисления для контроля вычислитель-1976.

ных систем; Автоматика и вычислительная техника , № 6, 1976.s41 Авторское свидетельство СССР по

3.Стахов А. П. Фибоначчиевы дво-заявке № 2358578, кл.Сг06 F 7/50, ичные позиционные системы счисления,03.05.76 (прототип).

n-3 п-че- е-/

n-i н-г

/ о

фаг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор кодов Фибоначчи | 1981 |

|

SU981993A1 |

| Последовательный сумматор | 1977 |

|

SU696452A1 |

| Параллельный сумматор кодов фибоначчи | 1984 |

|

SU1180880A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Параллельный сумматор кодов фибоначчи | 1978 |

|

SU840891A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Комбинационный сумматор | 1987 |

|

SU1442988A1 |

| Сумматор избыточного кода | 1987 |

|

SU1476460A1 |

| Параллельный сумматор | 1986 |

|

SU1363188A1 |

| Последовательный сумматор | 1988 |

|

SU1571573A1 |

Авторы

Даты

1980-05-05—Публикация

1976-12-22—Подача