1

(21) 4331440/31-25

,(22) 23.11.87

,(46) 07.08.90. Бюл. № 29

i(71) Физико-механический институт

м. Г.В.Карпенко

,(72) О.П.Бухало и П.П.Драбич

(53)550.837,621.327.7 (088.8)

(56)Авторское свидетельство СССР If 883760, кл. G 01 R 19/04, 1980.

Авторское свидетельство СССР f| 1343378, кл. G 01 V 3/10, 1985.

(54)ИНТЕГРАТОР С ВЕСОВЫМ УСРЕДНЕНИЕМ СИГНАЛОВ

(57)Изобретение относится к информа- иионно-измерительной технике, предназначено для интегрирования случайных импульсных биполярных сигналов

с1 весовым усреднением и может быть использовано в геофизической аппаратуре метода переходных процессов.Цель изобретения - повышение точности из- мгрений путем исключения шумов усилителя постоянного тока и упрощение конструкции. Цель достигается путем интегрирования в стробах информационных импульсов и весового усреднения результата интегрирования. Интегратор содержит шестиканальный коммутатор аналоговых сигналов, входы управления которого подключены к выходам распределителя импульсов, усилитель постоянного тока, резистор, интегрирующий и накопительный конденсаторы. Два вывода интегрирующего конденсатора и один вывод накопительного конденсатора через ключи коммутатора соединены с инвертирующим входом и выходом усилителя постоянного тока, другой вывод накопительного конденсатора постоянно подключен к выходу усилителя постоянного тока, а резистор включен между а 1алоговым входом интегратора и входом одного из ключей коммутатора. 3 ил.

о

(Я

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для геоэлектроразведки | 1990 |

|

SU1777110A1 |

| Устройство для геоэлектроразведки | 1985 |

|

SU1343378A1 |

| Устройство для усреднения импульсной последовательности | 1988 |

|

SU1524071A1 |

| Устройство для электроразведки в движении | 1985 |

|

SU1242884A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388987A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU342296A1 |

| Устройство для определения экстремумов | 1982 |

|

SU1024959A1 |

Изобретение относится к информационно-измерительной технике, предназначено для интегрирования случайных импульсных биполярных сигналов с весовым усреднением и может быть использовано в геофизической аппаратуре метода переходных процессов. Цель изобретения - повышение точности измерений путем исключения шумов усилителя постоянного тока и упрощение конструкции. Цель достигается путем интегрирования в стробах информационных импульсов и весового усреднения результата интегрирования. Интегратор содержит шестиканальный коммутатор аналоговых сигналов, входы управления которого подключены к выходам распределителя импульсов, усилитель постоянного тока, резистор, интегрирующий и накопительный конденсаторы. Два вывода интегрирующего конденсатора и один вывод накопительного конденсатора через ключи коммутатора соединены с инвертирующим входом и выходом усилителя постоянного тока, другой вывод накопительного конденсатора постоянно подключен к выходу усилителя постоянного тока, а резистор включен между аналоговым входом интегратора и входом одного из ключей коммутатора. 3 ил.

Изобретение относится к информа- щ| онно-измерительной технике, пред- нАзначено для интегрирования случай- HKIX импульсных биполярных сигналов с|весовым усреднением и может быть использовано в геофизической аппаратуре метода переходных процессов.

Цель изобретения - повышение точ- но сти измерений путем исключения шумов усилителя постоянного тока и

уп1;

рощения конструкции интегратора.

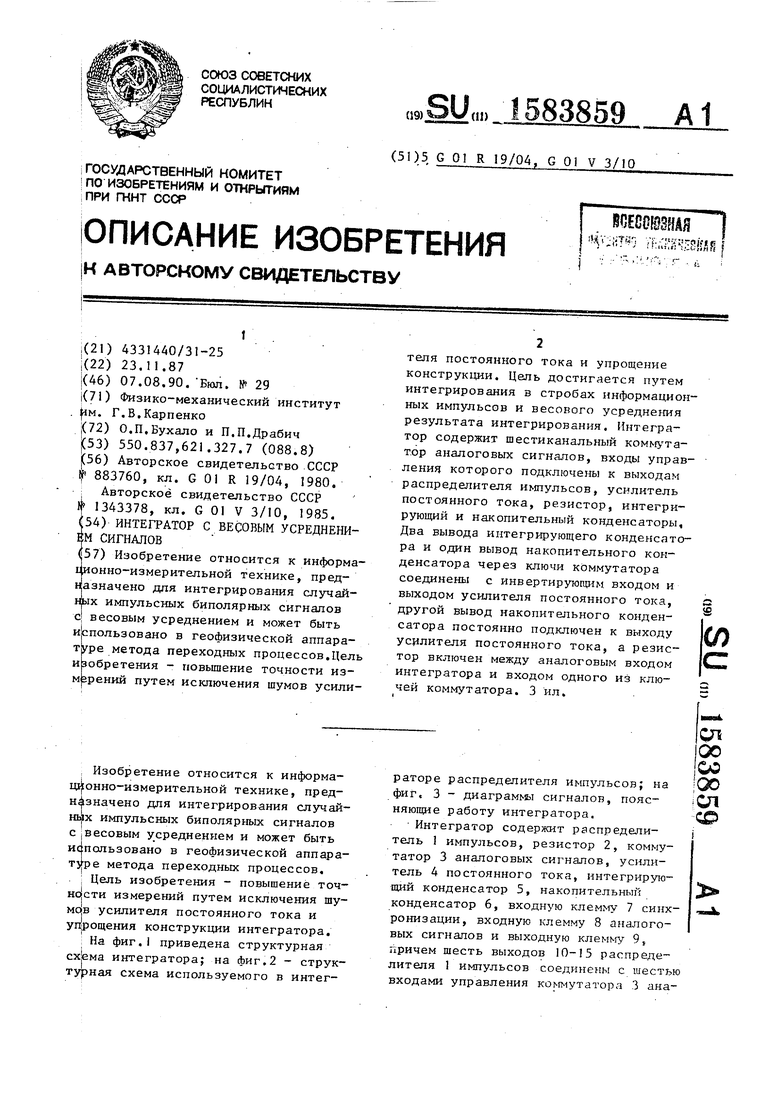

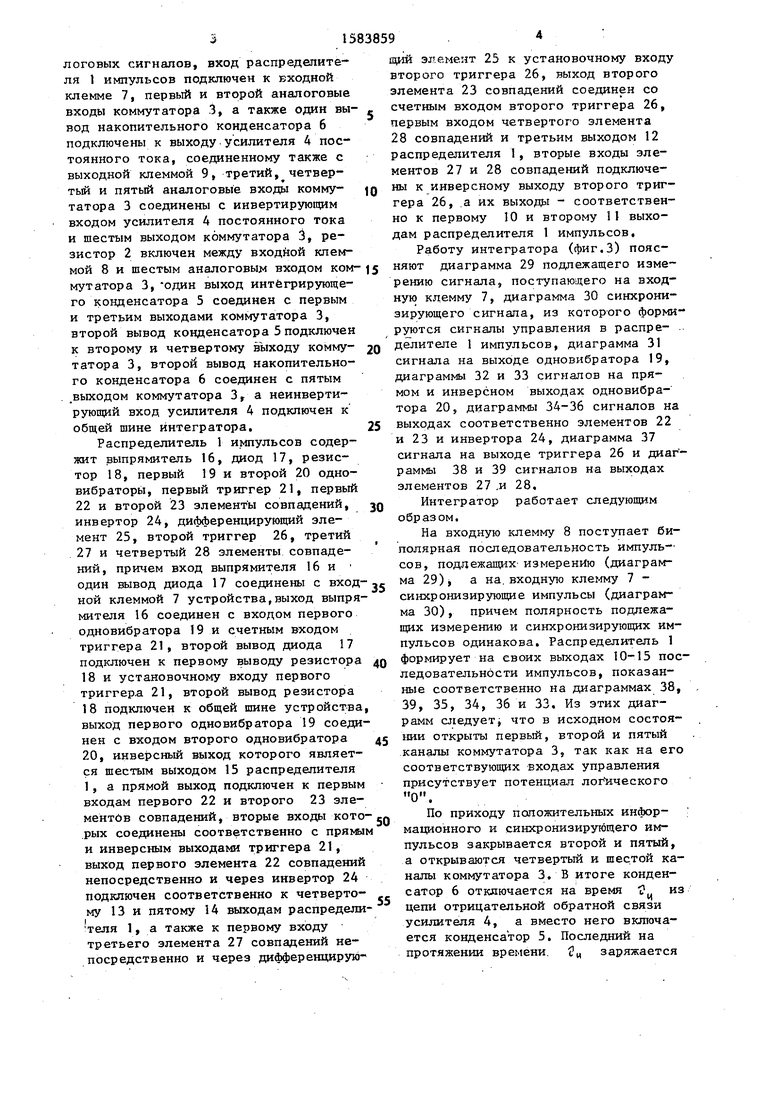

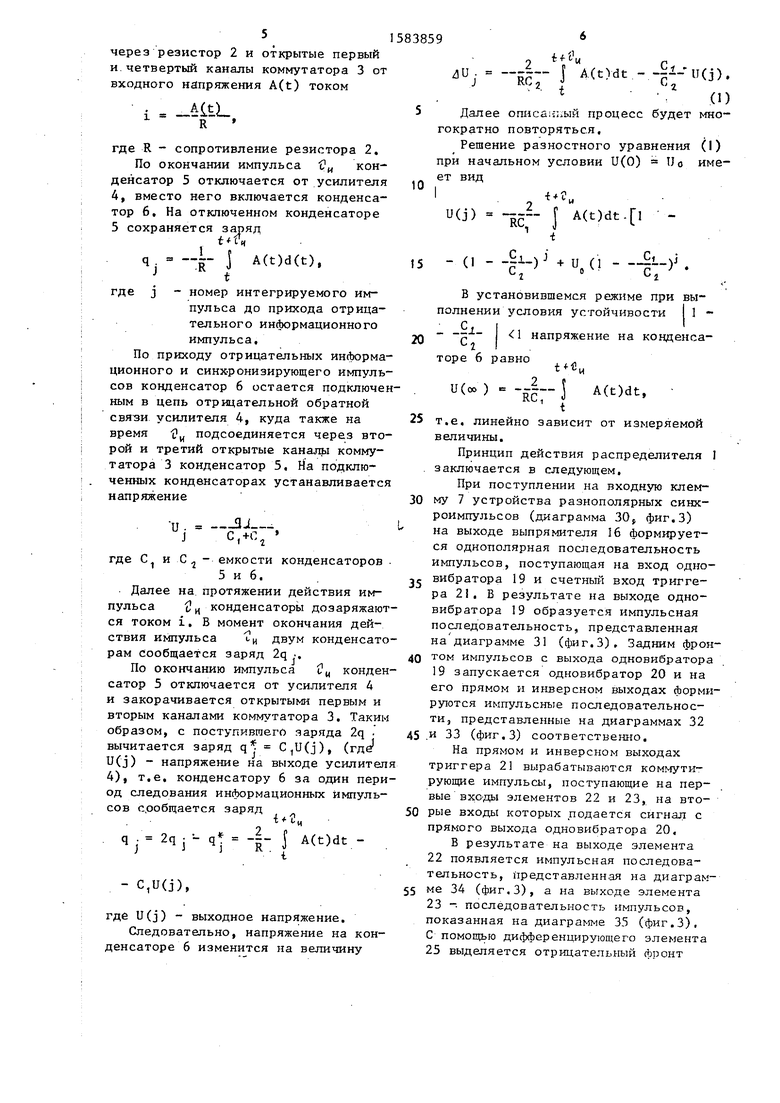

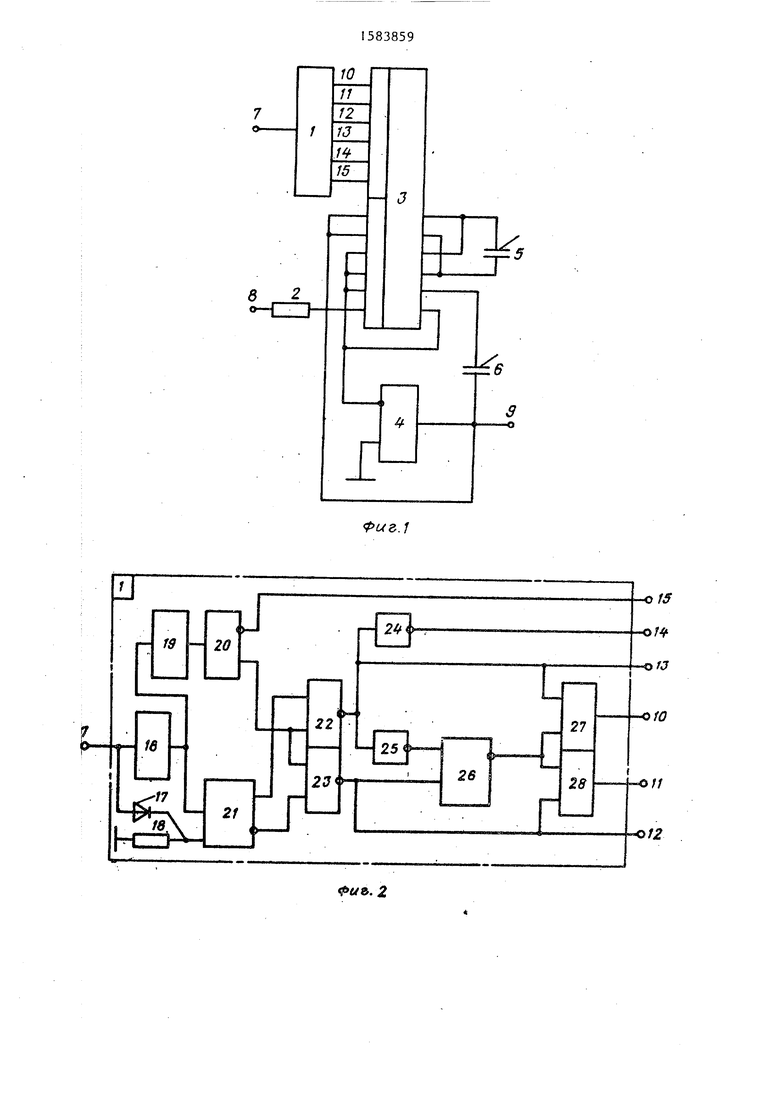

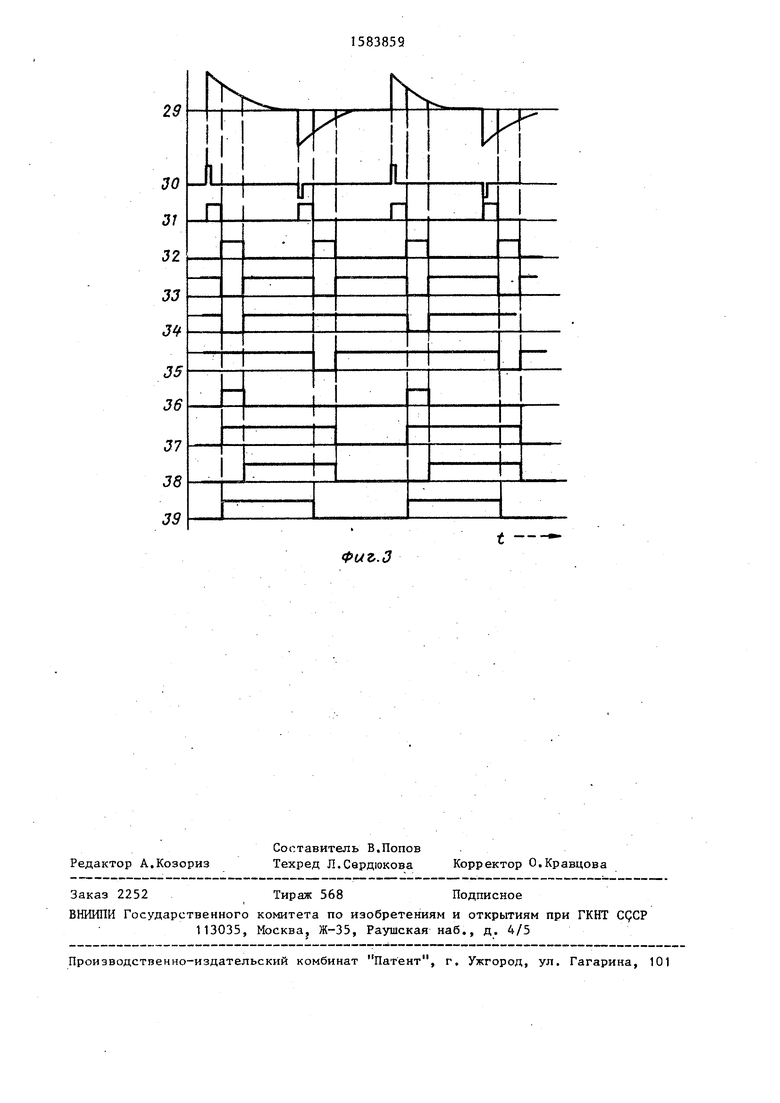

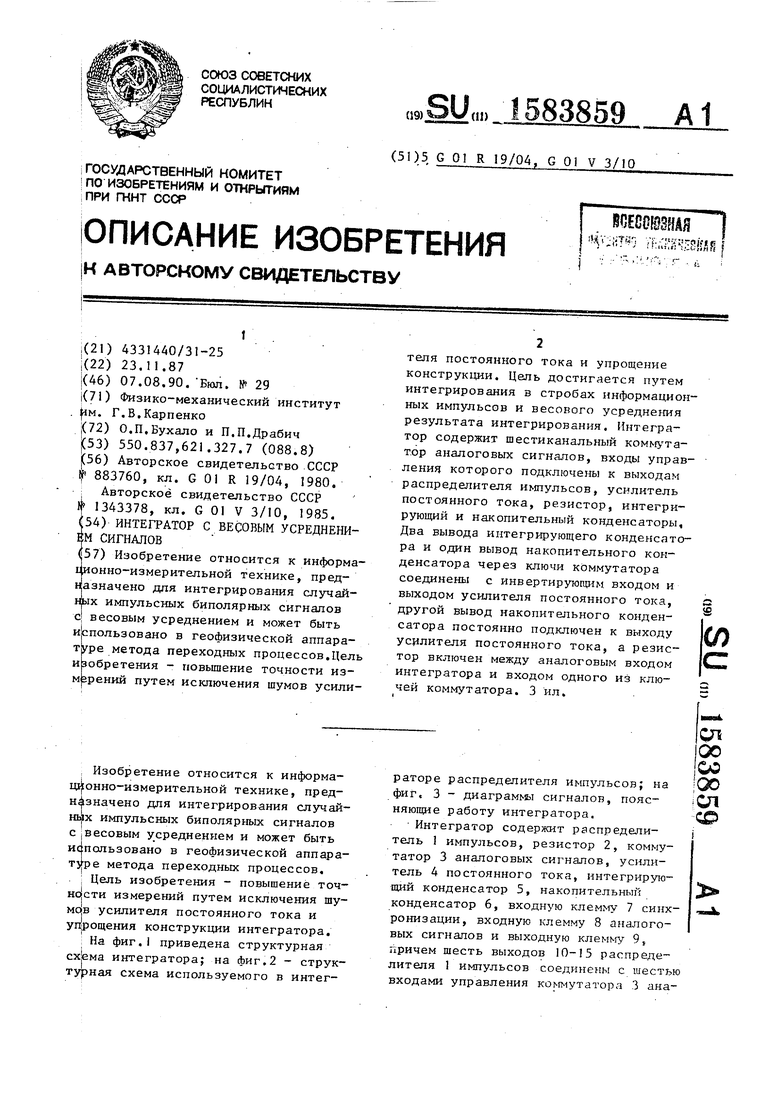

На фиг.1 приведена структурная сх|ема интегратора; на фиг.2 - структурная схема используемого в интеграторе распределителя импульсов; на фиг, 3 - диаграммы сигналов, поясняющие работу интегратора.

Интегратор содержит распределитель 1 импульсов, резистор 2, коммутатор 3 аналоговых сигналов, усилитель 4 постоянного тока, интегрирующий конденсатор 5, накопительный конденсатор 6, входную клемму 7 синхронизации, входную клемму 8 аналоговых сигналов и выходную клемму 9S причем шесть выходов 10-15 распределителя 1 импульсов соединены с шестью входами управления коммутатора 3 анаел оо со оо ел со

лотовых сигналов, вход распределителя 1 импульсов подключен к входной клемме 7, первый и второй аналоговые входы коммутатора 3, а также один вывод накопительного конденсатора 6 подключены к выходу усилителя 4 постоянного тока, соединенному также с выходной клеммой 9, третий, четвертый и пятый аналоговые входы коммутатора 3 соединены с инвертирующим входом усилителя 4 постоянного тока и шестым выходом коммутатора 3, резистор 2 включен между входной клеммой 8 и шестым аналоговых входом ком- мутатора 3, один выход интегрирующего конденсатора 5 соединен с первым и третьим выходами коммутатора 3, второй вывод конденсатора 5 подключен к второму и четвертому выходу комму- татора 3, второй вывод накопительного конденсатора 6 соединен с пятым .выходом коммутатора 3, а неинвертирующий вход усилителя 4 подключен к общей шине интегратора.

Распределитель 1 импульсов содержит выпрямитель 16, диод 17, резистор 18, первый 19 и второй 20 одно- вибраторы, первый триггер 21, первый 22 и второй 23 элементы совпадений, инвертор 24, дифференцирующий элемент 25, второй триггер 26, третий 27 и четвертый 28 элементы совпадений, причем вход выпрямителя 16 и один вывод диода 17 соединены с вход- ной клеммой 7 устройства,выход выпрямителя 16 соединен с входом первого одновибратора 19 и счетным входом триггера 21, второй вывод диода 17 подключен к первому выводу резистора 18 и установочному входу первого триггера 21, второй вывод резистора 18 подключен к общей шине устройства выход первого одновибратора 19 соединен с входом второго одновибратора 20, инверсный выход которого является шестым выходом 15 распределителя 1, а прямой выход подключен к первым входам первого 22 и второго 23 элементов совпадений, вторые входы кото рых соединены соответственно с прямы и инверсным выходами триггера 21, выход первого элемента 22 совпадений непосредственно и через инвертор 24 подключен соответственно к четверто

му 13 и пятому 14 выходам распредели- теля 1, а также к первому входу третьего элемента 27 совпадений непосредственно и через дифференцирую10

1520 25

3859

щий элемент 25 к установочному входу второго триггера 26, выход второго элемента 23 совпадений соединен со счетным входом второго триггера 26, первым входом четвертого элемента 28 совпадений и третьим выходом 12 распределителя 1, вторые входы элементов 27 и 28 совпадений подключены к инверсному выходу второго триггера 26, а их выходы - соответственно к первому 10 и второму 31 выходам распределителя 1 импульсов.

Работу интегратора (фиг.З) поясняют диаграмма 29 подлежащего измерению сигнала, поступаюдего на входную клемму 7, диаграмма 30 синхрони

5 л

5

зирующего сигнала, из которого формируются сигналы управления в распределителе 1 импульсов, диаграмма 31 сигнала на выходе одновибратора 19, диаграммы 32 и 33 сигналов на прямом и инверсном выходах одновибратора 20, диаграммы 34-36 сигналов на выходах соответственно элементов 22 и 23 и инвертора 24, диаграмма 37 сигнала на выходе триггера 26 и диаграммы 38 и 39 сигналов на выходах элементов 27 ,и 28.

Интегратор работает следующим образом.

На входную клемму 8 поступает биполярная последовательность импульсов, подлежащих измерению (диаграм- ма 29), а на входную клемму 7 - синхронизирующие импульсы (диаграмма 30), причем полярность подлежащих измерению и синхронизирующих импульсов одинакова. Распределитель 1 формирует на своих выходах 10-15 последовательности импульсов, показанные соответственно на диаграммах 38, 39, 35, 34, 36 и 33. Из этих диаграмм следует, что в исходном состоянии открыты первый, второй и пятый каналы коммутатора 3, так как на его соответствующих входах управления присутствует потенциал логического О.

По приходу положительных информационного и синхронизирующего импульсов закрывается второй и пятый, а открываются четвертый и шестой каналы коммутатора 3. В итоге конденсатор 6 отключается на время из цепи отрицательной обратной связи усилителя 4, а вместо него включается конденсатор 5. Последний на протяжении времени (н заряжается

через резистор 2 и открытые первый и четвертый каналы коммутатора 3 от входного напряжения A(t) током

A(t) 1R

где R - сопротивление резистора 2.

По окончании импульса Ј„ конденсатор 5 отключается от усилителя 4, вместо него включается конденсатор 6, На отключенном конденсаторе 5 сохраняется заряд

где

- - j A(t)d(t),

t

- номер интегрируемого импульса до прихода отрицательного информационного импульса.

По приходу отрицательных инФорма- ционного и синхронизирующего импульсов конденсатор 6 остается подключенным в цепь отрицательной обратной связи усилителя 4, куда также на

время

подсоединяется через второй и третий открытые каналы коммутатора 3 конденсатор 5. На подключенных конденсаторах устанавливается напряжение

UJ

JU

С,+Сг

Clконденсаторов

где Cj и

Далее пульса ся током

ствия импульса VH двум конденсаторам сообщается заряд 2q .

на

2и

емкости 5 и 6.

протяжении действия им- конденсаторы доэаряжаютВ момент окончания дей-

окончанию импульса см конденПо

сатор 5 отключается от усилителя 4 и закорачивается открытыми первым и вторым каналами коммутатора 3. Таким образом, с поступившего яаряда 2q . вычитается заряд q C,U(j), (где U(j) - напряжение на выходе усилител 4), т.е. конденсатору 6 за один период следования информационных импульсов сообщается заряд

q ; 2q ; - q -§- .f A(t)dt ,

- C,U(j),

где U(j) - выходное напряжение.

Следовательно, напряжение на конденсаторе 6 изменится на величину

,uj

A(t)dt

- (j).

Li

(1)

Далее описал: ый процесс будет многократно повторяться.

Решение разностного уравнения (I) при начальном условии U(0) Uo имеет вид

I. «и

U(J --5cf- J A(t)dt-.

5

0

5

0

5

0

5

0

5

-О --§MJ

V- ,

с,

+ u,(i - -f)

г°г

В установившемся режиме при полнении условия устойчивости

1

вы1 Јl

Сг торе 6

U( )

напряжение на конденсаравно 2

кс7

-J A(t)dt,

t

т.е. линейно зависит от измеряемой величины.

Принцип действия распределителя I заключается в следующем.

При поступлении на входную клемму 1 устройства разнополярных синхроимпульсов (диаграмма 30t фиг.З) на выходе выпрямителя 16 формируется однотшлярная последовательность импульсов, поступающая на вход одно- вибратора 19 и счетный вход триггера 21. В результате на выходе одно- вибратора 19 образуется импульсная последовательность, представленная на диаграмме 31 (фиг.З). Задним фронтом импульсов с выхода одновибратора 19 запускается одновибратор 20 и на его прямом и инверсном выходах формируются импульсные последовательности, представленные на диаграммах 32 и 33 (фиг.З) соответственно.

На прямом и инверсном выходах триггера 21 вырабатываются коммутирующие импульсы, поступающие на первые входы элементов 22 и 23, на вторые входы которых подается сигнал с прямого выхода одновибратора 20,

В результате на выходе элемента

22появляется импульсная последовательность, представленная на диаграмме 34 (фиг.З), а на выходе элемента

23- последовательность импульсов, показанная на диаграмме 35 (фиг.З),

С помощью дифференцирующего элемента 25 выделяется отрицательный фронт

импульсов на выходе элемента 22„Сигнал с выхода элемента 25 подается ка вход установки в О триггера 265на счетный вход которого подаются импульсы с выхода элемента 23, В итоге на инверсном выходе триггера 26 фор мируется сигнал, изображенный на диаграмме 37 (фиг,3)9 который поступает на первые входы элементов 27 и 28 совпадений. На вторые входы элементов 27 и 28 подаются импульсы напряжения с выходов элементов 22-и 23 совпадений. Выходные сигналы элементов 27 и 28 иллюстрируются диаграммами 38 и 39 (фиг.З), Таким образом, на выходах 10-15 распределителя 1 формируются импульсы управления работой коммутатора 3,

Интервал усреднения входных значений сигнала задается соотношением дозирующего и накопительного конденС1 1 саторов, в частности при -J- 1

Ч переходной процесс заканчивается за

один цикл работы устройства; при

Р

. 0,5 за 10 циклов с точностью

1с

0,1%; при 0,9, за четыре

Ч цикла с погрешностью 0,01%} при

р

-- - 0,1 за 60 циклов с погрешгCi

костью 0,07%; при -- 0,05 за

С1

100 циклов с точностью 0,4% и т,де

Предлагаемый интегратор, как и ивестный интегрирует на заданном интервале времени последовательность разнополярных импульсов и усредняет результат интегрирования по весовой функции Однако в нем исключено влиние шумов одного усилителя постояннго тока9 за счет чего повышается тоность, измерений, и он более прост по конструкции.

Формула изобретения

Интегратор с. весовым усреднением

, сигналов, содержащий распределитель импульсов, коммутатор аналоговых сигналов, состоящий из шести аналоговых ключей, входы и выходы которых служат входами и выходами коммутатора аналоQ говых сигналов, интегрирующий и накопительный конденсаторы, резистор и усилитель постоянного тока, причем вход распределителя импульсов служит синхронизирующим входом интегра5 тора, к выходам распределителя импульсов подключены шесть входов управления коммутатора аналоговых сигналов, выход усилителя постоянного тока, служащий выходом интегратора, подключен

0 к первому и второму аналоговому входу коммутатора аналоговых сигналов, к инвертирующему входу усилителя постоянного тока подключены третий и четвертый аналоговые входы коммутатора

5 аналоговых сигналов, а неинвертирующий вход подключен к общей шине интегратора, один вывод интегрирующего конденсатора соединен с первым и третьим выходом коммутатора аналоговых сигна30 ЛОБ, к второму и четвертому выходам которого подключен второй вывод интегрирующего конденсатора, а аналоговым входом интегратора служит первый вывод резистора, отличающий35 с я тем, что, с целью повышения точности измерений путем исключения шумов усилителя постоянного тока и упрощения конструкции, второй вывод резистора соединен с шестым анало40 говым входом коммутатора аналоговых сигналов, пятый вход и шестой выход которого соединены с инвертирующим входом усилителя постоянного тока, а между пятым выходом коммутатора 45 аналоговых сигналов И выходом усилителя постоянного тока включен накопительный конденсатор«,

Фиъ.2

Фиг.З

t

Авторы

Даты

1990-08-07—Публикация

1987-11-23—Подача