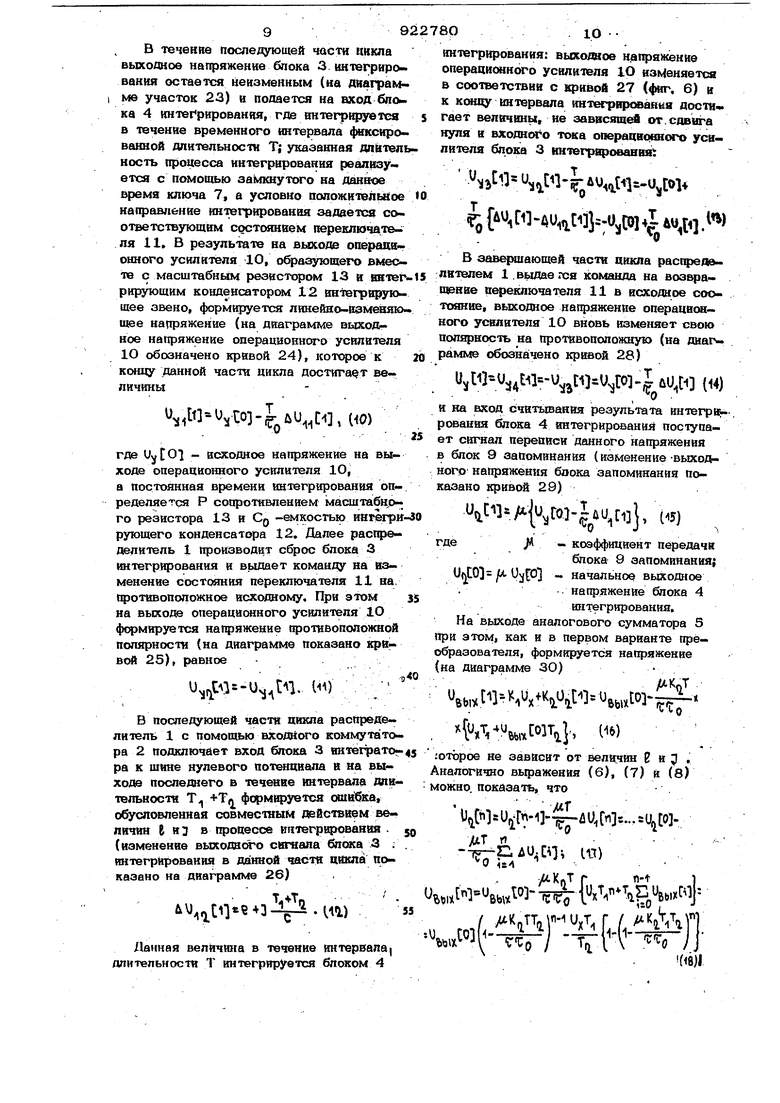

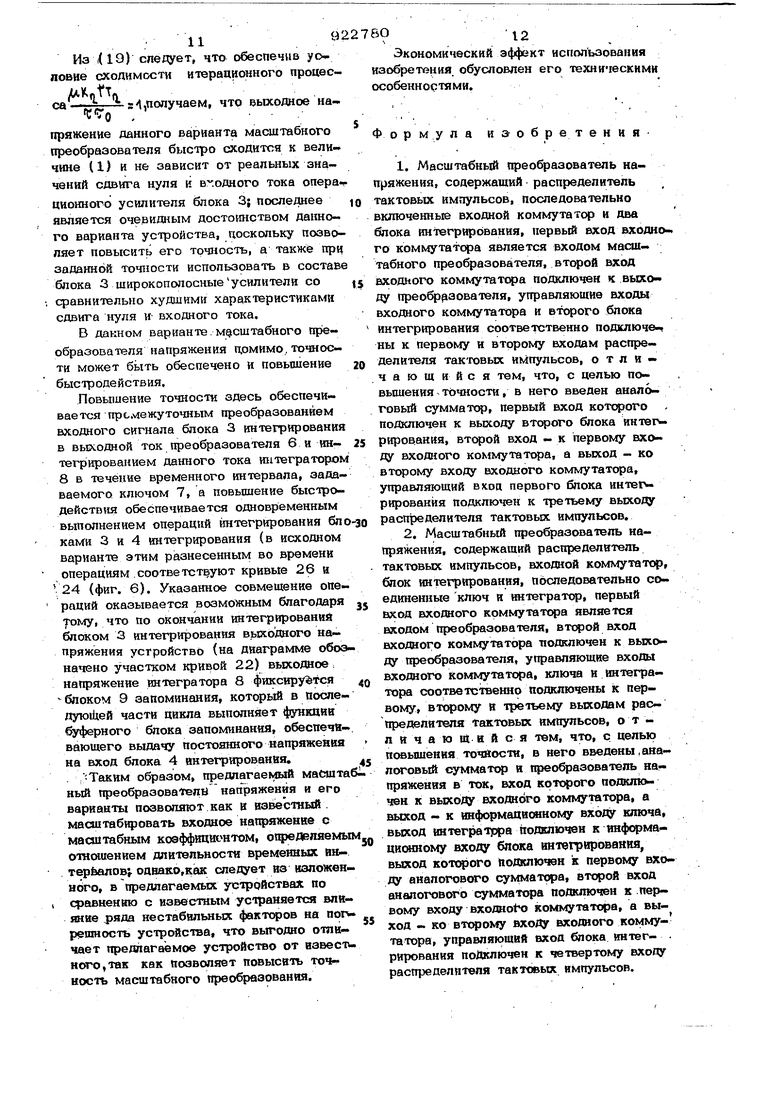

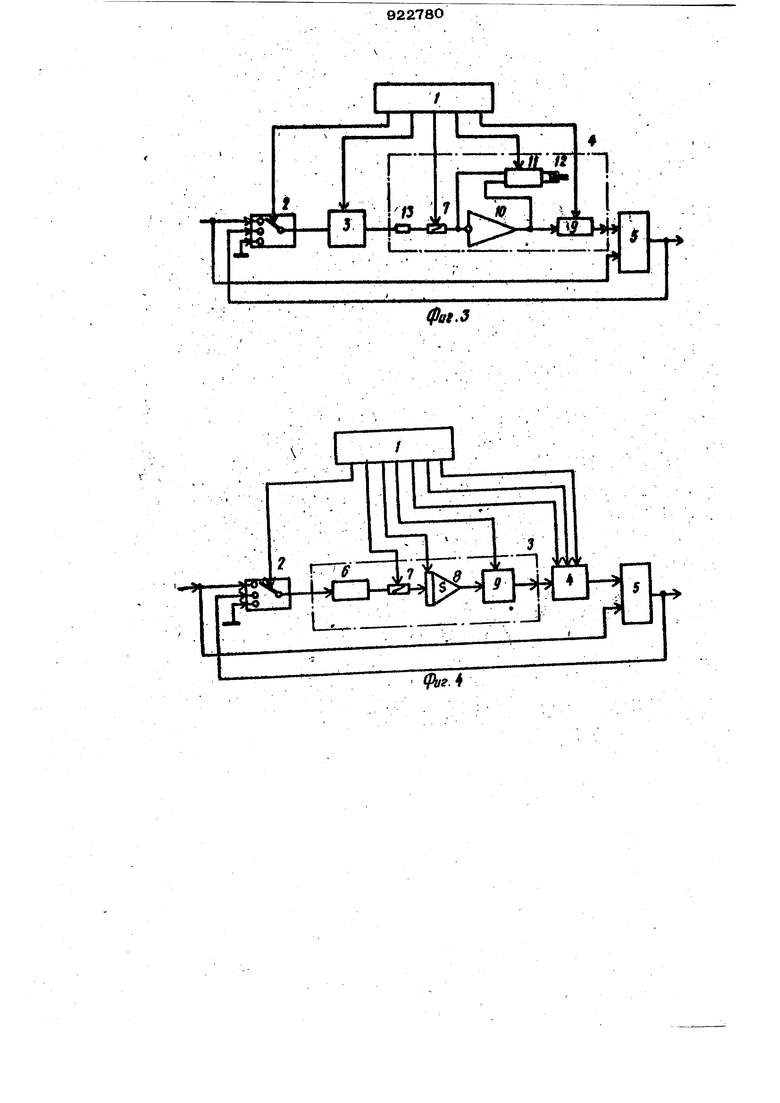

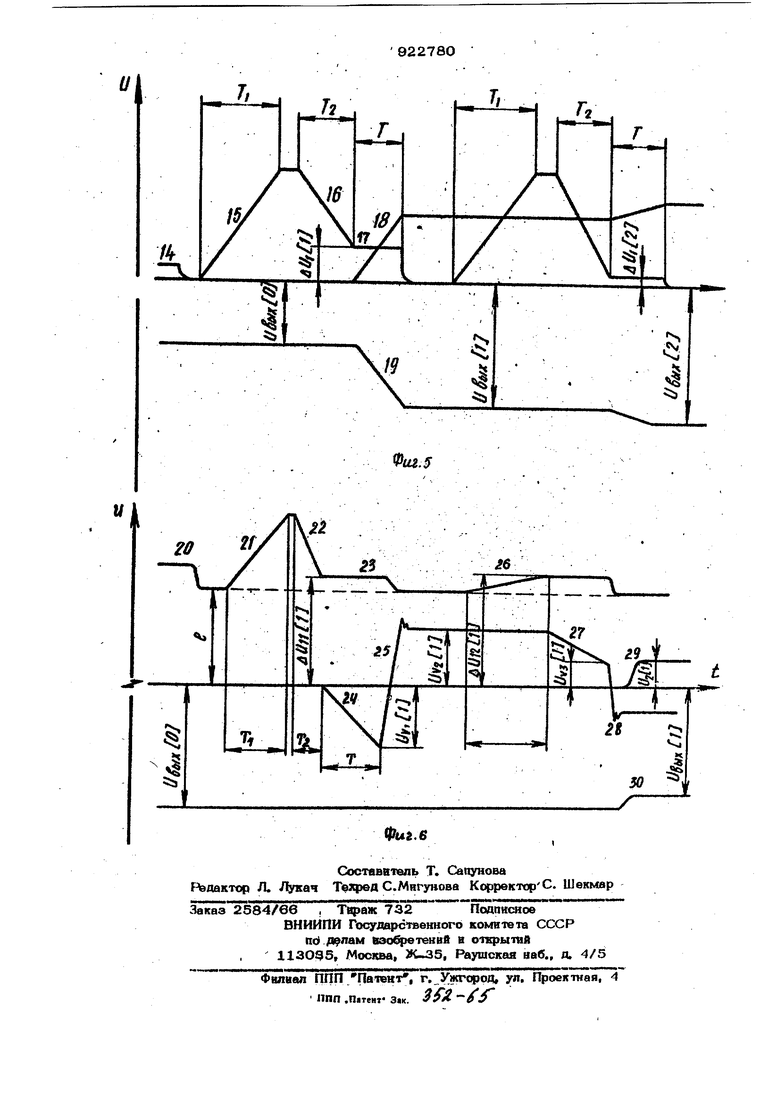

- : , : -.-. -;-Изобретение относится к вычислительной технике н может быть испопьэбввнр в аналоговых вычислитепьнЬк устройствах преобрааователяд аналоговых сигналов и электротехнических установках различного назначения. . Известны масштабные преобразователи напряжения, в которых стабильность и линейность преобразования обеспечиваются отсутствующими характеристиками отношения длительностей вре1 енных интервало ийгтегрированйя входиого ивыхоаного напр ЖеИий j.) .. . Недостаток данных устройств связан с тем, 4to при работе в области времен требуется увеличить постоянную времени интегрирования, приводит к увеличению погрешности преобразователя неидеальности усилителей, входящи; в состав блока интегрирования, а следовательно, при заданных точностных характеристиках сужают его рабочий диапазон. Наиболее близким к предлагаемому является устройство, содержащее расире -; - -- 2 ;, .,.;, Литель тактовых импульсов, посахедовательно включенные входнЬй коммутатор, два блока интегрирования и блок зйпонгинания,- в котором первый и второй входы коммутатора соответственно подключены коBxoj: устройства и выходу блока запоминания, блока запоминания является выходом ургройств1а а управляю щиё входы коммут атора и блока запоминания, а также управляющие входы второго блока интегрирования подключены к сойтветствующим выходам распределителя тактовых импульсов 2 . В случае идеального блока запоминания можно показать; что при увеличении числа, циклов выходное напряжение устройства быстро схо15(Ится к установивщемуся значению : , ст: Однако в случае peoni.iioro блока запоминания на выхо/ю H.iFinciunrn уст3 2ройства возникают пульсации с частотой повторения циклов и амплитудой, опреде. ляемой, в основном, зарядом aanoMHiiaющего конденсатора блока входным током операционного усилителя, а также влиянием импеданса подключенйых к Данному конденсатору элементов. При-сутствив на выходе устройства данных пульсаций снижает точюсть масштабного преобразователя напряжени Я1 Целью изобретения является повышени точности масштабного преобразователя Напряжения. Поставленная цель достигается тем, что D масштабный преобразователь напряжения ,содер кащий {распределитель.такт вых импульсов, последовательно включе ные входной коммутатор и два блока интегрирования, первый вход входного коммутатора является входом масштабного преобразователя, второй вход входного коммутатора подключен к выходу преобразователя, управляющие входы входного коммутатора и второго блока интегрирования сЬответственно подключены к первому и второму входам распределителя тактовых импульсов, введен аналоговый сумматор, первый вход которого подклю чен к выходу второго блока интегрирования; второй вход - JC первому входу входного коммутатора, а вЬпсод - кд вто рому входу входного коммутатора, управляющий вход первого блока интегри./рования подключен к третьему входу распределителя тактовых импульсов. Поставленная цель может быть достигнута тем, что в масш,табный преобрааователь напряжения, содержащий расгпределитель тактовых импульсов, входной коммутатор блок интегриров ия, последовательно соединенные, ключ и интегратор, первый вход входного коммутатора является входом преобразователя втсрой вход входного коммутатора поДяключен к выходу преобразователя, уп рапляющие входы входного коммутатора ключа и интегратора соответственно под ключены к первому, второму и третьему входам распределителя тактовьк импуль сов, введены аналоговый сумматор и преобразователь нап яжеяия в ток, .вход которого подключен к выходу входного коммутатора, а выход - к информационному вхойу ключа, вйход интегратора подключен к информационному входу. бло ка интегрирования, выход которого подключен к первому входу аналогового сумматора, второй вход анапоговогр сум матора подключен к первому входу вхоД 04 ного коммутатора, а выход - ко BTopoKjy входу входное коммутатора, управляющйй вход блока интегрирования подключен к че верто му входу распределителя тактовьк импульсов. Поставленная цель достигается так-же Tet, что в масштабный преобразова-. тель напряжения, содержащий распреде-. лiiTBfib тактовых импульсов, последовательно соединенные входной коммутатор, блок интегрирования, масштабный реаистор, ключ, операционный усилитель и блок запоминания, в обратной связи операционного усилителя включены параллельно соединенные переключатель и интегри ующий конденсатор, первый вход входного коммутатора является входом преобразователя, второй вход., подключен к выходу/преобразователя, управляющие входы входного коммутатора, ключа, переключателя и блока запоминания соответственно подключены к первому, в то- . рому, третьему и четвертому выходам распределителя импульсов, введен анаЯоговый сумматор, первый вход,которого подключен к выходу блока аапомина.ния, второй вход - к первому входу входного коммутатора, а выход - ко второму входу входаого комму та , третий вход которого подключен к шине нулевого потенциала, управляющий .вход блока интег подключен к пятому выходу . распределителя тактовых импульсов. , В последнем варианте масштабного преобразователя напряжения может быть повьшено быстродействие. Кроме того, первый блок интегрирований содержит последовательно соединенные преобразователь напряженияВ ток, ключ, интегратор и блок запоминания, выход которого является выходом первого бло- . ка интегрирования, вход преобрдзователя напряжения в ток является входом первого блока интегрирования, управпяющие входы ключа, интегратора и блока запоминания являются управаяюСа ми входами первсуго блока интегрирования и подключены соответственно к пятому, шестому и седьмому входам распределителя тактовых импульсов. На фиг. 1-4 приведены структурные схемы различных царнантрв масштабного преобразователя, соответственно} на фиг. . 5 - диаграммы, поясняющие работу пер-г вого варианта масштабного .преобразова- . теля напряжени{{; на фвг. 6 - временные диаграммы, поясняющие работу третьего варианта масштабного, преобразоват ия напряжения. МвсштабныА преобразователь насфяжения содержит распределитель 1 тактовьос импульсои, входной коммутатор 2, первый я второй блоки 3 и 4 интегрирования, аналоговый сумматор 5, прео(ааователь 6 напряжения в ток, ключ 7, интегратор 8, блок 9 запоминания, ; операционный, усилитель 10, переключатель 11, интегрирующий конденсатор 12 масштабный резистор 13. Первый вариант масштабного преобраасжателя напряжения (фиг. 1 и 5) оаботает следующим образом. Выходаое напряжение сумматора 5 в произвольный момент времени опредалвется вьфажением:. V«w-- ,vчKw fwVаи.. .AAVK.EIU.fi - выходное напряжение блока 4 Интегрирования в произ- вольный момент времени; выходное напряжени блока 4 цнтегрироваиия и аналогового сумматора 5 в момент окончания пре дыдущего j -го цикла; S(i) - погрешность выходного сигнала блока 4 интегрирования, обусловленная перезарядом накопительного эпемеата данного блока в течение цикла, причем , ,,гДе Тдлительность цикла Hfroi oj - коэффициент передачи аналогового сумматсфа 5 по соответствующим входам причем К 0, К(0, ) R 1К)1. Инерционный сгроцесс установления выходного напряжения преобразовате1Ш осу шествляется за п циклов. В начале первого цикла распределитель 1 производит сброс блока 3 интегрирования (сортвет-. . ствуюШеё изменение выходного сигнала блока 3 интегрированияобозначено ва диаграмме 14 (фиг. 5) в по окончание с помощью входного коммутатора 2 подключает вход данного блока интог рирования ко входу феобразователя. В результате даш{ой операции входное напряжение устройства в течение интервала длительности Т интегрируется блоком 3 интегрирования (изменение выхолного,сигнала блока 3 интегрирования в этрй части цикла показано на диаграмме кривой 15), а по окончании данного интервала вход блока 3 интегрирования отключается от входа прео азователя и подключается на время Тя к выходу а алогового су мматора 5. В течение тнной части цикла выходное напряжение аналогового суммат а 5 интегрируется блоком 3 интегрирования, .а результат интегрирования алгебраически суммируется с результатом ингегр1фования входного напряжения (изменению выходного сигнала аналогового сумматора 5 в этой части цикла соответствует кривая 16). По окончании данного miTepaaла на входной коммутатор 2 подается команда отключения входа блока 3 интегрирования от выхода аналогового сумматора 5, а на выходе блока иитегр1фова-ния 1ФИ этом фикс1фуется напряжение ) в оставшейся части цикла выходное атфяжение блока 3 штегрнрования, опеделяемое вьфажен{$ем (4), остается остоянным («фивая 17). Данное напря ение интегрируется блоком 4 йнчегриованвя в течение временного 1гатервала, лительность которого Т задается распреелителем 1; на выходе блока 4 формиуется напряжение первЫ поправки (криая 18), величина фиксируется блоке yij..) , де - начальное выходное напряже- ие блока 4 интегрирования, а на ыхода г налогового сумматора 5 при ТОМ, согласно (3), формируется сответствующий сигнал (процесс формир1 ання показан, кривой 19). , . 15) Периодическое повторение описанного икла п раз обеспечивает накопление в ISnoKe 4 интегрирования требуемое аначе ние поправки ... PUU.№ (b) и а на выходе аналогового сумматора 5 формирование напряжения . . . -1 .,rq. (Т) Можно показать, что решение рекуррентного уравнения (7) имеет вид . Нетрудно заметить, что если парамет ры преобразования выбраны с учетом требования сходимости итерационного процесса -j -.1, то выходное напряжение аналогового сумматора 5 в уста новившемся режиме и при (i:)0 описы вается выражением (1), т.е. при отсут.ствии перезаряда накопительного элемен та второго блока 4 интегрирования со ответствует выходному на1тряжению идеализированного преобразователя. Однако при сопоставлении реальных устройств {(.1)5 О) становится очевидным что коэффициент влияния погрешности f(t), . обусловленный перезарядом запоминаЬще го конденсатора выходной сигнал преобразователя равен 1, в то время как сле дует из (2), соответствующий показател погрешности, обусловленный перезарядом накопительного элемента вторЬго блока интегрирования данного преобразователя равен Kij, где ) 1, Последнее выгод но отличает данный масштабный преобра зователь .от известного, поскольку Позраз уменьшить амплитуду воляет BI Щ пульсации на его выходе. Второй вариант масштабного преЬбра аователя напряжения (фиг. 2) работает следующем офазом.. Подключение сигнала ко входу блока 3 интегрирования коммутатором 2 произ водвтся заблаговременно, причем начало интервала интегрирования сдвинуто оЬносительно момента подключения на , достаточное для окончания переходных npcHieccoB в преобразователе 6. Установившееся значение выходного тока преобразователя 6, пропорциональное текуиюму значению входного сигнала блока 3 интегрирования, интегрируется далее интегратором 8, причем длительность ин егрнрования обеспечивается замыканием ключа 7 в течение соответствующего временного интервала. Достоинство данного варианта преобразователя заключается в том, что интегрирование интегратором 8 сигнала в виде тока позволяет устранить влияние сопротивления замкнутого ключа 7 на посто5пшую времени интегрирования и, следовательно, устранить погрешность линейности обусловленную зависимость постоянной времени интегрирования блока 3 интегрирования от уровня интегрируемого им сигнала; последаее обеспечивает повышение точности выполняемых блоком 3 интегрирования операций, а следовательно, и точности преофазователя в целом. Третий вариант масштабного преобразователя напряжения (фиг. 3 и 6) работает следующим образом. Достоинством данного варианта является устранение погрешности основного устройства, обусловленной сдвигом нуля и входным током 3 операционного усилителя блока 3 интегрирования. Коррекция данной погрешности в каждом цикле обеспечивается следующей последовательностью операций.. В начале цикла распределитель 1 производит сброс блока 3 интегрирования и на выходе блока устанавливается напряжение К (фиг. 6, диаграмма 2О); далее аналогично первому варианту преобразователя , блоком 3 интегрирования интегрируется входное и выходное напряжения преобразователя (соответствующие кривые на фиг. 6 обозначены 21 м 22), а результат интегрирования алгебраически суммируется с ошибкой, обусловленной влиянием величин Р и J . К концу данной части цикла йа выходе блока 3 присутствует напряжение ли,) где 1 определяется вьфажением (3) для идеализированного преобразователя ( и 3 О) С - емкость интегрирующего кояденсатора блока 3 нитегрирования. 99 В течение последующей части никла выходное напряжение блока 3. интегрирования остается неизменным (на диаграмме участок 2-3) и подается на вход бло. ка 4 интегрирования, где интегрируется в течение временного интервала фиксированной длительности Т; указанная дп1нтел ность процесса интегрирования реализуется с помощью замкнутого на время ключа 7, а условно положительное направ/1ение интегрирования задается соответствующим состоянием переключа.теля 11. В результате на выходе операционного усилителя 10, о азующего вмеоте с масштабным резистором 13 и иятеГ рирующим конденсаторс«л 12 интегрирующее звено, формируется линевно измевяю шее напряжение (на диаграмме выходное напряжение операционного усилителя Ю обозначено кривой 24), которое к концу данной части цикла достигает величиныu,,,,,(a) где - исходное напряжение на выходе операционного усилителя 1О, а постоянная времени интегрирования определяется Р сопротивлением масштабнрго резистора 13 и CQ -емкостью ингегри рующего конденсатора 12. Далее распределитель 1 производит сброс блока 3 интегрфования и выдает команду на изменение состояния переключателя 11 на, противоположное исходному. При этом на выходе операционного усилителяЮ формируется напряжение противополондаой полярности (на диаграмме показано криг вой 25), равное U,,,tn. 1) в последующей части цикла распределитель 1 с помощью входного коммутатора 2 подключает вход блока 3 ш1те1ратора к щнне нулевого потенциала в на выходе последнего в таченве интервала длительности Т 4-T,j формируется ошибка, обусловленная совместным действием величин К и:; в процессе интегрирования . (изменение выхода л о сигнала блсжа 3 : интегрИровани$| в данной части цикла показано на диаграмме 26), Данная величина в течение интервала| длительности Т интегрируется блоком 4 89 интегрирования: выходное напряжение операционного усилителя Ю изменяется в соответствии с кривой 27 (фиг. 6) и к концу интервала интегрирс ан(ш достигает величины не за сящей от.сдвига нуля и ВХОШ1017О тока операционного усилителя блока 3 интегрирование Vs,,.|-UU,.U,,Ol+ fg {uU,,,C014 ) В завершающей части цикла pact eoaлЕтелем 1.вь1Даегся команда на возращение переключателя 11 в исходное соотояние, выходное напряжение операцисяного усилителя 10 вновь изменяет свою полярность на противоположную (на диаграмме обозначено кривой 28) ,,д№-и,,,,) и на вход считывания результата интэгри рованин блока 4 интегрирования поступает сигнал переписи данного напряжения в блок 9 запоминания (изменение-выходного напряжения боока запоминания показано кривой 29) (и,,, (.5) /t - коэффициент передачи блока 9 запоминания; /X - начальное выходное напряжение блока 4 интегрирования. На выходе аналогового сумматора 5 при этом, как и в первом варианте пребразователя, формируется напряжение (на диаграмме 30) вb,чt l x Ч Jat 6Ыllto щ-« . W готЬрое не зависит от величин К и налогично вьфажения (6), (7) и (8) ожно, показать, чтои С и,,М-.... .ciii ш) О /,Х«Т гn-t1 -fc , BbixCOJ: .Г.//ЧУгГ S П (e)l

Из ((19) спецует, что обеспечив уоловие сходимости итераднонного пронесМЧ Ч

5,получаем, что выходное на-

С-УО пряжение данного варианта масштабного преобразователя быстро сходится к величине (1) и не зависит от реальных значений сдвига нуля и вводного тока опера ционного усилителя блока 3; последнее является очевидным достоинством данно го варианта устройства, поскольку позволяет повысить его точность, а также прц заданной точности использовать в составе блока 3 широкополосныеусилители со . сравнительно худшими характеристиками сдвига нуля и входного тока. В данном варианте, масштабного преобразователя напряжения п,омимо, точности может быть обеспечено и повышение быстродействия. Повышение точности здесь обеспечивается промежуточным преобразованием входного сигнала блока 3 интегрирования в выходной ток преобразователя 6 и интегрированием данного тока интегратором 8 в течение временного интервала, задаваемого ключом 7, а повышение быстродействия обеспечивается одновременным выполнением операций интегрирования бло ками 3 и 4 интегрирования (в исходном варианте этим разнесенным во времени операциям соответствуют кривые 26 и 24 (фиг. 6). Указанное совмещение операций оказывается возможным благодаря 7Х)му, что по окончании интегрирования блоком 3 интегрирования вькодаого напряжения устройство (на диаграмме обоз начено участком кривой 22) выходное, напряжение интегратора 8 фиксируется -блоком 9 запоминания, который в последуюйхей части цикла выполняет функции ферного блока запоминания, обеспечй- Бающего выдачу постояшюго напряжения на вход блока 4 интегрирования. . :Таким образом, предлагаемый масшта ный преобразователе напряжения и его варианты позволяют как И известный . масштабировать входное напряженке с масштабным коэффйцаонтом, oпpвдвиявмьш отно1иением длительности временных Roтер лов} одвако,как следует вз изложенного, в предлагаемых устройствах по , сравненшо с известным устраняется влияние ряда нестабильны :: факторов на ntan решность устройства, что выгодно отличает предлагаемое устройство от извести нотч),так как Позволяет повысить точность масштабного преобразования.

Экономический эффект использования изобретения обусловлен его техническими особенностями. Формула изобретения 1.Масштабный преобразователь напряжения, содержащий распределитель тактовых импульсов, последовательно включенные входной коммутатор и два блока интегрирования, первый вход входного коммутатора является входом маодтабного преобразователя, второй вход входного коммутатора подключен к выходу преобразователя, управляющие входы входного коммутатора и второго блока интегрирования соответственно подключе ч ны к первому и второму входам распределителя тактовых импульсов, отличающийся тем, что, с целью повьшения точности, в него введен аналоговый сумматор, первый вход которого подключен к выходу второго блока интегрирования, второй вход - к первому входу входного коммутатора, а выход - ко второму входу входного коммутатора, управляющий вход первого блока инте|. рированйя подключен к третьему выходу распределителя тактовых импульсов. 2.Масштабный преобразователь напряжения, содержащий распределитель тактовых импульсов, входной коммутатор, блок интегрирования, последовательно соединенные ключ и интегратор, первый вход входного коммутатора является входом преобразователя, второй вход входного коммутатора подключен к выходу преобразователя, управляющие входы входного коммутатора, ключа и интегратора соответственно подключены к первому, вт(Ч)ому И третьему выходам распределителя тактовых импульсов, о тл и ч а ю Щ н и с я тем, что, с. целью повышения точности, в него введены,аналоговый сумматор и преобразователь напряжения в ток, вход которого подключен к выходу входного коммутатора, а выход - к информадисяному входу ключа, выход интегратрра подключен к информационному входу блока интегрирования, выход которого Подключен к первому входу аналогового суксматора, второй вход аналогового сумматора подключен к .первому входу входно1о коммутатора, а выход - ко второму входу входного комму- татора, управляющий вход блока интег- . рированйя подключен к четвертому входу распределителя тактоьых импульсов. 13Э 3. Масштабный п|)еобраэователь напряжения, роавржащий распределитель тактовых импульсов, последовательно соеди1{енные входной коммутатор, блок интегрирования, масштабный резистор, ключ, операционный усилитель и блок aai поминания, в цепь обратной связи операц онного усилителя включены параллельно, соединенные переключатель и иноегри- рующий конденсатор, первый вход входного коммутатора является входом преобразователя, второй вход подключен к выходу преобразователя, управляющие входы входного коммутатора, ключа, переключателя и блока запоминания соответственно подключены к пеовому. второму, третьему и четвертому выходам распределителя импульсов, о .т л и ч а ю щ н и с .я тем, что, с целью повышения точности, б него введен аналоговый сумматор, первый вход которого подключен к выходу блока запомшганйя, второй выход - к первому входу входного комму татора, а выход - ко второму входу вход ного коммутатора, третий вход которого , подключен к шине нулевого потенциала. О управляющий вход блока интегрирования подключен к пятому выходу расгфеделителя тактовьк импульсов. 4, Преобразователь по п. 3, о т л и ч а ю щ,« и с я тем, что, с целью пoвь шения быстродействия, первый блок интегрирования содержит последовательно соединенные преобразователь напряжения в ток, ключ,, интегратор и блок запоминания, выход которого является выходом первого блоки интегрирования, вход преобразователя напряжения в ток является входом первого блока интегрирования, управляющие входы ключа, интегратора н .блока запоминания являются управляющими входами первого блока интегрирования и подключены соответственно к пятому, шестому и седьмому входам распределителя тактовых импульсов. Источники информации, принятые во внимание при экспертизе .1. Патент США № 3646545, кл. 34О-347, опублик.. 1972. 2. Авторское свидетельство СССР NO 619927, кл. e06Q 7/161, 1977 (ПРОТОТИП).

| название | год | авторы | номер документа |

|---|---|---|---|

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Множительно-делительное устройство | 1980 |

|

SU934494A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Время-импульсное множительное устройство | 1982 |

|

SU1048489A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU930387A1 |

| Источник калиброванных напряжений | 1979 |

|

SU860021A2 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| Устройство для моделирования упругого гистерезиса | 1980 |

|

SU966708A1 |

| Функциональный аналогоцифровой преобразователь | 1982 |

|

SU1072066A1 |

Авторы

Даты

1982-04-23—Публикация

1980-09-09—Подача