Изобретение относится к вычислительной технике и может быть ис.поль- зовано для выполнения многоканального одномерного дискретного преобразования Фурье, перемножения, матрицы сигнала на фиксированную матр ицу,вычисления двумерного дискретного преобразования Фурье,

Цель изобретения - повьшение быстродействия устройства.

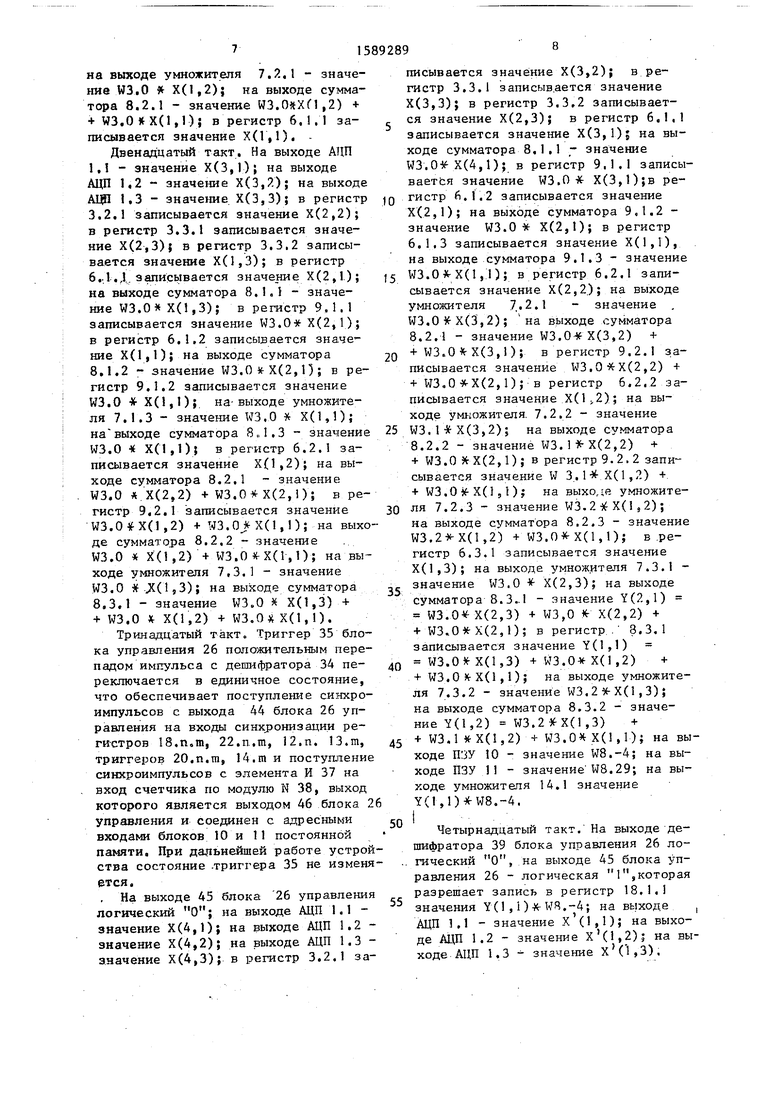

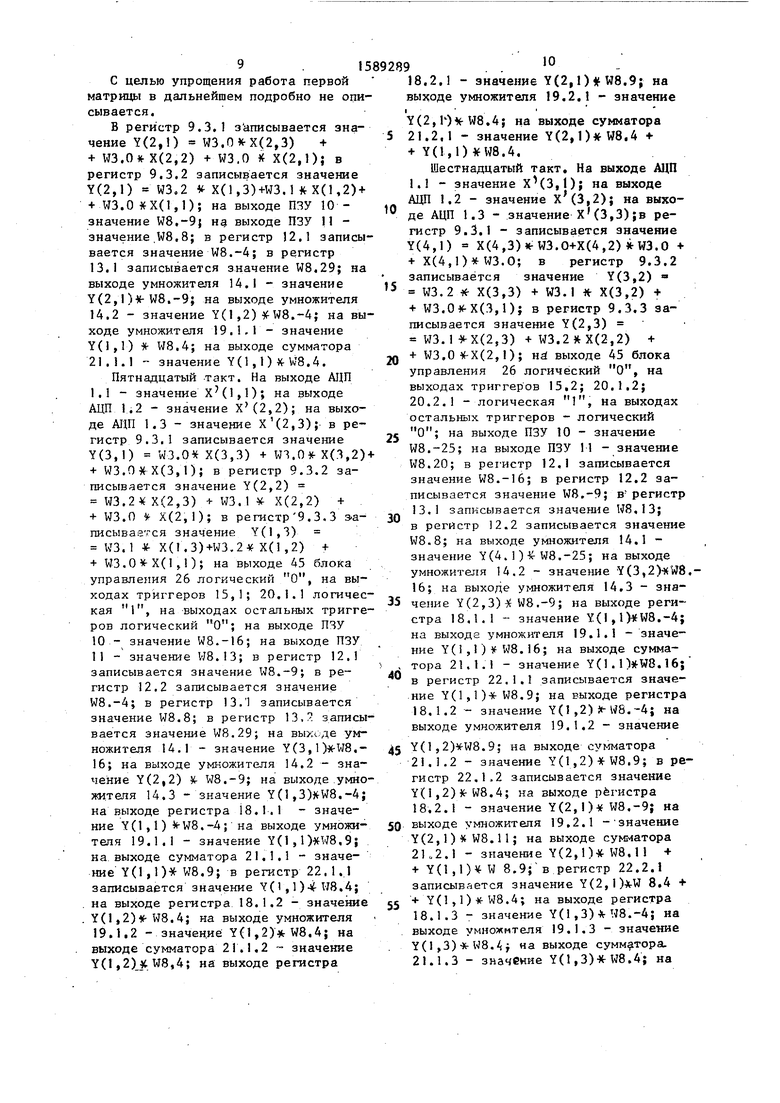

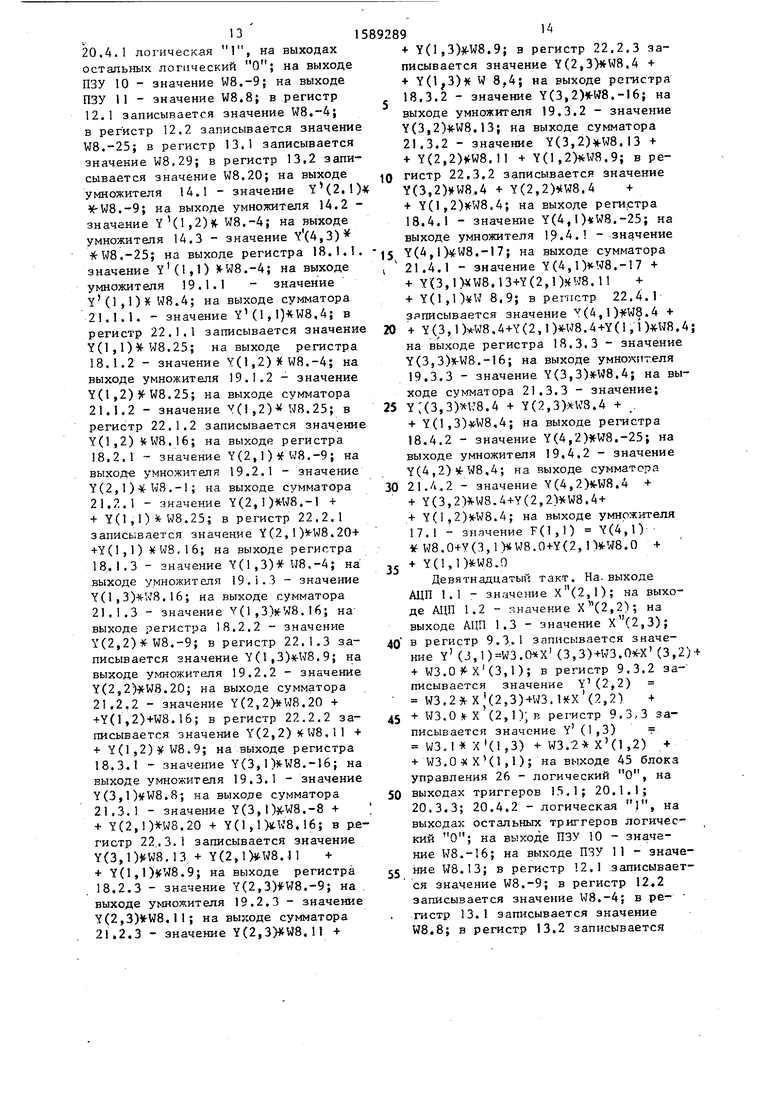

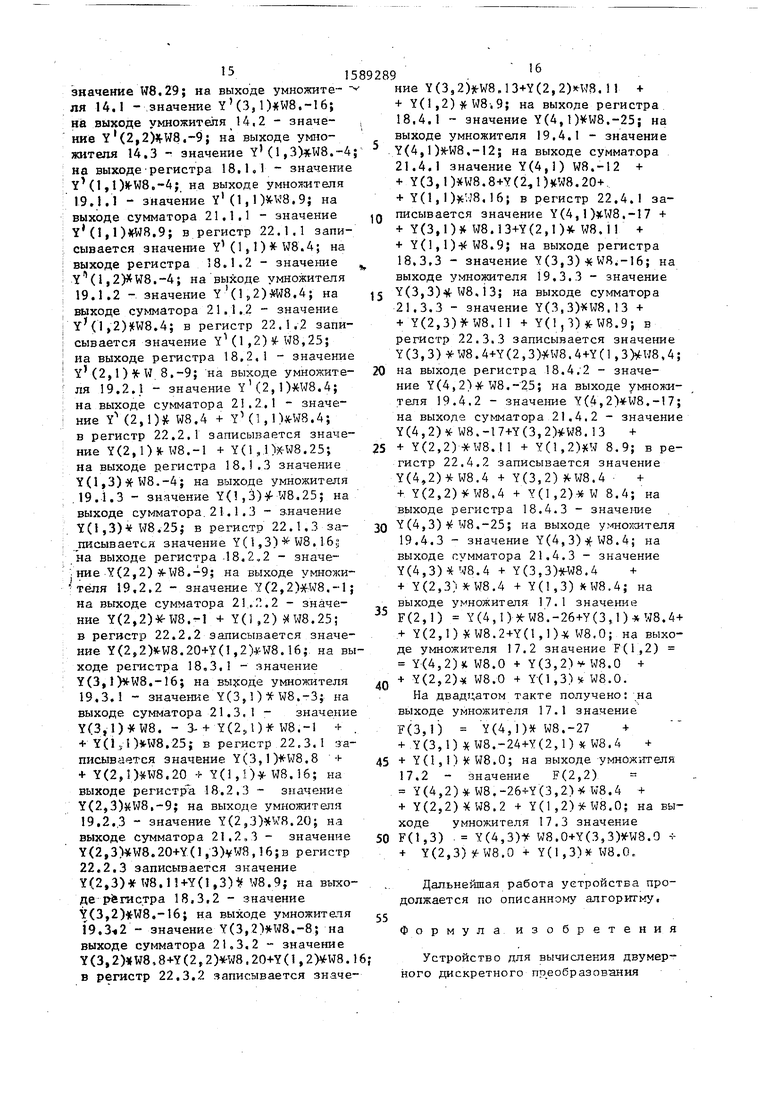

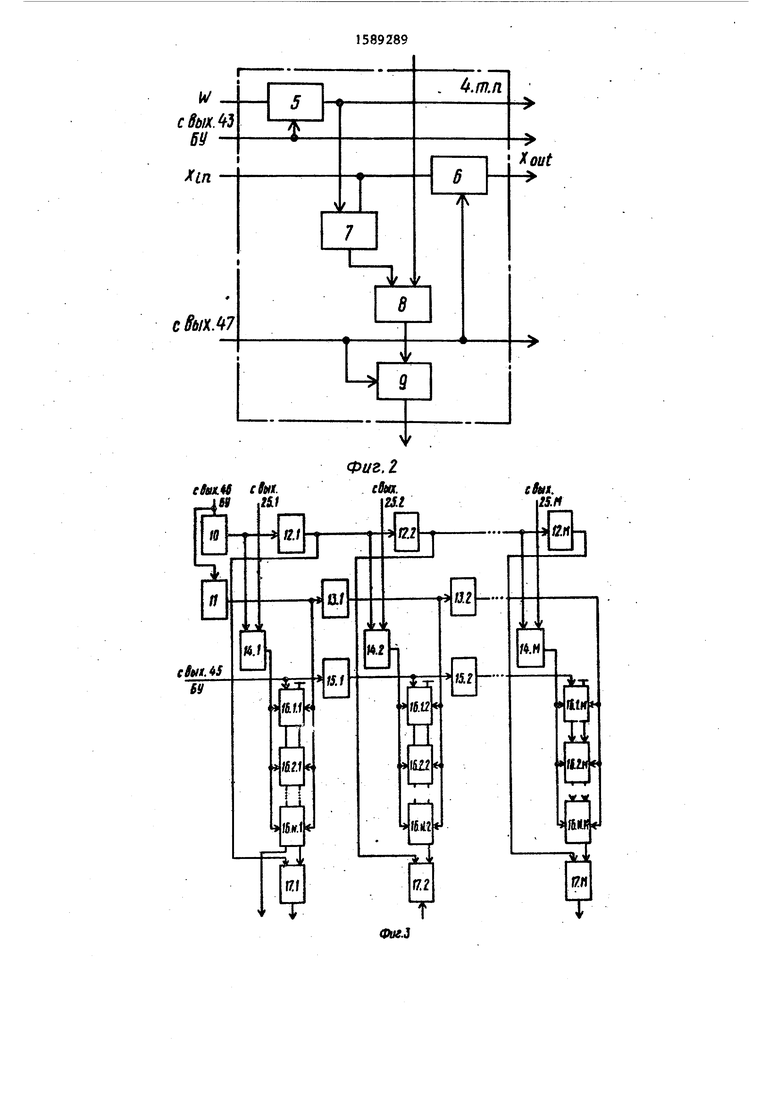

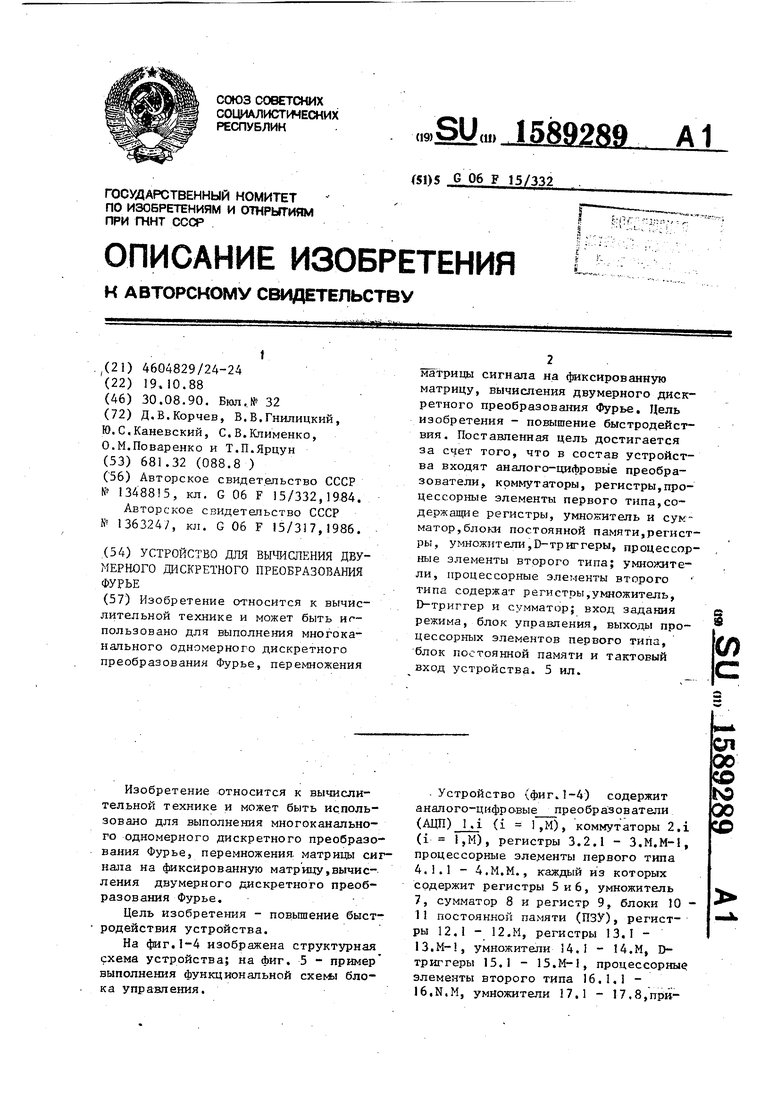

На фиг,1-4 изображена структурная схема устройства; на фиг, 5 - пример выполнения функциональной схемы блока управления.

Устройство (фиг.1-4) содержит аналого-цифро-вые преобразователи (АЦП) (i ), коммутаторы 2.i (i l,M), регистры 3,2,1 - 3,М,М-1, процессорные элементы первого типа 4.1.1 - 4,М,М., каждый из которых содержит регистры 5 и 6, умножитель 7, сумматор 8 и регистр 9, блоки 10 - 11 постоянной памяти (ПЗУ), регистры 12.1 - 12.М, регистры 13,1 - 13.М-, умножители 14.1 - 14.М, D- триггеры 15.1 - 15,М-1, процессорны элементы второго типа 16.1,1 - le.N.M, умножители 17.1 - 17.8,приСП

с

CD

00

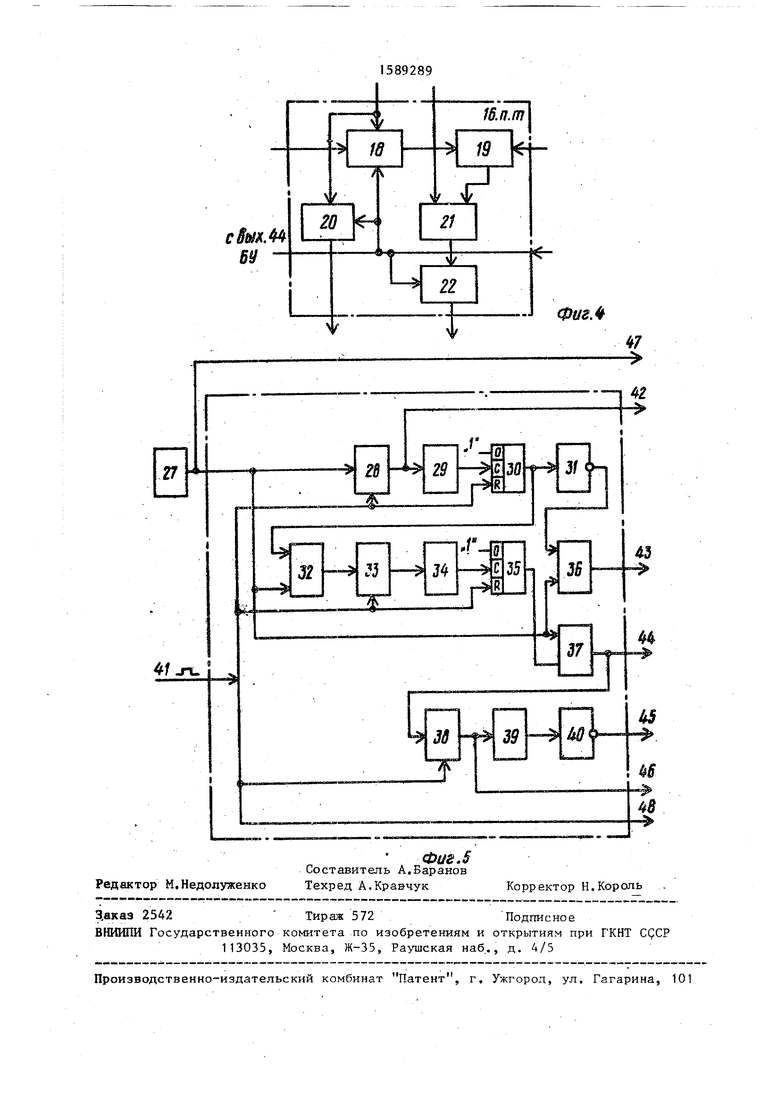

чем процессорный элемент второго ти- ;па (фиг.4) содержит регистр 18,умножитель 19, 1)-триггер.20, сумматор 21 и регистр 22, вход задания режима устройства 23, блок 24 управления, выходы 25,1 - 25,М процессорных элементов первого, типа, блок 26 постоянной памяти, тактовый вход устройст- ;ва 21.

Блок 24 управления (фиг.5) содер- жит счетчик по модулю МЛ 2+1 28,де- j шифратор 29, триггер 30, элемент НЕ I 31, элемент И 32,- счётчик 33, деши(- i ратор 34, триггер 35, элемент И 36, элемент И 37, счетчик 38, дешифра- I тор 39, элемент НЕ 40, выхода 41 : 48.

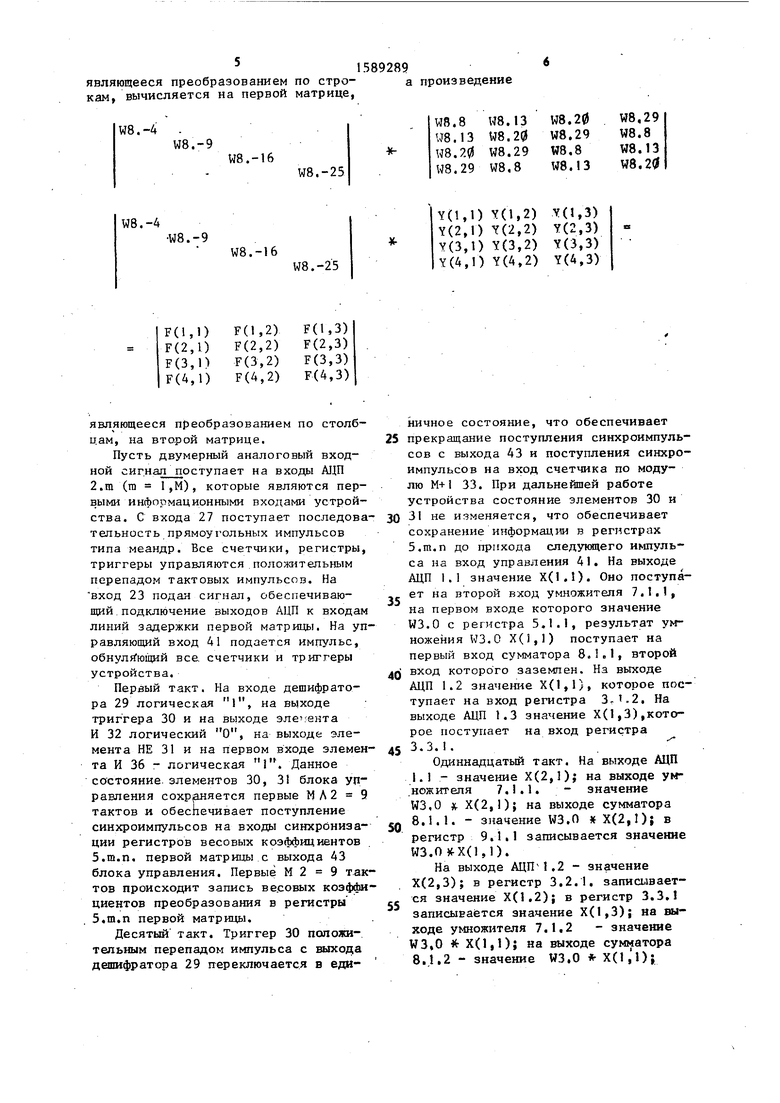

: Рассмотрим работу устройства в режиме вычисления двумерного ДПФ. Устройство вычисляет следующее выражение :

F(N,M) G(N)r(N)-G(N) (X(N,M) Е(М)),

(1)

где Е(М) - квадратная матрица весовых коэффициентов;

М - точечного одномерного :ДПФ;

X(N, М) - матрица входных двумерных данных, содержащая М столбцов и N строк; r(N) - лево-циркулярная матрица с элементами вида r(i,k) W.2N.i+k)+4; G(N) - диагональная матрица;

G(N) diag(W.2N.-4,W.2N.-Y,..., ...,W.2N.-(i+l)A2,...,W.2N. - - (N+l)Л 2);

W.N.n expC-jZn n/N),

F(N,M) - выходная матрица коэЛЛициента преобраэования; W - символ весового коэффициента;

- символ умножения; Л - символ возведения в степень;

Дан описания работы устройства примем , . В этом случае выражение (1) имеет вид:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1508233A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1697085A1 |

| Параллельное устройство для вычисления двухмерной свертки | 1985 |

|

SU1269237A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1989 |

|

SU1619299A1 |

| Устройство для вычисления двухмерного преобразования фурье | 1989 |

|

SU1661790A1 |

| Устройство для цифровой двумерной свертки | 1986 |

|

SU1363250A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1499374A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1802363A1 |

Изобретение относится к вычислительной технике и может быть использовано для выполнения многоканального одномерного дискретного преобразования Фурье, перемножения матрицы сигнала на фиксированную матрицу, вычисления двумерного дискретного преобразования Фурье. Цель изобретения - повышение быстродействия. Поставленная цель достигается за счет того, что в состав устройства входят аналого-цифровые преобразователи, коммутаторы, регистры, процессорные элементы первого типа, содержащие регистры, умножитель и сумматор, блоки постоянной памяти, регистры, умножители, Д-триггеры, процессорные элементы второго типа, умножители. Процессорные элементы второго типа содержит регистры, умножитель, Д-триггер и сумматор

вход задания режима, блок управления, выходы процессорных элементов первого типа, блок постоянной памяти и тактовый вход устройства. 5 ил.

W3. W3.0 W3.( W3.0 W3.1 W3.2 W3.0 W3.2 W3.1

Произведение

X(l,l)Х(Ь2)Х(1,3)

Х(2,1)Х(2,2)Х(2,3)

Х(3,1)Х(3,2)Х(3,3)

Х(4,1)Х(4,2)Х(4,3)

Y(l,l)Yd,2)Y(I,3

Y(2,l)Y(2,2)Y(2,3)

Y(3,l)Y(3,2)Y(3,3)

Y(4,l)Y(4,2)Y(4,3)

W8.-16

W8.-25

(2)

W3.0 W3-.( W3.0 W3.0 W3.1 W3.2 W3.0 W3.2 W3.1

(3)

являющееся преобразованием по строкам, вычисляется на первой матрице,

W8.-4

W8.-9

W8.-16

W8.-25

W8.-4

W8.-9

W8.-16

W8.-25

являющееся преобразованием по столбцам, на второй матрице.

Пусть двумерный аналоговый входной сигнал поступает на входы А1ДП 2.т (га 1,М), которые являются первыми информационными входами устройства, С входа 27 поступает последовательность прямоугольных импульсов типа меандр. Все счетчики, регистры, триггеры управляются положительным перепадом тактовых импульсов. На вход 23 подан сигнал, обеспечивающий подключение выходов АЦП к входам линий задержки первой матрицы. На уп равляюЕЦИй вход 41 подается импульс, обнул юш:ий все. счетчики и триггеры устройства.

Первый такт. На входе дешифратора 29 логическая 1, на выходе триггера 30 и на выходе эле ::ента И 32 логический О, на выходе элемента НЕ 31 и на первом входе элеме та И 36 - логическая I, Данное состояние, элементов 30, 3 блока управления сохр|аняется первые МЛ2 9 тактов и обесЬечивает поступление синхроимпульсов на входы синхронизации регистров весовых коэффициентов 5,m,n, первой матрицы с выхода 43 блока управления. Первые М 2 9 так тон происходит запись ве.совых коэффи циентов преобразования в регистры 5.m.n первой матрицы.

Десятый такт. Триггер 30 положительным перепадом импульса с выхода дешифратора 29 переключается в еди1589289

а произведение

W8.20

W8.29

W8.8

W8.13

W8,29 W8.8 W8.13 W8.2(

Y(l,l) У(1,2)V(J,3)

Y(2,l) Y(2,2)Y(2,3)

Y(3,l) Y(3,2)Y(3,3)

Y(4,l) Y(4.2)Y(4,3)

ничное состояние, что обеспечивает 25 прекращание поступления синхроимпульсов с выхода 43 и поступления синхроимпульсов на вход счетчика по модулю М+1 33, При дальнейшей работе устройства состояние элементов 30 и 30 31 не изменяется, что обеспечивает сохранение информации в регистрах 5,m,n до прихода следующего импульса на вход управления 41. На выходе АЦП 1.1 значение Х(1.1), Оно поступает на второй вход умножителя 7.1., на первом входе которого значение W3.0 с регистра 5.1.1, результат умножения W3.0 Х(1,1) поступает на первый вход сумматора 8.1.1, второй лп вход которого заземлен. На выходе

АЦП 1.2 значение. Х(1,1), которое поступает на вход регистра 3л .2. На выходе АЦП 1,3 значение Х(1,3),которое поступает на вход регистра

5 -3 I

, J, 1 .

Одиннадцатый такт. На выходе АЦП 1,1 - значение Х(2,1); на выходе ум- .ножителя 7.1.1. - значение W3.0 jt Х(2,); на выходе сумматора 8.1,1. - значение W3.О Х(2,1); в регистр 9.1.1 записывается значение W3.n)tX(l,l).

На выходе .2 - значение Х(2,3); в регистр 3.2.1. записывается значение Х(1.2); в регистр 3.3.1 записывается значение Х(1,3); на выходе умножителя 7.1.2 - значение W3,0 t Х(1,1); на выходе сумматора В..1,2 - значение W3.0 «-ХС,);

45

50

55

на выходе умножителя 7.2,1 - значе- гае W3,0 Jt Х(1,2); на выходе су:мма- тора 8.2.1 - значение WS.OftXfl.Z) + W3.(1,1); в регистр 6,1,1 записывается значение Х(Г, 1). Двенадцатый такт. На выходе АЦП 1,1 - значение Х(3,1); на выходе АЦП 1,2 - значе ше Х(3,/); на выходе А1Щ 1,3 - значе1ше ХСЗаЗ); в регистр

W3.0 Х(1 ,2) + W3.(1,1); на выходе умножителя 7.3.1 - значение W3.0 #.Д(1,3); на выходе сумматора 8,3.1 - значение W3.0 3( Х(1,3) + + W3,0 Х(Г,2) + W3.0 Х(1,),

Тринадцатый такт. Триггер 35 блока управления 26 положительным перепадом импульса с дешифратора 34 переключается в единичное состояние, что обеспечивает поступление сизихро- импульсов с выхода 4А блока 26 управления на входы синхронизации регистров 18.п,т, 22.п..т, 12.п. 13.т, триггеров 20.п.т, 14.m и поступ-пение синхроимпульсов с элемента И 37 на вход счетчика по модулю К 38, выход которого является выходом 46 блока 2 управления и соединен с адресными входами блоков 10 и 11 постоянной памяти. При дальнейшей работе устройства состояние .триггера 35 не изменяется ,

, На выходе 45 блока 26 управления логический на выходе АЦП 1.1 - значение Х(4,1); на выходе АЦП 1.2 - значение Х(4,2); на выходе АЦП 1.3 - значение Х(4,3); в регистр 3.2.1 за

6 10

15

89289S

писывается значение Х(3,2); в регистр 3.3.1 записывается значение Х(3,3)} в регистр 3.3.2 записывается значение Х(2,3); в регистр 6,1,1 записывается значение X(3,l)j на выходе сумматора 8,1 .1 ,- значение W3.0-) Х(4,1); в регистр 9,1.1 записы- ваетья значение ЫЗ.П Х(3,1);в регистр 6.1.2 записывается значение Х(2,1); на выходе сумматора 9,1.2 - значение W3.0 it Х(2,); в регистр 6.1,3 записывается значение Х(1,1), на выходе сумматора 9.1.3 - значение W3.(1, 1); в регистр 6.2.1 записывается значение Х(2,2.); на выходе умнояштеля 7,. 2.1 - значение . W3.0 (-Х(3,2); на выходе ч-умматора

+ (3,1); в регистр 9.2.1 з.а- писывается значение W3.0 (2,2) + + (2,1); в регистр 6.2,2 записывается значение Х(1v2); на выходе умножителя. 7.2.2 - значение W3.(3,2); на выходе сумматора

+ W3.0 Х-Х(2,1); в регистр 9.2.2 записывается значение W 3.(1,Л) + + W3.0{ Х(151); на выходе умножителя 7.2.3 - значение W3. 2-) Х(, 2); на выходе сумматора 8.2.3 - значение W3.(I,2) + W3.(l,l)j в .регистр 6,3.1 записывается значение Х(1,3); на выходе умножителя 7.3.1 - значение W3.0 - Х(2,3); на выходе сумматора 8.3..1 - значение Y(2,l) W3.(2,3) + W3,0 Х(2,2) + + W3.(2,1); в регистр . 8.3.1 записывается значение Y(l,l) W3.(1,3) +W3.(1,2) + + W3.0 Х-Х(1,1) ; на выходе умножителя 7.3.2 - значение W3,2 Х( 1,3); на выходе сумматора 8.3.2 - значение Yd,2) W3.(,3) + 45 + W3.1 X(I,2) + W3.0H Х(1,1)} на выходе ПЗУ 10 - значение W8.-4; на выходе ПЗУ 1 1 - значение W8.29; на выходе умножителя 14.1 значение Y(l,l)W8.-4.

20

25

30

35

40

Четырнадцатый такт. На выходе дешифратора 39 блока управления 26 логический О,,на выходе 45 блока управления 26 - логическая 1,которая разрешает запись в регистр 18.1. значения Y(1 ,1) -Х- W8. на выходе , АЦП 1.1 - значение х (,1) выходе АЦП 1.2 - значение )j на выходе АЦП 1.3 -

значение X (1,3).

С целью упрощения работа первой атрицы в дальнейшем подробно не опиывается.

В регистр 9.3.1 записывается зна ение Y(2,l) W3.0 « Х(2,3) + W3.(2,2) + W3.0 Х(2,1); в егистр 9.3.2 записывается значение (2,l) W3,2 1 X(l,3)+W3.Ht Х(1,2) + W3.0 (Х(1,1); на выходе ПЯУ 10 - значение W8.-9j на выходе ПЗУ 11 - значение,W8.8; в регистр 12.1 записывается значение W8.-4; в регистр

Пятнадцатый такт. На выходе А1ДП 1.1 - значение х (1,1); на выходе АЦП 1.2 - значение Х (2,2); на выходе АЦП 1.3 - значение Х (2,3); в регистр 9.3.1 записывается значение Y(3,l) W3.0( Х(3,3) + W3.0(-Х(3,2)-1- + W3.0XX(3,1); в регистр 9.3.2 записывается значение Y(2,2) W3.(2,3) + W3.1 Х(2,2) + + W3.n Х(2,1); в регистр 9.3.3 з-а- писывается значение У(1,3) W3.1 X(r.3)+W3. Х(1,2) + + W3.0 Х(1 ,1) ; на выходе 45 блока управления 26 логический О, на выходах триггеров 15,1; 20.1.1 логическая 1, на выходах остальных триггеров логический на выходе ПЯУ

10- значение W8.-16; на выходе ПЗУ

11- значение VJ8.13; в регистр 12.1 записывается значение W8.-9; в регистр 12.2 записывается значение W8.-4; в регистр 3, 1 записывается значение W8.8; в регистр 13.л записывается значение W8.29; на выходе умножителя 14.1 - значение Y(3,1 )(-W8,- 16; на выходе умножителя 14.2 - значение Y(2,2) Х- W8.-9; на выходе умно- зштеля 14.3 - значение Y(l ,3)W8.-4; на выходе регистра 18.1.1 - значение Y(l, 1) VW8.-4; на выходе умножителя 19.1.1 - значение Y(1,1)W8.9| на выходе сумматора 21.1.1 - значение Y(l ,}) W8.9; в регистр 22. 1 ..1 записывается значение Y(1,1)4H8.4; на выходе регистра 18.1.2 - значение

Y(l ,2)if-W8.4; на выходе умножителя 19.1.2 -значение Y(l,2) W8.4; на выходе сумматора 21.1.2 - значение Y(l,2)jC W8,4; на выходе регистра

0

5

Y(2,.4; на выходе сумматора 21.2,1 - значение Y(2,1)#W8.4 + + Y(l,l))fW8.4.

Шестнадцатый такт. На выходе А11П 1.1 - значение хЧЗ,1); на выходе АЦП 1.2 - значение х (3,2); на выходе АЦП 1.3 - значение Х (3,3);в регистр 9.3.1 - записывается значение Y(4,l) X(4,3)ieW3.0+X(4,2) W3.0 + + Х(4,1) W3.0; в регистр 9.3.2 записывается значение Y(3,2) W3.2 Х(3,3) + W3.1 Х(3,2) + + W3.(3,1)} в регистр 9.3.3 записывается значение Y(2,3) W3.1 )X(2,3) +W3.(2,2) + + W3.(2,1); Hd выходе 45 блока управления 26 логический О, на выходах триггеров 15.2; 20.1.2;

в регистр 12.2 записывается значение W8.8; на выходе умножителя 14.1 - значение (4. 1)-if W8.-25; на выходе умножителя 14,2 - значение Y(3,2)(W8.- 16; на выходе умножителя 14.3 - зна- 5 чение (2,3)- W8.-9; на выходе регистра 18.1.1 - значение У(1,l)W8.-4; на выходе умножителя 19.1.1 - значение (i,1) W8.16; на выходе сумматора 21.1.1 - значение (1. .16; в регистр 22.1.1 записывается значение (1,1)-(-W8.9; на выходе регистра

5 Y(1,2)W8.9; на выходе сумматора

0

0

0

5

выходе регистра 18.2.2 - значение Y(2,2) fW8.-9; на выходе умножитепя 19.2.2 - значение Y(2,2)# W8.4| на выходе сумматора 21.3.1 - значение Y(2,2) W8. ;t + Y(l,3)( W8.A5 на выходе регистра 18.3.1 - значение Y(3,l) W8.-16; на выходе умножителя 19.3.1 - значение Y(3,1)W8.4; на выходе сумматора 21.3.1. - значение Y(3,l)i W8.4 + Y(2,l) W8.4 + + Y(l,l) W8,4..

Семнадцатый такт. На выходе АПП 1.1 - значение х (4,1); на выходе А1Щ 1.2 - значение Х (4,2); на вы- ходе АЦП 1.3 - значение Х (4,3); в регистр 9.3.1. записывается значение Y4r,l)W3.,3)+W3.,2) + + W3.0 ХЧ1,1)в регистр 9.3.2 записывается значение Y(4,,2) W3.(4,3) «- W3.(4,2) + + W3.(4,l), в регистр 9.3.3 записывается значение Y(3,3) W3.H«- Х(3,3) + W3.2 Х(3,2) + Х(3,1)} на выходе 45 блока управления 26 логический на выходах триггеров 20.1.3; 20.2.2; 20.3.1 логическая 1, на выходах .остальных триггеров - логический О на выходе ПЗУ 10 - значение W8.-4;; на выходе ПЗУ П - значение W8.29,, в регистр 12.1 записйвается значе1«1е W8.-25; в регистр 12.2 записывается значение W8.-16; в регистр 13.1 записывается значение W8.20; в регистр 13.2 записывается значение W8.13; на выходе умножителя I4.I - значезние Y (1 ,1) W8.-4J на выходе умножшчапя 14.2 - значение Y(4,2)1( W8.-25; на вькоде умножителя 14,3 - значение Y(3,3) W8.-16; на выходе регистра 18.1. - значение Y(l,1) W8.-4; на выходе умножителя 19.1.1 - значение Y(l,l)itW8.25; на выходе сумматора 21.1.1 - значение Y(1, О W8.25; в регистр 22.1.1 записывается значение Y(1 ,1)W8,16; на выходе регистра 18.1.2 - значение Y(1,2) lfW8.-4; на выходе умножителя 19.1.2 - значение Y(l j2)-«-W8. J6; на выходе суммато ра 21.1.2 - значение Y(l,2)WS.16; в регистр 22,1.2 записывается значение Y(1,2)W8,9; на выходе регистр 18.2.1 - значение Y(2,l)-Sf W8.-9; на выходе умножителя 19.2.-1 - значение Y (2, l)lt W8,20; на выходе сумматора 21.2.1 - значение Y(2,l) W8.20 + + Y(1,1)W8.16; в регистр 22.2.1 записывается значение Y(2,1) W8.11

+ Y(I,1)W8.9; на выходе регистра 18.1.3- значение Y(1 ,3HW8.-4; на выходе умножителя 19.1.3 - значение Y(l ,3) W8.9; на выходе сумматора 21.1.3 - значение Y(1 ,3)-(-W8,9; в ре гистр 22.1.3 записывается значение Y(1,3)W8.4; на выходе регистра 18.2.2 - значение Y(2 ,2)-Х-У8.-9;на выходе умножителя 19.2.2 - значение Y(2,2) W8.ll; на выходе сумматора

+ Y(l,2) ifW8,9; в регистр 22.2.2 записывается значение Y(2,2)W8.4 + ч- Y(l,2)-)i. W 8,4; на выходе регистра

Y(l , 1) Jt-W8.4; на выходе регистра

+ Y(l ,3) W8. 4; на выходе регистра

на выходе умножителя 19.3.2 - значение Y(3,2)W8.4; на выходе сумматора 21.2.3. - значение Y(2,3)-«-W8.4 -f- + Y(l,3) W8.4; на выходе регистра 18.3.2 - значение Y(3,2)J(-W8.-16; на выходе умножителя 19.3.2 - значение Y(3,2) .4; на выходе сумматора

на выходе сумматора 21.4.1 - значение Y(4,l ) W8.4 + Y(3, 1 ) W8.4 + + Y(2,t) W8.4 + Y(1,1)W8.4.

Восемнадцатый такт. На выходе АЦП 1.1- значение X (1,О; на выходе АЦП 1.2 - значение Х (1,2); на выходе АЦП 1.3 - значение Х (); в регистр 9.3.1 записывается значение Y42,l) W3.(2,3) + +W3.,2) + W3.n t-X42,l); в регистр 9,3.2 записывается значение Y (1,2)W3.(1,3)+W3.RX (1,2) + + W3.WX (1,O; в регистр 9.3.3 записывается значение ,Y(4,3) W3.H(-X(4,3) + W3.2-)(-X(4,2) + + W3.Q-«-Х(4,); на выходе 45 блока 26 управления логическая , на выходах триггеров 20.2.3; 20,3.2;

13

+ Y(l,l)vW8.9; на выходе регистра 18.2.3 - значение y(2,3)-)(-W8.-9; на выходе умножителя 19.2.3 - значение y(2,3)1(-W8.1 1 ; на выходе сумматора

89289

14

10

20

25

+ Y(l,3)W8.9; в регистр 22.2.3 записывается значение Y(2,3XW8.4 + + У(1,3) W 8,4; на выходе регистра 18.3.2 - значение Y(3,2)«-W8.-16; на

выходе умножителя 19.3.2 - значение Y(3,2)-W8.13; на выходе сумматора 21.3.2 - значение Y(3,2)W8.13 + + Y(2,2)tW8.11 + Y(l,.9; в регистр 22.3.2 записывается значение YC3,2HW8.4 + y(2,2)W8.4 + + Y(l ,2)i(-W8.4; на выходе регистра

15 Y(4,1)W8.-17; на выходе сумматора 21.4.1 - значение Y(4,.-17 + + y(3,l(W8.13-bY(2,l))W8.11 + + Y(1,1)W 8.9; в регистр 22.4.1 записывается значение У(4,1 )-)fW8.4 + + Y(3,l)W8,4+Y(2,l)-W8.4+Y(r,l)W8.4; на выходе регистра 18.3.3 - значение Y(3,3)-W8.-16; на выходе умножителя 19.3.3 - значение Y(3,3)-W8.4; на выходе сумматора 21.3.3 - значение; Y:(3,3)W8.4 + Y(2,3XW8.4 + . + Y(l ,3)-)tW8,4; на выходе регистра

+ y(3,2)WB.4+y(2,2)W8.4+ + Y(1,2)W8.4; на выходе умножителя 17.1 - значение F(l,1) У(4,1) If W8.0+y(3,.0+Y(2,.0 + + y(l,l):W8.0

Девятнадцатый такт. На. выходе АЦП 1.1 - значение х(2,1); на выходе МЩ 1.2 - значение х(2,2); на выходе АЦП 1.3 - значение х(2,3); в регистр 9.3.1 записывается значение у (J,1)W3. (3,3)+W3.(3,2)-«- + W3.0 )«-Х (3,1); в регистр 9.3.2 записывается значение У (2,2) W3.29i-X,42,3)+W3.UX (7.,2) + + W3.0 х (2,1); в регистр 9.3,3 записывается значение У (Ij3) W3.X41,3) + W3.-2 Х (1,2) ,+ + W3.0-х ХЧ1,1); на выходе 45 блока управления 26 - логический О, на выходах триггеров 15.1; 20.1.1; 20.3.3; 20.4.2 - логическая 1, на выходах остальных триггеров логический на выходе ПЗУ 10 - значение W8.-16; на выходе ПЗУ 11 - значение W8.13; в регистр 2.1 записывается значение W8.-9; в регистр 12.2 заш1сывается значение W8.-4; в регистр 13.1 записывается значение W8.8; в регистр 13.2 записывается

30

35

40

45

50

15

1589289

значение W8.29; на выходе умножите- ля 14.1 -.значение Y (3,1)W8.-16; на выходе умножителя 14,2 - значе- ние Y (2,2)t-W8.-9; на выходе умно- жителя 14.3 - значение Y (1,3)W8.-4 на выходе регистра 18.1,1 - значение Y4l,l) W8.-4; на выходе умнолмтеля 19.1.1 - значение Y (1, 1 . 9; на выходе сумматора 21.1.1 - значение : Y(1,1)W8.9; в регистр 22.1.1 запи- : сывается значение Y (1,1) -W8.4; на выходе регистра 18.1.2 - значение Y (i ,2)W8.-4; на выходе умножителя : 19.1.2 - значение Y (U2)W8.4; на : выходе сумматора 21.1.2 - значение ; Y ())tW8.4; в регистр 22.1.2 запи- I сывается значение Y (1 2) W8,25; i на выходе регистра 18.2.1 - значение Y (2,1)W 8.-9; на выходе умножите- ( ля 19.2.1 - значение Y (2,1)XW8.4; на выходе сумматора 21.2.1 - значе- I ние Y (2,1) W8.4 + Y4l,l)W8.4; в регистр 22.2.1 записывается значение Y(2, 1 ) К W8.-1 + Y(l,nx-W8.25; на выходе регистра 18.1.3 значение Y(l ,3) W8.-4; на BMxojqe умножителя .19.1.3 - значение Y(l,3)f W8.25; на выходе сумматора. 21.1.3 - аначение Y(l,3)f W8.25| в регистр 22.1.3 за- : писывается значение Y(l ,3) W8.16; : на выходе регистра .18.2., 2 - значе- /ние Y(2,2) W8.-9; на выходе умножи- теля 19.2.2 - значение Y(2,2):)fW8.-l; на выходе сумматора 21,2.2 - значение Y(2,2))W8.-1 + Y(i,2) W8.25; в регистр 22.2.2 записывается значение Y(2s2XW8.20+Y(l,.16; на выходе регистра 18,3.1 - значение Y(3, )V-W8.-16; на выходе умножителя 19.3,1 - значение Y(3,l)-if W8.-3; на выходе сумматора 21.3,1 - значение Y(3,)W8. - 3-+ Y(2.,l) W8.-1 +

+ Y(1.,S)-W8.25; в регистр 22,3.1 записывается значение Y(3, ) t(-W8.8 + + Y(2,,1)W8.20 ( Y(l,r)W8.16; на выходе регистр 18.2,3 значение Y(2,3)i(W8,-9; на выходе умножителя 19.2.3 - значение Y(2,3)4W8.20; на выходе сумматора 21.2,3 - значение Y(2,3XW8.20+Y(1,3)W8,16;в регистр 22.2.3 записывается значение Y(2,3) W8.n+Y(l,3)1 W8.9J на выко- де регистра 18.3.2 - значение Y(3,2HW8.-16; на выходе умножите-чя 19.3ч2 - значение Y(3,2)W8.-8; на выходе сумматора 21.3.2 - значение Y(3,2)W8.8+Y(2,2)W8,20+Y(1,2)W8. в регистр 22.3.2 записывается значе16

0

0

5

ние Y(3,2)i(-W8 Л 3-t-Y(2, 2)xrW8. П + + Y(1,2)W8.9; на выходе регистра 18,4.1 - значение Y(4,1)W8.-25; на выходе умножителя 19.4.1 - значение Y(4,1)W8.-12; на выходе сумматора 21.4.1 значение Y(4,l) W8.-12 + + Y(3,.8+Y(2, l)tW8.20+. + Y(l, l)t;J8.6; в регистр 22.4.1 записывается значение Y(4,1)W8.-17 + + Y(3,l)t W8.13+Y(2,l)t W8.ll + Y(l, 1 )- W8.9; на выходе регистра 18.3.3 - значение Y(3,3) W8.-16; на выходе умножителя 19.3.3 - значение

5 Y(3,3) W8.13; на выходе сумматора 21.3.3 - значение Y(3,3)XW8,13 + + Y(2,3)W8,11 + Y(l,3)tWB.9; в регистр 22.3.3 записывается значение Y(3,3)W8.4+Y(2,3)-)tW8.4+Y(l,3V-U8,4; на выходе регистра 18.4. 2 - значение Y(4, 2)-Х-W8.-25; на выходе умножителя 19.4.2 - значение Y(4, .-1 7; на выходе сумматора 21.4,2 - значение Y(4,2) W8.-17+Y(3,2)-)tW8. 13 + + Y(2,2)W8.11 + Y(1,2)W 8.9; в регистр 22.4.2 записывается значение Y(4,2) W8,4 + Y(3,2) W8.4 + + Y(2,2)W8,4 + Y(l,2)- W 8.4; на выходе регистра 18.4.3 - значение

30 Y(4,3)- W8.-25; на выходе у гно ;штеля 19.4.3 - значение Y(4, 3)-jf W8. 4; на выходе сумматора 21.4.3 - значение Y(4,3) W8.4 + Y(3,3)f-W8.4 + + Y(2,3) W8.4 + Y(l,3) tW8.4; на выходе умножителя 17.1 значение F(2,l) Y(4,.-26+Y(3,l) W8.4-f + Y(2,l) XW8.2+Y(l,) W8.0; на выходе умножителя 17.2 значение F(l,2) Y(4,2)K W8.0 + Y(3,2)-W8.0 + + Y(2,2)( W8.0 + Y-(l,3)4 W8.0.

Ha двадцатом такте получено;;на выходе умножителя 17.1 значение

FOjO Y(4,l) W8.-27 + ,Y(3,1) W8.-24+Y(2,l) W8.4 + + Y(l, I) f W8.0; на выходе умнож;ггеля 17.2 - значение F(2,2) , Y(4,2) W8.-26+Y(3,2)4W8.4 + + Y(2,2)W8.2 + Y(l ,2)7tW8.0; на выходе умножителя 17.3 значение 50 F(l,3) . Y(4,3)y W8.0+Y(3,3)V-W8.0 v + Y(2,3) if W8.0 + Y(l ,3)f W8.0.

35

40

45

Дал.ьнейшая работа устройства продолжается по описанному алгоритму.

Формула изобретения

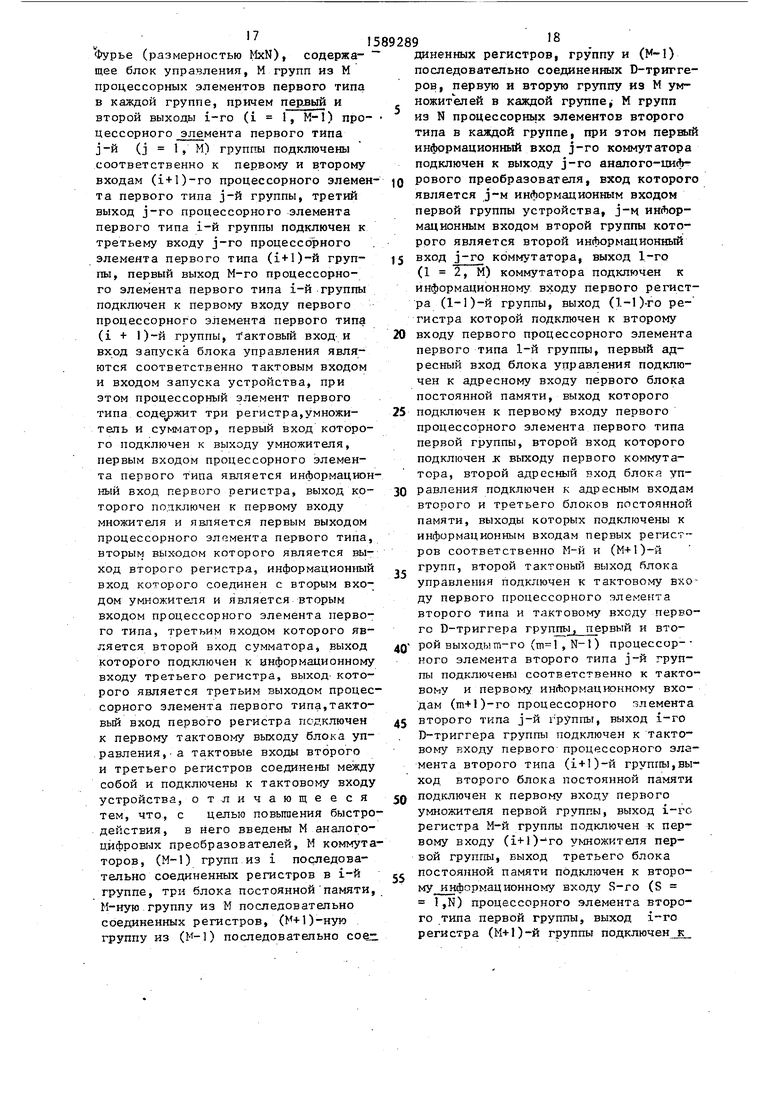

Устройство для вычисления двумерного дискретного пр еобразования

17

Фурье (размерностью lxN), содержа- щее блок управления, М групп из М процессорных элементов первого типа в каждой группе, причем пердый и второй выходы i-ro (i 1, М-1) про- цессорного элемента первого типа j-й (J 1, М) группы подключены соответственно к первому и второму входам (i+l)-ro процессорного элемента первого типа j-й группы, третий выход j-ro процессорного элемента первого типа i-й группы подключен к третьему входу j-ro процессбрного элемента первого типа (1+1)-й группы, первый выход М-го процессорного элемента первого типа i-й группы подключен к первому входу первого процессорного элемента первого типа (i + 1)-й группы, т актовый вход-и вход запуска блока управления являются соответственно тактовым входом и входом запуска устройства, при этом процессорный элемент первого типа содержит три регистра,умножитель и сумматор, первый вход которого подключен к выходу умножителя, первым входом процессорного элемента первого типа является информационный вход первого регистра, выход которого подключен к первому входу множителя и является первым выходом процессорного эл мента первого типа, вторым вых-одом которого является выход второго регистра, информационный вход которого соединен с вторым входом умножителя и является вторым входом процессорного элемента первого типа, третьим входом которого является второй вход сумматора, выход которого подключен к информационному входу третьего регистра, выход- которого является третьим выходом процессорного элемента первого типа,тактовый вход первого регистра подключен к первому тактовому выходу блока управления, -а тактовые входы второго и третьего регистров соединены между собой и подключены к тактовому входу устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены М аналого- цифровых преобразователей, М коммутаторов, (М-1) групп из i последовательно соединенных регистров в i-й группе, три блока постоянной памяти, М-ную группу из f последовательно соединенных регистров, (М+1)-ную группу из (M-l) последовательно coe::i

, :i

589289

18

10

20

25

диненных регистров, группу и (М-1) последовательно соединенных D-тригге- ров, первую и вторую группу из М умножителей в каждой группеj М групп из N процессорнь1х элементов второго типа в каждой группе, при этом первый информационный вход j-ro коммутатора подключен к выходу j-ro аналого-цифрового преобразователя, вход которого является J-M информационным входом первой группы устройства, J-M инАор- мационным входом второй группы которого является второй информационный 15 вход j-ro коммутатора, выход 1-го (1 2, М) коммутатора подключен к информационному входу первого регистра (1-1 )-й группы, выход (l-l)-ro ре- гистра которой подключен к второму входу первого процессорного элемента первого типа 1-й группы, первый адресный вход блока управления подключен к адресному входу первого блока постоянной памяти, выход которого подключен к первому входу первого процессорного элемента первого типа первой группы, второй вход которого подключен к выходу первого коммутатора, второй адресный вход блоки управления подключен к адресным входам второго и третьего блоков постоянной памяти, выходы которых подключены к информационным входам первых регистров соответственно М-й и (М+О-й групп, второй тактовый выход блока управления подключен к тактовому входу первого процессорного элемента второго типа и тактовому входу первого D-триггера rpynjibi, первый и второй выходыт-го ( , N-1) процессор- ного элемента второго типа j-й группы подключены соответственно к тактовому и первому инЛ)ормац}юнному входам (т+1)-го процессорного элемента второго типа j-й группы, выход i-ro D-триггера группы подключен к тактовому входу первого процессорного элемента второго типа (1+1)-и групгы,выход, второго блока постоянной памяти подключен к первому входу первого умножителя первой группы, выход i-ro регистра М-й группы подключен к первому входу (i+O- ro умножителя первой группы, выход третьего блока постоянной памяти подключен к второму инф о р мац ион ному входу S-ro (S 1,N) процессорного элемента второго типа первой группы, выход i-ro регистра (М+1)-й группы подключен к

30

35

40

45

50

55

второму информационному входу S-ro процессорного элемента второго типа (1+1)-й группы, Bbixofl j-ro умножителя первой группы подключен к третьему информационному входу S-ro процессорного элемента второго типа j-й группы,, первый выход которого подключен к первому входу j-ro умножителя втрро й группы, выходы которых и второй выход N-ro процессорного элемента второго типа первой группы образуют группу информационных выхо- .дов устройства, входим выбора режима которого являются соединенные между собой управляющие входы KOMi-iy- таторов, выход j-ro регистра М-й группы подключен к второму входу j-r умножителя второй группы, третий выход j-ro процессорного элемента первого типа М-й группы подключен к второму входу j-ro умножителя первой группы, при этом, процессорный элемент второго типа содержит сумматор,

- Ы1

17

/4

4J 44 45

фф47

два регистра, D-триггер и умножитель, выход которого подключен к первому входу сумматора, выход которого под,ключен к. информационному входу первого регистра, выход которого является выходом процессорного элемента второго типа,вторым выходом кото- .рого является выход В-триггера,уста- новочный вход которого соединен с установочным входом второго регистра

и является тактовым входом процессорIного элемента второго типа, вторым

информационным входом которого явля- ется первый вход умножителя, второй вход которого подключен к выходу второго регистра, информационный вход которого является третьим информационным входом процессорного элемен- та второго типа, тактовые входы первого и второго регистра D-триггера подключены к третьему тактовому выходу блока управления. .

Фиг. I

eStUi cltHt.

Фиг.г cBta.

| Устройство для замены изношенной перфорации фильма | 1928 |

|

SU13488A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения микросферического (пылевидного) катализатора для процесса окислительного хлорирования бензола в кипящем слое | 1960 |

|

SU136324A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-30—Публикация

1988-10-19—Подача