I

(21)4699048/24

(22)24.04.89

(46) 30.05.91. Бюп. (Г 20

(71)Житомирский филиал Киевского политехнического института

(72)Д.В. Корчев, Ю.С. Каневский и С.В. Клименко

(53)68Ь32 (088.8)

(56)Авторское свидетельство СССР

№ 1314352, кл. G 06 F 15/353, 1985.

Авторское свидетельство СССР № 1388891. кл. G 06 F 15/353, 1986.

(54)УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ

(57)Изобретение относится к вычислительной технике и предназначено для выполнения двумерного и одномерного преобразования Фурье, цифровой фильтрации в устройствах цифровой

обработки сигналов. Цель изобретения - расширение функциональных возможностей за счет вычисления двумерного преобразования Фурье. Поставленная цель достигается за счет того, что в состав устройства входят N/2 процессорных модулей (N - размер преобразования) 1, блок управления 2, причем процессорный модуль содержит входной регистр 3, регистры 4, 5, умножители 6, 7, триггер 8, регистр коэффициентов 9, триггер 10, сумматоры 11, 12, элементы задержки 13, 14, триггер 15, коммутаторы 16, 17, элементы задержки 18, 19, умножители 20, 21, регистр 22, сумматоры 23, 24, узлы 25, 26 постоянной памяти коэффициентов, регистр адреса 27, генератор 28 тактовых импульсов. 2 ил.

г со

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1988 |

|

SU1589289A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1697085A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1508233A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1499374A1 |

| Цифровой фильтр | 1986 |

|

SU1348981A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1545230A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| Цифровой фильтр | 1986 |

|

SU1387015A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1596347A1 |

Изобретение относится к вычислительной технике и предназначено для выполнения двумерного преобразования Фурье, одномерного преобразования Фурье, процедуры фильтрации в устройствах цифровой обработки сигналов.

Цель изобретения - расширение функциональных возможностей устройства за счет вычисления двумерного дискретного преобразования Фурье.

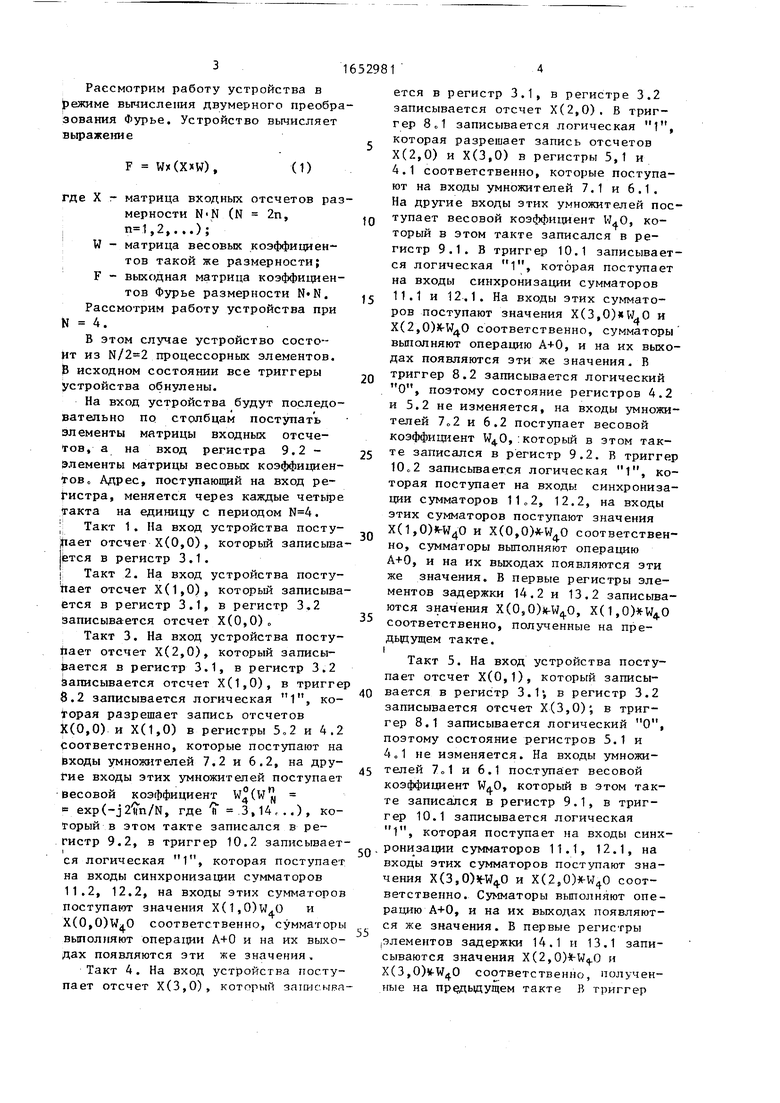

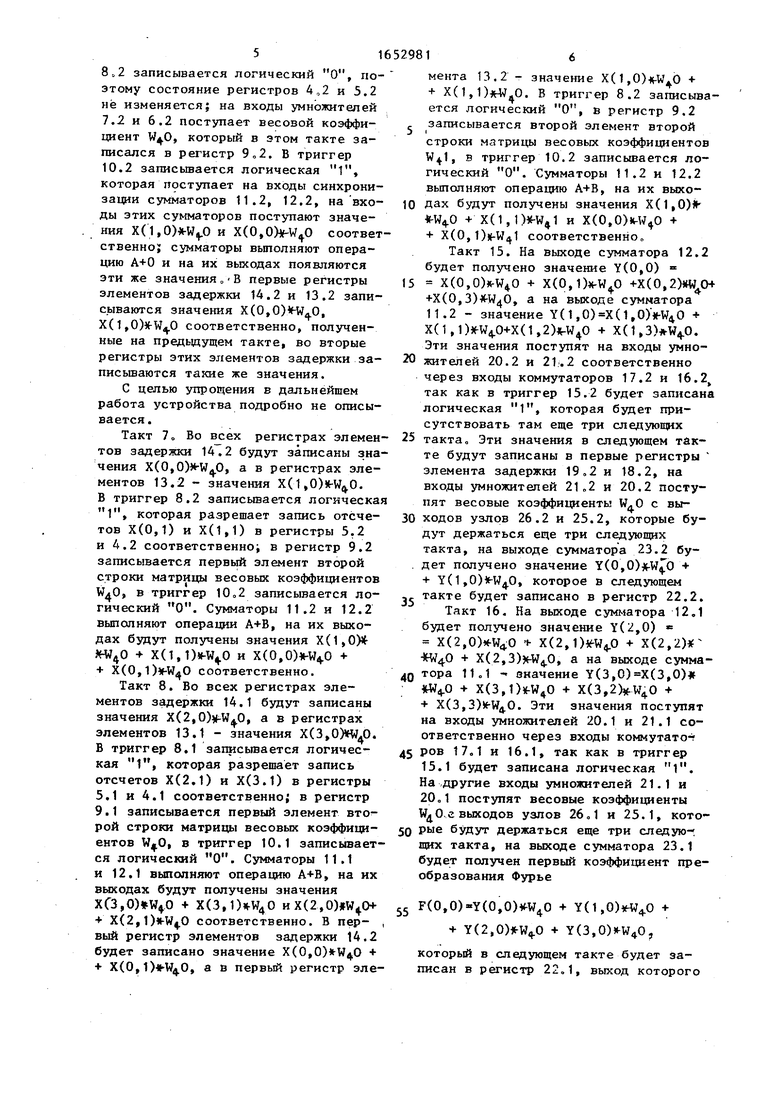

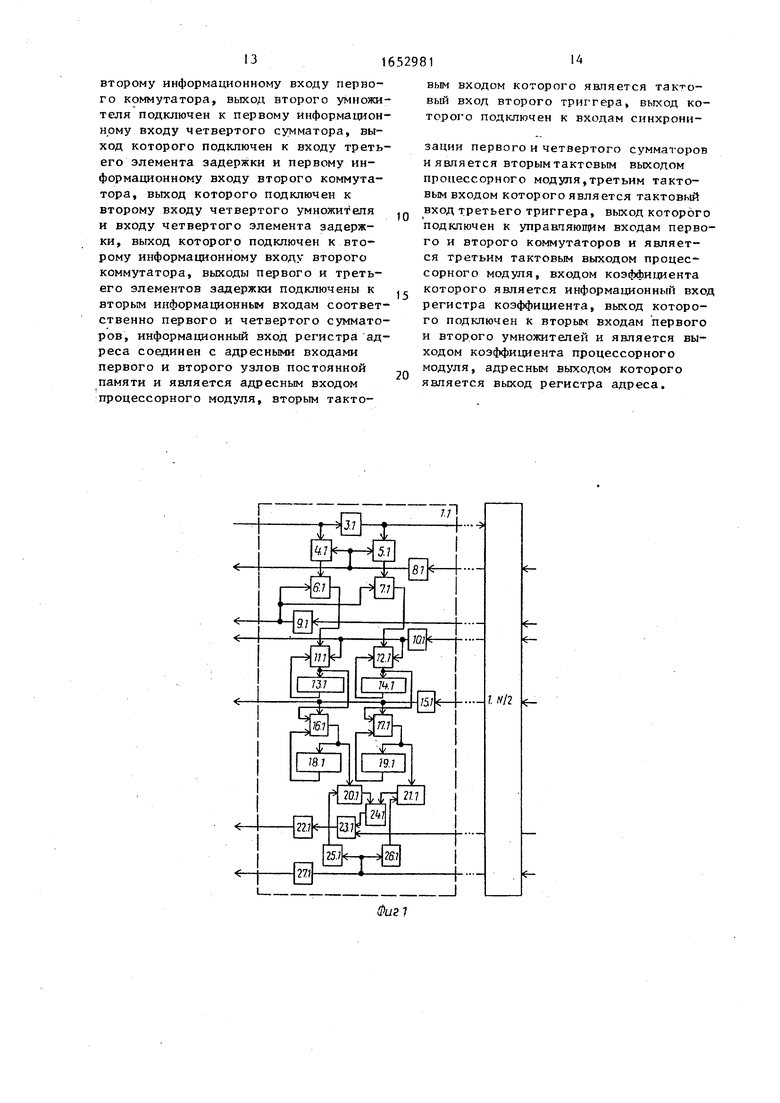

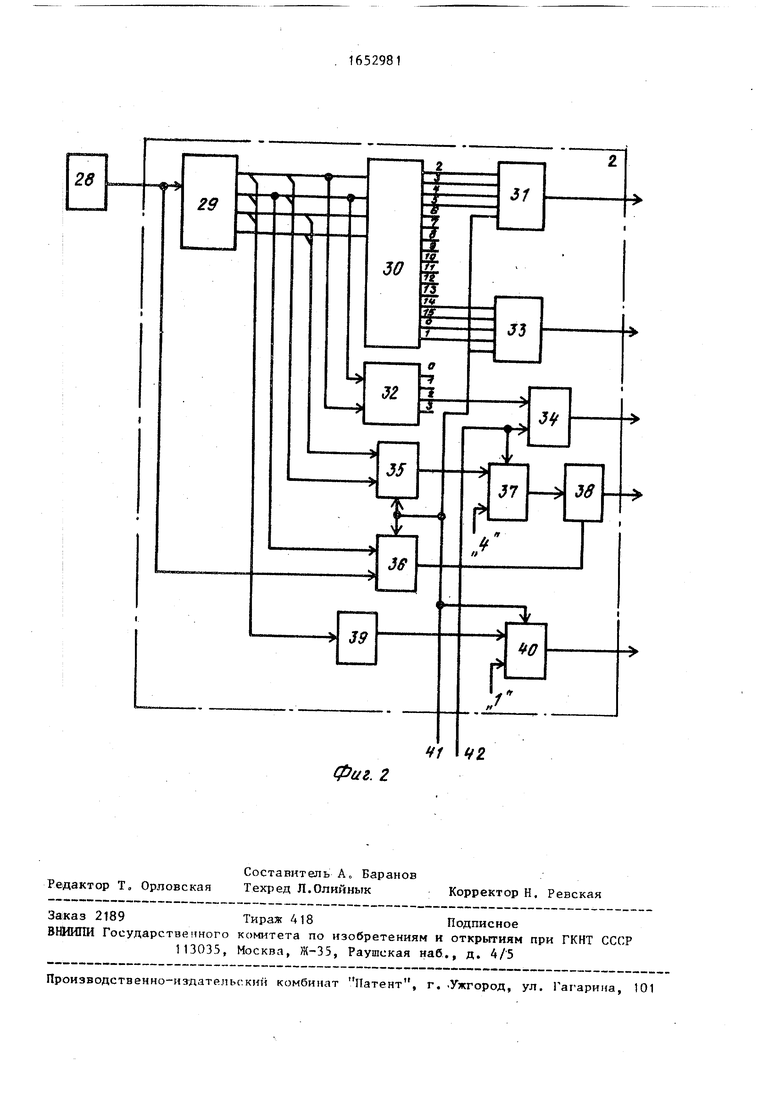

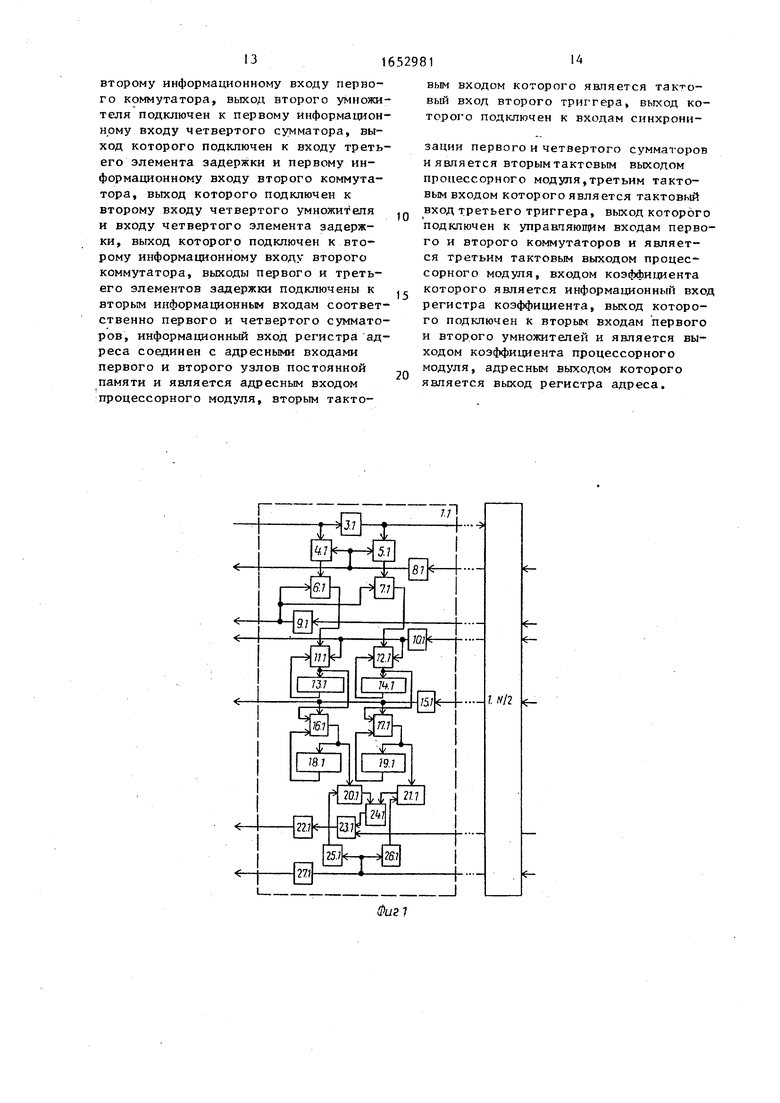

На фиг„1 изображена структурная схема устройства; на фиг.2 - структурная схема блока управления.

Устройство (фиг.1) содержит N/2 (N размерность преобразования) процессорных модулей 1.1-1.N/2 блок управления 2, причем каждый процессорный модуль состоит из входного регистра 3, регистров 4 и 5, умножителей 6 и 7, триггера 8, регистра 9 коэффициентов, триггера 10, сумматоров 11 и 12, элементов задержки 13 и 14, триггера 15, коммутаторов 16 и 17, элементов задержки 18 и 19, умножителей 20 и 21, регистра 22, сумматоров 23 и 24, узлов 25 и 26 постоянной памяти коэффициентов и регистра адреса 27, генератор 28 тактовых импульсов.

Блок управления 2 при N 4 (фиг.2) содержит счетчик 29 (по модулю 16), дешифратор 30, элемент ИЛИ 31, дешифратор 32, элементы ИЛИ 33, 34, коммутаторы 35, 36, 37, регистр 38, узел 39 постоянной памяти, коммутатор 40, входы 41, 4Г задания режима .

Рассмотрим работу устройства в режиме вычисления двумерного преобразования Фурье. Устройство вычисляет выражение

F Wx(),

(1)

где X - матрица входных отсчетов размерности N-N (N 2п, ,2,. ..);

W - матрица весовых коэффициентов такой же размерности; F - выходная матрица коэффициентов Фурье размерности . Рассмотрим работу устройства при N 4.

В этом случае устройство состоит из процессорных элементов. В исходном состоянии все триггеры устройства обнулены.

На вход устройства будут последовательно по столбцам поступать элементы матрицы входных отсчетов, а на вход регистра 9.2 - элементы матрицы весовых коэффициентов с Адрес, поступающий на вход регистра, меняется через каждые четыре такта на единицу с периодом .

Такт 1. На вход устройства поступает отсчет Х(0,0), который записывается в регистр 3.1.

Такт 2. На вход устройства поступает отсчет Х(1,0), который записывается в регистр 3.1, в регистр 3.2 записывается отсчет Х(0,0)„

Такт 3. На вход устройства поступает отсчет Х(2,0), который записывается в регистр 3.1, в регистр 3.2 записывается отсчет Х(1,0), в триггер 8.2 записывается логическая 1, которая разрешает запись отсчетов Х(0,0) и Х(1,0) в регистры 5„2 и 4.2 соответственно, которые поступают на входы умножителей 7.2 и 6.2, на другие входы этих умножителей поступает весовой коэффициент W4(WH exp(-j2/5 n/N, где 7 3,14, ..), который в этом такте записался в регистр 9.2, в триггер 10.2 записывается логическая 1, которая поступает на входы синхронизации сумматоров 11.2, 12.2, на входы этих сумматоров поступают значения X(1,0)W40 и X(0,0)WjO соответственно, сумматоры выполняют операции А+0 и на их выходах появляются эти же значения .

Такт 4. На вход устройства поступает отсчет Х(3,0), который ташн мвл

5

0

5

0

5

0

5

0

5

ется в регистр 3.1, в регистре 3.2 записывается отсчет Х(2,0). В триггер 8,1 записывается логическая 1, которая разрешает запись отсчетов Х(2,0) и Х(3,0) в регистры 5,1 и 4.1 соответственно, которые поступают на входы умножителей 7.1 и 6.1. На другие входы этих умножителей поступает весовой коэффициент W..O, который в этом такте записался в регистр 9.1. В триггер 10.1 записывается логическая 1, которая поступает на входы синхронизации сумматоров

i

Такт 5. На вход устройства поступает отсчет Х(0,1), который записывается в регистр 3.1; в регистр 3.2 записывается отсчет Х(3,0); в триггер 8.1 записывается логический О, поэтому состояние регистров 5.1 и 4„1 не изменяется. На входы умножителей 7о1 и 6.1 поступает весовой коэффициент W,,0, который в этом такте записался в регистр 9.1, в триггер 10.1 записывается логическая 1, которая поступает на входы синхронизации сумматоров 11.1, 12.1, на входы этих сумматоров поступают значения X(3,0)i(-Wq.O и X(2,0)W40 соответственно. Сумматоры выполняют операцию А+0, и на их выходах появляются же значения. В первые регистры рлементов задержки 14.1 и 13.1 записываются значения X(2,0)-W.( и X(3,0)-W40 соответственно, полученные на предыдущем ТЯКТР Р. триггер

С целью упрощения в дальнейшем работа устройства подробно не описывается .

Такт 7, Во всех регистрах элемен тов задержки 14.2 будут записаны значения Х(0,0), а в регистрах элементов 13.2 - значения Х( 1,0)-W(j.O. В триггер 8.2 записывается логическа 1, которая разрешает запись отсче- тов Х(0,1) и Х(1,1) в регистры 5.2 и 4.2 соответственно в регистр 9.2 записывается первый элемент второй строки матрицы весовых коэффициентов W 40, в триггер 10,2 записывается логический О. Сумматоры 11.2 и 12.2 выполняют операции А+В, на их выходах будут получены значения Х(1,0) 740 + Xd.Dtt-W O и X(0,0)-W40 + + X(0,1)-W40 соответственно.

Такт 8. Во всех регистрах элементов задержки 14.1 будут записаны значения X(2,0), а в регистрах элементов 13.1 - значения Х(3,0). В триггер 8.1 записывается логичес- кая 1, которая разрешает запись отсчетов Х(2.1) и Х(3.1) в регистры 5.1 и 4.1 соответственно; в регистр 9.1 записывается первый элемент второй строки матрицы весовых коэффици- ентов , в триггер 10.1 записывается логический О. Сумматоры 11.1 и 12.1 выполняют операцию А+В, на их выходах будут получены значения

xC3,o)w4o + x(3,i)w4o HX(2,o)#w4o+

X(2,1) соответственно. В пер- вый регистр элементов задержки 14.2 будет записано значение X(0,0)W40 + + X(0,1)#-W40, а в первый регистр элемента 13.2 - значение X(1,0)(-W40 + + X(1,1)V О. В триггер 8.2 записывается логический О, в регистр 9.2 записывается второй элемент второй строки матрицы весовых коэффициентов , в триггер 10.2 записывается логический О. Сумматоры 11.2 и 12.2 выполняют операцию А+В, на их выходах будут получены значения Х(1,0)#- -W40 + X(1,1)-W41 и X(0,0)-W40 + + X(0,1)-W41 соответственно.

Такт 15. На выходе сумматора 12.2 будет получено значение Y(0,0) X(0,0)W40 + X(0,1)-WfO +X(0,2)W4CH +X(0,3)-W40, а на выходе сумматора 11.2 - значение Y( 1,0)Х( 1,0)-W40 + X(1,1)-W4.0+X(1 ,2)«-W40 + X(1,3)W4,0. Эти значения поступят на входы умножителей 20.2 и 21.2 соответственно через входы коммутаторов 17.2 и 16.2 так как в триггер 15.2 будет записан логическая 1, которая будет присутствовать там еще три следующих такта. Эти значения в следующем такте будут записаны в первые регистры элемента задержки 19,2 и 18.2, на входы умножителей 21.2 и 20.2 поступят весовые коэффициенты с выходов узлов 26.2 и 25.2, которые будут держаться еще три следующих такта, на выходе сумматора 23.2 будет получено значение Y(0,0) + + Y( 1,0)-W40, которое в следующем такте будет записано в регистр 22.2.

Такт 16. На выходе сумматора 12.1 будет получено значение Y(2,0) X(2,0)W40 Х(2, + Х(2,2) Н/40 + Х(2,3)-ИфО, а на выходе сумматора 11.1 - оначение Y(3,0)X(3,0)# «4.0 + X(3,1)-W40 + X(3,2)W40 + + X(3,3)W40. Эти значения поступят на входы умножителей 20.1 и 21.1 соответственно через входы коммутато- ров 17.1 и 16.1, так как в триггер 15.1 будет записана логическая 1. На другие входы умножителей 21.1 и 20.1 поступят весовые коэффициенты W4Оевыходов узлов 26„1 и 25.1, которые будут держаться еще три следую- , щих такта, на выходе сумматора 23.1 будет получен первый коэффициент преобразования Фурье

F(0,0)-Y(0,0)W40 + Y(1,0)4.0 + + Y(2,0)W,.0 + Y(3,0)-W40,

который в следующем такте будет записан в регистр 22.1, выход которого

является информационны выходом устройства .

Начиная с 18-го такта на выходе устройства будут последовательно получены коэффициенты: такт 18

F(0,1)Y(0,1)W40 + Y(1,1) +

+ Y(2,1)W40 + Y(3,1)W40

такт 19

F(0,2)Y(0,2)-W%0 + Y(1,2)W40 + + Y(2,2)W40 + Y(3,2)W40,

такт 20

F(0,3)Y(0,3)W40 + Y(1,3)W40 + + Y(2,3)W40 + Y(3,3)W40

Смена весовых коэффициентов на выходах узлов постоянной памяти процессорных модулей будет происходить через каждые четыре такта, причем в процессорном модуле 1„1 с задержкой на один такт относительно процессорного модуля Т.2 за счет наличия регистра 27.1.

Начиная с 21-го такта на выходе устройства будут последовательно получены коэффициенты:

F(1,0)Y(0,0)«-W40 + Y(1,0)«-W41 + +Y(2,0)W42 + Y(3,0)-W4321

F( 1,1) Y(0,1 )-WfO-i-Y( 1,1)W41 + +Y(2,1)-W42+Y(3,1)-W4322

F( 1,2) Y(0,2)-W4(HY( 1,2)W4 1 + +Y(2,2)W42 + Y(3,2)-W4323

F(1,3)Y(0,3XW40+Y(1,3)-W4H- +Y(2,3)Wf2+Y(3,3)W4324

F(2,0)Y(0,0)-W4.0+Y(1,0)#W,.2H- fY(2,0)-W40+Y(3,0)W4225

F(2,1)Y(0,1)W40+Y(1,1)«-W42+ +Y(2,1)W4(HY(3,1)W4226

F(2,2)Y(0,2)W40+Y(1,2)x-W42+ +Y(2,2)W40+Y(3,2)W4227

F(2,3)+Y(0,3)W40+Y(1,3)-W42+ +Y(2,3)«-W40+Y(3,3)W4228

F(3,0)-Y(OtO)«-W40+Y( 1,0) +Y(2,0)W42+Y(3,0)W4129

F(3,1)-Y(0,1)-W40+Y(1f 1)W43+ +Y(2,1)(3t1)W4130

F(3,2) Y(0,2) (1 , 2)W4 3+ +Y(2,2)W42+Y(3,2)W4131

F(3,3)Y(0,3)W40- Y(1 ,3)W43 +Y(2,3)W4.2fY(3,3)«-W,13

16529818

где Y(1,j)X(1,0)-W4,0+X(1t1)«W4J + +X(1,2)W4()+X(1,3)W () В дальнейшем работа устройства продолжается по описанному алгоритму. 1Рассмотрим работу устройства в режиме вычисления одномерного ДПФ. Устройство вычисляет выражение

10

F

(2)

0

5

0

5

0

6

5

где X - исходный вектор входных отсчетов размерности N; W - матрица весовых коэффициентов размерности , Рассмотрим работу устройства при

N 4. I

В этом случае устройство состоит

из процессорных модулей. В этом режиме на информационные входы триггеров 10.2, 15.2 постоянно поступает логическая 1, на информационный вход регистра 9.2 - двоичное число 1. Предполагается, что в исходном состоянии триггеры 10.1, 15.1 и регистры 9.1 находятся в единичном состоянии. В этом случае на входы умножителей 6.1, 7.1 постоянно поступает единица, сумматоры 11.1, 12.1 выполняют операцию А+0, коммутаторы 16.1, 17.1 принимают информацию с входа, адрес, поступающий на вход регистра 27.2, изменяется в каждом такте на единицу с периодом , В соответствии с описанным, состояние входов умножителей 20.1, 21.1 соответствует состоянию выходов регистров 4.1 и 5.1 соответственно, поэтому в дальнейшем состояние элементов 6.1, /Л, 9.1, 10.1, 11.1, 12.1, 13.1, 14.1, 15.1, 16.1, 17.1, 18.1, 19.1 не рассматривается.

Такт 1. На информационный вход устройства поступает отсчет Х(0), 5 который записывается в регистр 3.1.

Такт 2. На информационный вход устройства поступает отсчет Х(1), который записывается в регистр 3.1; в регистр 3.2 записывается отсчет Х(0).

Такт 3. На информационный вход устройства поступает отсчет Х(2), который записывается в регистр 3.1, в регистр 3.2 записывается отсчет Х(1).

Так как на выходе триггера 8.2 появилась логическая 1, в регистры 5.2 и 4.2 записываются отсчеты Х(0) и Х(1), которые поступают нл входы

умножителей 21.1 и .10.2 соответственно, ня другие входы этих умножителей поступают с выходов узлов ,.Ь. 2 и 25.2 весовые коэффициенты , на выходе сумматора 23.2 будет получено значение X(0)W4.0+X( , которое в следующем такте будет записано в регистр 22.2.

Такт 4. На информационный вход УСТ ройства поступав отсчет Х(3), который записывается в регистр 3.1; в регистр 3.2 записывается отсчет Х(2). Так как на выходе триггера 8.1 появилась логическая 1, в регистры 5.1 .- 25.1 весовые коэффициенты и .

и 4.1 записываются отсчеты Х(2) и Х(3), которые поступают на входы умножителей 21.1 и 20.1 соответственно, на другие входы этих умножителей поступают с выходов узлов 26.1 и 25.1 весовые коэффициенты , на выходе сумматора 24.1 будет получено значение X(2)it-W4.0+X(3)K-W4.0, на выходе сумматора 23.1 будет получено значение F(0)X(0)-W40+X(1)-W40+X(2)frW4.0+ + X(3)-WqЈ), которое в следующем такте будет записано в регистр 22.1. Так как на выходе триггера 8.2 появился логический О, в регистрах 5.2 и 4.2 сохраняются отсчеты Х(0) и Х(1), которые поступают на входы умножителей 21 .2 и 20.2 соответственно. На другие входы этих умножителей поступают с выходов узлов 26.2 и 25.2 весовые коэффициенты и , на выходе сумматора 23.2 будет получено значение Х(0)( 1)W41, которое в следующем такте будет записано в регистр 22.2.

Такт 5а Так как на выходе триггера 8. 1 появился логический О, в регистрах и 4.1 сохраняются отсчеты Х(2) и Х(3), которые поступают на входы умножителей 21.1 и 20.1 соответственно. На другие входы этих умножителей поступают с выходов узлов 26.1 и 25„1 весовые коэффициенты W42 и W,3; на выходе сумматора 24.1 будет получено значение X(2)W4.2 + + Х(3) W43, на выходе сумматора 23.1 будет получено значение F( 1 )+X(G)W4p+ +Х(1)(2)(3)и43, которое в следующем такте будет записано в регистр 22.1. Так как на выходе триггера 8.2 логический О, в регистрах 5.2 и 4.2 сохраняются отсчеты Х(0) и Х(1), которые поступают на входы умножителей 21.2 и 20.2 соответственно; на другие входы этих умножителей

20

30

На выходе сумматора 24.1 будет получено значение X(2)V40-bX(3)W42; на выходе сумматора 23.1 будет получено значение F(2)X(0) W 0+X(1)W,.2 + + X(2)W4.0 + X(3)W4.2, которое в следующем такте будет записано в регистр 2:1.1. Так как на выходе тригге ра 8.2 логический О, в регистрах 5.2 и 4.2 сохраняются отсчеты Х(0)

25 и Х(1), которые поступают на входы умножителей 21.2 и 20.2 соответствен но; на другие входы этих умножителей поступают с выходов узлов 26.2 и 25. весовые коэффициенты и . На выходе сумматора 23.2 будет получено значение Х(0) + , которо в следующем такте будет записано в регистр 22.2.

Такт У „ Так как на выходе триггера 8 . 1 логический О, в регистрах

3 5.1 и 4,1 сохраняются отсчеты Х(2) и Х(3), которые поступают на входы умножителей 21.1 и 20.1 соответствен но; на другие входы этих умножителей поступают с выходов узлов 27.1 и 25.1 весовые коэффициенты W42 и W.1. На выходе сумматора 24.1 будет получено значение X(2)-W42 + X(3)W41; на выходе сумматора 23.1 будет получено значение F(3)X(0)«.( 1 )W43 + +X(2)«-W42 + X(3)«-W41, которое в следующем такте будет записано в регистр 22.1 и т.д.

При цифровой фильтрации при N 4 устройство вычисляет выходные отсчеты фильтра в ссответствии с выражением

40

45

50

55

А(К)Х(К-0)Н(0) + Х(К-1)Н(1)+ +Х(К-2)Н(2) + Х(К-3)Н(3), (3)

где Н(1) - коэффициенты импульсной

характеристики; Х(1) - отсчеты входного сигнала

поступают с выходов узлов 26.2 и 15.2 весовые коэффициенты W40 и . На выходе сумматора 24. 2 Судет получено значение ХССОи-Ы О + X(1)W42, которое в следующем такте будет записано в регистр 22.2.

Такт 6. Так как на выходе триггера 8 . 1 логический О, в регистрах 5.1 и 4.1 сохраняются отсчеты Х(2) и Х(3), которые поступают на входы умножителей 21.1 и 20.1 соответственно, на другие входы этих умножителей поступают с выходов узлов 26.1 и

На выходе сумматора 24.1 будет получено значение X(2)V40-bX(3)W42; на выходе сумматора 23.1 будет получено значение F(2)X(0) W 0+X(1)W,.2 + + X(2)W4.0 + X(3)W4.2, которое в следующем такте будет записано в регистр 2:1.1. Так как на выходе триггера 8.2 логический О, в регистрах 5.2 и 4.2 сохраняются отсчеты Х(0)

и Х(1), которые поступают на входы умножителей 21.2 и 20.2 соответственно; на другие входы этих умножителей поступают с выходов узлов 26.2 и 25.2 весовые коэффициенты и . На выходе сумматора 23.2 будет получено значение Х(0) + , которое в следующем такте будет записано в регистр 22.2.

Такт У „ Так как на выходе триггера 8 . 1 логический О, в регистрах

При цифровой фильтрации при N 4 устройство вычисляет выходные отсчеты фильтра в ссответствии с выражением

А(К)Х(К-0)Н(0) + Х(К-1)Н(1)+ +Х(К-2)Н(2) + Х(К-3)Н(3), (3)

где Н(1) - коэффициенты импульсной

характеристики; Х(1) - отсчеты входного сигнала.

При работе устройства в режиме фильтрации на вход триггера 8.N/2 постоянно поступает высокий уровень, который устанавливает все триггеры 8 в единичное состояние, что обеспечивает прием исходных операндов в каждом такте в регистры 4, 5. На вход регистра 27.N/2 постоянно поступает адрес, по которому в узлы 25, 26 записаны соответствующие коэффициенты импульсной характеристики фильтра. К началу процедуры цифровой фильтрации этот адрес записывается во все регистры 27. Состояние остапь ных модулей устройства такое же, как в режиме вычисления одномерного ДПФ. Первый выходной отсчет фильтра получаем через N/2 тактов, в каждом следующем такте на выходе фильтра появляется новый отсчет.

Формула изобретения

Устройство для цифровой обработки сигналов, содержащее N/2 процессорных модулей (N - размер обрабатываемых последовательностей), блок управления и генератор тактовых импульсов, выход которого подключен к тактовому входу блока управления, первый тактовый выход которого подключен к первому тактовому пходу N/2-го процессорного модуля, первый информацион- ный выход i-го (i 1, N/2-1) процессорного модуля подключен к первому информационному входу (i-M)-ro процессорного модуля, второй информационный и первый тактовый выходы которого подключены соответственно к второму информационному и первому тактовому входам 1-го процессорного модуля, второй информационный выход первого процессорного модуля является информационным выходом устройства, информационным входом и входом задания режима которого являются соответственно первый информационный вход первого процессорного модуля и вход задания режима блока управления, причем каждый процессорный модуль содержит два сумматора, два умножителя, три регистра, первый триггер и второй регистр, выход которого подключен к информационному входу п.орвого регистра и является первым информационные выходом процессорного модуля, первым информационным входом которого являются соединенные между

Q 5

0

5

0

5

0

5

собой информационные входы входного регистра и второго регистра, выход которого подключен к первому входу первого умножителя, выход которого подключен к первому информационному входу первого сумматора, выход первого регистра подключен к первому входу второго умножителя, вькод второго сумматора подключен к информационному входу третьего регистра, выход которого является вторым информационным выходом процессорного модуля, вторым информационным и первым тактовым входами которого являются соответственно первый вход второго сумматора и тактовый вход первого триггера, выход которого подключен к тактовым входам первого и второго регистров и является первым тактовьм выходом процессорного модуля, о т- личающееся тем, что, с целью расширения функциональных возможное гей за счет вычисления двумерного дискретного преобразования Фурье, второй и третий тактовые выходы, адресный выход и выход задания коэффициента блока управления подключены соответственно к второму и третьему тактовым входам, адресному входу и входу коэффициента N/2-го процессорного модуля, второй и третий тактовые входы, адресный вход и вход коэффициента 1-го процессорного модуля подключены соответственно к второму и третьему тактовым выходам, адресному выходу и выходу коэффициента (i+1)-ro процессорного модуля, причем в каждый процессорный модуль введены регистр адреса, третий и четвертый сумматоры, регистр коэффициента, второй и третий триггеры, третий и четвертый умножители, два коммутатора, четыре элемента задержки и два узла постоянной памяти коэффициентов, выходы которых подключены к первым входам соответственно третьего и четвертого умножителей, выходы которых подключены соответственно к первому и второму входам третьего сумматора, выход которого подключен к вторс у входу второго сумматора, выход первого сумматора подключен к входу первого элемента задержки и первому информационному входу первого коммутатора, выход которого подключен к второму входу третьего умножителя и входу второго элемента задержки, выход которого подключен к

второму информационному входу первого коммутатора, выход второго умножителя подключен к первому информационному входу четвертого сумматора, выход которого подключен к входу третьего элемента задержки и первому информационному входу второго коммутатора, выход которого подключен к второму входу четвертого умножителя и входу четвертого элемента задержки, выход которого подключен к второму информационному входу второго коммутатора, выходы первого и третьего элементов задержки подключены к вторым информационны входам соответственно первого и четвертого сумматоров, информационный вход регистра адреса соединен с адресными входами первого и второго узлов постоянной памяти и является адресным входом процессорного модуля, вторым тактоI

$uг

0

вым входом которого яапяется вый вход второго триггера, выход которого подключен к входам синхронизации первого и четвертого сумматоров и является вторым тактовым выходом процессорного модуля,третьим тактовым входом которого является тактовый вход третьего триггера, выход которого подключен к улранпяющим входам первого и второго коммутаторов и является третьим тактовым выходом процессорного модуля, входом коэффициента которого является информационный вход регистра коэффициента, выход которого подключен к вторым входам первого и второго умножителей и является выходом коэффициента процессорного модуля, адресным выходом которого является выход регистра адреса.

Фиг. 2

V/

чг

Авторы

Даты

1991-05-30—Публикация

1989-04-24—Подача