Изобретение относится к вычисли-. тельной технике и может быть исполь-- зовано при обработке двумерных и од- номерных массивов данных большой размерности, например для фильтрации сигналов или обработки изображений.

Целью изобретения является расширение функциональных возможностей путем выполнения рекурсивной двзтер- ной и одномерной фильтрации.

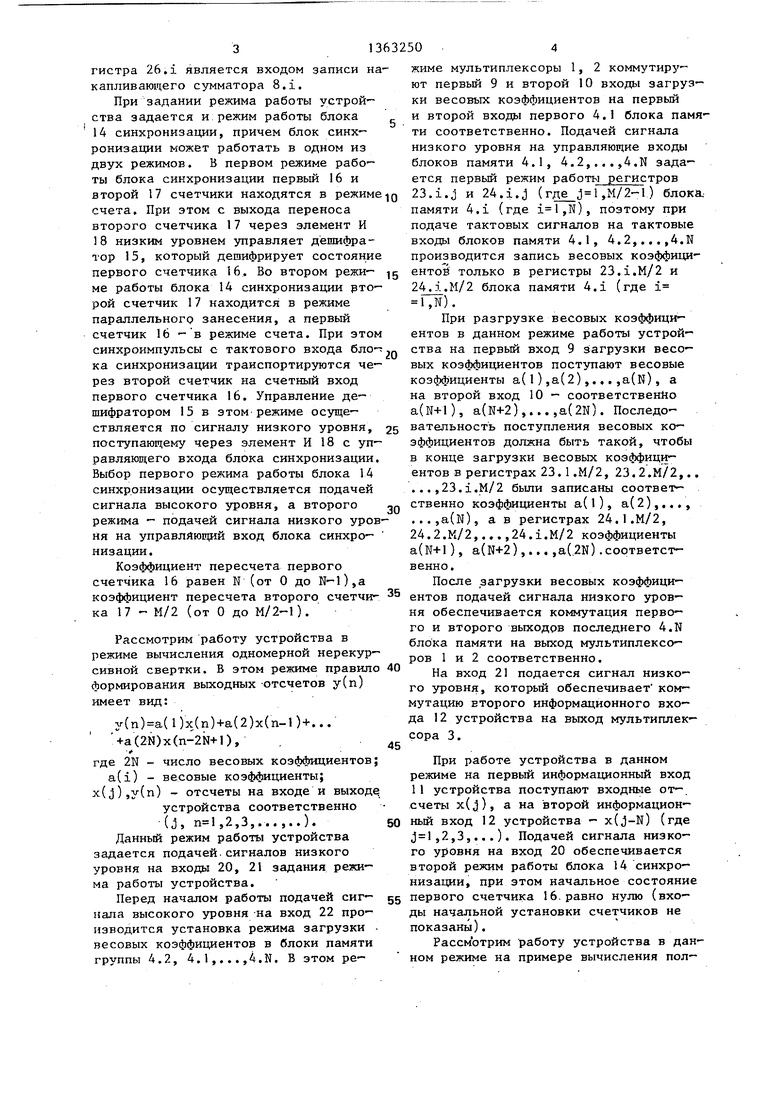

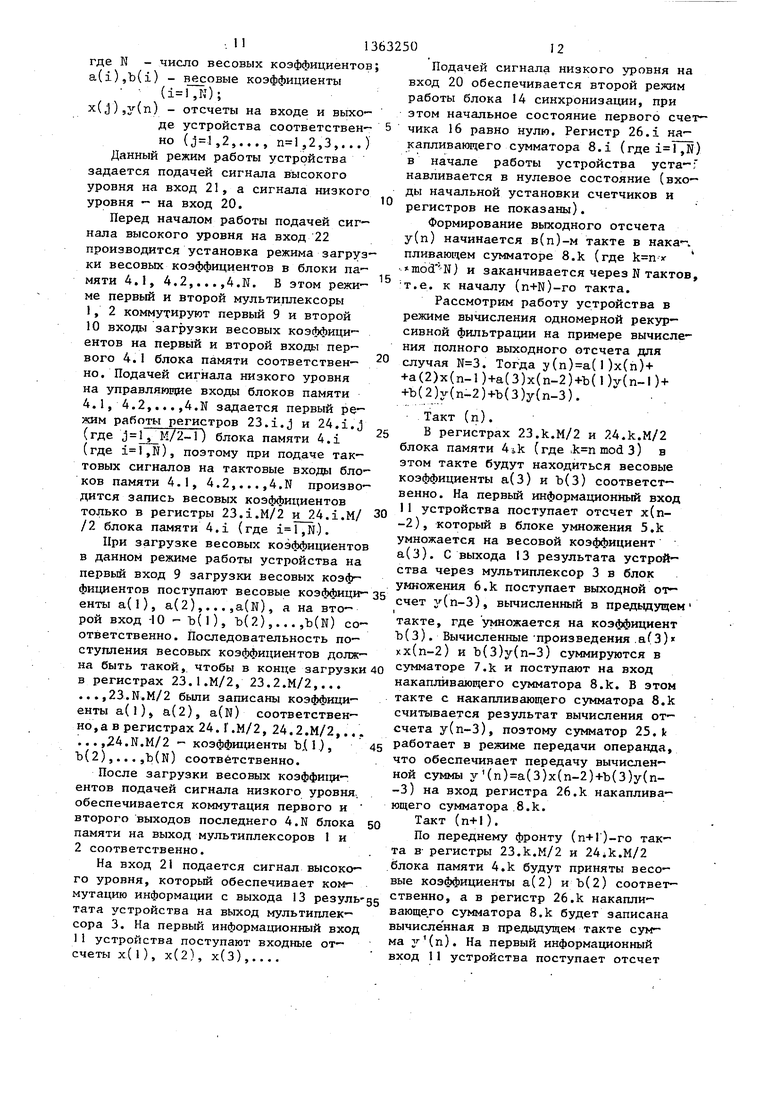

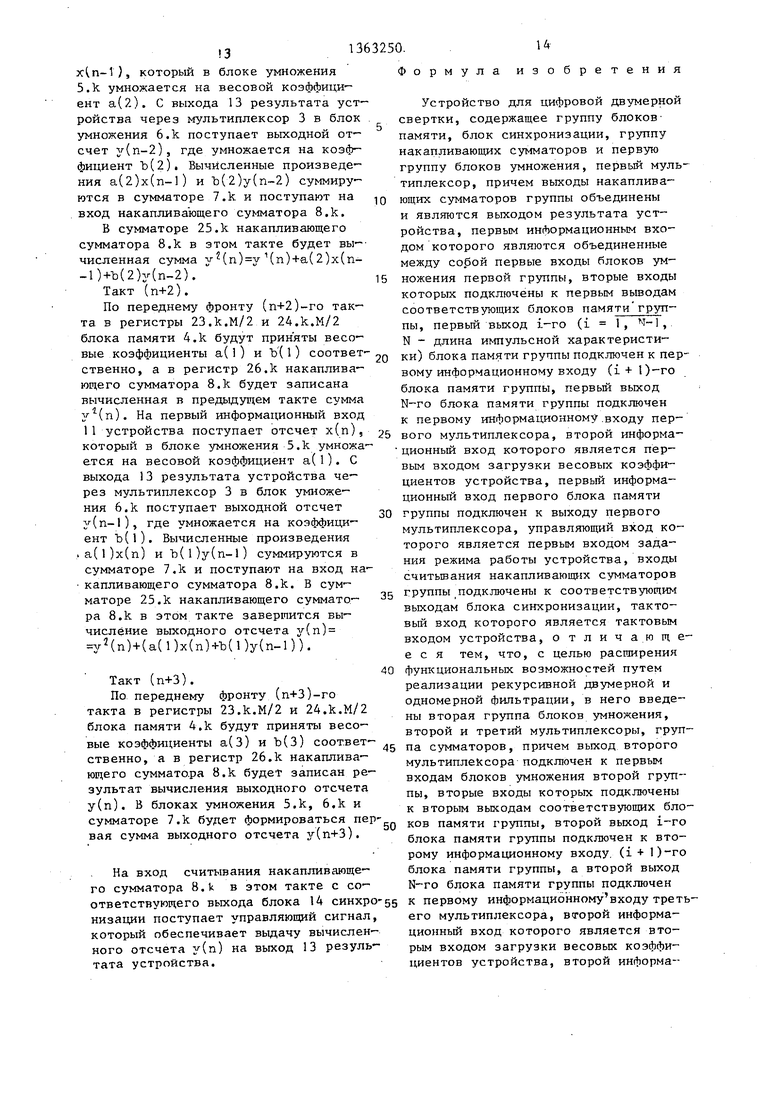

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - схема блока памяти; на фиг. 3 - схема накапливающего сумматора.

Устройство для цифровой двумерной свертки содержит мультиплексоры I, 2, 3, блоки памяти группы 4.1, 4.2,,, ...,4.N, блоки умножения первой группы 5.1, 5,25.,.,5.N5 блоки умножения второй группы 6,1, 6.25...,6.N, сумматоры группы- 7,1, ,...,7.N, накапливающие сумматоры группы 8.1, 8.2,...,8.N, первый 9 и второй 10 входы загрузки весовых коэффициентов устройства, первый 11 и второй 12 информационные входы устройства, выход 13 результата устройства, блок 14 синхронизации, содержагщй дешифратор 15, первый 16, второй 17 счетчики, элемент И 18, тактовый вход 19j входы 20, 21 задания режима работы, вход 22 запуска.

Блок памяти 4,1 (фиг. 2) представляет собой две группы регистров . . 23.1.1, 23.V.2,..,,23.i.M/2 и 24.1.1 24.1.2,,..,24.1.М/2, причем входы регистров 23.i.J и 24.i.j (где j l,M/2-l) соединены с информационными входами соответственно регистров 23.i.j+l и 24.i.j+l. Информационные входы регистров 23.1.1 и 24.1.1 являются соответственно первым и вторым информационными входами узла памяти 4.1. Выходы регистра 23.1.М/2 и 24.1.М/2 являются соответственно первым и вторым выходами блока памя ти 4.1. Тактовые входы регистров обеих групп объединены и являются товым ВХОДОМ блока памяти 4.1. Управляющие входы всех регистров блока памяти 4.1, кроме 23,1.М/2 и 24.1.М/2, объединены и подключены к управляющему входу блока памяти 4.1.

Накапливающий сумматор 8.1, где ,N (фиг. З), состоит из сумматора 25.1, регистра 26,1 и логического переключателя 27.1 с третьим состоянием. Первый информационный вход сум

5

0

5

матора 25.1 является входом накапливающего сумматора 8.1, второй информационный вход сумматора 25.1 подключен к выходу регистра 26,1, Вы- ход сумматора 25,1 соединен с информационным входом регистра 26,1, Информационный вход логического переключателя с третьим состоянием 27.1 соединен с выходом регистра 26,1,

Устройство работает следующим образом.

Перед рассмотрением реализации основных режимов условимся, что сдвиг информации в блоке памяти 4,1 (где ,И), запись в регистры накаплива- юпщх сумматоров 8,1, стробиров-ание счетчиков 16 и 17 осуществляются по переднему фронту тактовых сигналов. Условимся также, что передача информации с первых информационных входов мультиплексоров 1, 2, 3 на их выходы и параллельное занесение информации в счетчик 17, выдача информации из накапливающих сумматоров 8.1 и задание первого режима, работы регистров 23.1..и 24,i.j (где ,M/2-l) блоков памяти 4,1 осуществляются подачей сигнала низкого уровня на соответствующие ВХО.ЦЫ, Все регистры

блока памяти 4.1, кроме 23, 1,М/2 и 24.1,М/2, работают в двух режимах, В первом режиме работы регистры передают входную информацию на выход, а во втором режиме- осуществляется запись 5 информации в каждом такте,Регистры 23,1.М/2 и 24.1.М/2 блока памяти 4,1 работают только во втором режиме.

I. , -

Сумматор 25,1 также работает в

0 двух режимах: первый режим - суммирование двух операндов, поступающих на первый и второй информационные входы сумматора 25,1, второй режим - передача операнда, поступающего на

5 первый информационный вход, на выход сумматора. Режим сумматора 25,1 задается управляющим сигналом на входе считывания накапливающего сумматора 8.1, который является также управляю0 щим сигналом для логического переключателя с третьим состоянием 27.i. При активном состоянии на входе считывания накапливающего сумматора 8,1 производится передача информации с

5 входа логического переключателя 27,1 с третьим состоянием на выход накапливающего сумматора 8,1 и одновременно отрабатывается второй режим сумматора 25,1. Тактирую1 Д1й вход ре0

гистра 26,i является входом записи на капливающего сумматора 8.1.

При задании режима работы устройства задается и:режим работы блока 14 синхронизации, причем блок синхронизации может работать в одном из двух режимов. В первом режиме работы блока синхронизации первый 16 и

13632504

жиме мультиплексоры 1, 2 коммутируют первый 9 и второй 10 входы загрузки весовых коэффициентов на первый и второй входы первого 4.1 блока памяти соответственно. Подачей сигнала низкого уровня на управляющие входы блоков памяти 4.1, 4.2,...,4.N задается первый режим работы регистров второй 17 счетчики находятся в режиме д 23.i.j и 24.i.j (где ,M/2-l) блока счета. При этом с выхода переноса памяти 4.1 (где ,N), позтому при второго счетчика 17 через элемент И подаче тактовых сигналов на тактовые 18 низким уровнем управляет дёшифра- входы блоков памяти 4.1, 4.2,...,4.N тор 15, который дешифрирует состояние производится запись весовых коэффици- первого счетчика 16. Во втором режи- g ентоё только в регистры 23.i.M/2 и ме работы блока 14 синхронизации рто- 24.i.M/2 блока памяти 4.1 (где 1 рой счетчик 17 находится в режиме параллельногр занесения, а первый счетчик 16 - в режиме счета. При этом

синхроимпульсы с тактового входа бло-.,, ства на первый вход 9 загрузки весо- ка синхронизации транспортируются че- вых коэффициентов поступают весовые рез второй счетчик на счетный вход коэффициенты а(1),а(2),.,,,a(N), а первого счетчика 16. Управление де- на второй вход 10 - соответственно

1,N).

При разгрузке весовых коэффициентов в данном режиме работы устрой-

шифратором 15 в этом-режиме осуществляется по сигналу низкого уровня, поступающему через элемент И 18 с уп- равляю0(его входа блока синхронизации. Выбор первого режима работы блока 14 синхронизации осуществляется подачей

a(N+l), a(N+2),...,a(2N). Последо- 25 вательность поступления весовых коэффициентов должна быть такой, чтоб в конце загрузки весовьпс коэффициентов в регистрах 23.1.М/2, 23.2.м72, ...,23.1.М/2 были записаны соответ-

сигнала высокого уровня, а второго -,, ственно коэффициенты а( 1 ), а(2).

...,а(Ы), а в регистрах 24.1.М/2, 24.2.К/2,...,24.1.М/2 коэффициенты a(N+l ), a(N+2),... ,a(.2N) .соответственно.

После загрузки весовых коэффици-

режима - подачей сигнала низкого уровня на управлйющий вход блока синхро- низации.

Коэффициент пересчета первого счетчика 16 равен N (от О до N-l),a

коэффициент пересчета второго счетчи- 35 ентов подачей сигнала низкого уров- ка 17 - М/2 (от О до М/2-1).ня обеспечивается коммутация первого и второго выходов последнего 4.N

Рассмотрим работу устройства в g. памяти на выход мультиплексо- режиме вычисления одномерной нерекур- ров 1 и 2 соответственно. В этом режиме правило 40

сивнои свертки,

формирования выходных -отсчетов у(п)

имеет вид:

y(n)a(l)x,(n)+a(2)x(n-l) + ...

+a(2N)x(n-2N+l),

где 2N - число весовых коэффициентов;

a(i) - весовые коэффициенты; x(j),y(n) - отсчеты на входе и выходу устройства соответственно vjj ,2,3,...J..;. Данный режим работы устройства задается подачей.сигналов низкого уровня на входы 20, 21 задания режима работы устройства.

Перед началом работы подачей сигнала высокого уровня на вход 22 производится установка режима загрузки . весовых коэффициентов в блоки памяти группы 4.2, 4.1,...,4.N. В этом ре45

На вход 21 подается сигнал низкого уровня, который обеспечивает коммутацию второго информационного входа 12 устройства на выход мультиплек сора 3.

При работе устройства в данном режиме на первый информационный вход 11 устройства поступают входные отсчеты x(j), а на второй информацион- 50 ный вход 12 устройства - x(j-N) (где ,2,3,...). Подачей сигнала низкого уровня на вход 20 обеспечивается второй режим работы блока 14 синхронизации, при этом начальное состояни первого счетчика 16.равно нулю (входы начальной установки счетчиков не показаны).

Рассм отрим работу устройства в да ном режиме на примере вычисления пол

55

жиме мультиплексоры 1, 2 коммутируют первый 9 и второй 10 входы загрузки весовых коэффициентов на первый и второй входы первого 4.1 блока памя ти соответственно. Подачей сигнала низкого уровня на управляющие входы блоков памяти 4.1, 4.2,...,4.N задается первый режим работы регистров 23.i.j и 24.i.j (где ,M/2-l) блока памяти 4.1 (где ,N), позтому при подаче тактовых сигналов на тактовые входы блоков памяти 4.1, 4.2,...,4.N производится запись весовых коэффици- ентоё только в регистры 23.i.M/2 и 24.i.M/2 блока памяти 4.1 (где 1

1,N).

При разгрузке весовых коэффициентов в данном режиме работы устрой-

a(N+l), a(N+2),...,a(2N). Последо- вательность поступления весовых коэффициентов должна быть такой, чтобы в конце загрузки весовьпс коэффициентов в регистрах 23.1.М/2, 23.2.м72,.. ...,23.1.М/2 были записаны соответ-

ственно коэффициенты а( 1 ), а(2).

...,а(Ы), а в регистрах 24.1.М/2, 24.2.К/2,...,24.1.М/2 коэффициенты a(N+l ), a(N+2),... ,a(.2N) .соответственно.

После загрузки весовых коэффици-

ентов подачей сигнала низкого уров- ня обеспечивается коммутация перво g. памяти на выход мультиплексо- ров 1 и 2 соответственно. 40

45

На вход 21 подается сигнал низкого уровня, который обеспечивает коммутацию второго информационного входа 12 устройства на выход мультиплексора 3.

При работе устройства в данном режиме на первый информационный вход 11 устройства поступают входные отсчеты x(j), а на второй информацион- 0 ный вход 12 устройства - x(j-N) (где ,2,3,...). Подачей сигнала низкого уровня на вход 20 обеспечивается второй режим работы блока 14 синхронизации, при этом начальное состояние первого счетчика 16.равно нулю (входы начальной установки счетчиков не показаны).

Рассм отрим работу устройства в данном режиме на примере вычисления пол-

5

5 .13

ного выходного отсчета при числе ве- совых коэффициентов, равном .Тогда у(п)а(1)х(п)+а(2)х(п-1)+а(3)х(п- -2)+a(4)x{n-3)+a(5)x(n-4)+a(6)x(n-5)

Формирование у(п) начинается в п-м такте на накапливающем сумматоре 8.1с(где и) и заканчивается через N тактов, т.е. к началу (п+И)-го .такта.

Рассмотрим работу устройства в данном режиме по тактам.

Такт.(п).

В регистрах 23.k.M/2 и 24.k.M/2 блока памяти 4.k будут находиться весовые коэффициенты а(3) и а(6) соответственно. На первый информационный вход 11 устройства поступает отсчет х(п-2), а на второй 12 - соответственно х(п-5). Входной течет х(п-2) поступает на вход блока умножения 5.k, а отсчет х(п-5) через мультиплексор 3 - на вход блока умножения b.k. На блоках умножения 5.1 и b.k вычисляются произведения а(3) хСп-2) .и а(6)х(п-5), которые суммируются на сумматоре 7.k. Результат суммирования поступает на вход накапливающего сумматора 8.k. В этом такте с накапливающего сумматора 8.k считывается результат вычисления отсчета у(п-З), поэтому сумматор 25.k работает в режиме передачу операнда, что обеспечивает передачу вычисленной суммы а(3)х(п-2)+а(6)х{п-5) на вход регистра 26.k накапливающего сумматора.8.k. Такт (п+.1).

По переднему фронту (п+1)-го такта в регистры 23.k.M/2 и 24.k.M/2 блока памяти 4.k будут приняты весовые коэффшщенты а(2) и а(5) соответственно, а в регистр 26.k накапливающего сумматора 8 будет записана вычисленная в предьщущем такте сумма а(3)х(п-2)+а(б)х(п-5). На первый информационный вход 11 устройства поступает отсчет х(п-1), а на второй 12 - соответственно х(п-4). Входной отсчет х(п-1) поступает на вход блока умножения 5.k, а отсчет х(п-4) -через мультиплексор 3 - на вход блока умножения 6.k. Вычисленные в блоках умножения 5.k и 6.k произведения а(2)х(п-1) и а{5)х(п-4) суммируются в сумматоре 7.k. В сумматоре 25.k накапливающего сумматора S.k B этом такте будет вычислена сумма а(3)х(п- -2)+а(б)х(п-5))+(а(2)х(п-1)+а(5)х(п- -4)).

0

5

0

5

250

6

Такт (п+2).

По переднему фронту (п+2)-го такта в регистры 23.k.M/2 и 24.k.M/2 блока памяти 4.k будут приняты весовые .коэффициенты а(1) и а(4) соответственно, а в регистр 26.k накапливающего сумматора 8.k будет записана вычисленная в предыдуи.1ем такте сумма.

На первый информационный вход 11 .устройства поступает отсчет х(п), а на второй 12 - соответственно х(п-З). Входной отсчет х(п) в блоке умножения 5.k умножается на весовой коэффициент а(1); а входной отсчет х(п-З) умножается в блоке умножения 6.1с на весовой коэффициент а(4). Вычисленные произведения а(1)х(п) и а(4)х(п- 3) суммируются в сумматоре 7.k. В сумматоре 25.k накапливающего сумматора 8.k в этом такте завершится вычисление выходного отсчета у(п) (a(3)x(n-2)+a(6)x(n-5))+(a(2)x(n-l)+ +a(5)x(n-4)+(a(l)x(n-4)+a(l)x(n)+ +a(4)x(n-3). Такт (n+З).

. По первому фронту (п+3)-го такта в регистры 23.k.M/2 и 24.k.M/2 блока памяти 4.k будут приняты весовые коэффициенты а(3) и а(б) соответственно, а в регистр 26.k накапливающего сумматора 8.k будет записан результат вычисления выходного отсчета у(п). В блоках умножения 5.k и 6.k, сумматоре 7.k будет формироваться 35 первая сумма выходного отсчета у(п+ +3). В этом такте с соответствующего выхода блока 14 синхронизации на вход считывания накапливающего сумматора 8.k поступает управляющий сигнал, который обеспечивает выдачу вычисленного отсчета у(п) на выход 13 результата устройства.

0

40

Рассмотрим работу устройства в ре- 45 жиме вычисления двумерной свер.тки. В этом режиме правило формирования выходных отсчетов имеет вид:

y(m,n)a( 1 ,1 )x(m,n)+a(2,l )x(in-l ,n)+,- .. .+а(М, 1 )x(m-M+l ,n)+a( 1. ,2)x(m,n-l ) + 50 +a(2,2)x(m-l,n-l)+...+a(M,2)x(m-M+l, n-1)+...+a(1,N)x(m,n-N+l)+a(2,N)x(m- -1,n-N+l)+...+a(M,N)x(m-M+l,n-N+l),

55

где M,N - число- весовых коэффициентов;

a(i,k) - весовые коэффициенты (i , )i

х(j|,Jj)y(m,n) - отсчеты соответственно на входе и выходе

8

7 1363250

устройства ( ,2,...,L, пают в следующей последовательности: . J2 , 1,2,...,S, где SL-раз-- x(m-M/2+l ,n-N+l ), x(m-M/2+2, n-N+ мерность входного массива , +1),.. . ,x(m,n-N+l ) ,x(m-M/2+l ,n-N+2), n,2,...,S, ,2,.,.,L) x(m-M/2+2,n-N+l J,... ,x(m,n-N+2),. .. Данный режим работы устройства за- 5 ...,x(in-K/2+l,п),x(m-M/2+2,n),...

...,x(m,n), а на второй информационный вход 12 устройства - соответственно: х(т-М+1,n-N+l),x(m-M+2,n-N+ .+),...,x(m-M/2,n-N+l),x(m-M+l,n-N+ 10 +2),x(m-M+2,n-N+2)5...,x(m-M/2,n-N+ +2),...,x(m-M+l,n),x(m-M+2,n),... ,..,x(m-M/2,n) (где n изменяется от 1 до S при m const (,L)).

По дачей сигнала высокого уровня

этом режиме через каждые М/2 тактов на управляюищй вход дешифратора 15 с второго счетчика 17 через элемент

ного состояния первого счетчика 16 на выход блока 14 синхронизации, поэтому через каждые М/2 тактов рабодается подачей сигнала низкого уровня на вход 21, а сигнала высокого уровня - на вход 20.

Перед началом работы подачей сигнала высокого уровня на вход 22 производится установка режима загрузки весовых коэффициентов в блоки памяти 4.1, 4,2,...,4,N. В этом режиме мультиплексоры 1 и 2 коммутируют первый 9 и второй 10 входы загрузки весовых 5, на вход 20 обеспечивается первый ре- коэффициентов на первый и второй вхо- жим работы блока 14 синхронизации, В ды первого 4.1 блока памяти соответственно. Сигнал высокого уровня, поступающий с входа 20 на управляющие входы блоков памяти 4.1, 4.2,...,4.N,20 И 18 поступает сигнал низкого уровня, обеспечивает второй режим работы всех который разрешает выдачу дешифрован- регистров блоков памяти, поэтому при - подаче тактовых сигналов этот режим предусматривает запись и хранение весовых коэффициентов во. всех регист- -5 ты устройства на выход 13 результата pax блока памяти 4.N (где ). устройства будет выдаваться выходной

При загрузке весовых коэффициен- отсчет. Начальное состояние первого тов в данном режиме работы устройства 16 и второго 17 счетчиков равно ну- на первый вход 9 загрузки весовых лю. Регистр 26,1 накапливающего сум- коэффициентов поступают весовые ко- 30 матора 8.1 (где ,М) в начале работы устройства устанавливается в нулевое состояние (входы начальной установки счетчиков и регистров не показаны).

Формирование выходного отсчета y(m,n) начинается в Т(т-1)S-M/2+ +(п-1)-М/2+1 -м такте на накапливающем сумматоре B.k (где k nmodN) и заканчивается через М/2 тактов, т.е. к началу. T+M/2--N-ro такта.

Рассмотрим работу устройства в режиме вычисления двумерной свертки на примере вычисления полного выходного отсчета для случая , .Тог- 45 да y(m,n)a(l,1)x(m,n)+a(2,l)х(т-1, n)+a(3,-l)x(m-2,n)+a(4,l)x(ri-3,n) +

35

40

эффициенты а(1,1), а(1,2)...,а(1,N),

а(2,1), a(2,2),...,a(2,N)а(М/2,

1), a (M/2,2),...,a(M/2,N), а на второй вход 10 - соответственно а(М/2+ + 1,1), а(М/2+1,2),.. . ,а( М/2-И ,N),. а(М/2+2,1), а(М/2+2,2),...,а(М/2+2, N),...,a(M,l), a(M,2),...,a(M,N). Последовательность поступления весовых коэффициентов должна быть такой, чтобы в конце загрузки в регистрах 23.i.j и 24.i.j (где ,N, J ) были записаны весовые коэффициенты a(j,i) и a(M/2+j i) были записаны весовые коэффициенты a(j,i) и a(M/2+J, 1) соответственно.

После загрузки весовых коэффициентов подачей сигнала низкого уровня

на вход 22 обеспечивается коммутация первого и второго выходов последнего 4.N блока памяти на выход мультиплек-CQ соров 1 и 2 соответственно.

- На вход 21 подается сигнал высокого уровня, который обеспечивает ком-

+а( 1,2)x(in,n-l )+а(2,2)х(т-1 ,п-1 ) + +a(3,2)x(m-2,n-l)+a(4,2)x(m-3,n-l).. Такт (т).

В регистрах 23.k.l, 23.k.2, 24.k.l и 24.k.2 блока памяти 4.k (где k n mod 2) в этом случае будут находиться весовые коэффициенты а(1,2), а(2,2), а(3,2) и а(4,2) соответственВ регистрах 23.k.l, 23.k.2, 24.k. и 24.k.2 блока памяти 4.k (где k n mod 2) в этом случае будут находиться весовые коэффициенты а(1,2), а(2,2), а(3,2) и а(4,2) соответствен

мутацию второго информационного входа 12 устройства на выход мультиплек-gg но. На первь1й информационный вход 11 сора 3.устройства, поступает отсчет ,х(т-1,

При работе устройства в данном режиме на первый информационный вход 11 устройства входные отсчеты посту-

n-l), а на второй вход 12 - соответственно х(т-3, п-1). Входной отсчет х(т-1, n-l) поступает на вход блока

8

ос x( ,x .. (m

По дачей сигнала высокого уровня

вход 20 обеспечивается первый ре работы блока 14 синхронизации, 8 поступает сигнал низкого уровн орый разрешает выдачу дешифрован устройства на выход 13 результат ройства будет выдаваться выходно

этом режиме через каждые М/2 тактов на управляюищй вход дешифратора 15 с второго счетчика 17 через элемент

на вход 20 обеспечивается первый ре- жим работы блока 14 синхронизации, В И 18 поступает сигнал низкого уровня который разрешает выдачу дешифрован- ты устройства на выход 13 результата устройства будет выдаваться выходной

ного состояния первого счетчика 16 на выход блока 14 синхронизации, поэтому через каждые М/2 тактов рабона вход 20 обеспечивается первый ре- жим работы блока 14 синхронизации, В И 18 поступает сигнал низкого уровня, который разрешает выдачу дешифрован- ты устройства на выход 13 результата устройства будет выдаваться выходной

Рассмотрим работу устройства в режиме вычисления двумерной свертки на примере вычисления полного выходного отсчета для случая , .Тог- да y(m,n)a(l,1)x(m,n)+a(2,l)х(т-1, n)+a(3,-l)x(m-2,n)+a(4,l)x(ri-3,n) +

+а( 1,2)x(in,n-l )+а(2,2)х(т-1 ,п-1 ) + +a(3,2)x(m-2,n-l)+a(4,2)x(m-3,n-l).. Такт (т).

В регистрах 23.k.l, 23.k.2, 24.k.l и 24.k.2 блока памяти 4.k (где k n mod 2) в этом случае будут находиться весовые коэффициенты а(1,2), а(2,2), а(3,2) и а(4,2) соответственно. На первь1й информационный вход 11 устройства, поступает отсчет ,х(т-1,

но. На первь1й информационный вход 11 устройства, поступает отсчет ,х(т-1,

n-l), а на второй вход 12 - соответственно х(т-3, п-1). Входной отсчет х(т-1, n-l) поступает на вход блока

9

умножения 5.k, а отсчет xl.m-3, n-1) через мультиплексор 3 - на вход блок умножения 6.k. В блоках умножения 5.k и 6.k вычисляются произведения a{2,2)x(in-l,n-l) и a(4,2)x(m-3,n-l), которые суммируются в сумматоре 7.k. Результат суммирования поступает на вход накапливающего сумматора 8,k. В этом такте с накапливающего сумма тора 8.k считывается результат вычисления отсчета y(m,n-2), поэтому сумматор 25.k работает в режиме переДа- чи операнда, что обеспечивает передачу суммы у (п1,п)а(2,2)х{т-1, п-1)-)г +a(4,2)x(m-3,n-l) на вход регистра 26.k накапливающего сумматора 8.k. Такт (Т+1).

По переднему фронту (Т+1)-го такта в регистры 23.k.l, 23.k.2, 24.k. и 24.k.2 блока памяти 4.k будут приняты весовые коэффициенты а(2,1), a(4,l) и а{3,2) соответственно, а в регистр 26.k накапливающего сумматора S.k будет записана вычисленная в предыдущем такте сумма j 4(m,n). На первый информационный вход 11 устройства поступает отсчет x(ni,n-l), а на второй вход 12 - соответственно x(n-2,n-l). x(m,n-l) поступает на вход блока умножения 5.k, а отсчет х(р1-2,п-1). через мультиплексор 3 - на вход блока умножения 6.k. В Ьлоках умножения 5.k и 6.k вычисляются произведения а(1,2)x(m,n-l) и a(3,2)x(m-2,n-l), которые суммируются в сумматоре 7.k. Результат суммирования поступает на вход накапливающего сумматора B.k, где суммируется с ранее вычисленной суммой y;(m,n).

Такт (Т+2).

По .переднему фронту (Т+2)-го такт в регистры 23.k,l, 23.k.2, 24.k.l и 24.k.2 блока памяти 4,k будут прйня- ты весовые коэффициенты а( 1., 1 ) ,а(2, а{3,1) и a(4 jl) соответственно, а в регистр 26. k накапливающего сумматора 8.k будет записана вычисленная в предыдущем такте сумма y(m,n) у 4in,n)+a(1,2)x(m,n-l)+a(3,2)x(m-2 п-1). На первый информационный вхо 11 устройства поступает отсчет -xCmп), а на второй 12 - соответственно x{m-3,n). Входной отсчет x(m-l,n) в блоке умножения 5.k умножается на всовой коэффициент а(2,1), а отсчет x{m-3,n) в блоке умножения 6.k умножается на весовой коэффициент а.(4,1

0

0

5

3250

g

g

10

Вычисленные произведения суммируются в сумматоре 7.k, результат поступает на вход накапливающего сумматора 8.k, где суммируется с ранее вычисленной суммой у(н1,п). Такт (Т+3).

По переднему фронту {Т+3)-го такта в регистры 23.k.l, 23.k.2, 24.k.l и 24.k.2 блока памяти 4.k будут приняты весовые коэффициенты а(2,2),а(1,1) а(4,2) и а(3,) соответственно, а в регистр 26.k накапливающего сумматора 8.k будет записана вычисленная в предыдущем такте сумма у(in,n); (m, п)+а(2,1)х(га-1,п)+а(4,1)x(m-3,n).Ha первый информационный вход 11-устройства поступает отсчет x(m,n), а на второй 12 - соответственно х(т-2, п). Входной отсчет x(m,n) в блоке умножения 5.k умножается на весовой коэффициент а(1,1), а отсчет x(m-2,n) в блоке умножения 6.k умножается на весовой коэффициент а(3,). Вычисленные произведения суммируются в сумматоре 7.k. В сумматоре 8.k в этом такте будет формироваться окончательный результат вычисления отсчета y(m,n), равный y(m,n)y (m,n)+x(m,n)a( 1., 1) + - +x(m-2,n);a(3,l).

U I

Такт {Т+4).

По переднему фронту этого такта в регистры 23.k.l, 23.k.2, 24.k.l и 24.k.2 будут приняты весовые коэффи- 35 циенты а(1,2), а(2,2), а(3,1) и (4,1) соответственно. В регистр 26.k накапливающего сумматора 8.k по переднему фронту этого такта будет принят вычисленный отсчет y(m,n). В этом такте на вход считывания накапливающего сумматора 8..k- с соответствующего выхода блока 14 синхронизации поступает управляющий сигнал, который обеспечивает выдачу отсчета y(m,n) на выход 13 результата устройства.В блоках умноже ния 5.k, 6.k и сумматоре 7.k в этом такте будет формиро- : ваться первая сумма выходного отсчета у{т,п+2).

40

Рассмотрим работу устройства в режиме вычисления одномерной рекурсивной фильтрации. В этом режиме правило формирования выходных отсчетов у(п) имеет вид:

y(n)a(l)x(n)+a(2)x(n-l)+...+a(N)x -x(n-N+l)+Ъ(1)у(п-1)+Ъ(2)у(п-2)+.... ...+b(N)y(n-N),

10

15

20

25

где И - число весовых коэффициентов; a(i),b(i) - весовые коэффициенты

(,N);

x(j),y(n) - отсчеты на вкоде и выходе устройства соответственно (,2,..., ,2,3,...)

Данный режим работы устройства задается подачей сигнала высокого уровня на вход 21, а сигнала низкого уровня - на вход 20.

Перед началом работы подачей сигнала высокого уровня на вход 22 производится установка режима загрузки весовых коэффициентов в блоки памяти 4.1, 4.2,...,4.N. В этом режиме первый и второй мультиплексоры I, 2 коммутируют первый 9 и второй 10 входы загрузки весовых коэффициентов на первый и второй входы первого 4.I блока памяти соответственно. Подачей сигнала низкого уровня на управляющие входы блоков памяти 4.1,4.2,...,4.N задается первый режим работы регистров 23.i.j и 24.i.j (где , М/2-1) блока памяти 4.1 (где ,N), поэтому при подаче тактовых сигналов на тактовые входы блоков памяти 4.1, 4.2,...,4.N производится запись весовых коэффициентов только в регистры 23.1.М/2 и 24.1.М/ 30 /2 блока памяти 4.1 (где ,N ).

При загрузке весовых коэффициентов в данном режиме работы устройства на первый вход 9 загрузки весовых коэффициентов поступают весовые козффици- 35 енты а(1), а(2),...,a(N), а на второй вход -10 - Ъ(1), Ъ(2),...,b(N) соответственно. Последовательность поступления весовых коэффициентов должна быть такой, чтобы в конце загрузки 40 в регистрах 23.1.М/2, 23.2.М/2,... ...,23.N.M/2 бьши записаны коэффициенты a(l), а(2), a(N) соответственно, а в регистрах 24.Г.М/2, 24.2.М/2,.,. ...,24.N.M/2 - коэффшц1енты Ml.), 45 Ъ(2),...,Ъ(к) соответственно.

После загрузки весовых коэффициентов подачей сигнала низкого уровня, обеспечивается коммутация первого и второго выходов последнего 4.N блока 50 памяти на выход мультиплексоров 1 и 2 соответственно.

На вход 21 подается сигнал высокого уровня, который обеспечивает комПодачей сигнала низкого уровня вход 20 обеспечивается второй режи работы блока 14 синхронизации, при этом начальное состояние первого чика 16 равно нулю. Регистр 26.1 н капливающего сумматора 8.1 (где 1 в начале работы устройства уст навливается в нулевое состояние (в ды начальной установки счетчиков и регистров не показаны).

Формирование выходного отсчета у(п) начинается в(п)-м такте в нак плавающем сумматоре 8.k (где х- mod -Nj и заканчивается через К так т.е. к началу (n+N)-ro такта.

Рассмотрим работу устройства в режиме вычисления одномерной рекур сивной фильтрации на примере вычис ния полного выходного отсчета для случая . Тогда у(п)а(1)х(п)+ +а(2)х(п-1)+а(3)х(п-2)+Ъ(1)у(п-1)+ +Ъ(2)у(п-2)+Ъ(3)у(п-3). .

Такт (п).

В регистрах 23.k.M/2 и 24.k.M/2 блока памяти 4ik (где ,k nmod3) в этом такте будут находиться весовы коэффициенты а(3) и Ъ(3) соответст венно. На первый информационный вх I1 устройства поступает отсчет х(п -2), который в блоке умножения 5.k умножается на весовой коэффициент а(3). С выхода 13 результата устро ства через мультиплексор 3 в блок умножения 6.k поступает выходной о счет у(п-З), вычисленный в предыду

такте, где умножается на коэффицие Ъ(3). Вычисленные -произведения.аСЗ хх(п-2) и Ь(3)у(п-3) суммируются в сумматоре 7.k и поступают на вход накапливающего сумматора S.k. В эт такте с накапливающего сумматора 8 считывается результат вычисления о счета у(п-З), поэтому сумматор 25. работает в режиме передачи операнд что обеспечивает передачу вычисленной суммы уЧп)а(3)х(п-2)+Ъ(3)у(п -3) на вход регистра 26.k накаплив ющего сумматора.S.k.

Такт (п+1)t

По переднему фронту (п+Г)-го так та в- регистры 23.k.M/2 и 24ik.M/2 блока памяти 4.k будут приняты весо вые коэффициенты а(2) и ъ(2) соотве

мутацию информации с выхода 13 резуль зз твенно, а в регистр 26.k накапливающе.го сумматора 8.k будет записан вычисле нная в предьщущем такте сумма у (п). На первый информационный вход 11 устройства поступает отсчет

тата устройства на вькод мультиплексора 3. На первый информационный вход 11 устройства поступают входные отсчеты х(1), х(2), х(3)

0

5

0

5

0

5 0 5

0

Подачей сигнала низкого уровня на вход 20 обеспечивается второй режим работы блока 14 синхронизации, при этом начальное состояние первого счетчика 16 равно нулю. Регистр 26.1 на- капливающего сумматора 8.1 (где ,N) в начале работы устройства уста-Г навливается в нулевое состояние (входы начальной установки счетчиков и регистров не показаны).

Формирование выходного отсчета у(п) начинается в(п)-м такте в нака -. плавающем сумматоре 8.k (где х- mod -Nj и заканчивается через К тактов, т.е. к началу (n+N)-ro такта.

Рассмотрим работу устройства в режиме вычисления одномерной рекурсивной фильтрации на примере вычисления полного выходного отсчета для случая . Тогда у(п)а(1)х(п)+ +а(2)х(п-1)+а(3)х(п-2)+Ъ(1)у(п-1)+ +Ъ(2)у(п-2)+Ъ(3)у(п-3). . .

Такт (п).

В регистрах 23.k.M/2 и 24.k.M/2 блока памяти 4ik (где ,k nmod3) в этом такте будут находиться весовые коэффициенты а(3) и Ъ(3) соответственно. На первый информационный вход I1 устройства поступает отсчет х(п- -2), который в блоке умножения 5.k умножается на весовой коэффициент а(3). С выхода 13 результата устройства через мультиплексор 3 в блок умножения 6.k поступает выходной отсчет у(п-З), вычисленный в предыдущем

такте, где умножается на коэффициент Ъ(3). Вычисленные -произведения.аСЗ) хх(п-2) и Ь(3)у(п-3) суммируются в сумматоре 7.k и поступают на вход накапливающего сумматора S.k. В этом такте с накапливающего сумматора 8.k считывается результат вычисления отсчета у(п-З), поэтому сумматор 25. ) работает в режиме передачи операнда, что обеспечивает передачу вычисленной суммы уЧп)а(3)х(п-2)+Ъ(3)у(п- -3) на вход регистра 26.k накапливающего сумматора.S.k.

Такт (п+1)t

По переднему фронту (п+Г)-го такта в- регистры 23.k.M/2 и 24ik.M/2 блока памяти 4.k будут приняты весовые коэффициенты а(2) и ъ(2) соответ-

твенно, а в регистр 26.k накапливающе.го сумматора 8.k будет записана вычисле нная в предьщущем такте сумма у (п). На первый информационный вход 11 устройства поступает отсчет

3

), который в блоке умножения 5.k умножается на весовой коэффициент а(2). С выхода 13 результата устройства через мультиплексор 3 в блок умножения 6.k поступает выходной отсчет у(п-2), где умножается на коэффициент Ъ(2). Вычисленные произведения a(2)x(n-l) и Ъ(2)у(п-2) суммируются в сумматоре 7.k и поступают на вход накапливающего сумматора 8,k.

В сумматоре 25.k накапливающего сумматора 8.k в этом такте будет вычисленная сумма у Чп)у (п)+а(2)х(п- -1)+Ъ(2)у(п-2).

Такт (п+2).

По переднему фронту (п+2)-го такта в регистры 23.k.M/2 и 24.k.M/2 блока памяти 4.k будут приняты весовые коэффициенты а( 1 ) и Ъ ( 1) соответственно, а в регистр 26.k накапливающего сумматора 8.k будет записана вычисленная в предыдущем такте сумма у(п). На первый информационный вход 11 устройства поступает отсчет х(п), который в блоке умножения 5.k умножается на весовой коэффициент а(1). С выхода 13 результата устройства через мультиплексор 3 в блок умножения 6.k поступает выходной отсчет y(n-l), где умножается на коэффициент Ъ(1). Вычисленные произведения ,. a(l)x(n) иЪ(1)у(п-1) суммируются в

сумматоре 7.k и поступают на вход на капливающего сумматора B.k. В сумматоре 25.k накапливающего сумматора 8.k в этом такте завершится вычисление выходного отсчета (п) у2(п)+(а(1)х(п)+Ъ(1)у(п-1)).

Такт (п+3).

По переднему фронту (п+3)-го такта в регистры 23.k.M/2 и 24,k.M/2 блока памяти 4.k будут приняты весовые коэффициенты а(3) и Ь(3) соответственно, а в регистр 26.k накапливающего суммато.ра 8.k будет записан результат вычисления выходного отсчета у(п). В блоках умножения 5.k, 6.k и сумматоре 7.k будет формироваться певая сумма выходного отсчета j (n+3).

На вход считывания накапливающего сумматора В.Я в этом такте с соответствующего выхода блока 14 синхро-55 к первому информационному входу третьнизации поступает управляющий сигнал, который обеспечивает выдачу вычисленного отсчета у(п) на выход 13 результата устройства.

ормула

14 изобретения

Устройство для цифровой двумерной

свертки, содержащее группу блоков-

памяти, блок синхронизации, гр-уппу

накапливающих сумматоров и перв-ую группу блоков умножения, первый мультиплексор, причем выходы накапливающих сумматоров группы объединены и являются выходом результата устройства, первым информационным входом которого являются объединенные между собой первые входы блоков ум-

ножения первой группы, вторые входы которых подключены к первым выводам соответствующих блоков памяти груп- пы, первый выход i-го (i 1, N-1, N - длина и myльcнoй характеристи-

ки) блока памяти группы подключен к первому информационному входу (i+l)-ro блока памяти группы, первый выход N-ro блока памяти группы подключен к первому информационному.входу пер-

Бого мультиплексора, второй информа- ционный вход которого является первым входом загрузки весовых коэффициентов устройства, первый информационный вход первого блока памяти

группы подключен к выходу первого мультиплексора, управляющий вход которого является первым входом задания режима работы устройства, входы считьшания накапливающих сумматоров

группы подключены к соответствующим выходам блока синхронизации, тактовый вход которого является тактовым входом устройства, отличающе-- е с я тем, что, с целью расширения

функциональных возможностей путем реализации рекурсивной двумерной и одномерной фильтрации, в него введены вторая группа блоков умножения, второй и третий мультиплексоры, группа сумматоров, причем выход второго мультиплексора подключен к первым входам блоков умножения второй группы, вторые входы которых подключены к вторым выходам соответствующих блоков памяти группы, второй выход i-ro блока памяти группы подключен к второму информационному входу, (i+ 1)-го блока памяти группы, а второй выход N-ro блока памяти группы подключен

его мультиплексора, второй информационный вход которого является вторым входом загрузки весовых коэффициентов устройства, второй информа151

ционньп вход первого блока памяти группы подключен к выходу третьего мультиплексора, управляющий вход которого подключен к первому входу задания режима работы устройства., выходы блоков умножения первой группы подключены к первым входам соответствующих сумматоров группы, вторые входы которых подключены к вьпсодам соответствующих умножителей второй группы, выходы сумматоров группы подключены к информационным входам соответствующих накапливающих сумматоров группы, первый информационный

16

вход второго мультиплексора является вторым информационным входом устройства, выход результата которого подключен к второму информационному входу второго мультиплексора, управляющий вход которого является вторым входом задания режима работы устройства, тактовые входы блоков памяти соединены между собой и подключены к тактовому входу устройства, входом запуска которого являются соединенные между собой входы начальной ycTat oBKH блоков памяти группы и вход запуска блока синхронизации.

Фие.З

Редактор Л.Веселовская

Составитель А.Баранов Техред А.Кравчук

Заказ 6365/43

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор В.Гирняк

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления быстрого преобразования Фурье | 1988 |

|

SU1508233A1 |

| Цифровой фильтр | 1980 |

|

SU955512A1 |

| Цифровой фильтр | 1985 |

|

SU1327281A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Арифметическое устройство процессора быстрого преобразования Фурье | 1981 |

|

SU999061A1 |

| Устройство для цифровой фильтрации | 1987 |

|

SU1499374A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

Изобретение относится к вычислительной технике, и может быть использовано при обработке двумерных и одномерных массивов данных большой размерности, например для фильтрации сигналов или обработки изображений. Цель изобретения - расширение функциональных возможностей путем выполнения рекурсивной двумерной и одномерной фильтрации. Поставленная цель достигается за счет того, что в состав устройства входят мультиплексоры 1-3, группа блоков памяти 4.14.N, первая 5.1,...,5.N, вторая 6.1,...,6.N группа блоков умножения, группа сумматоров 7 ..1,..., 7 .N., группа накапливающих сумматоров 8.1, ... ,8.N, входы загрузки весовых коэ фициентов 9у 10, информационные входы 11, 12, выход результата 13, блок синхронизации 14, состоящий из дешифратора 15, счетчиков 16, 17, элемента И 18, тактовый вход 19, входы задания режима работы 20, 21 и вход запуска 22. 3 ил.(Л 00 О5 со ю ел

| Устройство для цифровой фильтрации | 1984 |

|

SU1211748A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для цифровой двумерной свертки | 1984 |

|

SU1196871A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-29—Подача