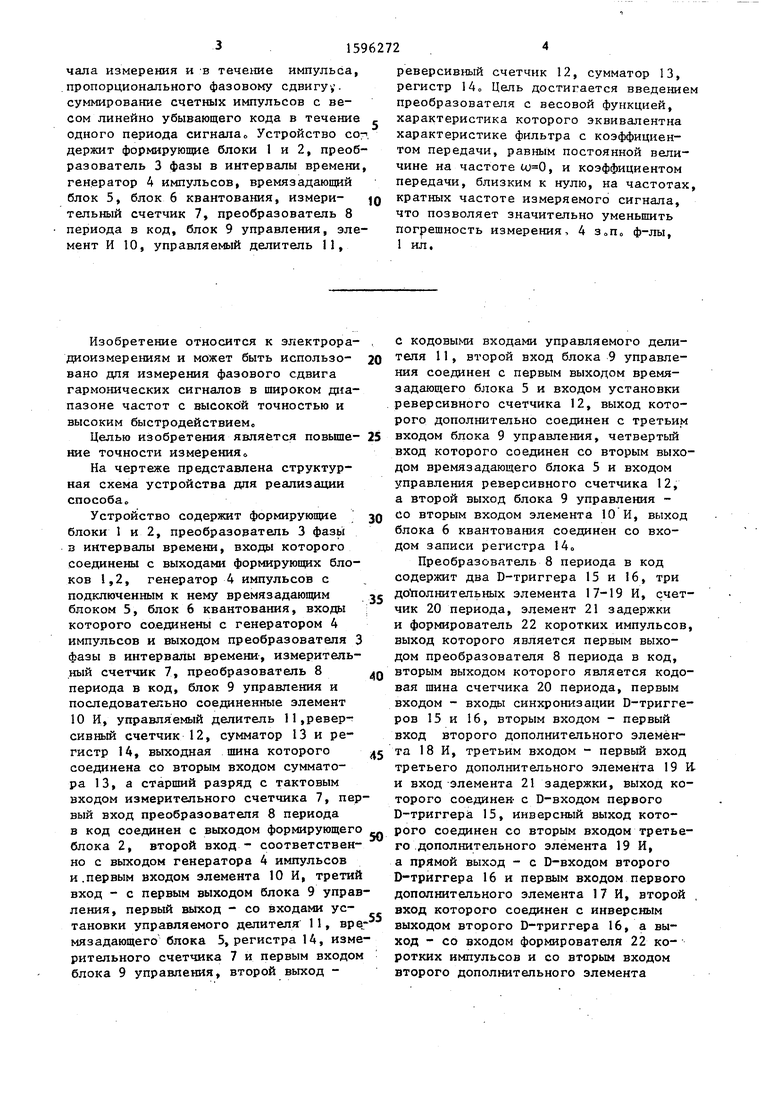

чала измерения ив течение импульса, .пропорционального фазовому сдвигуvсуммирование счетных импульсов с весом линейно убывающего кода в течение одного периода сигнала Устройство со-, держит формирующие блоки 1 и 2, преобразователь 3 фазы в интервалы времени, генератор 4 импульсов, времязадающий блок 5, блок 6 квантования, измери- JQ тельный счетчик 7, преобразователь 8 периода в код, блок 9 управления, элемент И 10, управляемый делитель 11,

реверсивный счетчик 12, сумматор 13, регистр 14о Цель достигается введением преобразователя с весовой функцией, характеристика которого эквивалентна характеристике фильтра с коэффициентом передачи, равным постоянной величине на частоте , и коэффициентом передачи, близким к нулю, на частотах, кратных частоте измеряемого сигнала, что позволяет значительно уменьшить погрешность измерения, 4 ф-лы, 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1981 |

|

SU970258A1 |

| Генератор-калибратор временных интервалов | 1985 |

|

SU1367138A1 |

| Широкопредельный цифровой фазометр | 1983 |

|

SU1128189A1 |

| Генератор-калибратор временных интервалов | 1985 |

|

SU1367139A1 |

| Цифровой фазометр с постоянным измерительным временем | 1982 |

|

SU1045162A2 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Цифровой фазометр | 1981 |

|

SU1029100A1 |

| Цифровой фазометр с постоянным измерительным временем | 1984 |

|

SU1167528A1 |

| Цифровой компенсатор | 1972 |

|

SU439915A1 |

| Двухканальный фазовый компаратор | 1988 |

|

SU1538144A1 |

Изобретение может быть использовано для измерения фазового сдвига гармонических сигналов в широком диапазоне частот. Цель изобретения - повышение точности измерения фазового сдвига. Способ измерения фазового сдвига включает формирование фиксированного временного интервала, формирование прямоугольных импульсов с длительностью, пропорциональной фазовому сдвигу заполнение сформированных прямоугольных импульсов счетными импульсами и их подсчет за фиксированный временной интервал, измерение периода входного сигнала и запоминание его, далее в течение импульса, пропорционального фазовому сдвигу, суммирование счетных импульсов с весом линейно увеличивающегося кода в течение одного периода измеряемого сигнала от начала измерения и в течение импульса, пропорционального фазовому сдвигу, суммирование счетных импульсов с весом линейно убывающего кода в течение одного периода сигнала. Устройство содержит формирующие блоки 1 и 2, преобразователь 3 фазы в интервалы времени, генератор 4 импульсов, времязадающий блок 5, блок 6 квантования, измерительный счетчик 7, преообразователь 8 периода в код, блок 9 управления, элемент И 10, управляемый делитель 11, реверсивный счетчик 12, сумматор 13, регистр 14. Цель достигается введением преобразователя с весовой функцией, характеристика которого эквивалентна характеристике фильтра с коэффициентом передачи, равным постоянной величине на частоте ω=0, и коэффициентом передачи, близким к нулю, на частотах, кратных частоте измеряемого сигнала, что позволяет значительно уменьшить погрешность измерения. 4 з.п. ф-лы, 1 ил.

Изобретение относится к электрорадиоизмерениям и может быть использовано для измерения фазового сдвига гармонических сигналов в широком диапазоне частот с высокой точностью и

высоким быстродействием

Целью изобретения ЯВЛЯЕТСЯ повьшекие точности измерения

На чертеже представлена структурная схема устройства для реализации способа

Устройство содержит формирующие блоки 1 и 2, преобразователь 3 фазы в интервалы времени, входы которого соединены с выходами формирующих блоков 1,2, генератор 4 импульсов с подключенным к нему времязадающим блоком 5, блок 6 квантования, входы которого соединены с генератором 4 импульсов и выходом преобразователя 3 фазы в интервалы времени, измерительный счетчик 7, преобразователь 8 периода в код, блок 9 управления и последовательно соединенные элемент 10 И, управляемый делитель 11 ,ревер-: сивный счетчик 12, сумматор 13 и регистр 14, выходная шина которого соединена со вторым входом сумматора 13, а старший разряд с тактовым входом измерительного счетчика 7, первый вход преобразователя 8 периода в код соединен с выходом формирующего блока 2, второй вход - соответственно с выходом генератора 4 импульсов и.первым входом элемента 10 И, третий вход - с первым выходом блока 9 управления, первый выход - со входами установки управляемого делителя 11, вр мязадающего блока 5, регистра 14, измерительного счетчика 7 и первым входом блока 9 управления, второй выход с кодовыми входами управляемого делителя 11, второй вход блока 9 управления соединен с первым выходом времязадающего блока 5 и входом установки реверсивного счетчика 12, выход которого дополнительно соединен с третьим входом блока 9 управления, четвертый вход которого соединен со вторым выходом времязадающего блока 5 и входом управления реверсивного счетчика 12, а второй выход блока 9 управления со вторым входом элемента 10 И, выход блока 6 квантования соединен со входом записи регистра 14

Преобразователь 8 периода в код содержит два D-триггера 15 и 16, три дополнительных элемента 17-19 И, счетчик 20 периода, элемент 21 задержки и формирователь 22 коротких импульсов выход которого является первым выходом преобразователя 8 периода в код, вторым выходом которого является кодовая шина счетчика 20 периода, первым входом - входы синхронизации D-триггеров 15 и 16, вторым входом - первый вход второго дополнительного элемента 18 И, третьим входом - первьй вход третьего дополнительного элемента 19 Ии вход элемента 21 задержки, выход которого соединен- с D-входом первого D-триггера 15, инверсный выход которого соединен со вторым входом третьего .дополнительного элемента 19 И, а прямой выход - с D-входом второго D-триггера 16 и первым входом первого дополнительного элемента 17 И, второй вход которого соединен с инверсным выходом второго D-триггера 16, а выход - со входом формирователя 22 коротких импульсов и со вторым входом второго дополнительного элемента 18и, выход которого соединен с такто вым входом счетчика 20 периода, вход установки которого соединен с выходом третьего дополнительного элемента 19И,. Блок 9 управления содержит дешифратор 23, вход которого является третьим входом блока 9 управления, два элемента 24, 25 ИЛИ, входы первого элемента 24 ИЛИ соединены с выходами дешифратора 23, а входы второго элемента 25 ИЛИ являются первым ивторым входами блока 9 управления, управляе-мый триггер 26, входы которого подключены к выходам элементов 24, 25 ИЛИ, а прямой выход является вторым выходом блока 9 управления, и четвертый дополнительный элемент 27 И, первый вход которого соединен с инверсным выходом управляемого триггера 26, второй вход является ч:етвертым входом блока 9 управления, а выход - первым выходом блока 9 управления. Времязадающий блок 5 содержит последовательно соединенные пятый дополнительный элемент 28 И, времязадаю щий делитель 29, выход которого является первым выходом времязадающего блока 5, и второй управляемый триггер 30, второй вход которого является входом установки времязадающего блока 5, инверсный выход - вторым выходом времязадающего блока 5, прямой выход соединен со вторым входом пятого дополнительного элемента 28 И, пер вый вход которого является первым вхо дом времязадающего блока 5-, Способ осуществляют следующим образом. В общем виде результат измерения можнопредставить в виде TH i/ 1 Jg(t).S(t)dt, (1) где Т - время измерения; SCt) - прямоугольные импульсы единичной амплитуды с дпительностью t, ( срУЗбО) и перио дом Т; . Lp - измеряемый фазовый сдвиг; Т - период измеряемого сигнала; g(t) - весовая функция t/T для , 1 для T,.. +Т - -) для И и Как видно из (1), измерительная часть фазометра может быть представ152 лена в-виде линейного фильтра с тотной характеристикой Л(а/), определяемой преобразованием Фурье от весовой функции g(t) Ти . Ф() I g(t) Сигнал S(t) можно представить в виде S(t)(t),(4) где Sjj - постоянная составляющая S(T), равная /5S(t) - переменная составляющая S(t), Результат измерения можно представить в виде составляющей, соответствующей истинному значению измеряемого фазового сдвига, равной произведению постоянной составляющей S на значение частотной характеристики на частоте и составляющей, соответствующей погрешности и определяемой суммой произведений гармонических составляющих переменной части S(t) на значения частотной характеристики Ф(ьи) на соответствуюш 1х частотах. Подставляя (2) в (3), получим следующее выражение для модуля частотной характеристики измерительного тракта фазометра sincuTiY/2 brajM T «. - « WT/2 Значение частотной характеристики на частоте Ф(а)0)Т , составляющая, соответствующая истинному значению измеряемого фазового сдвига, определяется Ф()360 1 (f (8) т-- и равна измеряемому фазовому сдвигу (. Гармонические составляющие сигкала S(t) соответствуют частотам, кратным частоте измеряемого сигнала На этих частотах значения частотной характеристики Ф(са) равны нулю. Благодаря этому погрешность будет равна нулю о При практическойреализации во многих случаях вес линейно увеличивающегося кода и вес линейно убьшающегокода целесообразно изменять в дискретиые моменты времени с некоторым шагом Т. Вместо идеальной линейной функции в этом случае будет иметь место ступенчато-аппроксимированная линейная функ ция. Число интервалов аппроксимации будет равно 1-T/JT. Для такой функции g(t) частотная характеристика эквивалентного фильтра определяется выражением фл.) 1 ./2.. .4 - (1о 1 72 } Значение частотной характеристики на частотах гармонических составляющи измеряемого сигналасо па) равно sin пи)оГи/2 1-е |Ф(,)| 1 е-;г1ги Как видно из (11), значения частотной характеристики в частотных точ ках w п ы равны нулю, кроме точек, кратных а)1сОд, Тое, равных oi) °nila(,, где ,2,3... В этих точках максимальное значение частотной характерис тики равно ),)2/1Гт1(12) Если просуммировать произведение значений Ф () на амплитуды спектральных составляющих сигнала S(t с учетом размерности, то получим 90/К1.; ЧмакГЭО/К.-.(13) Таким образом, как видно из (13), при ступенчато-изменяющейся весовой функции g(t) погрешность имеется, но она уменьшается в 1 раза Устройство дпя осуществления спосо ба работает следующим образом Входные сигналы поступают на входы формирующих блоков 1 и 2о Формирующие блоки 1 и 2 обычно выполняются в виде усилителей-ограничителей. Тое на их выходе формируются прямоугольные импульсы, фронты и срезы которых привязаны, к переходам входных сигналов через нулевой уровень Прямоугольные импульсы с выходов формирующих блоков 1 и 2 поступают на преобразователь 3 фазы в интервалы времени, осуществляю щий преобразование измеряемого фазово го сдвига в эквивалентные инт ервалы . времени по положительным и отрицательным нуль-переходам исследуемых сигналов, В блоке 6 квантования временные интервалы заполняются счетшши импульсами частотой от генератора 4 импульсов Времязадающий блок 5 под действием импульсов генератора 4 импульсов формирует фиксированный интервал времени T,, равный ,g где К - коэффициент деления времязадающего делителя 29. Величина коэффициента К определяет размерность отсчета фазового сдвига Счетные импульсы, поступающие из блока 6 квантования на вход записи регист--. ра 14, вызывают накопление измерительной информации с весом, определяемым кодом реверсивного счетчика 12о Это происходит в связи с тем, что на входе данных регистра 14 имеет место выходной код сумматора 13, представляющий из себя суммарнь1й код регистра 14 и реверсивного счетчика 12, К старшему разряду регистра 14 подключен измерительный счетчик 7, осуществляющий окончательное накопление результирующего кода. Изменение веса данных измерения происходит под действием импульсов, поступающих с выхода управляемого делителя 11 на тактовый вход реверсивного счетчика 12, На тактовый вход управляемого делителя П через элемент 10 И поступают импульсы .с генератора 4 импульсов Коэффициент деления управляемого делителя 11 задается счетчиком 20 периода преобразователя 8. периода в код таким образом, чтобы за период входного сигнала на выходе управляемого делителя 11 имело место 1 импульсов Это достигается следующим образом По сигналу конца времяизмерительного цикла (логическая единица), поступающему с выхода элемента 27 И блока 9 управления, и под действием импульсов сигнала на выходе формирующего блока 2, поступающих на первый вход преобразователя 8 периода в код, срабатывают D-триггеры 15 и 16 Появление единичного потенциала на выходе второго D-триггера 16 относительно первого D-триггера 15 сдвинуто на период сигнала Н результате этого на выходе первого дополнительного элемента 17 имеет место импульс дпительностью, соответствующей периоду сигнала Сформированный интервал времени заполняется во втором дополнительном элементе 18 И импульсами генератора 4 импульсов, а полученная таким образом пачка импуль-сов подсчитывается счетчиком 20 периода. Структура этого счетчика включает делитель на 1 и счетчик, выходная шина которого подключается к кодовому входу управляемого делителя I1„ Начальная устаной ка счетчика осуществляется сигналом с выхода третьего дополнительного элемента 19 И, имеющим место перед появлением счетных импульсов счетчика 20 периода, в пауэе между измерениями Минимальная длительность этог сигнала ограничена величиной задержки элемента 21 задержки . По завершении процесса измерения кода периода с помощью формирователя 22 коротких импульсов производится начальная установка управляемого делителя 11, регистра 14, измерительного счетчика 7, запуск первого управляемого триггера 26 блока 9 управления и вто рого уп)авляемого триггера 30 времязадающего блока 5 Указанные триггеры переключаются в единичное состояние, определяющее начало цикла измеренияо Пятый дополнительныйэлемент 28 И открывается, и на тактовый вход времязадающего делителя 29 начинают поступать импульсы генератора 4 импульсов, начиная формировать фиксиро ванный интервал времени Т. Одновременно через открытый элемент 10 И на вход управляемого делителя 11 начина ется поступление импульсов генератора 4 импульсов о Управляемый делитель целесообразно выполнить на реверсивных счетчиках (например, 1533ИЕ7}, работающих в вычитающем режиме. При этом выход переноса счетчика нужно подключить ко входу управления записью информации кодовых входов. Указанная структура управляемого делите ля I 1 позволяет обеспечить прямое управление его коэффициентом деления кодом счетчика 20 периода. Начальное состояние управляемого делителя 11 устанавливается нулевым, в связи с чем первый же импульс на тактовом входе управляемого делителя 11 приво дит к появлению импульса на его выходе и предустановке его разрядов в состояние, соответствующее коду пери да Начальное состояние реверсивного счетчика 12 также нулевое, что соответствует его состоянию в конце предыдущего измерительного цикла В течение времени формирования фиксированного интервала времени Т режим счета реверсивного счетчика 12 - сум м {рующий, ЧТО определяется соотт:.;;тствующим потенциалом на его упра.е.ля;ощем входе. Поскольку одновремето с | началом цикла измерения на тактовый вход реверсивного счетчика 12 поступает импульс с выхода управляемого делителя 11, то начальный вес данных измерения соответствует коду единицы о В дальнейшем в течение периода сигнала код реверсивного счетчика 12 лг;-нейно возрастает от 1 до 1, По д;остижении кода реверсивного счетчика 12 числа 1 срабатывает дешифратор 23 блока 9 управления и через элемент 24 11ГШ на динамический вход установки в ноль управляемого триггера 26 поступает переключающий перепад напряжения, Переключение указанного триггера приводит к закрытию элемента 10 И и постоянству кода 1 реверсивного счетчика 12 до конца фиксированного интервала времени. Завершение фиксированного интервала време1Ш опредачяется переполнением времязадающего делителя 29. При этом происходит переключение в ноль второго управляемого триггера 30, что в свою очередь ПРИБОДРИТ -к закрытию пятого дополнительного элемента 28 И и смене режима счета реверсивного счетчика 12 на вычитаюгдийо Одновременно реверсивный счетчик 12 предустанавливается в состояние, соответствующее коду 1-1. Кроме этого, через элемент ИЛИ 25 происходит переключение управляемого триггера 26 в состояние логической единицы,, в связи с чем элемент 10 И открывается и начинается формирование линейно убывающего кода По достижешш нулевого кода реверсивного счетчика 12 срабатывает дешифратор 23, что приводит к переключению управляемого триггера 26 в ноль о Процесс измерения завершается, что фиксируется четвертым дополнительным элементом 27 IL Технико-экономический эффект способа и устройства дпя его осуществления заключается в уменьшеш и погрешности дискретного преобразования на низких частотах, что приводит к повышению точности измерегдая, а следовательно, расширению диапазона рабочих частот и повышению быстродействия, Формула изобретения 1, Способ измерения фазового сдвига между двумя гармоническими сигналами, Е котором формируют фиксирован ный временной интервал и прямоугольные импульсы с длительностью, пропор циональной фазовому сдвигу, заполняют сформированные прямоугольные импульсы счетными импульсами и подсчитывают их за фиксированный временной интервал, отличающийся тем, что, с целью повьппения точности измерения, дополнительно измеряют период входного сигнала и запоминают его, далее в течение импульса, пропорционального фазовому сдвигу, суммируют счетные импульсы с весом линейно увеличивающегося кода в течение одного периода измеряемого сигнала от начала измерения и после конца стандартного временного интервала в течение импульса, пропорционального фазовому сдвигу, суммируют счетные импульсы с весом линейно убывающего кода, в течение одного периода сигнала 2 о Устройство для измерения фазового сдвига между двумя гармоническими cигнaлa йI содержащее два формирующих блока, входы которых являются входами устройства, преобразова тель фазы в интервалы времени, входы которого соединены с выходами формирующих блоков, генератор импульсов с подключенным к нему времязадающим блоком, блок квантования, входы кото рого соединены соответственно с выхо дами преобразователя фазы в интервалы времени и генератора импульсов, и измерительный счетчик, отличаю щееся тем, что, с целью повышения точности измерения, устройство снабжено преобразователем периода в код, блоком управления и последова тельно соединенными элементом совпадения, управляемым делителем, ревер сивн1 1м счетчиком, сумматором и регистром, выходная шина которого соединена с вторым входом сумматора, а старший разряд - с тактовым входом измерительного счетчика, первый вход преобразователя периода в код соединен с. выходом второго формирующего блока, второй вход - соответственно с выходом генератора импульсов и первым входом элемента совпадения, третий вход - с первым входом блока управления, первый выход - с входами установки управляемого делителя, вре мязадающего блока, регистра, измерительного счетчика и первым входом блока управления, второй выход - с кодовыми входами управляемого делителя, второй вход блока управления соединен с первым выходом времязадающего блока и входом установки реверсивного счетчика, выход которого дополнительно соединен с третьим входом блока управления, четвертый вход которого соединен с вторым выходом времязадающего блока и входом управления реверсивного счетчика, а второй выход - с вторым входом элемента совпадения, выход блока квантования соединен с входом записи регистра, Зо Устройство по п. 2, отличающееся тем, что преобразователь периода в код содержит два D-триггера, три дополнительных элемента совпадения, счетчик периода, элемент задержки и формирователь коротких импульсов, выход которого является первым выходом преобразователя периода в код, .вторым выходом которого является кодовая шина счетчика периода, первым входом - входы синхронизации D-триггеров, вторым входом - первый вход второго дополнительного элемента совпадения, третьим входом - первый вход третьего дополнительного элемента совпадения и вход элемента задержки выход которого соединен с D-входом первого D-триггера, инверсный выход которого соединен с вторым входом третьего дополнительного элемента совпадения, а прямой выход - с D-входом второго D-триггера и первым входом первого дополнительного элемента совпадения, второй вход которого соединен с инверсным выходом второго D-триггера, .а выход - с входом формирователя коротких импульсов и с вторым входом второго дополнительного элемента совпадения, выход которого соединен с тактовым входом счетчика периода, вход установки которого соединен с выходом третьего дополнительного элемента совпадения 4, Устройство по По 2, отличающееся тем, что блок управления содержит дешифратор, вход которого рвляется третьим входом блока управления, два элемента ИЛИ, входы первого элемента ИЛИ соединены с выходами дешифратора, а входы второго являются первым и вторым входами блока управления, управляемый триггер, входы которого подключены к выходам элементов ИЛИ, а прямой выход является вторым выходом блока управления и четвертый дополнительный элемент совпадения, первый вход которого соединен с инверсным выходом управляе мого триггера, второй вход является четвертым входом блока управления, а выход - первым выходом блока управления « 5, Устройство по По 2, отличающееся тем, что времязадающий блок содержит последовательно соединенные пятый дополнительный элемент совпадения, времязадающий делитель, выход которого является первым выходом времязадающего блока, и второй управляемый триггер, второй вход которого является входом установки времяэадающего блока, инверсный выход - вторым выходом времязадающего блока, прямой выход соединен с вторым входом пятого дополнительного элемента совпадения, первый вход которого является первым входом времязадающего блока.

| Цифровые методы измерения сдвига фаз о Новосибирск, 1979, с, 33-34 о Там же, Со 25, рис о 1.19» |

Авторы

Даты

1990-09-30—Публикация

1988-07-07—Подача