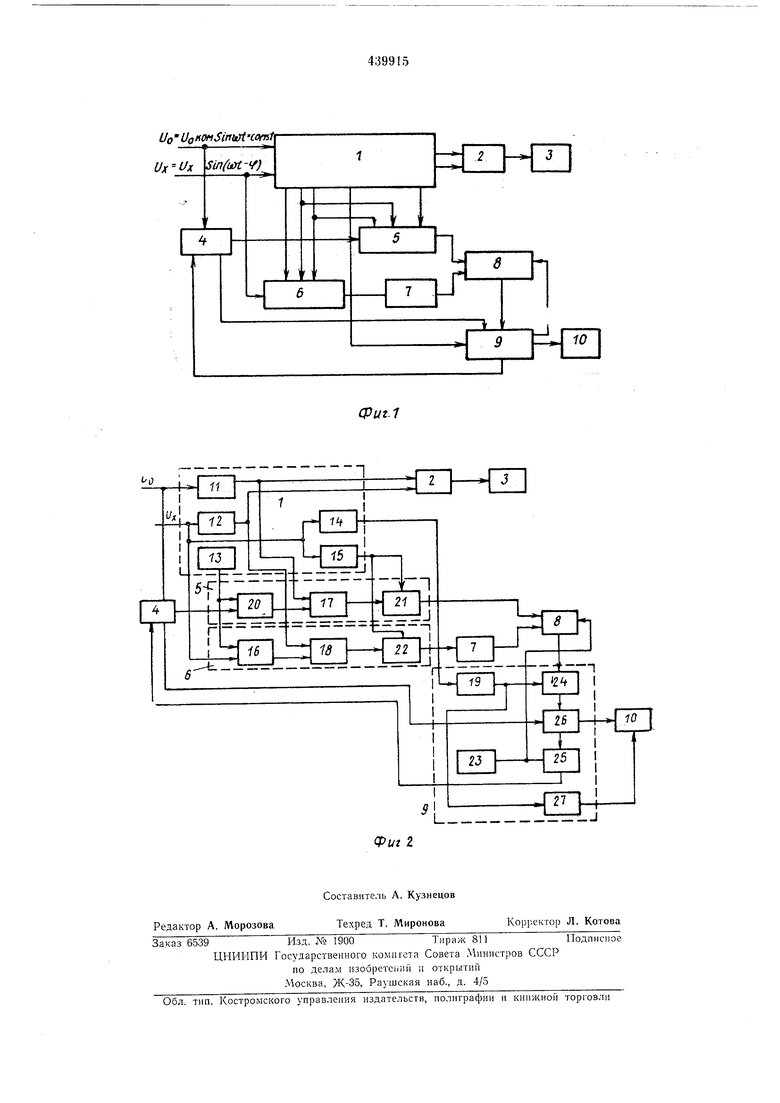

2

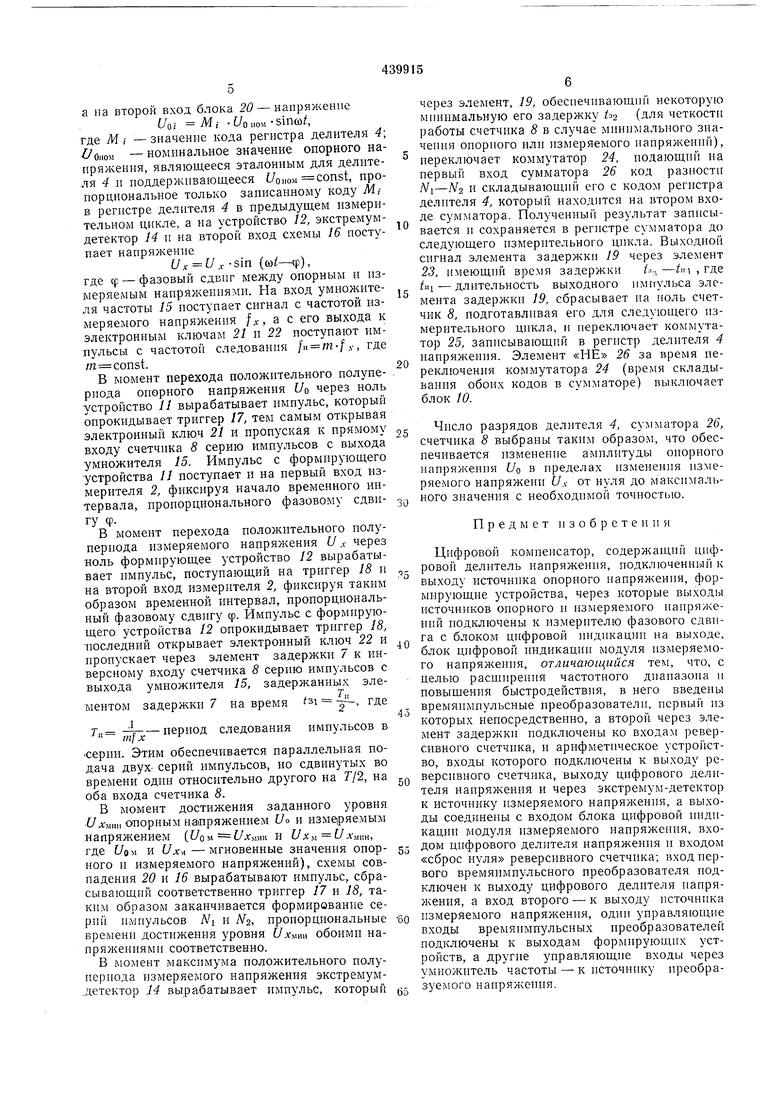

(в качестве эталонного) и на вход формирующего устройства 11, а измеряемое напряжение Ux Vx-5m((i)t-ф) поступает на второй вход схемы совпадения 16, иа вход формирующего устройства 12, экстремум-детектора 14 и умножитель частоты 15. Выходы формирующих устройств 11 и 12 подключеиы к опрокидывающему входу триггеров 17 и 18 соответственно и к обоим входам измерителя 2 фазового сдвига, а выход экстремум-детектора 14 - к элементу задержки 19 арифметического устройства 9. Источник 13 эталонного постоянного напряжения EQ с величиной Eo , где дгмип- значение возможной мииимальной амплитуды измеряемого напряжения, подключей к первому входу схем совпадения 20 и 16. Входным сигиалом умножителя частоты 15 является частота измеряемого напряжения L.r, а его выход иодключен к ииформациоииому входу электронных ключей 21 и 22.

Времяимпульсные преобразователи 5 6 идентичны и преобразуют время достижен Я заданного уровня опорным и измеряемым папряжениями в пропорциональное число импульсов и каждый из них содержит следующие узлы: для времяимпульспого преобразователя 5 - схема совпадения 20, триггер с разделениым управлением 17 и электронный ключ 2/; для времяимпульсного преобразователя 6 - схему совпадения 16, триггер 18 и электронный ключ 22, причем первые входы схем совпадеиия 20 и 16 иодключеиы к выходу источипка 13, а второй вход схемы совпадения 20 - к выходу цифрового делителя напряжения 4, иа второй вход схемы совпадения 16 поступает измеряемое напряжение /7л. Выходы схем совпадения 20 и 16 соединеиы со сбрасывающим входом триггеров 17 и 18. а их опрокидывающий вход - с выходом формирующих устройств // и 12 соответственно.

Выходы триггеров 17 и 18 соединены с управляющим входом электронных ключей 21 и 22 соответственно, а их информационные входы - с выходом умножителя частоты 15. Выход электронного ключа 21 подключен к прямому входу реверсивного счетчика импульсов 8, а его инверсный вход через элемент задержки 7 - к выходу электронного ключа 22.

Выходным сигналом реверсивного счетчика импульсов 8 является двоичный код, пронорциональиый разности серии импульсов Л и Лг, поступившие на его входы с времяимпульсных преобразователей 5 п 6 соответственно. Этот код является прямым при положительной разности и дополнительным при отрицательной разности. Вход «сброс нуля реверсивного счетчика импульсов 8 подключен к выходу элемента задерн ки 23, а его выходы подключены ко входам многоканального коммутатора 24 арифметического устройства 9.

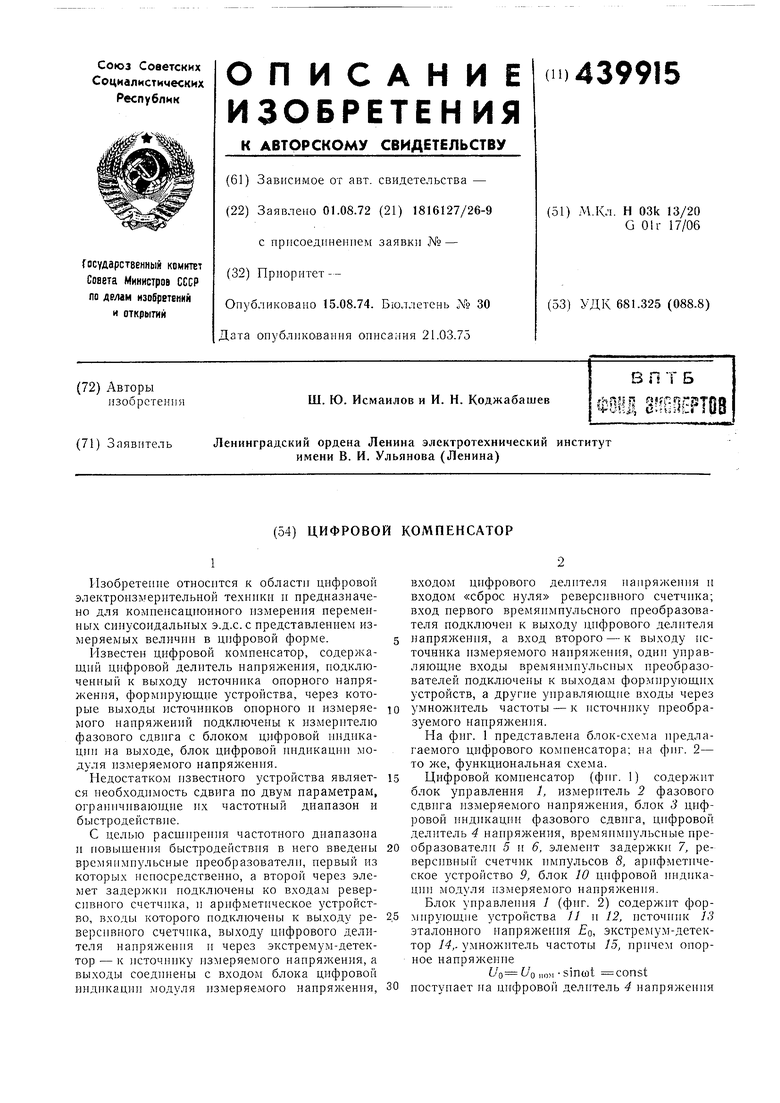

Арифметическое устройство 9 вырабатывает код управления цифрового делителя 4 наиряжеиия, управляет счетчиком 8 и блоком W цифровой индикации модуля измеряемого напряжения и содержит элементы задержки 19

и 23, многоканальные коммутаторы 24 и 25, су.мматор 26 с регистром и элемент «НЕ 27, причем вы.ходной сигиал экстремум-детектора 14 поступает на вход элемента задерлски 19, элементу «НЕ 27 и уиравляющему входу многоканального коммутатора 24. Выходной сигиал элемента задержки 19 иа время импульса переключает многоканальный коммутатор 24 )1 подключает выходы реверсивного счетчика пмиульсов 8 к иервому входу сумматора 26 с регистром, на второй вход которого подключены выходы регистра цифрового делителя 4 напряжения. Выходной сигнал элемента задержкн 19 через элемент «НЕ 27 управляет блоком 10 цнфровой нндпкации модуля измеряемого напряжения, а выходной сигиал элемента задержки 23 сбрасывает иа ноль реверсивный счетчик импульсов 8 и иереключает многоканальный коммутатор 25, подключая на время имиульса выходы сумматора 26 ко входам регистра цифрового делителя 4 иапряжеиия, который вырабатывает оиорное напряжение f/o, причем регистр делителя 4 управляет коммутирующими бескоитактиыми элементами сумматора 26, последним вырабатывается по заиисаииому коду в регистре величина опорного напряжения.

Цифровая индикация модуля блока W измеряемого наиряжеиия

и .v U ,f sin ((.}/-ф)

подключена к выходам сумматора 26 и индицирует значеь ие величины модуля U.i по заиисаииому коду в его регистре, являющемуся числовым эквивалентом модуля измеряемого наиряжеиия t/.v п одиозиачио связаииым с зиачением модуля оиорного иаиряжеиия /7о по окончании отработки результата сравиеиия.

Часть схемы цифрового комиенсатора, состоящая из иреобразователя 5, эле.меитов 4-9 и управляемая блоком 1, работает в следящем режиме, обеспечивая тем самым автоматическое сравиеиие, слежение и измереиие неизвестного наиряжения U ио величине оиорного напряженпя Соизмерение и индикация фазового сдвига ф между опорным f/o п иеизвестиым У ,t напряжениями осуществляется с помощью пзмерителя 2 фазового сдвига п измеряемого иапряжеиия ио известному ириицииу цифровых фазометров, причем временной интервал, пропорциональный фазовому сдвигу ф, формируется выходиыми сигналами формирующих устройств // и 12.

Предлагаемое устройство работает следуюп;им образом.

В исходном состоянни иа иервые входы блоков 20 и 16 подано эталониое иапряжеиие Ef)Uхтн, в регистре делителя 4 и в регистре сумматора 26 заиисаи код Mi с предыдущего измерительного цикла, счетчик 8 очищеи.

При подаче опорного напряжения /Уоиом и измеряемого иапряжеиия U на вход формирующего устройства // поступает напряжение

fJ о ли,, (U о iioM-SinoO/ COnst, а на второй вход блока 20 - напряжение (/о; jWi i7o 1ЮМ sino), где М; значение кода регистра делителя 4 омом - номинальное значение опорного на пряжения, являющееся эталонным для делите.ля 4 и иоддерживающееся /оном const, пропорциональное только записанному коду М,в регистре делителя 4 в иредыдуицем измерительном цикле, а на устройство П, экстремумдетектор 14 и на второй вход схемы /5 поступает напряжение иу. X -sin (), 1-де ф - фазовый сдвиг между опорным и измеряемым напряжениями. На вход умнол ителя частоты 15 поступает сигнал с частотой измеряемого напряжения /д;, а с его выхода к электронным ключам 21 и 22 поступают импульсы с частотой следования /n m-f.v, где const. В момент перехода положительного полупериода опорного напряжения f/o через ноль устройство П вырабатывает импульс, который опрокидывает триггер П, тем самым открывая электронный ключ 21 и пропуская к прямому входу счетчика S серию импульсов с выхода умножителя 15. Импульс с формирующего устройства 11 поступает и на первый вход измерителя 2, фиксируя начало временного интервала, пропорционального фазовому сдвигу ср. В момент перехода положительного полупериода измеряемого напряжения U л- через ноль формирующее устройство 12 вырабатывает импульс, поступающий на триггер 18 и на второй вход измерителя 2, фиксируя таким образом временной интервал, пропорциональный фазовому сдвигу ф. Импульс с формирующего устройства 12 опрокидывает триггер 18, последний открывает электронный ключ 22 и иропускает через элемент задержки / к инверсному входу счетчика 8 серию импульсов с выхода умножителя 15, задержанных элеf3i |l-, где ментом задержки 7 на время ,1 Г„ -тпериод следования импульсов в Серии. Этим обеспечивается параллельная подача двух- серий импульсов, но сдвинутых во времени один относительно другого на Г/2, на оба входа счетчика 8. В момент достижения заданного уровня Ux,a,i опорным наоряжением t/o и изме1ряемым напряжением (,mi и t/хм С/хч„„, где t/9M и UJCA -мгновенные значения опорного п измеряемого напряжений), схемы совпадения 20 и 16 вырабатывают импульс, сбрасывающий соответственно триггер 17 и 18, таким образом заканчивается формирование серий импульсов NI и N2, пропорциональные времени достижения уровня Uх,ш обоими напряжениям н соответственно. В момент максимума положительного полуиериода измеряемого напряжения экстремумлетектор 14 вырабатывает импульс, который через элемент, 19, обеспечивающий некоторую минимальную его задержку 32 (для четкостг работы счетчика 8 в случае минимального значения опорного или измеряемого иапряжеипй), переключает коммутатор 24, подающий на первый вход сумматора 26 код разности /Vi-.Vo и складывающий его с кодом регистра делителя 4, который находится на втором входе сумматора. Полученный результат записывается и сохраняется в регистре сумматора до следующего измерительного цикла. Выходной сигнал элемента задержки 19 через элемент 23, имеющий время задержки , -1м , где 1 - длительность выходного импульса элемента задержки 19, сбрасывает на ноль счетчик 8, подготавливая его для следующего измерительного цикла, и переключает коммутатор 25, записывающий в регистр делителя 4 напряжения. Элемент «НЕ 26 за время переключения коммутатора 24 (время складывания обонх кодов в сумматоре) выключает блок 10. Число разрядов делителя 4, су.мматора 26, счетчика 8 выбраиы таким образом, что обеспечивается изменение амплитуды опорного напряженпя t/o в пределах изменения пзмеряемого напряжени f/.v от нуля до максимального значения с необходимой точностью. Предмет и з о б р е т е и i я Цифровой компенсатор, содержащий цифровой делитель напряжения, подключенный к выходу источника опорного напряженпя, формирующие устройства, через которые выходы источников опорного и измеряемого наиряжеиий подключены к измерителю фазового сдвига с блоком цифровой индикации на выходе, блок цифровой индикации модуля измеряемого напряжения, отличающийся тем, что, с целью расщирения частотного диапазоиа и повыщения быстродействия, в него введены времяимпульсные преобразователи, первый из которых непосредственно, а второй через элемент задержки подключены ко входам реверсивного счетчика, и арифметическое устройство, входы которого подключены к выходу реверсивного счетчика, выходу цифрового делителя напряжения и через экстремум-детектор к источнику измеряемого напряжен я, а выходы соединены с входом блока цифровой пндикации модуля измеряемого иапряжеиия, цифрового делителя напряжеипя п входом «сброс пуля реверсивного счетчика; входиервого времяимпульсного преобразователя подключен к выходу цифрового делителя напряжения, а вход второго - к выходу источника измеряемого напряженпя, однп управляющие входы времяимпульсных преобразователей одключены к выходам формирующих устойств, а другие управляющпе входы через множитель частоты - к источнику преобразу мого напряжетиш.

UoUa fOMSinuiCOfKl

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Цифровой фазометр | 1982 |

|

SU1075187A1 |

| Преобразователь фазового сдвига в цифровой код | 1982 |

|

SU1056073A1 |

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Цифровой измеритель температуры | 1982 |

|

SU1075086A1 |

| Следящий фазометр (его варианты) | 1981 |

|

SU1029095A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Преобразователь угла поворота вала в код | 1986 |

|

SU1410277A1 |

Авторы

Даты

1974-08-15—Публикация

1972-08-01—Подача