СЛ

со оо

4 4.

Изобретение относится к радиоизмерительной технике и может быть использовано для построения двухка- нальных компараторов фазы.

Цель изобретения - повышение быстродействия измерений.

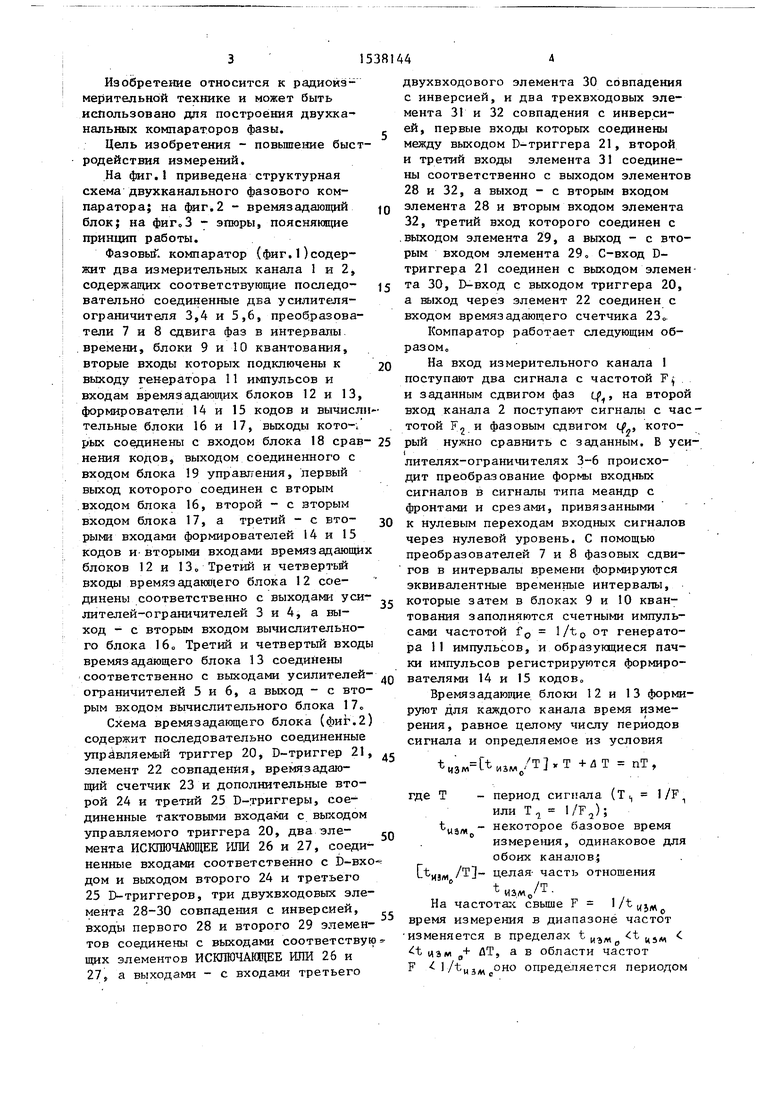

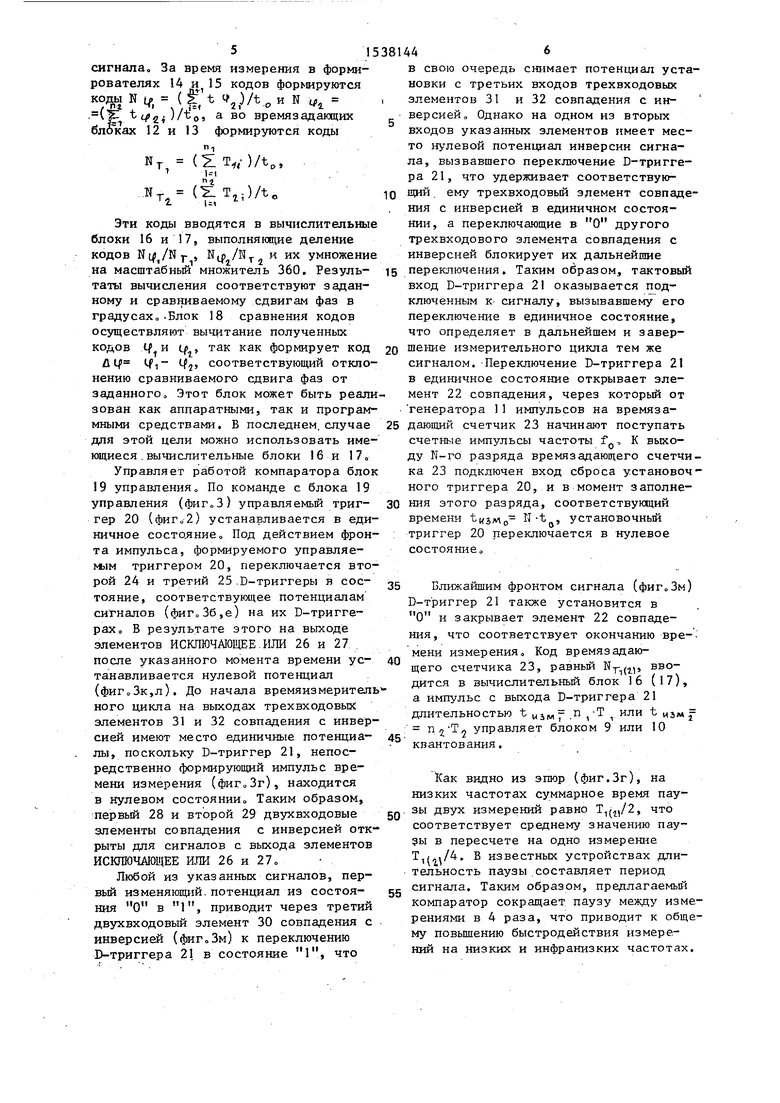

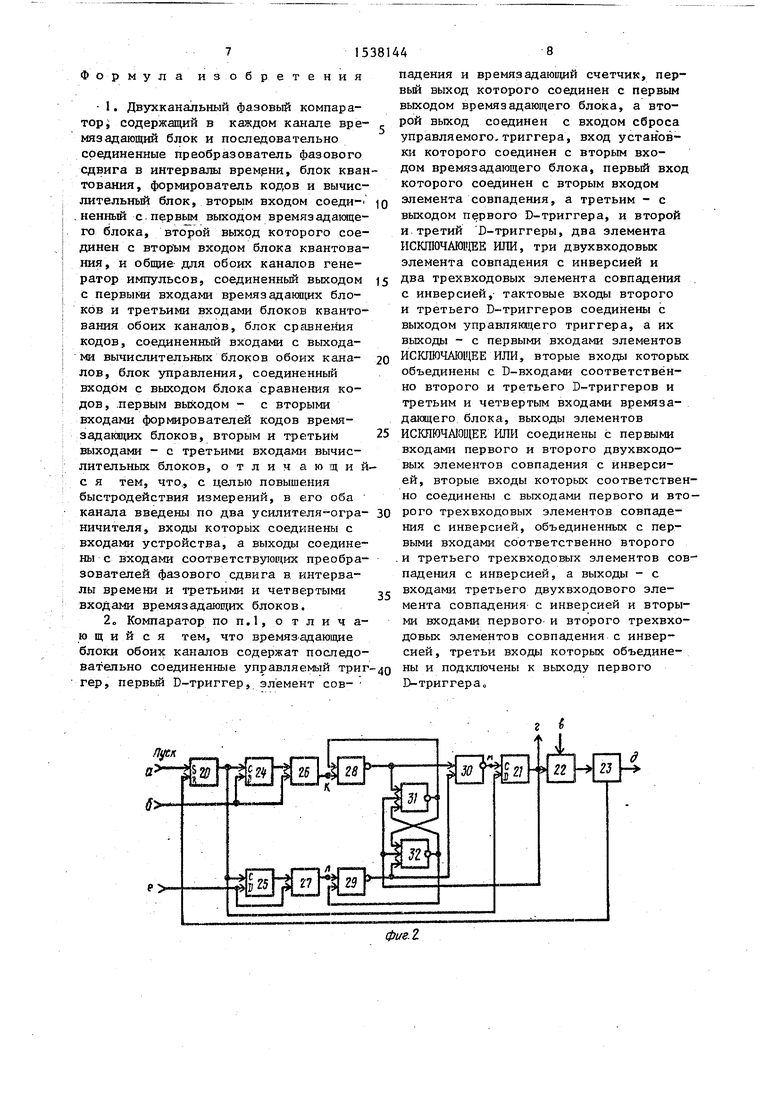

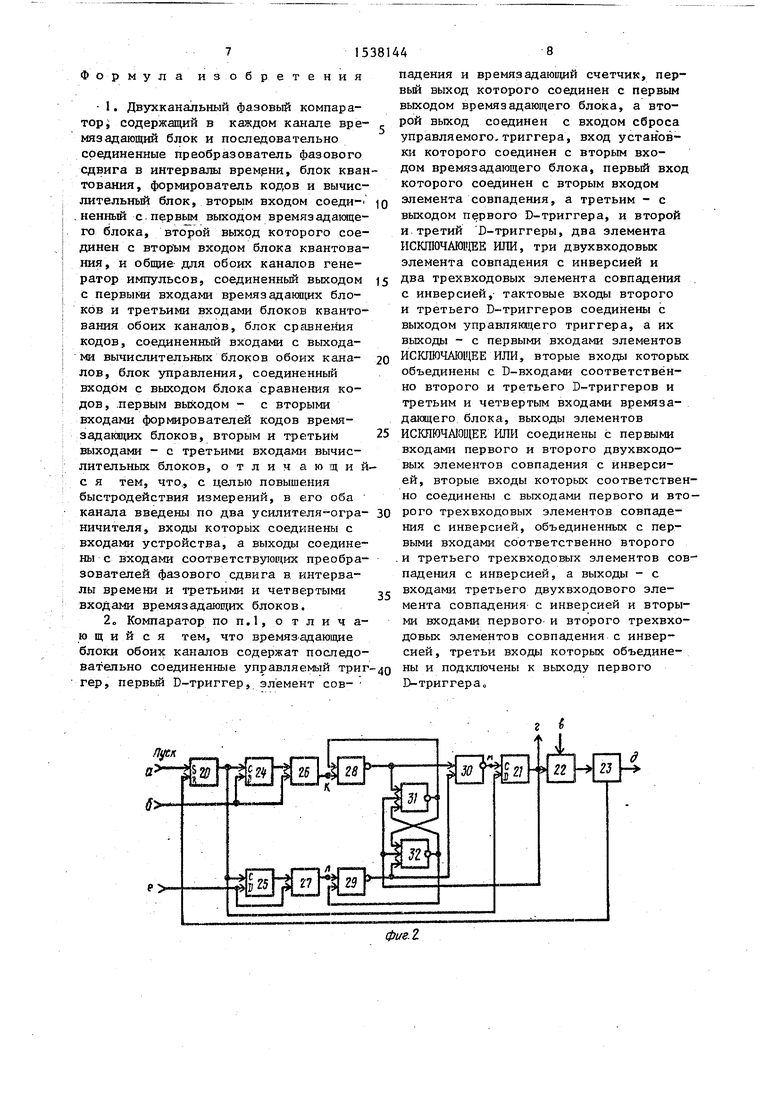

На фиг.1 приведена структурная схема двухканального фазового компаратора; на фиг.2 - времязадающий блок; на фиг„3 - эпюры, поясняющие принцип работы.

Фазовык компаратор (фиг.1)содержит два измерительных канала 1 и 2, содержащих соответствующие последо- вательно соединенные два усилителя- ограничителя 3,4 и 5,6, преобразователи 7 и 8 сдвига фаз в интервалы времени, блоки 9 и 10 квантования, вторые входы которых подключены к

выходу генератора 11 импульсов и входам времязадаклцих блоков 12 и 13, формирователи 14 и 15 кодов и вычислительные блоки 16 и 17, выходы кото-/ рых соединены с входом блока 18 срав- нения кодов, выходом соединенного с входом блока 19 управления, первый выход которого соединен с вторым входом блока 16, второй - с вторым входом блока 17, а третий - с вто- рыми входами формирователей 14 и 15 кодов и вторыми входами времязадающих блоков 12 и 13„ Третий и четвертый входы времяэадающего блока 12 соединены соответственно с выходами уси- лителей-ограничителей 3 и 4, а выход - с вторым входом вычислительного блока 16о Третий и четвертый входы времязадающего блока 13 соединены соответственно с выходами усилителей- ограничителей 5 и 6, а выход - с вторым входом вычислительного блока 17

Схема времязадающего блока (фиг.2) содержит последовательно соединенные управляемый триггер 20, D-триггер 21, элемент 22 совпадения, времязадающий счетчик 23 и дополнительные второй 24 и третий 25 D-триггеры, соединенные тактовыми входами с выходом управляемого триггера 20, два эле- мента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27, соединенные входами соответственно с D-вхо дом и выходом второго 24 и третьего 25 D-триггеров, три двухвходовых элемента 28-30 совпадения с инверсией, входы первого 28 и второго 29 элементов соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27, а выходами - с входами третьего

двухвходового элемента 30 совпадения с инверсией, и два трехвходовых элемента 31 и 32 совпадения с инверсией, первые входы которых соединены между выходом D-триггера 21, второй и третий входы элемента 31 соединены соответственно с выходом элементов 28 и 32, а выход - с вторым входом элемента 28 и вторым входом элемента 32, третий вход которого соединен с выходом элемента 29, а выход - с вторым входом элемента 29 , С-вход D- триггера 21 соединен с выходом элемен та 30, D-вход с выходом триггера 20, а выход через элемент 22 соединен с входом времязадающего счетчика 23

Компаратор работает следующим образом,

На вход измерительного канала 1 поступают два сигнала с частотой F и заданным сдвигом фаз if , на второй вход канала 2 поступают сигналы с чатотой F и фазовым сдвигом if , который нужно сравнить с заданным. В уси 1

лителях-ограничителях 3-6 происходит преобразование формы входных сигналов в сигналы типа меандр с фронтами и срезами, привязанными к нулевым переходам входных сигналов через нулевой уровень. С помощью преобразователей 7 и 8 фазовых сдвигов в интервалы времени формируются эквивалентные временные интервалы, которые затем в блоках 9 и 10 квантования заполняются счетными импульсами частотой f0 l/t0 от генератора 11 импульсов, и образующиеся пачки импульсов регистрируются формирователями 14 и 15 кодов

Времязадающие блоки 12 и 13 формируют для каждого канала время измерения , равное целому числу периодов сигнала и определяемое из условия

t ft

ь изм L изм

/Т х Т + и Т пТ ,

период сигнала (Т,, 1/F1

или Т

I/F,);

некоторое базовое время

измерения, одинаковое для обоих каналов; целая часть отношения

изм

/Т

На частота:-: свыше F I /t MjM время измерения в диапазоне частот изменяется в пределах t иэд, t M5W t из „+ ДТ, а в области частот Р оно определяется периодом

сигнала. За время измерения в формирователях 14 ит 15 кодов формируются кодыИ, (Ј t 02))Л0и N „t ,(1 t )/t0, а во время задающих блоках 12 и 13 формируются коды

N.

в свою очередь снимает потенциал установки с третьих входов трехвходовых i элементов 31 и 32 совпадения с инверсией. Однако на одном из вторых входов указанных элементов имеет место нулевой потенциал инверсии сигнала, вызвавшего переключение D-тригге- ра 21, что удерживает соответствую- 10 щий ему трехвходовый элемент совпадения с инверсией в единичном состоянии, а переключающие в О другого трехвходового элемента совпадения с инверсией блокирует их дальнейшие 15 переключения. Таким образом, тактовый вход D-триггера 21 оказывается подключенным к сигналу, вызывавшему его переключение в единичное состояние, что определяет в дальнейшем и эавер- 2о шение измерительного цикла тем же сигналом. Переключение D-триггера 21 в единичное состояние открывает элемент 22 совпадения, через который от генератора 11 импульсов на времяза- мными средствами. В последнем.случае 25 дающий счетчик 23 начинают поступать для этой цели можно использовать име- счетные импульсы частоты fQ, К выхо- ющиеся вычислительные блоки 16 и 17„ ду N-ro разряда времязадающего счетчиУправляет работой компаратора блок 19 управления. По команде с блока 19

.7 (ёт„.)/ч, 1

тг Т15)А.

Эти коды вводятся в вычислительные блоки 16 и 17, выполняющие деление кодов , /NT2 и их умножение на масштабный множитель 360. Результаты вычисления соответствуют заданному и сравниваемому сдвигам фаз в градусах -Блок 18 сравнения кодов осуществляют вычитание полученных кодов if и с; , так как формирует код

U ц If,- , соответствующий отклонению сравниваемого сдвига фаз от заданного, Этот блок может быть реализован как аппаратными, так и програмка 23 подключен вход сброса установочного триггера 20, и в момент заполне- управления (фиг„3) управляемый триг- 30 ния этого разряда, соответствующий гер 20 (фиг„2) устанавливается в еди- времени tM3M0- N-t, установочный

40

45

ничное состояние0 Под действием фронта импульса, формируемого управляемом триггером 20, переключается второй 24 и третий 25 D-триггеры в состояние, соответствующее потенциалам сигналов (фиг„3б,е) на их D-тригге- рах В результате этого на выходе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27 после указанного момента времени устанавливается нулевой потенциал (фиг„3к,л). До начала времяизмерителъ - ного цикла на выходах трехвходовых элементов 31 и 32 совпадения с инверсией имеют место единичные потенциалы, поскольку D-триггер 21, непосредственно формирующий импульс времени измерения (фиг„3г), находится в нулевом состоянии Таким образом, первый 28 и второй 29 двухвходовые 50 элементы совпадения с инверсией открыты для сигналов с выхода элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и 27

Любой из указанных сигналов, первый изменяющий, потенциал из состоя- 55 ния О в 1, приводит через третий двухвходовый элемент 30 совпадения с инверсией (фиг«Зм) к переключению D-триггера 21 в состояние 1, что

триггер 20 переключается в нулевое состояние

35 Ближайшим фронтом сигнала (фиг„3м) D-триггер 21 также установится в О и закрывает элемент 22 совпадения , что соответствует окончанию вре- . мени измерения. Код времязадающего счетчика 23, равный )} вводится в вычислительный блок 16 (17), а импульс с выхода D-триггера 21 длительностью t M JM n , -Т t или t иэм f п2 Т« управляет блоком 9 или 10 квантования.

Как видно из эпюр (фиг.Зг), на низких частотах суммарное время паузы двух измерений равно , что соответствует среднему значению паузы в пересчете на одно измерение Т, /4. В известных устройствах длительность паузы составляет период сигнала. Таким образом, предлагаемый компаратор сокращает паузу между измерениями в 4 раза, что приводит к общему повышению быстродействия измерений на низких и инфранизких частотах.

ка 23 подключен вход сброса установочного триггера 20, и в момент заполне- ния этого разряда, соответствующий времени tM3M0- N-t, установочный

триггер 20 переключается в нулевое состояние

Ближайшим фронтом сигнала (фиг„3м) D-триггер 21 также установится в О и закрывает элемент 22 совпадения , что соответствует окончанию вре- . мени измерения. Код времязадающего счетчика 23, равный )} вводится в вычислительный блок 16 (17), а импульс с выхода D-триггера 21 длительностью t M JM n , -Т t или t иэм f п2 Т« управляет блоком 9 или 10 квантования.

Как видно из эпюр (фиг.Зг), на низких частотах суммарное время паузы двух измерений равно , что соответствует среднему значению паузы в пересчете на одно измерение Т, /4. В известных устройствах длительность паузы составляет период сигнала. Таким образом, предлагаемый компаратор сокращает паузу между измерениями в 4 раза, что приводит к общему повышению быстродействия измерений на низких и инфранизких частотах.

Формула изобретения

1. Двухканальный фазовый компаратор, содержащий в каждом канале времяз адающий блок и последовательно соединенные преобразователь фазового сдвига в интервалы времени, блок квантования, формирователь кодов и вычислительный блок, вторым входом соеди- ненный с первым выходом времязадающе- го блока, второй выход которого соединен с вторым входом блока квантования, и общие для обоих каналов генератор импульсов, соединенный выходом с первыми входами времязадающих блоков и третьими входами блоков квантования обоих каналов, блок сравнения кодов, соединенный входами с выходами вычислительных блоков обоих каналов, блок управления, соединенный входом с выходом блока сравнения кодов, первым выходом - с вторыми входами формирователей кодов времязадающих блоков, вторым и третьим выходами - с третьими входами вычислительных блоков, отличающий- с я тем, что, с целью повышения быстродействия измерений, в его оба канала введены по два усилителя-огра- ничителя, входы которых соединены с входами устройства, а выходы соединены с входами соответствующих преобразователей фазового сдвига в интервалы времени и третьими и четвертыми входами времязадающих блоков.

2о Компаратор по п.1, о т л и ч а- ю щ и и с я тем, что времязадающие блоки обоих каналов содержат последовательно соединенные управляемый триггер, первый D-триггер, элемент сов

0

5

0

о

0

5

5

падения и времязадающий счетчик, первый выход которого соединен с первым выходом времязадающего блока, а второй выход соединен с входом сброса управляемого,триггера, вход установки которого соединен с вторым входом времязадающего блока, первый вход которого соединен с вторым входом элемента совпадения, а третьим - с выходом первого D-триггера, и второй и третий D-триггеры, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три двухвходовых элемента совпадения с инверсией и два трехвходовых элемента совпадения с инверсией, тактовые входы второго и третьего D-триггеров соединены с выходом управляющего триггера, а их выходы - с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых объединены с D-входами соответственно второго и третьего D-триггеров и третьим и четвертым входами времязадающего блока, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первыми входами первого и второго двухвходовых элементов совпадения с инверсией, вторые входы которых соответственно соединены с выходами первого и второго трехвходовых элементов совпадения с инверсией, объединенных с первыми входами соответственно второго и третьего трехвходовых элементов совпадения с инверсией, а выходы - с входами третьего двухвходового элемента совпадения с инверсией и вторыми входами первого и второго трехвходовых элементов совпадения с инверсией, третьи входы которых объединены и подключены к выходу первого D-триггера„

d l

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальный фазовый компаратор | 1981 |

|

SU991327A2 |

| Двухканальный фазовый компаратор | 1980 |

|

SU900214A1 |

| СПОСОБ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С МАГНИТНОГО НОСИТЕЛЯ ИНФОРМАЦИИ, ЗАПИСАННЫХ RLL КОДАМИ, И ДЕТЕКТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2015 |

|

RU2623660C2 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

| Цифровой фазометр | 1985 |

|

SU1298688A2 |

| САМОНАСТРАИВАЮЩЕЕСЯ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2017 |

|

RU2665906C1 |

| Цифровой фазометр | 1981 |

|

SU970258A1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 2005 |

|

RU2297096C1 |

| Способ дискретного задания фазового сдвига и устройство для его осуществления | 1986 |

|

SU1337818A1 |

Изобретение может быть использовано в радиоизмерительной технике. Цель - повышение быстродействия измерений. Цель достигается введением в каждый канал 1, 2 двух усилителей-ограничителей 3, 4 и 5, 6, входы которых соединены с входами устройства, а выходы - с входами соответствующих преобразователей 7, 8 фазового сдвига в интервал времени и входами времязадающих блоков 12 и 13. Устройство содержит также блоки 9 и 10 квантования, генератор 11 импульсов, формирователи 14 и 15 кодов, вычислительные блоки 16 и 17, блок 18 сравнения кодов и блок 19 управления. Поставленная цель достигается тем, что времязадающие блоки 12 и 13 дополнительно содержат последовательно соединенные Д-триггеры, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И и трехвходовые элементы И. Блоки 12 и 13 содержат также управляемый триггер, Д-триггер, элемент И и времязадающий счетчик. Повышение быстродействия достигается за счет сокращения паузы между измерениями. 1 з.п.ф-лы, 3 ил.

П

са ей

n

ч

P J

a ±

ab

I

з

n

ч

J J

CO

| Двухканальный фазовый компаратор | 1980 |

|

SU892345A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-01-23—Публикация

1988-05-17—Подача