К

(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на биполярных и МОП-транзисторах | 1988 |

|

SU1615877A1 |

| ИСТОЧНИК ЭЛЕКТРИЧЕСКОГО СИГНАЛА, ПРОПОРЦИОНАЛЬНОГО АБСОЛЮТНОЙ ТЕМПЕРАТУРЕ | 1993 |

|

RU2115099C1 |

| Повторитель напряжения | 1981 |

|

SU1043813A1 |

| Преобразователь переменного напряжения в постоянное | 1987 |

|

SU1504763A1 |

| Ключ | 1983 |

|

SU1119170A2 |

| Широкополосный усилитель | 1981 |

|

SU1030949A1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

| Многоканальный мультивибратор | 1979 |

|

SU809499A1 |

| УСТРОЙСТВО ЭЛЕКТРОННОГО ГИСТЕРЕЗИСА | 2012 |

|

RU2486670C1 |

| МОП ДИОДНАЯ ЯЧЕЙКА МОНОЛИТНОГО ДЕТЕКТОРА ИЗЛУЧЕНИЙ | 2011 |

|

RU2494497C2 |

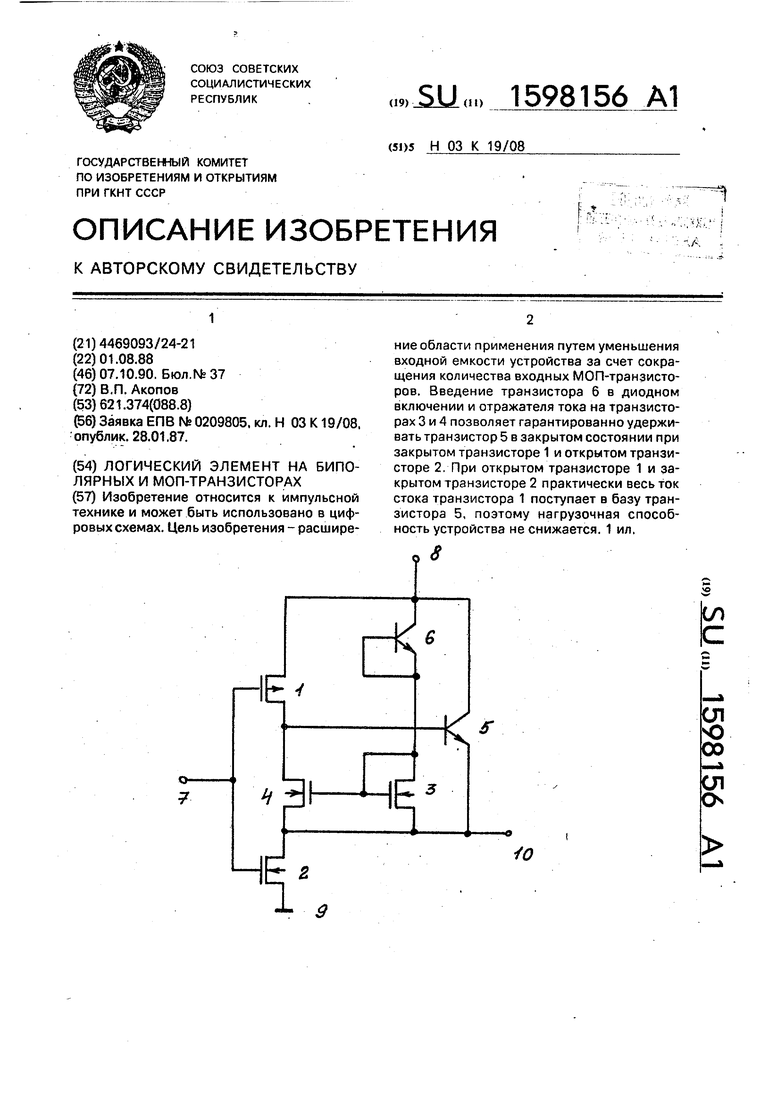

Изобретение относится к импульсной технике и может быть использовано в цифровых схемах. Цель изобретения - расширение области применения путем уменьшения входной емкости устройства за счет сокращения количества входных МОП-транзисторов. Введение транзистора 6 в диодном включении и отражателя тока на транзисторах 3 и 4 позволяет гарантированно удерживать транзистор 5 в закрытом состоянии при закрытом транзисторе 1 и открытом транзисторе 2. При открытом транзисторе 1 и закрытом транзисторе 2 практически весь ток стока транзистора 1 поступает в базу транзистора 5, поэтому нагрузочная способность устройства не снижается. 1 ил.

Ё

3

ЧЕ

к

ел ю

00

ел о

/

Изобретение отнесется к импульсной технике и может быть использовано в цифровых схемах.

Цель изобретения -- расширение об- ласти применения путем уменьшения входной емкости устройства за счет сокращения количества входных МОП-транзисторов.

На чертеже представлена злектри- ческая схема устройства.

Логический элемент содержит первый 1-р-канальный МОП-транзистор, второй 2, третий 3, четвертый 4 п-канальные МОП-тран- зисторы. первый 5, второй (диодно-включен- ныи) б биполярные п-р-п-транзисторы входную шину 7. шину 8 питания, общую шину 9, выходную шину 10,

Входная шина 7 соединена с затворами транзисторов 1 и 2 . Исток транзистора 1 коллекторы транзисторов 5 и 6 соединены с ШИНОЙ 8 питания. Сток транзистора 1 соединен с базой транзистора 5 и выходом отражателя тока на транзисторах 3 и 4 Эмиттер транзистора 5, общий вывод отражателя тока (истоки транзисторов 3 и 4), сток транзистора 2 подключены к выходной шине 10. Исток транзистора 2 соединен с общей ШИНОЙ 9. а объединенные база-эмиттер транзистора 6 - с входом отражателя тока.

Логический элемент работает следующим образом.

В исходном состоянии при подаче на входную шину 7 высокого потенциала логической Г транзистор закрыт, транзистор 2 открыт, на выходной шине 10 сформируется низкий потенциал логического О, близ- 4 КИЙ к потенциалу общей шины. При этрм разность потенциалов на участке база - коллектор транзистора 5 достигает максимальной величины, которая приблизительно равна величине напряжения источника пи- 4 тания. Примерно этой же величине равна и разность потенциалов на участке коллектор база транзистора 6. Если транзисторы 5 и 6 конструктивно одинаковы (что легко осуществимо при интегральном исполнении). 5 то и токи утечки этих транзисторов приблизительно равны. Ток утечки на участке коллектор - база транзистора 6 через отражатель тока на транзисторах 3 и 4 сформирует ток стока транзистора 4. Если при 5 этом крутизна характеристики транзистора 4 больше крутизны характеристики транзистора 3, JO ТОК стока транзистора 4 будет равен току утечки на участке коллеюор-база транзистора 5. а величина падения напря

жения на участке сток - исток транзистора 4 будет меньше величины падения напряжения на участке сток - исток транзистора 3 ,, пороговое напряжение отпирания кмоп-транзисторов в данном случае находится примерно на том же уровне, что и величина падения напряжения на прямо- смещенном переходе база - эмиттер транзистора 5. то величина падения напряжения на участке сток - исток транзистора 4 будет меньше величины напряжения отпирания перехода база - эмиттер транзистора 5 т е транзистор 5 будет закрыт. Таким образом наличие транзистора 6 с отражателем тока на транзисторах 3 и 4 позволяет гарантированно удерживать транзистор 5 в закрытом состоянии при закрытом 1 и открытом 2 транзисторах.

При подаче на входную шину 7 низкого потенциала логического О транзистор 2 запирается, транзистор 1 отпирается, открывается переход база эмиттер транзистора 5, который начинает работать в режиме усиления тока, уменьшая выходное сопротивление открытого транзистора 1 в раз (Й- козффициент усиления потоку транзистора 5. Поскольку при этом разность потенциалов на участке коллектор - база транзисторов 5 и б минимальна, то и токи утечки этих транзисторов либо равны нулю, либо минимальны. Тогда практически весь ток стока транзистора 1 поступает в базу транзистора 5. поэтому нагрузочная способность устройства будет достаточно высокой.

Формула изобретения

Логический элемент на биполярных и МОП-транзисторах, содержащий первый и второй МОП-транзисторы, затворы которых являются входом схемы, истоки подключены соответствено к шине питания и к общей шине, сток первого МОП-транзистора соединен с базой первого биполярного транзистора, коллектор которого подключен к шине питания, а эмиттер к выходу схемы, отличаю щийся тем. что. с целью расширения области применения путем уменьшения входной емкости, в него введены второй биполярный транзистор в диодном включении и отражатель тока, выполненный на третьем и четвертом МОП- фанзисторах. при этом коллектор второго биполярного транзистора подключен к шине питания, а база и эмиттер подключены к входу отражателя тока, выход которого соединен со стоком первого МОП-транзистора, а общий вывод - с выходом схемы и стоком второго МОП-транзистора, причем первый МОП-транзистор - одного типа про515981566

водимости, второй, третий, четвертый МОП- первый и второй биполярные транзисторы транзисторы - другого типа проводимости, одного типа проводимости. .

Авторы

Даты

1990-10-07—Публикация

1988-08-01—Подача