i

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент на биполярных и МОП-транзисторах | 1988 |

|

SU1598156A1 |

| Моп-ттл транслятор | 1979 |

|

SU836797A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

| ВЫСОКОЧАСТОТНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ СТАБИЛИЗАЦИИ ТОКА КОЛЛЕКТОРА | 2012 |

|

RU2509407C1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ КОРРЕКЦИИ ЭЛЕКТРОТЕРМИЧЕСКОЙ СВЯЗИ В БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2011 |

|

RU2462813C1 |

| ВЫСОКОЧАСТОТНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ СТАБИЛИЗАЦИИ ТОКА КОЛЛЕКТОРА ГЕТЕРОСТРУКТУРНОГО БИПОЛЯРНОГО ТРАНЗИСТОРА | 2012 |

|

RU2497271C1 |

| Ключ | 1977 |

|

SU621094A2 |

| Ключ | 1975 |

|

SU531278A1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ ЭСЛ-КМОП | 1994 |

|

RU2097914C1 |

Изобретение относится к импульсной технике и может быть использовано в цифровых схемах. Цель изобретения - повышение надежности устройства путем устранения сквозного тока в выходном каскаде. Это достигается за счет введения пятого N-канального МОП-транзистора. 1 ил.

8

П

1

П

2

(

11

in

00

Изобретение относится к импульсной технике и может быть использовано в цифровых схемах, .

Цель изобретения - повышение на- дежности путем устранения сквозного тока в выходном каскаде.

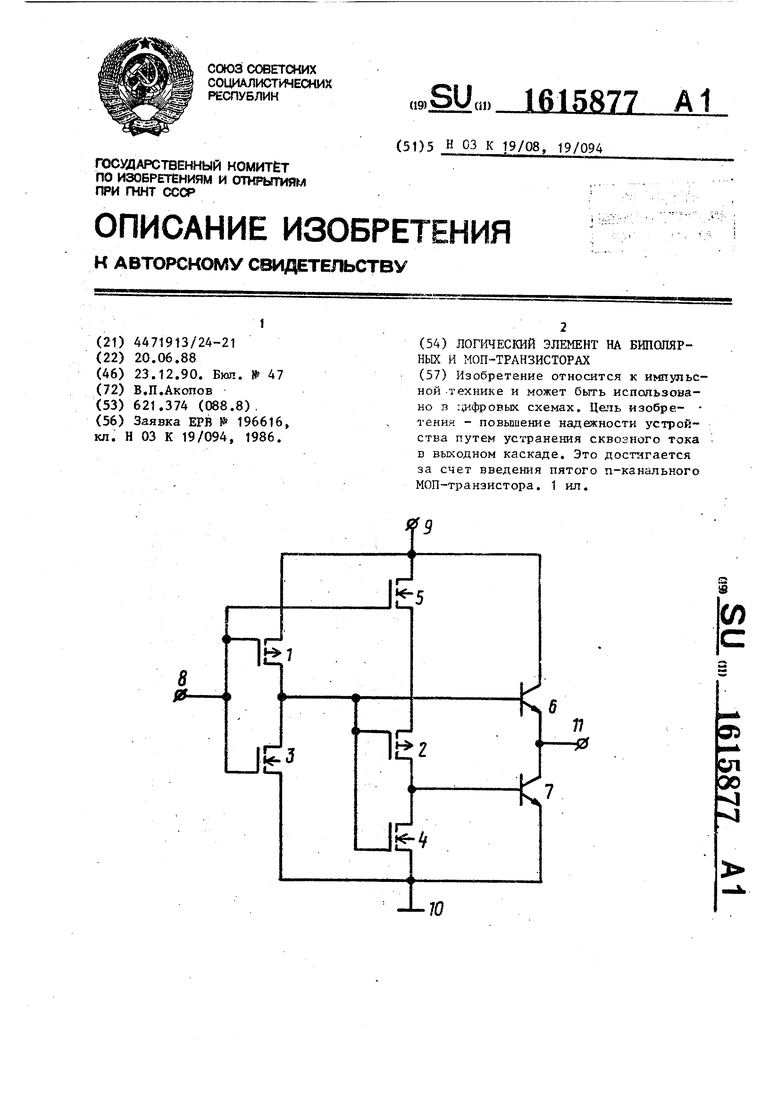

На чертеже представлена электрическая схема логического элемента

Логический элемент содержит пер- вьй 1, второй 2 р-канапьные МОП-транзисторы, первьй 3, второй А и третий

5п-канальные МОП-транзисторы, Первьй 6 и второй 7 биполярные п-р-п транзисторы, входную щину 8, шину 9 питания, общую шину 10, выходную шину 1 1 .

Входная шина 8 соединена с затворами транзисторов 1, 3 и 5, Исток транзистора 1, сток транзистора 5 и коллектор транзистора 6 соединены с шиной 9 питания. Сток-транзистора 1 соединен со стоком транзистора 3, затворами транзисторов 2 и 4 и базой транзистора 6, эмиттер которого со- единен с выходной шиной 11 и коллектором транзистора 7о База транзистора 7 соединена со стоками транзисторов 4 и 2, исток которого соединен с истоком транзистора 5. Истоки транзисторов 3 и 4 и эмиттер транзистора 7 соединены с общей шиной 10.

Логический элемент работает следующим образом.

При подаче на входную шину 8 низкого потенциала логического транзистор 3. закрыт, транзистор 1 открыт. При этом на стоке транзистора 1 сформирован потенциал, близкий По величине напряжению источника питания . который удерживает транзистор 2 в закрытом состоянии, а транзистор 4 - в открытом. Открытое состояние транзистора 4 формирует на базе транзистора 7 потенциал, близкий потенциалу общей шины 10, вследствие чего транзистор 7 закрыт. Благодаря высокому потенциалу на стоке транзистора 1J, на эмиттере транзистора

6(выходной шине 11) сформирован высокий потенциал логической 1,

При возрастании входного напряжения до величины, равной половине напряжения питания, транзисторы 5 и 2 находятся в закрытом состоянии,

так как возникающая при этом разност потенциалов между затворами транзисторов 5 и 2 меньше напряжения отпирания этих транзисторов. Например, при

Q

п 5

5 45

50

.

0

40

величине входного напряжения, равной половине напряжения питания, потенциал на стоке транзистора 1 соответственно также равен половине напряжения питания, т.е, и потенциал на затворах транзисторов 5 и 2 равен этой же величине, а поскольку истоки транзисторов 5 и 2 соединены между собой, то оба эти транзистора закры- ты,

, При дальнейшем возрастании входного напряжения потенциал на стоке транзистора 1 соответственно уменьшается и наступает момент, когда разность потейциалов между затворами транзисторов 5 и 2 становится больше напряжения отпирания этих транзисторов. При этом транзистор 4 еще открыт и поэтому транзистор 7 продолжает оставаться закрытым, вследствие чего сквозной ток через транзисторы выходного каскада не протекает,

К моменту, когда потенциал на стоке транзистора 1 становится близким к потенциалу общей шины 10, транзисторы 4 и 6 закрываются, а транзисторы 5 и 2 максимально открываются, что приводит к формированию такого базового тока транзистора 7-, при котором этот транзистор входит в насыщенное состояние, на выходной шине 11 присутствует низкий потенциал логического О и сквозной ток через транзисторы выходного каскада не протекает.

Формула изобретения

Логический элемент, на биполярных и МОП-транзисторах, содержаший входную шину, соединенную с затворами первого и второго МОП-транзисторов, шину питания, соединенную с истоком первого МОП-транзистора и коллектором первого биполярного транзистора, база которого подключена к стокам первого и второго МОП-транзисторов, эмиттер - к выходной шине и коллектору второго биполярного транзистора, эмиттер которого соединен с общей шиной, база подключена к стокам третьего и четвертого МОП-транзисторов, затворы которых подсоединены к стоку первого МОП-транзистора, а истоки второго и четвертого МОП-транзисТо- ров - к общей шине, отличающий .с я тем, что, с целью повьш1е- ния надежности, в него введен пятьй

51615877

МОП-транзистор, причем сток пятого торы - одного типа проводимости, вто- МОП-транзистора соединен с шиной пи-рой четвертый, пятый МОП-транзистотания, затвор - с входной шиной,ры - другого типа проводимости, перисток - с истоком третьего МОП-тран-вьй и второй биполярные транзистозистора, первьй, третий МОП-транзис-ры - одного типа проводимости.

| РЕЙДОВЫЙ ПЛАВУЧИЙ ПРИЧАЛ ДЛЯ ГРУЗОВЫХ ОПЕРАЦИЙ С НЕФТЕПРОДУКТАМИ | 0 |

|

SU196616A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-12-23—Публикация

1988-06-20—Подача