31

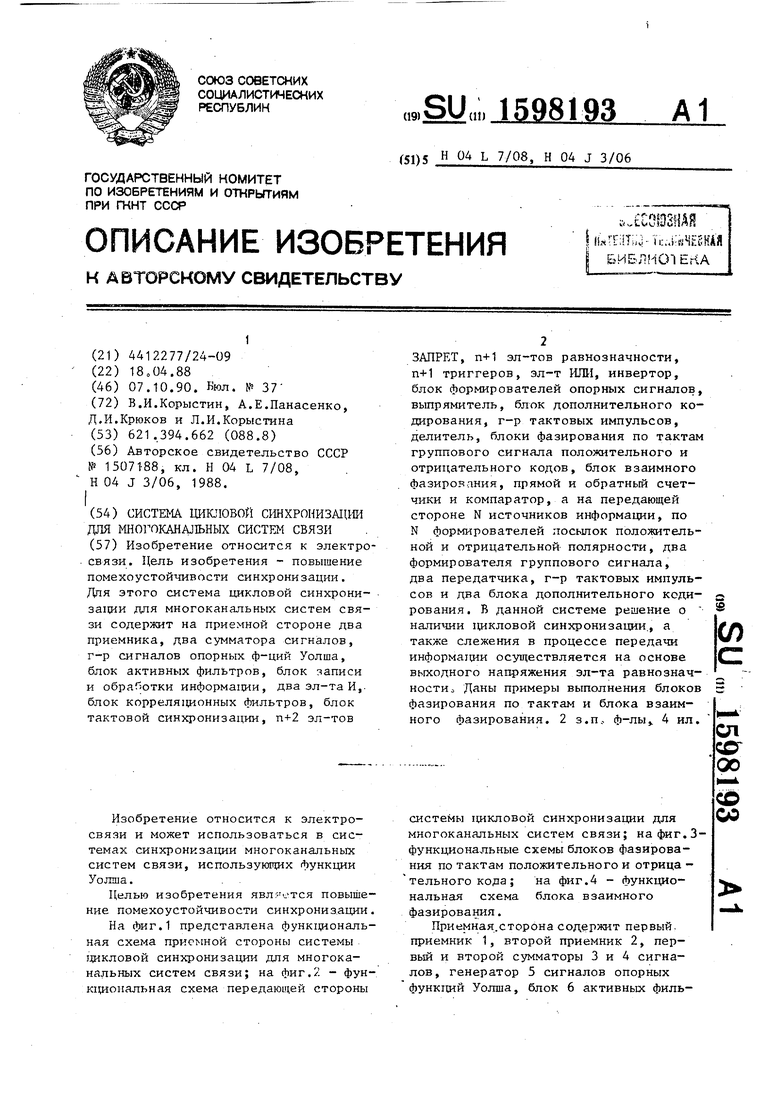

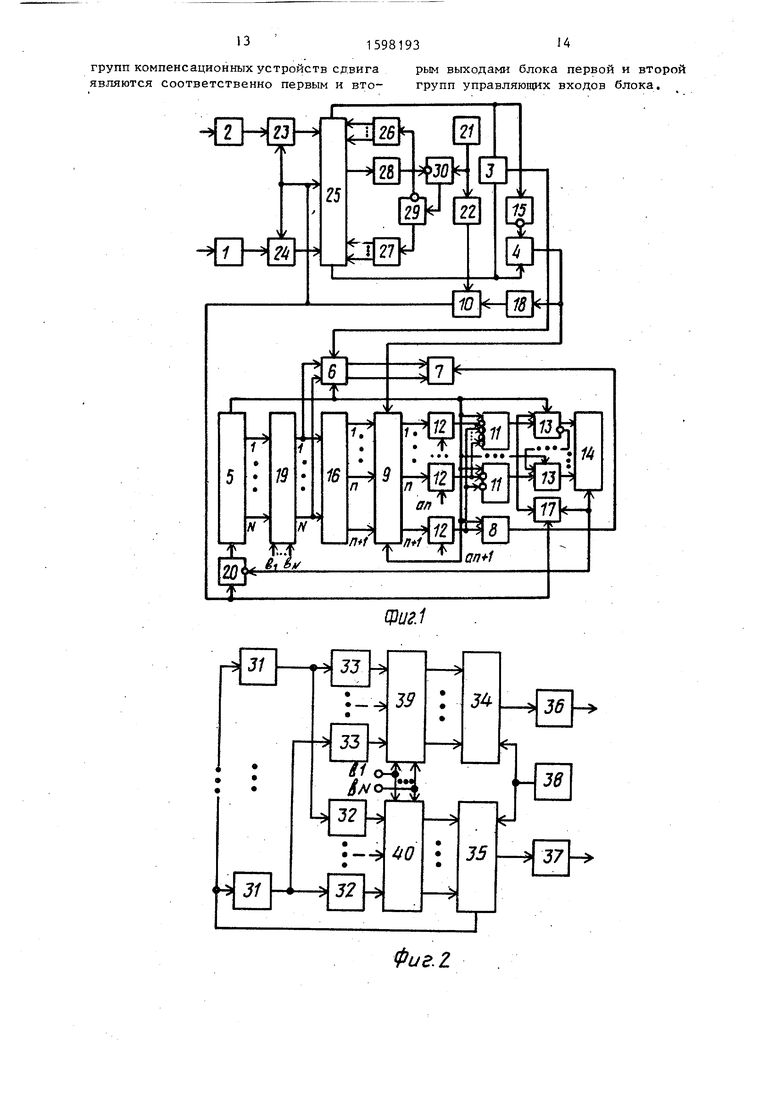

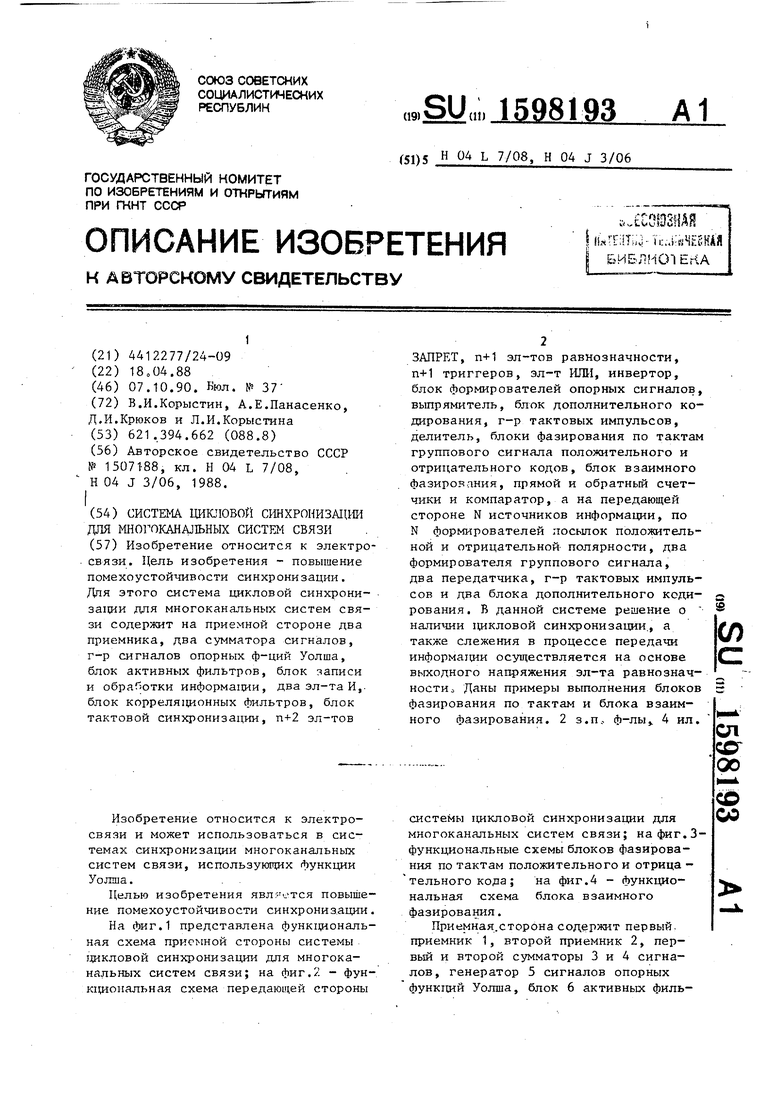

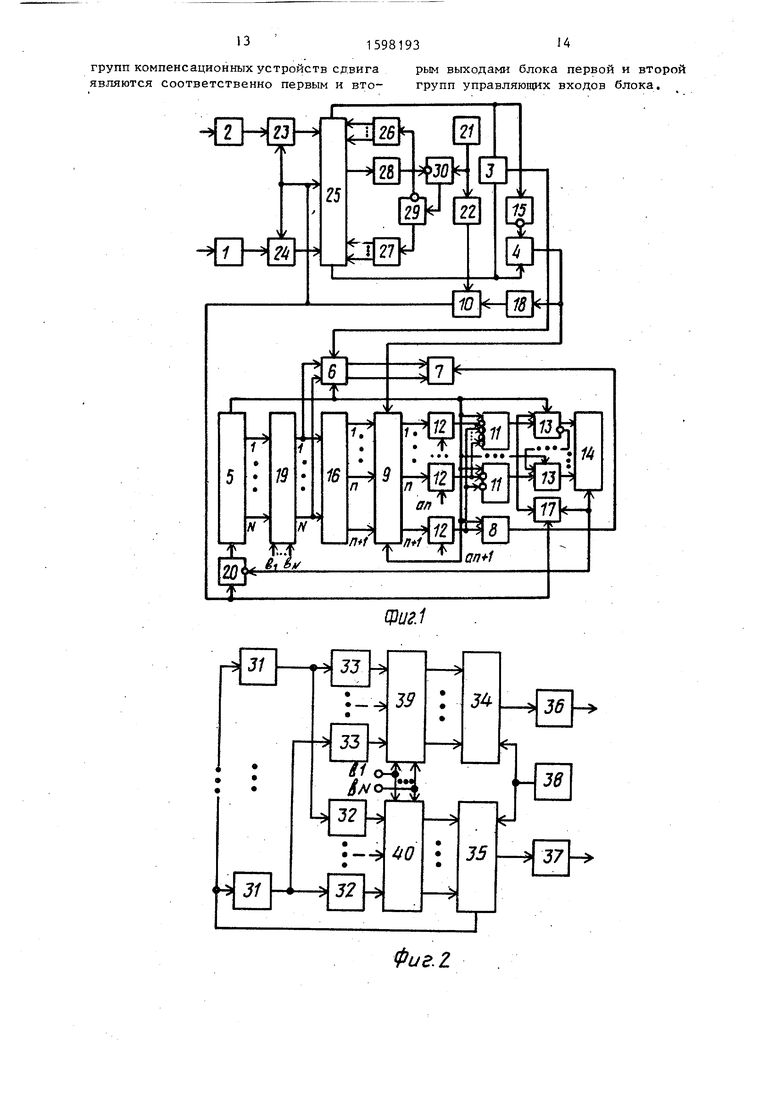

тров, блок 7 записи и обработки информации, первый элемент И 8, блок 9 корреляционных фильтров, блок 10 тактовой синхронизации, п элементов ЗАЛ PET 11, п+1 элементов 12 равнозначт ности, п триггеров 13, элемент ИЛИ 1 инвертор 15, блок 16 формирователей опорных сигналов, второй элемент И 17 выпрямитель 18, блок 19 дополнитель- ного кодирования, первьм дополнительный элемент ЗАПРЕТ 20, генератор 21 тактовых импульсов, делитель 22, бло 23 фазирования по тактам группового сигнала положительного кода, блок 24 фазирования по тактам группового сигнала отрицательного кода, блок 25 взаимного фазирования, прямой и обратный счетчики 26 и 27, компаратор 28, дополнительный триггер 29, второй дополнительньй элемент ЗАПРЕТ 30

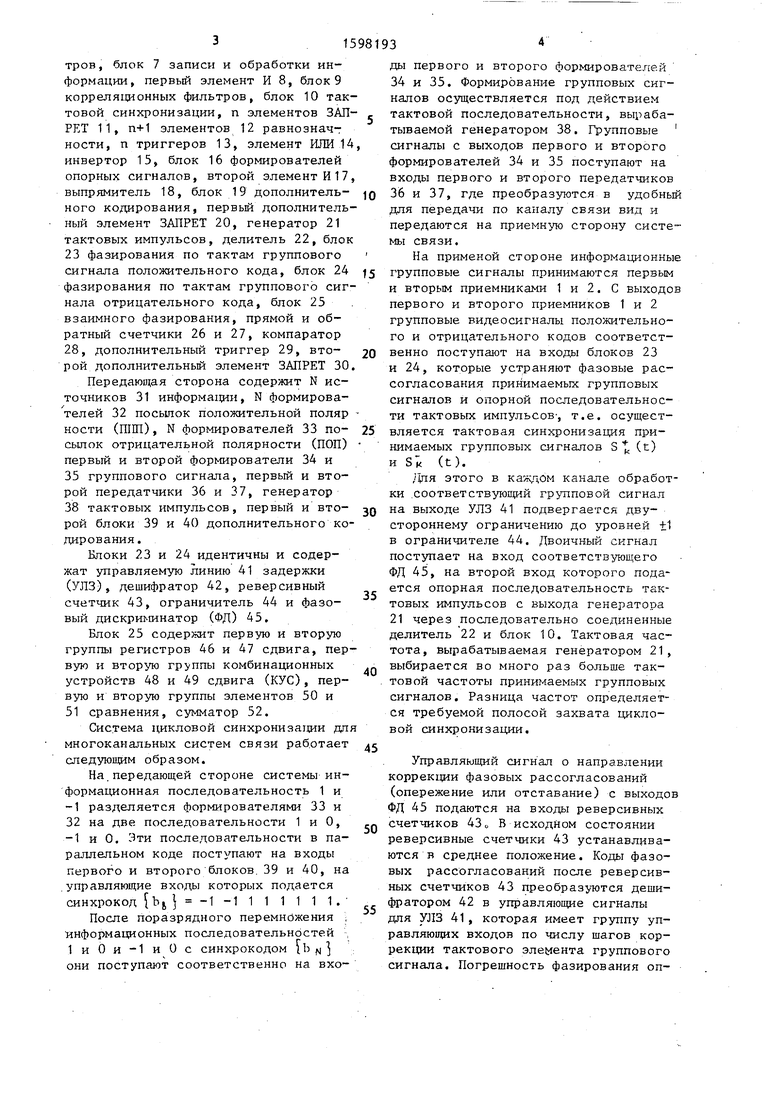

Передающая сторона содержит N источников 31 информахщи, N формирователей 32 посылок положительной поляр ности (ШШ), N формирователей 33 посылок отрицательной полярности (ПОП) первый и второй формирователи 34 и 35 группового сигнала, первьй и второй передатчики 36 и 37, генератор 38 тактовых импульсов, первый и второй блоки 39 и 40 дополнительного кодирования.

Блоки 23 и 24 идентичны и содержат управляемую линию 41 задержки (УЛЗ), дешифратор 42, реверсивный счетчик 43, ограничитель 44 и фазовый дискриминатор (ФД) 45.

Блок 25 содержит первую и вторую группы регистров 46 и 47 сдвига, первую и вторую группы комбинационных устройств 48 и 49 сдвига (КУС), первую и вторую группы элементов 50 и 51 сравнения, сумматор 52.

Система цикловой cинxpoнизar Jiи дл многоканальных систем связи работает следующим образом.

На.передающей стороне системы информационная последовательность 1 и -1 разделяется формирователями 33 и 32 на две последовательности 1 и О, -1 и О. Эти последовательности в параллельном коде поступают на входы Первого и второго блоков. 39 и 40, на управляющие входы которых подается синхрокод tl(,i 1 1 1 1 1 1 1 1«

После поразрядного перемножения информационных последовательностей 1 и О и -1 и О с синхрокодом Ь ft они поступают соответственно на вхо

5

0

5

, g

0

5

40

ды первого и второго формирователей 34 и 35. Формирование групповых сигналов осздцествляется под действием тактовой последовательности, вырабатываемой генератором 38. Групповые сигналы с выходов первого и второго формирователей 34 и 35 поступают на входы первого и второго передатчиков 36 и 37, где преобразуются в удобный для передачи по каналу связи вид и передаются на приемную сторону системы связи.

На применой стороне информационные групповые сигналы принимаются первым и вторым приемниками 1 и 2. С выходов первого и второго приемников 1 и 2 групповые видеосигналы положительного и отрицательного кодов соответственно поступают на входы блоков 23 и 24, которые устраняют фазовые рассогласования принимаемых групповых сигналов и опорной последовательности тактовых импульсов-, т.е. осуществляется тактовая синхронизация принимаемых групповых сигналов S. (t) и SK (t).

, щя этого в каждом канале обработки .соответствующий групповой сигнал на выходе УЛЗ 41 подвергается двустороннему ограничению до зфовней ±1 в ограничителе 44. Двоичный сигнал поступает на вход соответствующего ФД 45, на второй вход которого подается опорная последовательность тактовых импульсов с выхода генератора 21 через последовательно соединенные делитель 22 и блок 10. Тактовая частота. Вырабатываемая генератором 21, выбирается во много раз больше тактовой частоты принимаемых групповых сигналов. Разница частот определяется требуемой полосой захвата цикловой синхронизации.

0

5

Управляющий сигнал о направлении коррекции фазовых рассогласований (опережение или отставание) с выходов ФД 45 подаются на входы реверсивных счетчиков 43 о В исходном состоянии реверсивные счетчики 43 устанавливаются в среднее положение. Коды фазовых рассогласований после реверсивных счетчиков 43 преобразуются дешифратором 42 в управляющие сигналы для УЛЗ 41, которая имеет груцпу управляющих входов по числу шагов коррекции тактового элемента группового сигнала. Погрешность фазирования оп5релеляется количеством элементов в УЛЗ 41 и реверсивных счетчиков 43.

Групповые сигналы с выходов УЛЗ 41 поступают на входы блоков первой и второй групп регистров 46 и 47 бло ка 25. В системе имеется две ступени компенсагщи взаимного временного рас согласования групповых сигналов поло жительного и отрицательного кодов. УЛЗ 41 устраняет временное рассогласование в пределах такта, на первой и второй группе КУС 48 и 49 устраняется временное рассогласование в пределах нескольких длительностей группового сигнала. Интервал захвата второй ступени синхронизации определяется емкостью первой и второй группы регистров 46 и 47.

Работу системы 1Д1Кловой синхронизации рассмотрим для случая, когда время многолучевого растяжения не превышает длительности группового сигнала.

Пусть в первой и второй группах регистров 46 и 47 оказались записанными реализации групповых сигналов. 5 (t)HS )i(t) длиной по два сигнала каждая S (t), Sj (t) и S- (t), Sj (t), имею11Ц-1Х взаимное рассогласование л 4 C.

В исходном состоянии на выходе прямого счетчика 26 присутствует код 000, а на выходе обратного счетчика 27 - код 111. Под действием этих кодов первая и вторая группы КУС 48 и 49 установлены соответственно в начальное и конечное положения, т.е первая группа КУС 48 коммутирует на свои N выходов входы 1 -г N, а вторая группа КУС 49 коммутирует на свои N выходов входы N+1-J-2N. В результате . этого в первой и второй группах элементов 50 и 51 происходит сравнение реализаций сигналов S (с)и8 к (t).. Сравнение происходит поразрядно. Если все разряды сравнимаемых двоичных чисел совпали, то на выходе первой и второй групп элементов 50 и 51 появляется логический сигнал 1, если не совпадает хотя бы один разряд - О

Особенностью этих групповых сигналов является совпадение N-1 их эле.- ментов. Поэтому по числу совпадений э.чементов можно с определенной вероятностью говорить о наличии или отсутствии их временного расхощ;ения. Суммарное напряжение U , получаемое в сумматоре 52, сравни вается с опор981936

ным пороговым напряжением в компараторе 28. Опорное напряжение, выбирается из условия и рр N-1 или несколько меньше с учетом амплитудных искажений в канале связи. Если условие и выполняется, то на выходе компаратора 28 присутствует о. Второй дополнительньй элемент 10 ЗАПРЕТ 30 открывается и импульсы с выхода генератора 21 подаются на счетный вход триггера 29. Первый тактовый импульс изменит состояние триггера 29 на единичное. На смену сос- 15 тояния триггера 29 отреагирует обрат- ньм счетчик 27. На выходе обратного счетчика 27 появится код 110, под действием которого первая группа КУС 48 изменит свое состояние на од- 20 ну ПОЗИ1ЩЮ. На выходы второй группы КУС 49 коммутируются входы N-2N-1. Первая группа КУС 48 своего состояния не изменила, следовательно, временное расхождение сигналов измени- 25 лось на один такт (в данном случае уменьБ1илось). Суммарное напряжение в этом случае равно U 1, Условие вьшолняется и компаратор своего состояния не меняет (находит- 30 ся в нуле). Второй дополнительный элемент ЗАПРЕТ 28 открыт, а тактовые импульсы продолжают поступать на счетный вход триггера 29.

После второго тактового импульса j на счетном входе триггера 29 с вое положение изменит прямой счетчик 26. Его состояние станет равным 001. Первая группа КУС 48 коммутирует на свои выходы входы с номерами 2-TN-H . 40 Вторая группа КУС 49 своего состояния не изменила, следовательно, в первой и второй группах элементов 50 и 51 произойдет сравнение двух реализа1шй групповых сигналов. В этом 45 случае U 1 .

На следующем такте (третье - по счету) состояние обратного счетчика 27 станет равным 101. Суммарное напряжение для данного временного поло- 50 жения групповых сигналов равно U ,2. Под действием четвертого тактового импульса состояние прямого и обратного счетчиков 26 и 27 равно соответственно 010 и 101. Суммарное напря- 55 женив на выходе сумматора 52 равно U5 7- Условие и 5 и on выполняется. Компаратор 28 открывается и единич- ным потенциалом с его выхода закрывается для прохождения тактовых им 1

пульсов второй дополнительный эле- мент-ЗАПРЕТ 28. Коррекция временного положения групповых сигналов прекращается, так как принимаефся решение о том, что их взаимное временное расхождение устранено.

Если в процессе передачи информации временное расхождение групповых сигналов вновь возникает, то условие

и Up нарушается. Компаратор 28

запирается, а второй дополнительный элемент ЗАПРЕТ 28 открьшается. Алгоритм устранения временного рассогласования повторяется.

Третий этап установления цикловой синхронизации заключается в устранении временного рассогласования меяоду принимаемыми групповыми сигналами и опорными функциями Уолша. Для этого групповые сигналы в первой и второй группах КУС 48 и 49 из двоичного кода вновь преобразуется в многоуровневые .

С41азированные между собой сигналы суммируются в первом сумматоре 3 и информационный групповой сигнал поступает в первый блок 6 для вычисления коэ15)фициентов корреляции опорными функциями Уолша, Кроме этого, групповой сигнал отрицательного кода инвертируется инвертором 15 и суммируется с групповым сигналом положительного кода во втором сумматоре 4 Групповой синхросигнал с выхода второго сумматора 4 подается на вход второго блока 9 для вычисления коэф- фи1щентов корреляции с опорными сигналами о

Групповой синхросигнал будет пери одическим, так как от информационных параметров ) он не зависит, а определяется только синхрокодом Tbj который остается постоянным на все

8

В случае, если напряжения не сов0

5

0

5

0

падают (отношение сид нал/шум ниже максимального значения), на выхоле элемента 12 равнозначности формируется нулевой потенциал, открывающий элементы ЗАПРЕТ 1 1 , при условии, что на выходе старших по номеру элементов равнозначности нет единичных потешщалри.

Поскольку максимальное отношение сигнал/шум, формируемое вторым блоком 9, растет с увеличением номера коррелятора (что достигается за счет увеличения энергии соответствующих опорных сигналов), то вероятность ошибки в принятом решении в соответствующем элементе 12 равнозначности уменьшается с увеличением номера. Поэтому управляющими сигнал формируется из отклика на выходе старшего по номеру элемента 12 равнозначности, а все младшие элементы 12 равнозначности блокируются путем подачи запрещающего сигнала на соответствующие элементы ЗАПРЕТ 11.

По окончании цикла интегрирования из генератора 5 на прямые входы элементов ЗАПРЕТ 11 и на синхронизирующие входы триггеров 13 поступает короткий импульс конца цикла (ИКЦ),

0 на вход i-ro

5

Если на выходе элементов 12 равнозначности нулевой потенциал ( С,. / 0) , ИКЦ через открытый элемент ЗАПРЕТ 11 поступает на вход предварительной записи соответствующего триггера 13 и переводит его в единичное состояние.

Если О, то ИКЦ не проходит

и всех млад1:шх по номеру триггеров 13, которые остаются в нулевом Положении, В результате этого в триггерах 13 оказывается записанным код ошибки синхронизации и на

| название | год | авторы | номер документа |

|---|---|---|---|

| Система цикловой синхронизации для многоканальных систем связи | 1984 |

|

SU1238257A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1990 |

|

SU1800635A1 |

| Устройство цикловой синхронизации многоканальных систем связи | 1990 |

|

SU1757116A1 |

| Устройство синхронизации по групповому сигналу в многоканальных системах связи | 1987 |

|

SU1522418A1 |

| Устройство цикловой синхронизации многоканальных систем связи | 1983 |

|

SU1190531A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости синхронизации. Для этого система цикловой синхронизации для многоканальных систем связи содержит на приемной стороне два приемника, два сумматора сигналов, г-р сигналов опорных ф-ций Уолша, блок активных фильтров, блок записи и обработки информации, два эл-та И, блок корреляционных фильтров, блок тактовой синхронизации, N+2 эл-тов. ЗАПРЕТ, N+1 эл-тов равнозначности, N+1 триггеров, эл-т ИЛИ, инвертор, блок формирователей опорных сигналов, выпрямитель, блок дополнительного кодирования, г-р тактовых импульсов, делитель, блоки фазирования по тактам группового сигнала положительного и отрицательного кодов, блок взаимного фазирования, прямой и обратный счетчики и компаратор, а на передающей стороне N источников информации, по N формирователей посылок положительной и отрицательной полярности, два формирователя группового сигнала, два передатчика, г-р тактовых импульсов и два блока дополнительного кодирования. В данной системе решение о наличии цикловой синхронизации, а также слежения в процессе передачи информации осуществляется на основе выходного напряжения эл-та равнозначности. Даны примеры выполнения блоков фазирования по тактам и блока взаимного фазирования. 2 з.п. ф-лы, 4 ил.

время сеанса связи, С выходов второго 45 выходе элемента ИЛИ 14 появится едиблока 9 напряжения поступают на входы элементов 12 -равнозначности, где они сравниваются с постоянными напряжениями определенной величины: в i-M элементе равнозначности опорное напряжение определяется из условия

50

ничный потенциал, который закрывает первый дополнительный элемент ЗАПРЕТ 20 и открывает второй элемент И 17 для прохождения тактовых импульсов с выхода блока 10 на счетный вход первого триггера 13. Так как триггеры 13 образуют двоичный вычитающий счетхшк с параллельной записью, то под действием тактовых импульсов на счетном входе первого триггера 13 вся цепочка триггеров 13 начинает работать в режиме обратного счета. Как только состояние всех триггеров 13 станет равно нулю, на выходе элеи

и,

оп

о

W- 1) on

и .g

И

N (п+1)-м канале 1.

В случае, если напряжение на входах элементов 12 равнозначности совпадает, на его выходе формируется единичньй потенциал, закрывающий соответствующий элемент ЗАПРЕТ 11 и вс младпше по номеру.

0

5

ничный потенциал, который закрывает первый дополнительный элемент ЗАПРЕТ 20 и открывает второй элемент И 17 для прохождения тактовых импульсов с выхода блока 10 на счетный вход первого триггера 13. Так как триггеры 13 образуют двоичный вычитающий счетхшк с параллельной записью, то под действием тактовых импульсов на счетном входе первого триггера 13 вся цепочка триггеров 13 начинает работать в режиме обратного счета. Как только состояние всех триггеров 13 станет равно нулю, на выходе элемента ИЛИ 14 появится нулевой потенциал, под действием которого второй элемент И 17 закроет доступ тактовых импульсов на счетный вход первого триггера 13 и откроется первый дополнительный элемент ЗАПРЕТ 20 для прохождения тактовых импульсов на вход генератора 5, где начнется формирование опорных функций Уолша, Начинается новый цикл интегрирования.

По окончании второго цикла интегрирования ИКЦ вновь поступает на входы элементов ЗАПРЕТ 11 и на синхронизирующие входы триггеров 13.

Если ошибка синхронизации скомпенсирована на предыдущем цикле интегрирования во время работы обратного счета триггеров 13, то на выходах элементов 12 равнозначности будут единичные потенциалы (отношение сигнал/шум максимальное), закрывающие элементы ЗАПРЕТ 11 для записи-в триггеры 13 ИКЦ. Единичный потен1щал с выхода дополнительного (п+1)-го элемента .12 равнозначности открывает , первьй элемент И 8 для прохождения ИКЦ на управляюп(ий вход блока 7 и закрывает все элементы ЗАПРЕТ 11 для исключения влияния ложного срабатывания остальных элементов 12 равно-. значности. Если в элементах 12 равнозначности младших по номеру произойдет ошибка в оценке синхропара- .метра, а в старшем - правильный прием, то младслие по номеру элементы 12 равнозначности блокируются, а управляющий сигнал формируется на основе отклика старшего по номеру элемента 12 равнозначности.

Окончательное решение о наличии цикловой синхронизации, а также слежение в процессе передачи информации осуществляется на основе выходного напряжения дополнительного (п+1)-го элемента 12 равнозначности. Если на выходе этого элемента 12 равнозначности полоз ительный потенциал в момент прихода ИКЦ (отношение сигнал/шум максимальное), то система в синхронизме и, следовательно, выходные напряжения всех остальных элементов 12 равнозначности не анализируются.

Формула изобретения

1,Система цикловой синхронизации дпя многоканальных систем связи, со0

держаьчая на передающей стороне N источников информации, последовательно соединенные N формирователей посылок отрицательной полярности и первые блок дополнительного кодирования, формирователь группового сигнала и передатчик, последовательно соединенные N формирователей посылок положительной полярности и вторые блок дополнительного кодирования, формирователь группового сигнала и передатчик, а также генератор тактовых импульсов (ГТИ), выход которого подключен к

5 тактовым входам первого и второго формирователей группового сигнала, вход каждого из N формирователей посылок отрицательной полярности соединен с входом соответствующего фор0 мирователя посылок положительной по- лярности и подключен к выходу соот- вествующего источника информации, входы которых соединены и подключены к второму выходу второго формировате5 ля группового сигнала, управляющие входы первого и второго блоков дополнительного кодирования соединены между собой и являются входами синхро- кода, выходы первого и второго передатчиков являются соответственно первым и вторым выходами передающей стороны системы цикловой синхрониза-. ции для многоканальных систем связи, а на приемной стороне - первый и второй приемники, генератор тактовых импульсов (ТИ), последовательно соединенные первый сумматор, блок актив- . ных фильтров и блок записи и обработки информации, последовательно сое0 диненные инвертор, второй сумматор, выпрямитель, блок тактовой синхронизации, первый дополнительный элемент ЗАПРЕТ, генератор опорных функций Уолша, блок дополнительного кодирования -i блок формирования опорных сигналов, блок корреляционных фильтров, п+1 элементов равнозначности, п элементов ЗАПРЕТ, п триггеров и эле- мент ИЛИ, а также первый и второй элементы И, выходы которых подключены соответственно к управляющему входу блока записи и обработки информации и счетному входу первого триггера, причем инверсный выход преды- яущего триггера соединен со счетным входом последующего триггера, управляющие входы блока дополнительного кодирования являются входами синхро- кода, тактовый выход генератора опор0

5

5

0

5

ных функгшй Уолша подключен к соединенным тактовым входам блока активных фильтров и блока коррелягщонных фильтров, к прямым входам п элементов ЗА11ГЕТ и к синхронизирующим вхо- дШ л п Т; аггеров, и к первому входу первого элемента И, выход (п+1)-го элемента равнозначности подключен к сое;даненным второму входу, negeoro элемента И и инверсным входам всех элементов ЗАПРЕТj выход каждого элемента равнозначности, кроме первого и последнего, дополнительно соединен с вторыми инверсными входами всех пре дьщу115их элементов ЗАПРЕТ, вторые входы всех элементов равнозначности являются входами опорных напряжений, причем величина опорного напряжения тем больше, чем выше номер элемента равнозначности, первый и второй входы второго элемента И подключены соответственно к прямому входу первого дополнительного элемента ЗАПРЕТ, и к соединенным инверсному входу первого дополнительного элемента ЗАПРЕТ и выходу элемента ИЛИ, причем входы первого и второго приемников являются соответственно первым и вторым входами щэиемной стороны системы цикловой синхронизагщи для многоканальных систем связи, отличающая- с я теМр что, с цео1ью повышения помехоустойчивости синхронизации, на передающей стороне введены блок фа- зирования по тактам группового сигнала положительного кода, блок фазирования по тактам группового сигнала отрицательного кода, блок взаимного фазирования, прямой и обратный счет- чики, компаратор, дополнительный триггер, второй дополнительный элемент ЗАПРЕТ и делитель, причем выходы первого и второго приемников соответственно через блоки фазирова- ния по тактам групповых сигналов положительного кода и отрицательного кода подключены соответственно к первому и BTopohfy информационным входам блока взаимного фазирования, такто- вый вход которого подключен к соеди- HeHHbiNi тактовым входам блоков фазирования по тактам групповых сигналов положительного кода и отрицательного кода и к выходу блока тактовой син- хронизации, первый и второй информационные выходы блока взаимного фазирования подключены Соответственно к соединенным hepBOMy входу первого

сумматора и входу инвертора и к соединенным вторым.входам первого и второго сумматора, выход генератора ТИ соединен с опорным входом блока тактовой синхронизации через делитель и с прямым входом второго дополнительного элемента ЗАПРЕТ, выход которого подключен к счетному входу триггера, прямой и инверсный выходы которого соответственно через прямой и обрат- ньй счетчики подключены соответственно к первой и второй группам управяющих входов блока взаимного фазирова- ния, управляющий выход которого через компаратор подключен к инверсному входу второго дополнительного элемента ЗАПРЕТ.

5

0 0 e 0 5 0

2 оСистема по п.1, отличающая с я тем, что блоки фазирования по тактам группового сигнала положительного и отрицательного кода идентичны, каждый содержит последовательно соединенные управляемую линию за- держки, ограничитель, фазовый дискриминатор, реверсивный счетчик и дешифратор, вход и .выход управляемой линии задержки являются соответственно входом и выходом блоков, тактовый вход фазового дискриминатора является тактовым входом блоков.

3,Система попо1, отличающаяся тем, что блок взаимного фазирования содержит последовательно соединенные первые группы регистров, компенсационных устройств сдвига и элементов сравнения, последовательно соединенные вторые группы регистров, компенсационных устройств сдвига и элементов сравнения, а также сумматор, выход которого является управляющим выходом блока взаимного фазирования, вторые группы выходов первой и второй групп компенсационных устройств сдвига подключены к соответствующим группам входов второй и первой групп элементов сравнения, выходы которых подключены к соответствующим входам сумматора, тактовый вход блока подключен к соединенным тактовым входам первой и второй групп регистров, первый и второй информационные входы блока подключены соответственно к информатщонным входам первой и второй групп регистров, информационные выходы и первая и вторая группы управляющих.входов первой и второй

групп компенсационных устройств сдвига рым выходами блока первой и второй являются соответственно первым и вто- групп управляющих входов блока.

Фиг. 2.

.ZT J

as.J

Г

k

:

f

52

51

М

9

.. q

7

ЧРаг.

| Стол для вращательного бурения скважин | 1928 |

|

SU15071A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-10-07—Публикация

1988-04-18—Подача