Изобретение относится к многоканальной связи и может использоваться в системах многоканальной связи с кодовым разделением использующихся в каналах несущих функций Уолша.

Целью изобретения является повышение помехоустойчивости цикловой синхро - низации за счет обнаружения и устранений влияния пропусков элементов на стыке двух сигналов на процесс синхронизации.

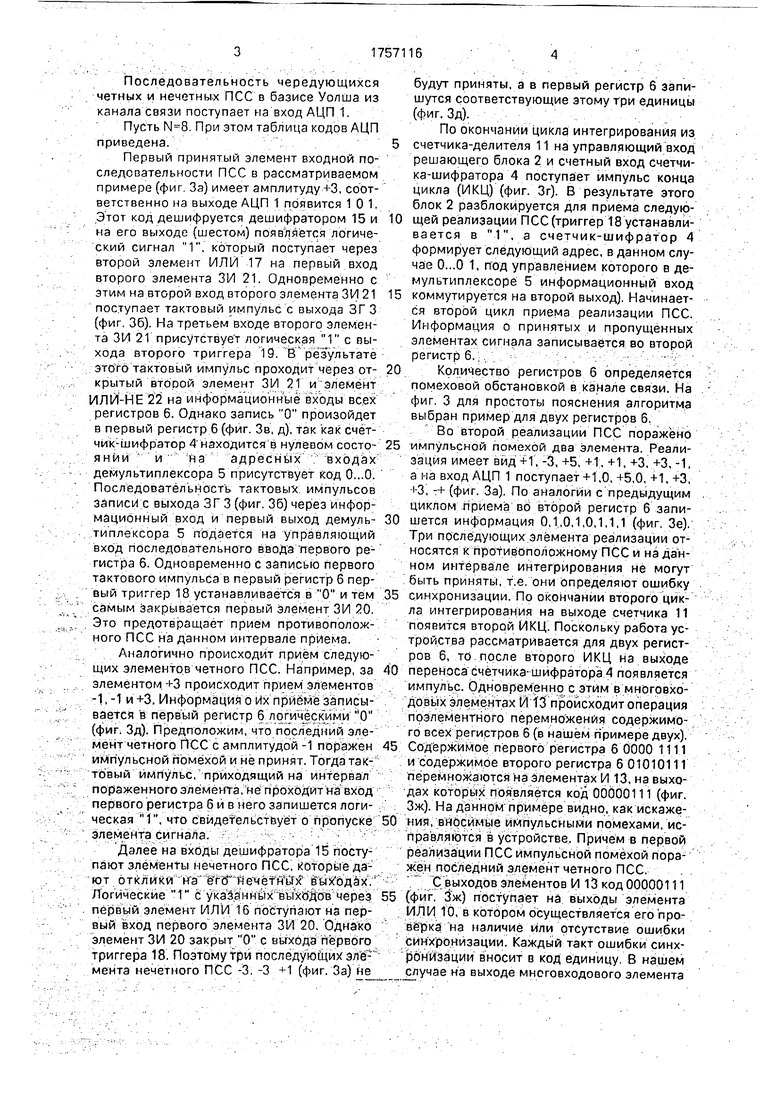

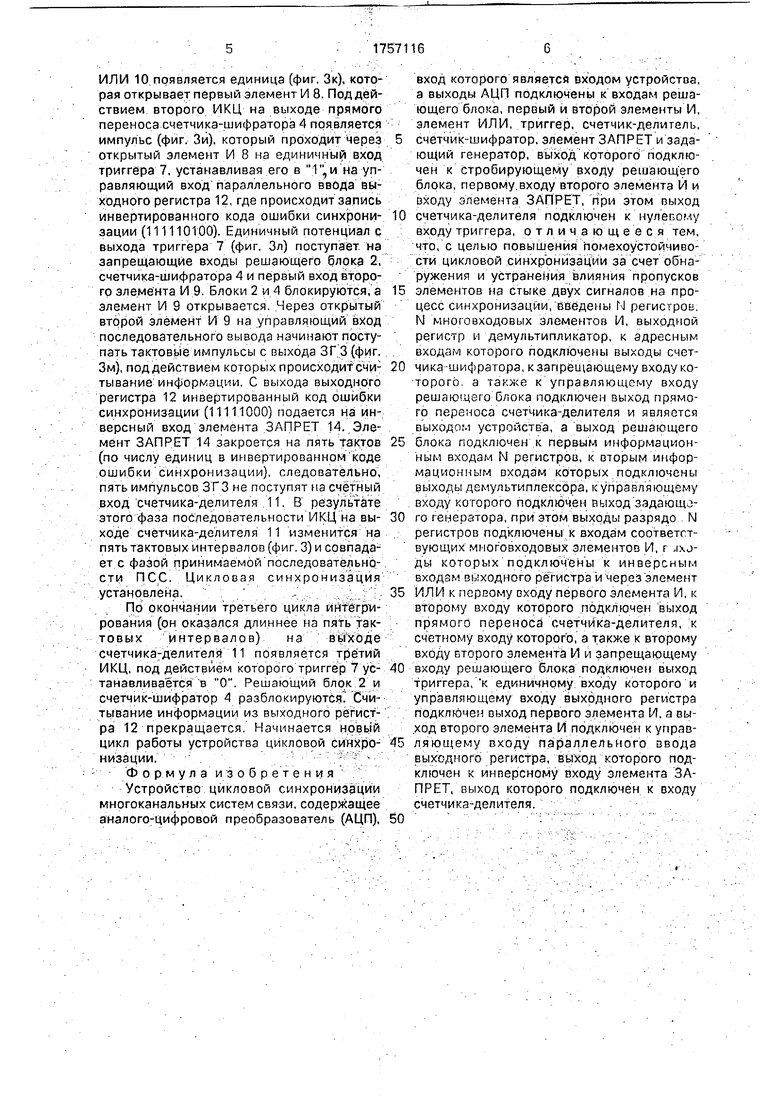

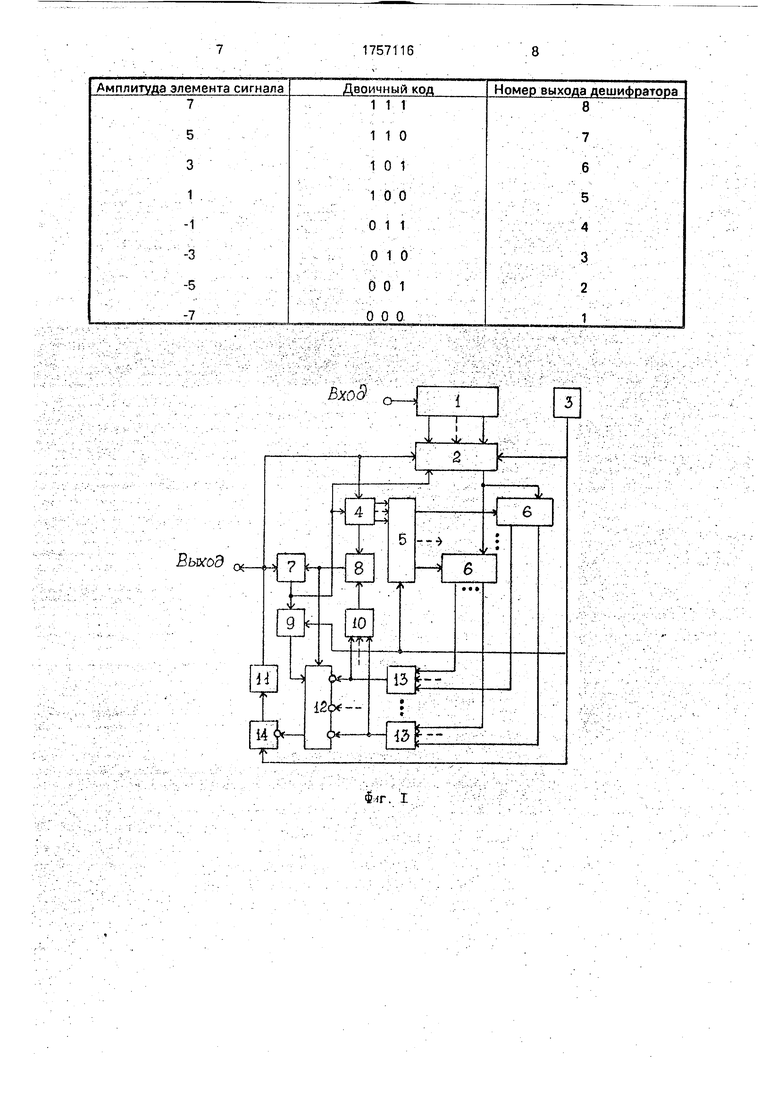

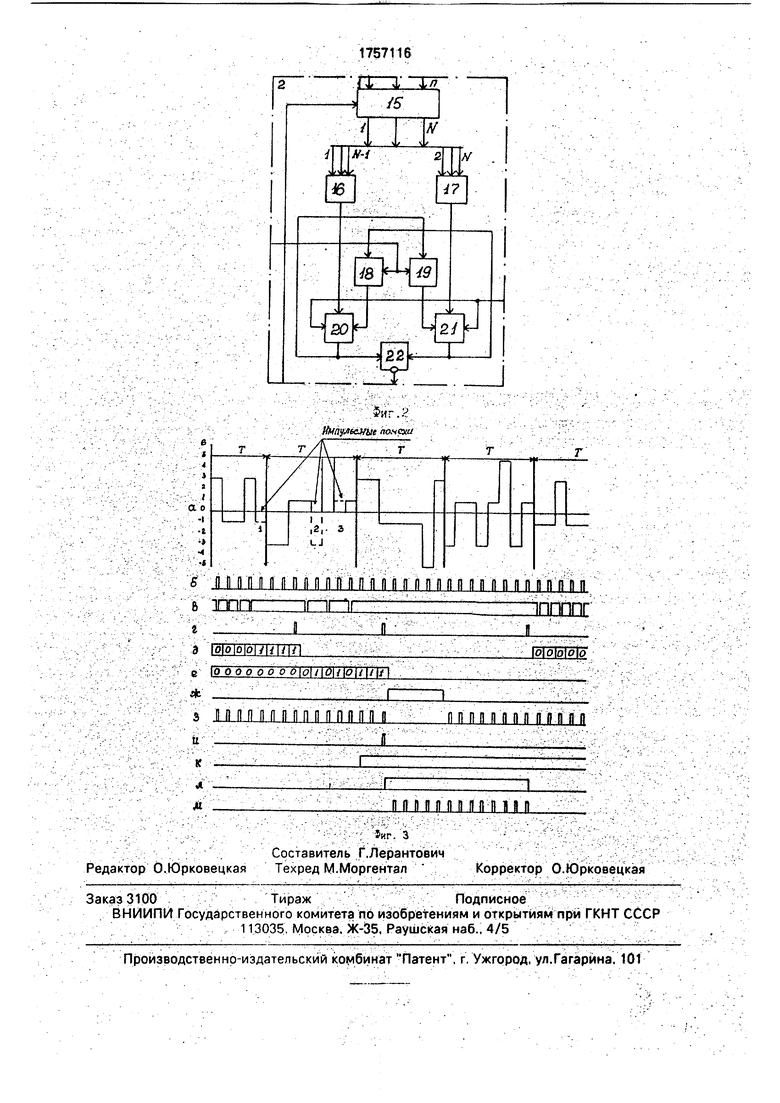

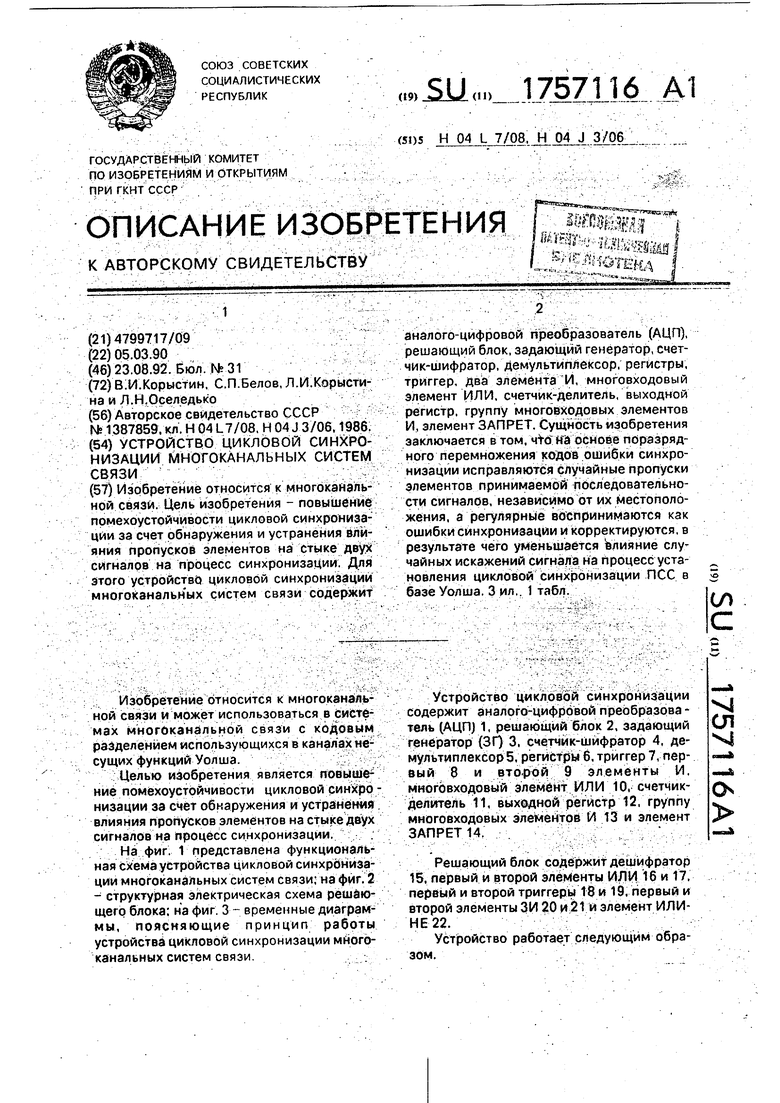

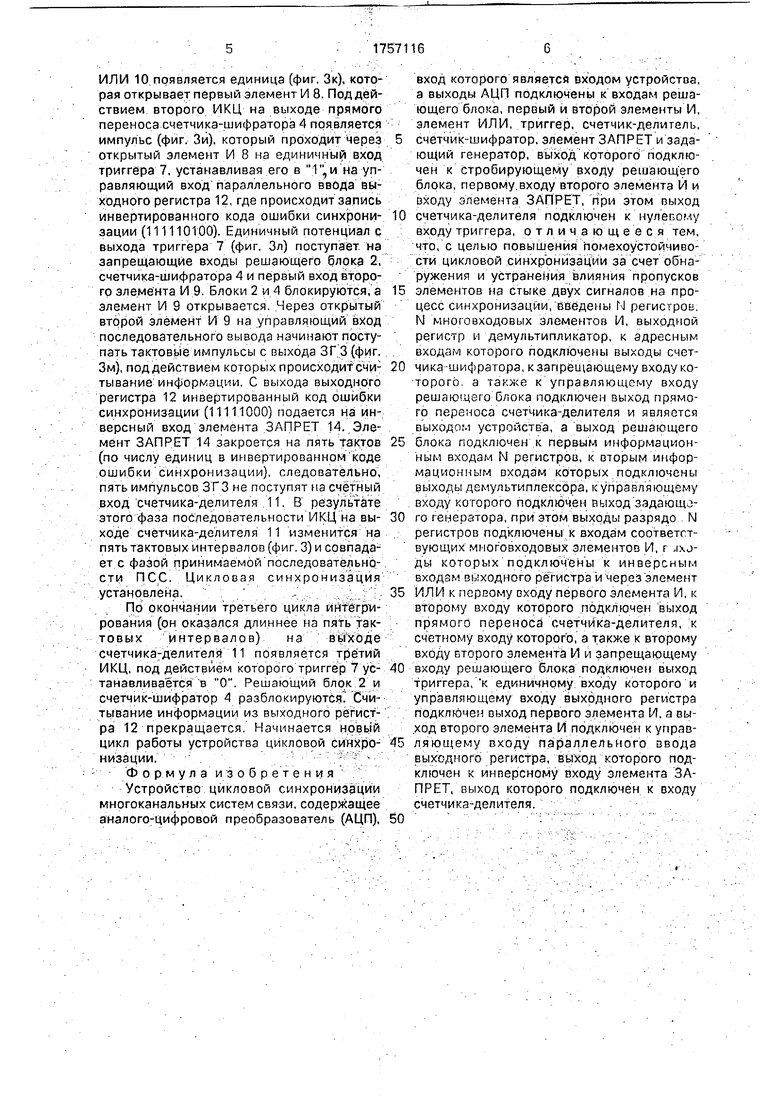

На фиг. 1 представлена функциональная схема устройства цикловой синхронизации многоканальных систем связи; на фиг. 2 - структурная электрическая схема решающего блока; на фиг 3 - временные диаграммы, поясняющие принцип работы устройства цикловой синхронизации многоканальных систем связи

Устройство цикловой синхронизации содержит аналого-цифровой преобразова - тель (АЦП) 1, решающий блок 2, задающий генератор (ЗГ) 3, счетчик-шифратор 4, демультиплексор 5, регистры 6, триггер 7, первый 8 и второй 9 элементы И, многовходовый элемент ИЛИ 10, счетчик- делитель 11, выходной регистр 12, группу многовходовых элементов И 13 и элемент ЗАПРЕТ 14.

Решающий блок содержит дешифратор 15, первый и второй элементы ИЛИ 16 и 17, первый и второй триггеры 18 и 19. первый и второй элементы ЗИ 20 и 21 и элемент ИЛИ- НЕ22.

Устройство работает следующим образом.

VI СП

XI

о

Последовательность чередующихся четных и нечетных ПСС в базисе Уолша из канала связи поступает на вход АЦП 1.

Пусть При этом таблица кодов АЦП приведена.

Первый принятый элемент входной последовательности ПСС в рассматриваемом примере (фиг За) имеет амплитуду +3, соответственно на выходе АЦП 1 появится 101. Этот код дешифруется дешифратором 15 и на его выходе (шестом) появляется логический сигнал 1, который поступает через второй элемент ИЛИ 17 на первый вход второго элемента ЗИ 21. Одновременно с этим на второй вход второго элемента ЗИ 21 поступает тактовый импульс с выхода ЗГ 3 (фиг 36). На третьем входе второго элемента ЗИ 21 присутствует логическая 1 с выхода второго триггера 19. В результате этого тактовый импульс проходит через открытый второй элемент ЗИ 21 и элемент ИЛИ-НЕ 22 на информационные входы всех регистров 6. Однако запись О произойдет в первый регистр 6 (фиг Зв, д), так как счетчик-шифратор 4 находится в нулевом состо- янии и на адресных входах демультиплексора 5 присутствует код 0...0. Последовательность тактовых импульсов записи с выхода ЗГ 3 (фиг 36) через информационный вход и первый выход демультиплексора 5 подается на управляющий вход последовательного ввода пеового регистра 6. Одновременно с записью первого тактового импульса в первый регистр б первый триггер 18 устанавливается в О и тем самым закрывается первый элемент ЗИ 20. Это предотвращает прием противоположного ПСС на данном интервале приема.

Аналогично происходит прием следующих элементов четного ПСС. Например, за элементом ьЗ происходит прием элементов -1, -1 и +3. Информации о Их приеме записывается в первый регистр 6 логическими О (фиг. Зд). Предположим, что последний элемент четного ПСС с амплитудой -1 поражен импульсной помехой и не принят. Тогда тактовый импульс, приходящий на интервал пораженного элемента, не проходит на вход первого регистра бив него запишется логическая 1, что свидетельствует о пропуске элемента сигнала.

Далее на входы дешифратора 15 поступают элементы нечетного ПСС, которые дают отклики ига е го нечетн ьЫ вых одах. Яогические Г с указанных выхбДотз через первый элемент ИЛИ 16 поступают на первый вход первого элемента ЗИ 20. Однако элемент ЗИ 20 закрыт О с выхода первого триггера 18. Поэтому три последующих элемента нечетного ПСС -3 -3 +1 (фиг. За) не

будут приняты, а в первый регистр б запишутся соответствующие этому три единицы (фиг. Зд).

По окончании цикла интегрирования из

счетчика-делителя 11 на управляющий вход решающего блока 2 и счетный вход счетчика-шифратора 4 поступает импульс конца цикла (ИКЦ) (фиг. Зг). В результате этого блок 2 разблокируется для приема следую0 щей реализации ПСС (триггер 18 устанавли- вается в 1, а счетчик-шифратор 4 формирует следующий адрес, в данном случае 0...0 1, под управлением которого в де- мультиплексоре 5 информационный вход

5 коммутируется на второй выход). Начинается второй цикл приема реализации ПСС. Информация о принятых и пропущенных элементах сигнала записывается во второй регистр 6.

0 Количество регистров 6 определяется помеховой обстановкой в канале связи. На фиг 3 для простоты пояснения алгоритма выбран пример для двух регистров 6.

Во второй реализации ПСС поражено

5 импульсной помехой два элемента. Реализация имеет вид +1, -3, +5, +1, +1, +3. +3, -1, а на вход АЦП 1 поступает+1,0, +5,0, +1. +3, 3, -ь (фиг. За). По аналогии с предыдущим циклом приема во второй регистр б запи0 шется информация 0,1,0,1,0,1,1,1 (фиг. Зе). Три последующих элемента реализации относятся к противоположному ПСС и на данном интервале интегрирования не могут быть приняты, т.е они определяют ошибку

5 синхронизации. По окончании второго цикла интегрирования на выходе счетчика 11 появится второй ИКЦ. Поскольку работа устройства рассматривается для двух регистров 6, то после второго ИКЦ на выходе

0 переноса счетчика-шифратора 4 появляется импульс. Одновременно с этим в многовхо- довых элементах И f 3 происходит операция поэлементного перемножения содержимого всех регистров 6 (в нашем примере двух).

5 Содержимое первого регистра б 0000 1111 и содержимое второго регистра 6 01010111 перемножаются на Элементах И 13, на выходах которых появляется код 00000111 (фиг. Зж). На данном примере видно, как искаже0 ния, вносимые импульсными помехами, исправляются в устройстве. Причем в первой реализации ПСС импульсной помехой поражен последний элемент четного ПСС.

С выходов элементов И 13 код 00000111

5 (фиг. Зж) поступает на выходы элемента ИЛИ 10, в котором осуществляется его проверка на наличие или отсутствие ошибки синхронизации. Каждый такт ошибки синхронизации вносит в код единицу В нашем случае на выходе мнсговходового элемента

ИЛИ 10 появляется единица (фиг. Зк), которая открывает первый элемент И 8. Под действием второго ИКЦ на выходе прямого переноса счетчика-шифратора 4 появляется импульс (фиг. Зи), который проходит через открытый элемент И 8 на единичный вход триггера 7, устанавливая его в 1, и на управляющий вход параллельного ввода выходного регистра 12, где происходит запись инвертированного кода ошибки синхрони- зации (111110100). Единичный потенциал с выхода триггера 7 (фиг. Зл) поступает на запрещающие входы решающего блока 2, счетчика-шифратора 4 и первый вход второго элемента И 9. Блоки 2 и 4 блокируются, а элемент И 9 открывается. Через открытый второй элемент И 9 на управляющий вход последовательного вывода начинают поступать тактовые импульсы с выхода ЗГ 3 (фиг. Зм), под действием которых происходит счи- тывание информации. С выхода выходного регистра 12 инвертированный код ошибки синхронизации (11111000) подается на инверсный вход элемента ЗАПРЕТ 14. Элемент ЗАПРЕТ 14 закроется на пять тактов (по числу единиц в инвертированном коде ошибки синхронизации), следовательно, пять импульсов ЗГЗ не поступят на счетный вход счетчика-делителя 11. В результате этого фаза последовательности ИКЦ на вы- ходе счетчика-делителя 11 изменится на пять тактовых интервалов (фиг. 3) и совпадает с фазой принимаемой последовательности ПСС, Цикловая синхронизация установлена.-

По окончании третьего цикла интегрирования (он оказался длиннее на пять тактовых интервалов) на вы ходе счетчика-делителя 11 появляется третий ИКЦ, под действием которого триггер 7 ус- танавливается в О. Решающий блок 2 и счетчик-шифратор 4 разблокируются Считывание информации из выходного регистра 12 прекращается. Начинается новый цикл работы устройства цикловой синхро- низации.

Формула изобретения Устройство цикловой синхронизации многоканальных систем связи, содержащее аналого-цифровой преобразователь (АЦП),

вход которого является входом устройства, а выходы АЦП подключены к входам решающего блока, первый и второй элементы И, элемент ИЛИ, триггер, счетчик-делитель, счетчик-шифратор, элемент ЗАПРЕТ и задающий генератор, выход которого подключен к стробирующему входу решающего блока, первому входу второго элемента И и входу элемента ЗАПРЕТ, при этом выход счетчика-делителя подключен к нулевому входу триггера, отличающееся тем, что, с целью повышения помехоустойчивости цикловой синхронизации за счет обнаружения и устранения влияния пропусков элементов на стыке двух сигналов на процесс синхронизации, введены N регистров N МНОГ08ХОДОВЫХ элементов И, выходной регистр и демультипликатор, к адресным входам которою подключены выходы счетчика шифратора, к запрещающему входу которого а также к управляющему входу решающего блока подключен выход прямого переноса счетчика-делителя и является выходом устройства, а выход решающего блока подключен к первым информационным входам N регистров, к вторым информационным входам которых подключены выходы демультиплексора, к управляющему входу которого подключен выход зэдающ.з- го генеоатора, при этом выходы разряде N регистров подключены к входам соответствующих многовходовых элементов И, г jxj- ды которых подключены к инверсным входам выходного регистра и через элемент ИЛИ к первому входу первого элемента И, к второму входу которого подключен выход прямого переноса счетчика-делителя, к счетному входу которого, а также к второму входу второго элемента И и запрещающему входу решающего блока подключен выход триггера, к единичному входу которого и управляющему входу выходного регистра подключен выход первого элемента И, а выход второго элемента И подключен к управляющему входу параллельного ввода выходного регистра, выход которого подключен к инверсному входу элемента ЗАПРЕТ, выход которого подключен к входу счетчика-делителя.

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации многоканальных систем связи | 1983 |

|

SU1190531A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Устройство синхронизации по групповому сигналу в многоканальных системах связи | 1987 |

|

SU1522418A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1984 |

|

SU1238257A1 |

| Устройство синхронизации по групповому сигналу в многоканальных системах связи | 1984 |

|

SU1314471A1 |

| Тренажер радиотелеграфиста | 1987 |

|

SU1456987A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1991 |

|

RU2045769C1 |

| Устройство цикловой синхронизации | 1985 |

|

SU1332555A1 |

Изобретение относится к многоканальной связи. Цель изобретения - повышение помехоустойчивости цикловой синхронизации за счет обнаружения и устранения влияния пропусков элементов на стыке двух сигналов на процесс синхронизации. Для этого устройство цикловой синхронизации многоканальных систем связи содержит аналого-цифровой преобразователь (АЦП), решающий блок, задающий генератор, счетчик-шифратор, демультиплексор, регистры, триггер, два элемента И, многовходовый элемент ИЛИ, счетчик-делитель, выходной регистр, группу многовходовых элементов И, элемент ЗАПРЕТ. Сущность изобретения заключается в том, что На основе поразрядного перемножения кодов ошибки синхронизации исправляются случайные пропуски элементов принимаемой последовательности сигналов, независимо от их местоположения, а регулярные воспринимаются как ошибки синхронизации и корректируются, в результате чего уменьшается влияние случайных искажений сигнала на процесс установления цикловой синхронизации ПСС в базе Уолша. 3 ил. 1 табл. (Л

. I

ЧгоИ s/ -

ЗИГ.2

MbnyJeeJ/bie

4 1 I

a -i г

4

ПИЛИ «ПДОПМПДИЯЯДПДПП ДПЯП1ПИИ

imrn iriMr

О

1ППППГ

n

i

101010Ю1/1Л/1Л

to о о oo о о o |/|0|/|o /|/|/f

С

ПП ПП ПО О (1П П ППППО fl

L

,1

Д

5иг. 3

Составитель Г.Лерантович Редактор О.Юрковецкая Техред М.Моргентал

ПА /5

N-i

X

22

.. JTI

1ППППГ

n

i

|0|0|Q|0|(

ПП ПП П П П И П1И1 Л П

П О И П П fl fl П П И 0

Корректор О.Юрковецкая

| Авторское свидетельство СССР N; 1387859 | |||

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-08-23—Публикация

1990-03-05—Подача