mus.i

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи.

Целью изобретения является повышение точности регенерации цифрового сигнала.

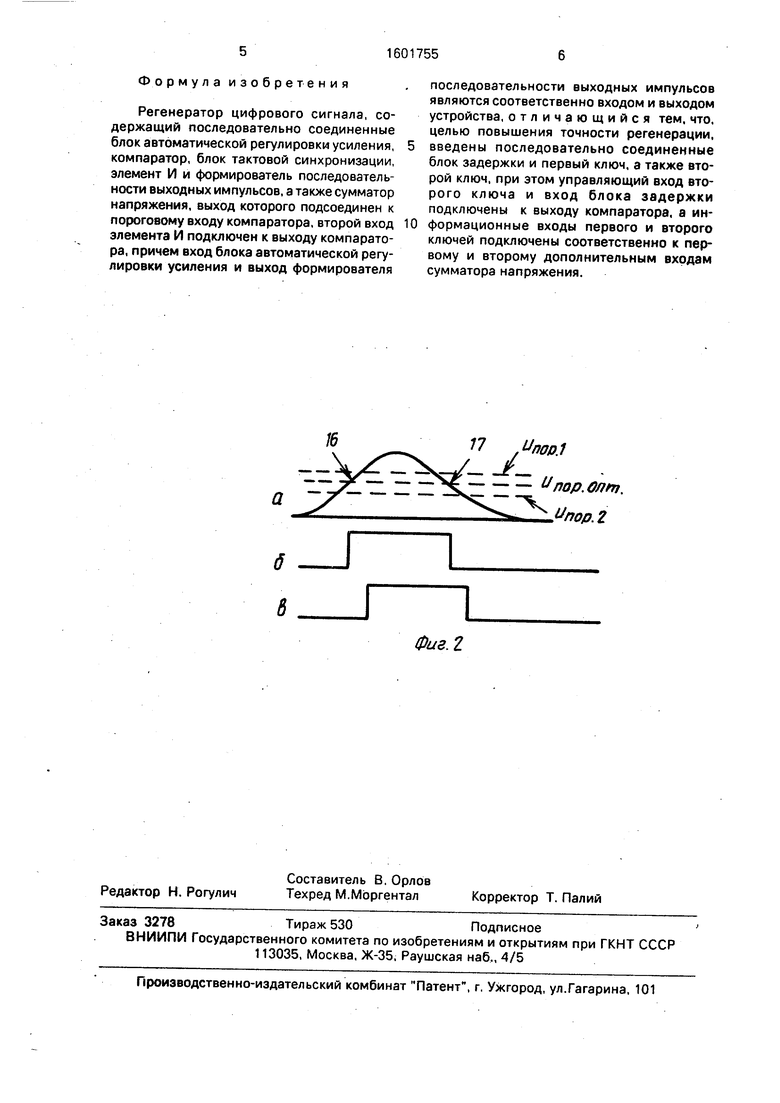

На фиг.1 представлена структурная электрическая схема регенератора цифрового сигнала; на фиг.2 - временные диаграммы сигналов, поясняющие работу регенератора цифрового сигнала.

Регенератор цифрового сигнала содержит блок 1 автоматической регулировки усиления, блок 2 задержки, компаратор 3, блок 4 тактовой синхронизации, элемент И 5, формирователь 6 последовательности выходных импульсов, сумматор 7 напряжения и первый 8 и второй 9 ключи.

Блок 1 автоматической регулировки усиления содержит корректирующий усилитель 10 и формирователь 11 управляющего

сигнала.

Сумматор 7 напряжения содержит первый 12 и второй 13 резисторы и первый 14 и второй 15 дополнительные резисторы.

Регенератор работает следующим образом.

Входные информационные импульсы цифрового сигнала после блока 1 автоматической регулировки усиления поступают на информационный вход компаратора 3. На пороговый его вход действует пороговое напряжение, которое до момента включения компаратора 3 сформировано первым 12 и вторым 13 резисторами и первым дополнительным резистором 14 (первый 12 и второй 13 резисторы подключены соответственно к шине стабилизированного напряжения (UCT) и общему проводу питания).

Первый дополнительный резистор 14 принимает участие в формировании порогового напряжения, так как до включения компаратора 3 (до его срабатывания) второй ключ 9 замкнут, в то время как первый ключ 8 находится в разомкнутом состоянии.

Первый 12 и второй 13 резисторы и первый дополнительный резистор 14 подобраны так. что при их совместном включении на пороговый вход компаратора 3 подают оптимальное пороговое напряжение (Unop.onr), равное половине амплитуды неискаженного информационного импульса (фиг.2а, на которой показан входной сигнал на информационном входе компаратора 3).

При нарастании уровня информационного импульса (входного сигнала) и достижения уровня оптимального порога (точка 16 на фиг.2а) произойдет включение компаратора 3 и на его выходе сформируется передний фронт прямоугольного импульса

5 10 1

а

(фиг.2б). В этот момент второй ключ 9 разомкнется под действием сигнала с выхода компаратора 3 и отключит первый дополнительный резистор 14 от шины стабилизиро- ванного напряжения. При этом уровень напряжения на пороговом входе компаратора 3 понижается до некоторого наперед заданного значения, например, до уровня Unop.2 (фиг.2а). Теперь для выключения ком- 0 паратора 3 необходимо, чтобы уровень сигнала стал меньше уровня Unop.2, а это значит, что помеха, действующая в точке 16 (фиг.2а), значение которой меньше разностного напряжения (Unop.onr. - Unop.2) не смо- 5 жет обратно перебросить (выключить) компаратор 3 в этой точке (Unop.2 выбирается с учетом величины уровня помехи в точке срабатывания). Импульс с выхода компаратора 3 (фиг.2б) с некоторой задер- 0 жкой, определяемой блоком 2 задержки, подается на управляющий вход первого ключа 8 и включает его. Теперь к выходу сумматора 7 напряжения подключается второй дополнительный резистор 15, который 25 подобран так, чтобы выключение компаратора 3 произошло точно в точке 17 (фиг.2а), т.е. в момент сравнения уменьшающегося по уровню входного импульса с оптимальным пороговым напряжением (Unop.oni. на 30 фиг,2а). В этот момент компаратор 3 отключается. При этом сформируется задний фронт импульса (фиг.25) и в этот же момент

вновь включится первый ключ 8 и подключит первый дополнительный резистор 14 к 35 выходу сумматора 7 напряжения, к которому уже подключен второй дополнительный резистор 15. Уровень порогового напряжения увеличится (например, до уровня Unop.i на фиг.2а) и, значит, помеха в точке 16 40 (фиг.2а), уровень которой меньше разностного напряжения (Unop.i Unop.onr), не вызовет обратного - опрокидывание (включение) компаратора 3 в точке 17. Через некоторое время, определяемое блоком 2 задержки, 45 исчезает импульс (фиг.2в) на управляющем входе первого ключа 8, и он отключается. При этом второй дополнительный резистор 15 отключится и на пороговый вход компаратора 3 вновь подается оптимальное поро- 50 говое напряжение Unop.onr. Время задержки блока 2 задержки выбирается с учетом уровня помех в точках переключения.

Сформированные прямоугольные импульсы с выхода компаратора 3 поступают 55 на вход блока 4 синхронизации и на второй вход элемента И 5, в котором происходит регистрация импульсов в оптимальные мо-. менты времени. Сигналы с выхода элемента И 5 через формирователь 6 передаются в линию.

Формула изобретения

Регенератор цифрового сигнала, содержащий последовательно соединенные блок автоматической регулировки усиления, компаратор, блок тактовой синхронизации, элемент И и формирователь последовательности выходных импульсов, а также сумматор напряжения, выход которого подсоединен к пороговому входу компаратора, второй вход элемента И подключен к выходу компаратора, причем вход блока автоматической регулировки усиления и выход формирователя

последовательности выходных импульсов являются соответственно входом и выходом устройства, отличающийся тем, что, целью повышения точности регенерации, введены последовательно соединенные блок задержки и первый ключ, а также второй ключ, при этом управляющий вход второго ключа и вход блока задержки подключены к выходу компаратора, а информационные входы первого и второго ключей подключены соответственно к первому и второму дополнительным входам сумматора напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УЛЬТРАЗВУКОВОЙ УРОВНЕМЕР | 2004 |

|

RU2292529C2 |

| Регенератор цифрового сигнала | 1986 |

|

SU1381728A1 |

| Регенератор цифрового сигнала | 1982 |

|

SU1083351A1 |

| Регенератор цифрового сигнала | 1986 |

|

SU1387203A1 |

| Регенератор цифрового сигнала | 1988 |

|

SU1540017A1 |

| Регенератор цифровых сигналов | 1988 |

|

SU1631740A1 |

| Регенератор цифрового сигнала | 1990 |

|

SU1748273A1 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1986 |

|

SU1363485A2 |

| Регенератор цифровых сигналов с квантованной обратной связью | 1987 |

|

SU1434552A1 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1990 |

|

SU1811007A2 |

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи. Целью изобретения является повышение точности регенерации цифрового сигнала. Регенератор цифрового сигнала содержит блок 1 автоматической регулировки усиления, блок задержки 2, компаратор 3, блок 4 тактовой синхронизации, элемент И 5, формирователь 6 последовательности выходных импульсов, сумматор напряжения 7, первый и второй ключи 8 и 9. В регенераторе цифрового сигнала достигается уменьшение влияния помех на процесс формирования прямоугольных импульсов компаратором 3 и восстановление их оптимального временного положения, что приводит к повышению точности регенерации. 2 ил.

а

б 8

/rOfl. ff/7f7j.

/7fi.f

ife.Z

Авторы

Даты

1990-10-23—Публикация

1988-12-26—Подача