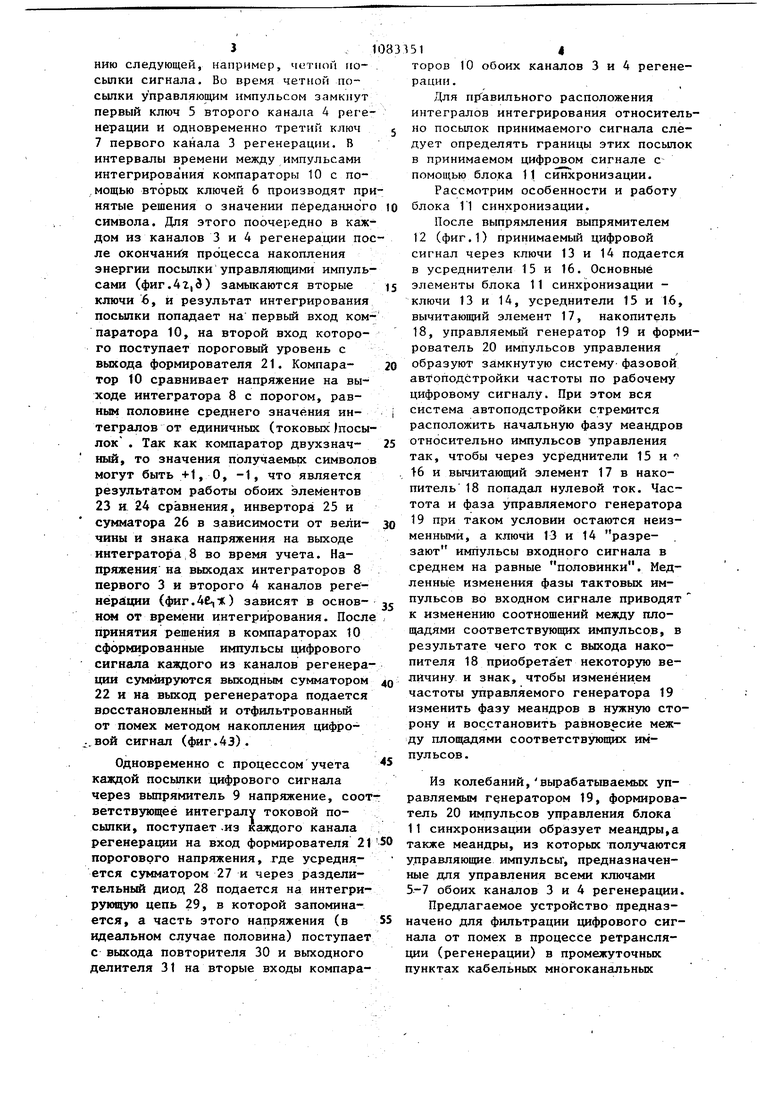

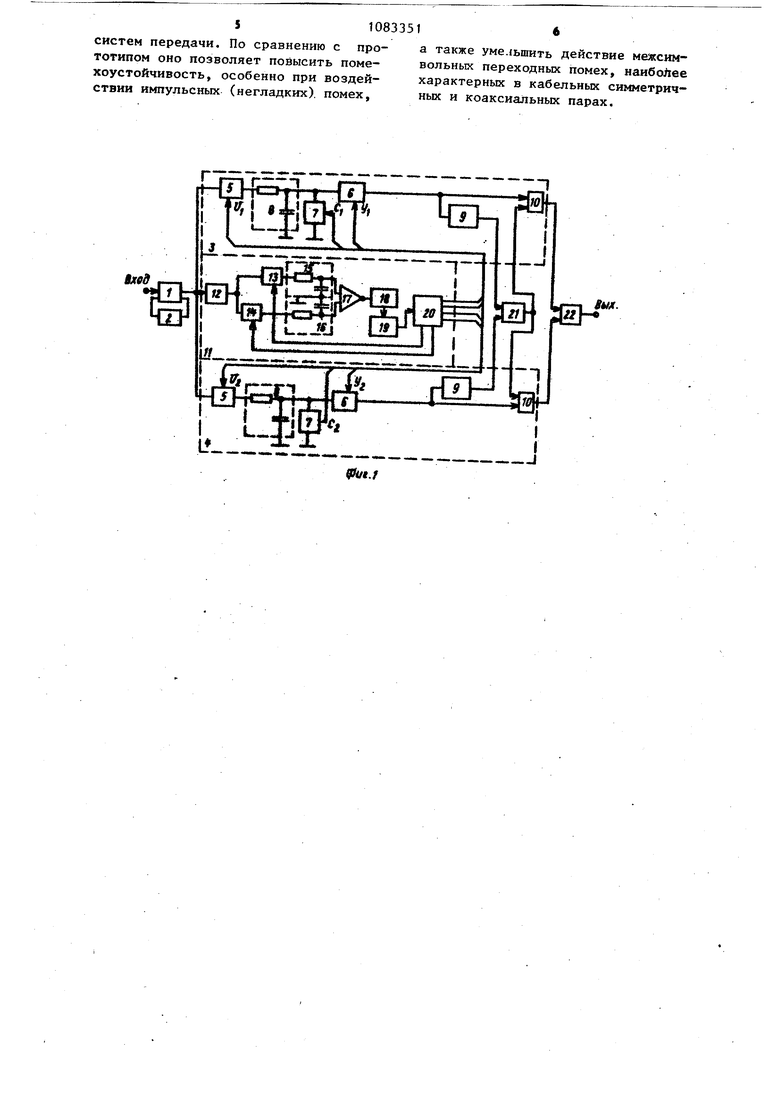

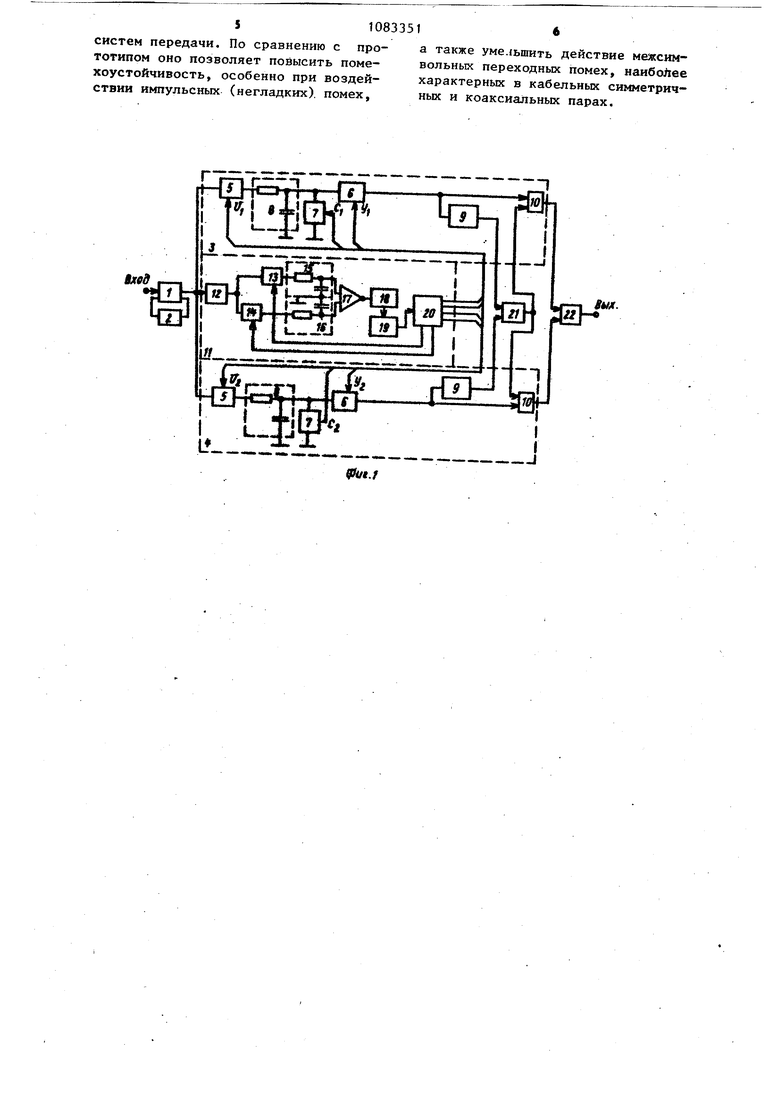

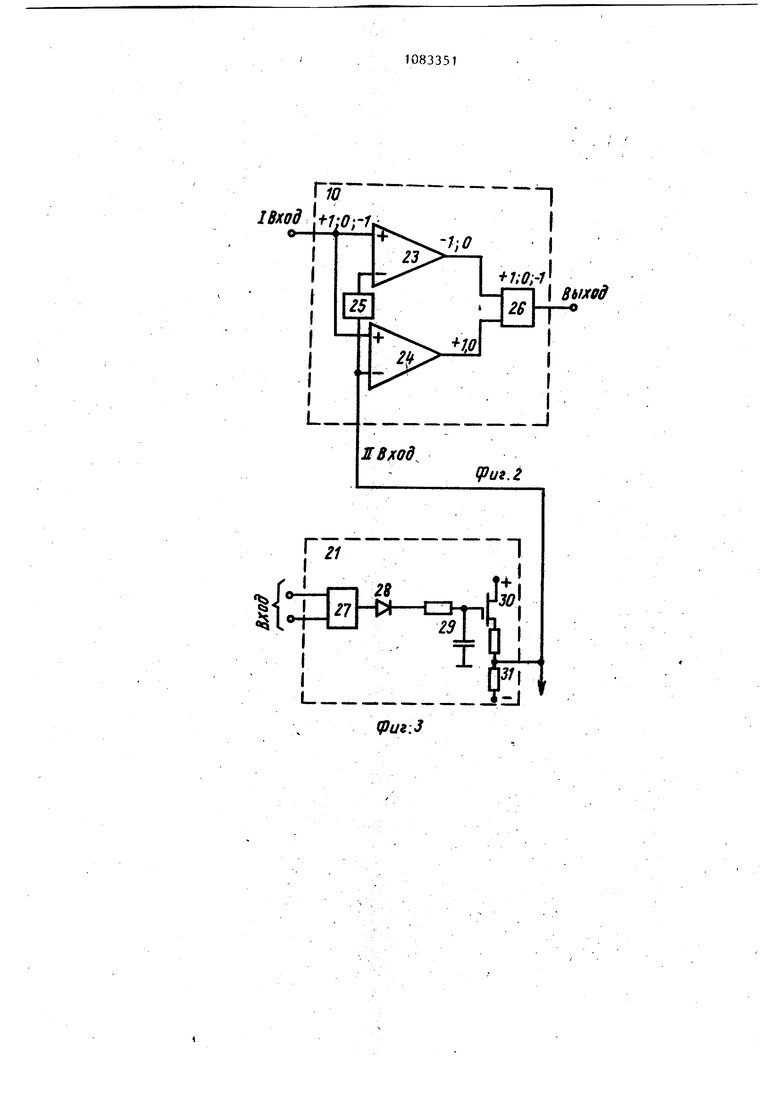

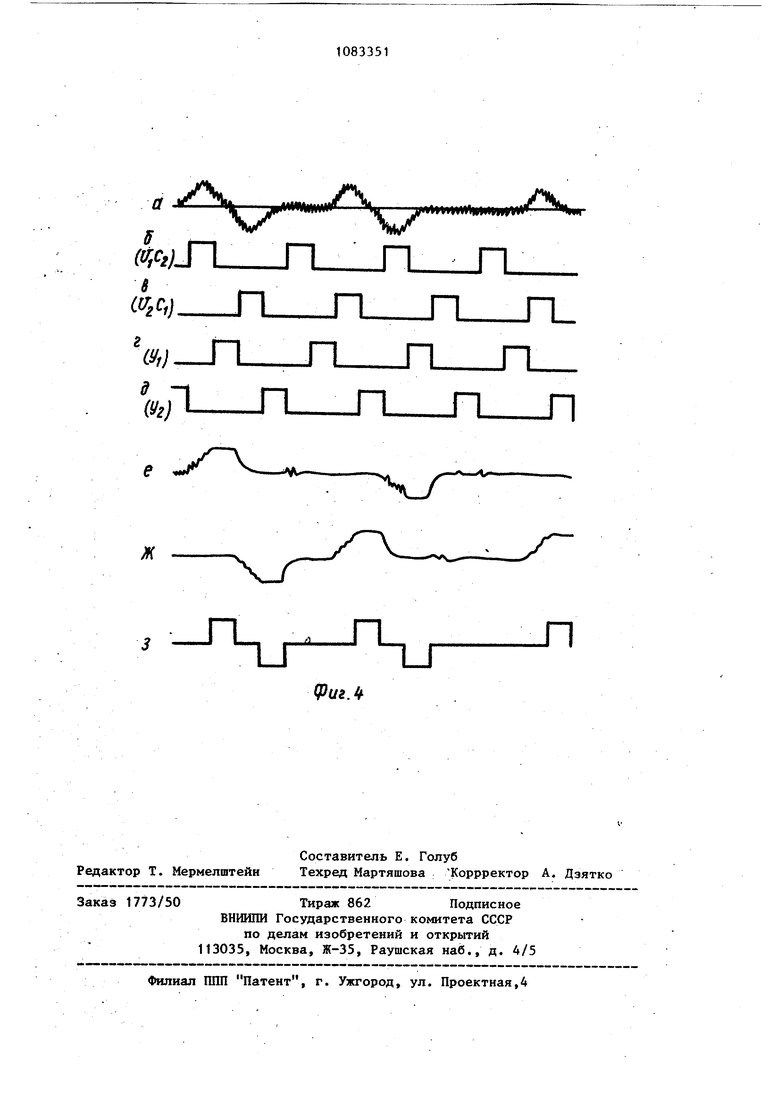

Изобретение относится к технике передачи цифровых сигналов по кабел ным линиям связи и может использоваться для ретрансляции видеоимпуль сов многоканальных систем передачи с импульсно-кодовой или дельта-моду цией. Известен регенератор цифрового сигнала, использующий метод однократного отсчета и содержащий перемножитель, интегратор, блок решения и приемник С1 Однако помехоустойчивость данного регенератора невысока, особенно при импульсном характере помехи. Наиболее близким к предлагаемому является регенератор цифрового сигнала, содержащий усилитель, первый вход которого соединен с объединенными входами блока синхронизации и первого и второго каналов регенерации, каждьй из которых состоит из интегратора, причем второй выход усилителя через корректор соединен с первым входом усилителя,второ вход которого является входом реген ратора, выходной сумматор, выход ко торого является выходом регенерато.тра 2. Однако известный регенератор име низкую помехозащищенность. Цель изобретения - повьшение помехозащищенности. Поставленная цель достигается тем, что в регенератор цифрового си нала, содержащий усилитель, первый выход которого соединен с объединенными входами блока синхронизации и первого и второго каналов регенерац1}и, каждый из которых состоит из интегратора, причем второй выход усилителя через корректор соединен с первым входом усилителя, второй вход которого является входом регенератора, выходной сумматор, выход которого является выходом регенератора, введены формирователь порогового напряжения, а в каждый из каналов регенерации введены три ключа выпрямитель и компаратор, при эФом сигнальные входы первых ключей соединены с входами каналов регенераци а выходы через интеграторы соединен с объединенными сигнальными входами второго и третьего ключей, причем выход второго ключа соединен с объе диненными входами выпрямителя и компаратора, выходы которых соедине соответственно с входами формирователя порогового напряжения и с входами выходного сумматора, причем выход формирователя порогового напряжения соединен с вторьцуш входами компйраторов, а управляющие входы всех ключей соединены с соответствующими выходами блока синхронизации. На фиг.1 представлена структурная электрическая схема предлагаемого регенератораJ на фиг.2 - компаратор, на фиг.З - фррмирователь порогового напряжения, на фиг.4 - зпюры напряжений. Регенератор цифрового сигнала содержит усилитель 1, корректор 2, первый 3 и второй А каналы регенерации, каждый из которых состоит из первого 5, второго 6 и третьего 7 ключей, интегратора 8, выпрямителя 9 и компаратора 10, блок 11 синхронизации, состоящий из выпрямителя. 12, двух ключей 13 и 14, двух усреднителей 15 и 16, вычитающего элемента 17, накопителя 18, управляемого генератора 19, формирователя 20 импульсов, формирователь 21 порогового напряжения и выходной сумматор 22. Компаратор (фиг.2) состоит из двух элементов сравнения 23 и 24, инвертора 25 и сумматора 26. Формирователь порогового напряжения (фиг.З) содержит сумматор 27, разделительный диод 28, интегрирующую цепь 29, повторитель 30 и выходной делитель 31. Регенератор цифрового сигнала работает следующим образом. После усиления усилителем 1 и коррекции корректором 2 цифровой линейный сигнал с чередованием полярности импульсов (ЧПИ) (фиг.4о() поступает в каналы 3 и 4 регенерации. В интервалы времени, определяемые положительными импульсами последовательностей (фиг,4б, б), поочередно замыкаются первые ключи 5 первого 3 1и второго 4 каналов регенерации. образом, за время, равное половине длительности посылки, происходит накопление энергии принимаемого импульса в интеграторах 8. Пока идет накопление энергии, например, нечетной посылки принимаемого сигнала в первом канале 3 регенерации, этим же управляющим импульсом замыкается третий ключ 7 во втором канале 4 регенерации. При этом интегратор 8 второго канала 4 регенерации разряжается для подготовки к интегрирова3, 1083

нию следующей, например, читпой но- . сьтки сигнала. Во время четной посылки управляющим импульсом замкнут первый ключ 5 второго канала 4 регенерации и одновременно третий ключ j 7 первого канала 3 регенерации. В интервалы времени между импульсами интегрирования компараторы 10 с помощью вторых ключей 6 производят принятые решения о значении переда1шого ю символа. Для этого поочередно в каждом из каналов 3 и 4 регенерации после окончания процесса накопления энергии посыпки управляющими импульсами (фиг.4г,д) замьжаются вторые 15 ключи 6, и результат интегрирования посыпки попадает на первый вход компаратора 10, на второй вход которого поступает пороговый уровень с выхода формирователя 21. Компара- 20 тор 10 сравнивает напряжение на выходе интегратора 8 с порогом, равным половине среднего значения ин- j теграпов от единичных (токовых посылок . Так как компаратор двухзнач- 25 ный, то значения получаемьрс символов могут быть +1, О, -1, что является результатом работы обоих элементов 23 и 24 сравнения, инвертора 25 и сумматора 26 в зависимости от вели- зо чины и знака напряжения на выходе интегратора 8 во время учета. Напряжения на выходах интеграторов 8 первого 3 и второго 4 каналов регенерации (фиг.) зависят в основн от времени интегрирования. После принятия решения в компараторах 10 сформированные импульсы цифрового сигнала каждого из каналов регенерации суммируются выходным сумматором 40 22 и на выход регенератора подается восстановленный и отфильтрованный от помех методом накоплени-я цифровой сигнал (фиг.43).

Одновременно с процессом учета каждой посыпки цифрового сигнала через выпрямитель 9 напряжение, соотт ветствующеё интегралу токовой посылки, поступает -из каждого канала регенерации на вход формирователя 2150 порогового напряжения, где усредняется сумматором 27 и через разделительный диод 28 подается на интегрирующую цепь 29, в которой запоминается, а часть этого напряжения (в 55 деальном случае половина) поступает с выхода повторителя 30 и выходного елителя 31 на вторые входы компара1514

торов 10 обоих каналов 3 и 4 регенерации .

Для правильного расположения интегралов интегрирования относително посыпок принимаемого сигнала следует определять границы этих посьио в принимаемом цифровом сигнале с помощью блока 11 синхронизации.

Рассмотрим особенности и работу блока 11 синхронизации.

После выпрямления выпрямителем 12 (фиг.1) принимаемый цифровой сигнал через ключи 13 и 14 подается в усреднители 15 и 16. Основные элементы блока 11 синхронизации ключи 13 и 14, усреднители 15 и 16, вычитающий элемент 17, накопитель 18, управляемый генератор 19 и формрователь 20 импульсов управления образуют замкнутую систему- фазовой автоподстройки частоты по рабочему цифровому сигналу. При этом вся система автоподстройки стремится расположить начальную фазу меандров относительно импульсов управления так, чтобы через усреднители 15 и }6 и вычитающий элемент 17 в накопитель 18 попадал нулевой ток. Частота и фаза управляемого генератора 19 при таком условии остаются неизменными, а ключи 13 и 14 разрезают импульсы входного сигнала в среднем на равные половинки. Медленные изменения фазы тактовых импульсов во входном сигнале приводят к изменению соотношений между площадями соответствующих импульсов, в результате чего ток с выхода накопителя 18 приобретает некоторую величину и знак, чтобы изменением частоты управляемого генератора 19 изменить фазу меандров в нужную сторону и восстановить равновесие между пло1цадями соответствующих импульсов .

Из колебаний,вырабатьшаемых управляемым генератором 19, формирователь 20 импульсов управления блока 11 синхронизации образует меандры,а также меандры, из которых получаются управляющие импульсы, предназначенные для управления всеми ключами 5-7 обоих каналов 3 и 4 регенерации.

Предлагаемое устройство предназначено для фильтрации цифрового сигнала от помех в процессе ретрансляции (регенерации) в промежуточных пунктах кабельных многоканальных

систем передачи. По сравнению с прототипом оно позволяет повысить помехоустойчивость, особенно при воздействии импульсных (негладких), помех.

а также умельшить действие межсимвольных переходных помех, наиболее характерных в кабельных симметричных и коаксиальных парах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор цифрового сигнала | 1986 |

|

SU1387203A1 |

| Регенератор цифрового сигнала | 1983 |

|

SU1160547A1 |

| Регенератор цифрового сигнала | 1983 |

|

SU1251305A1 |

| Регенератор цифрового сигнала | 1988 |

|

SU1601755A1 |

| Видеорегенератор цифровых сигналов с автоматической регулировкой усиления | 1980 |

|

SU1067611A2 |

| Регенератор цифрового сигнала | 1986 |

|

SU1381728A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| Устройство контроля работоспособности видеорегенератора цифровой системы связи | 1981 |

|

SU1054912A2 |

| Дельта-декодер | 1986 |

|

SU1432779A1 |

| Адаптивный приемник сигналов минимальной частотной манипуляции | 1989 |

|

SU1835611A1 |

РЕГЕНЕРАТОР ЦИФРОВОГО СИГНАЛА, содержащий усилитель, первый выход которого соединен с объединенными входами блока синхронизации и первого и второго каналов регенерации,, каждый из которых состоит из интегратора, причем второй выход усилителя через корректор соединен . с первым входом усилителя, второй вход которого является входом регенератора, выходной сумматор, выход которого является выходом регенератора, отличаю.щийся тем, что, с целью повышения помехозащищенности, в него введены формирователь порогового напряжения, а в каждьш из каналов регенерации введены три ключа, вьшрямитель и компаратор, при этом сигнальные входы первых ключей соединены с входами каналов регенерации, а выходы через интеграторы соединены с объединенными сигнальными входами второг о и третьего ключей, причем выход второго ключа соединен с объединенными входами вьтрямителя и Компаратора,выходы которых соединены соответственно с входами формирователя порогового напряжения и с входами выходного сумматора, причем выход формирователя порогового напряжения соединен с вторыми входами компараторов, а управляющие входы всех ключей соединены с соответствующими выходами блока 00 синхронизации. со со ел

П

I Выход

It. |МШмш г

П П П

nTL

(У,).-n.

g -I

П n

&г) L

-A-

yv

/

n

n

n

л

vy

ж

y

(ригЛ

л

| t | |||

| Харкевич А.А | |||

| Борьба с помехаьш.М., Наука, 1965, с | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гуревич В.Э., Лопушнак Ю.Г., Рабинович Г.В | |||

| Импульснокодовая модуляция в многоканальной связи | |||

| М., Связь, 1973, с | |||

| Способ укрепления под покрышкой пневматической шины предохранительного слоя или манжеты | 1917 |

|

SU185A1 |

Авторы

Даты

1984-03-30—Публикация

1982-05-18—Подача