10

20

25

31548830

Изобретение относится к электро- технике и может быть использовано при управлении автономными инверторами напряжения, входящими в состав систем частотно-регулируемого электропривода .

Целью изобретения является линеаризация закона изменения первой гароники выходного напряжения трехфазого мостового инвертора в процессе вязанного регулирования частоты и еличины выходного сигнала.

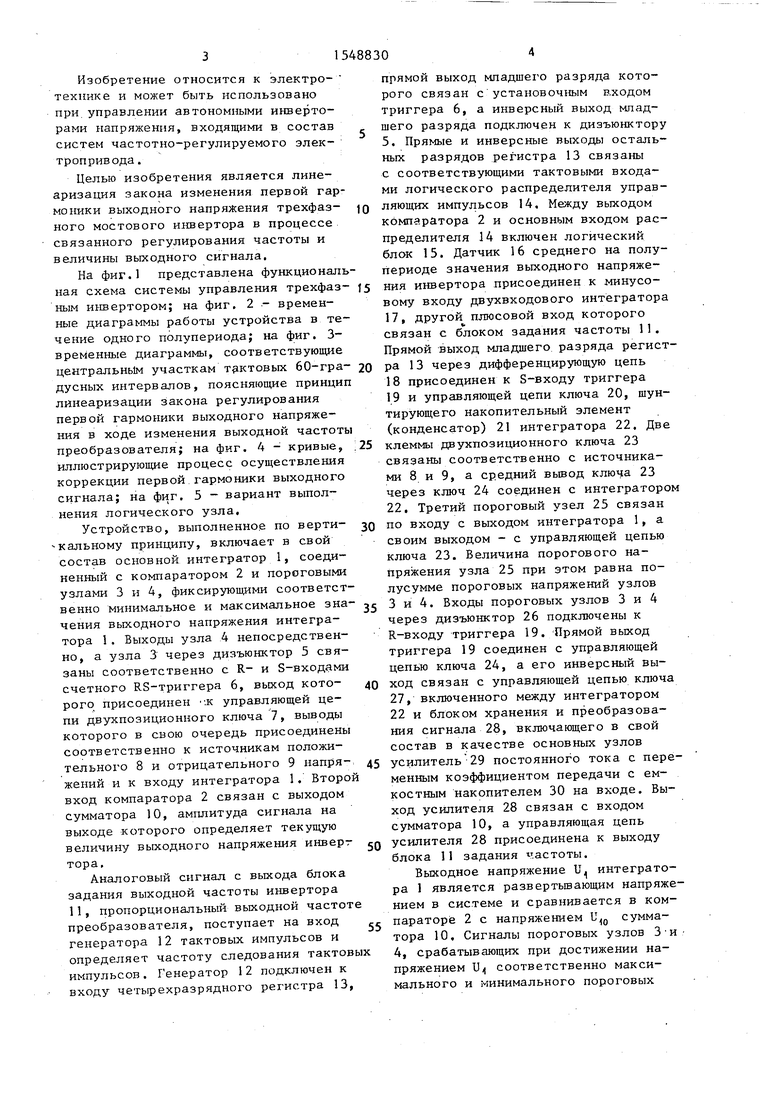

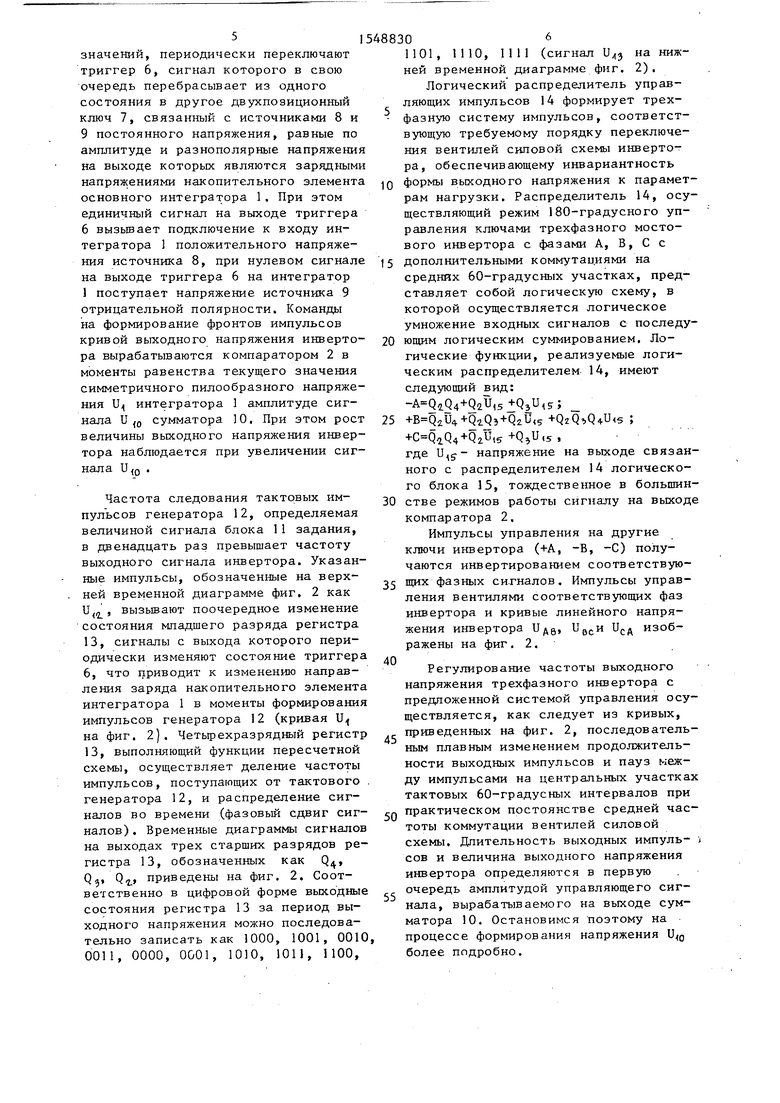

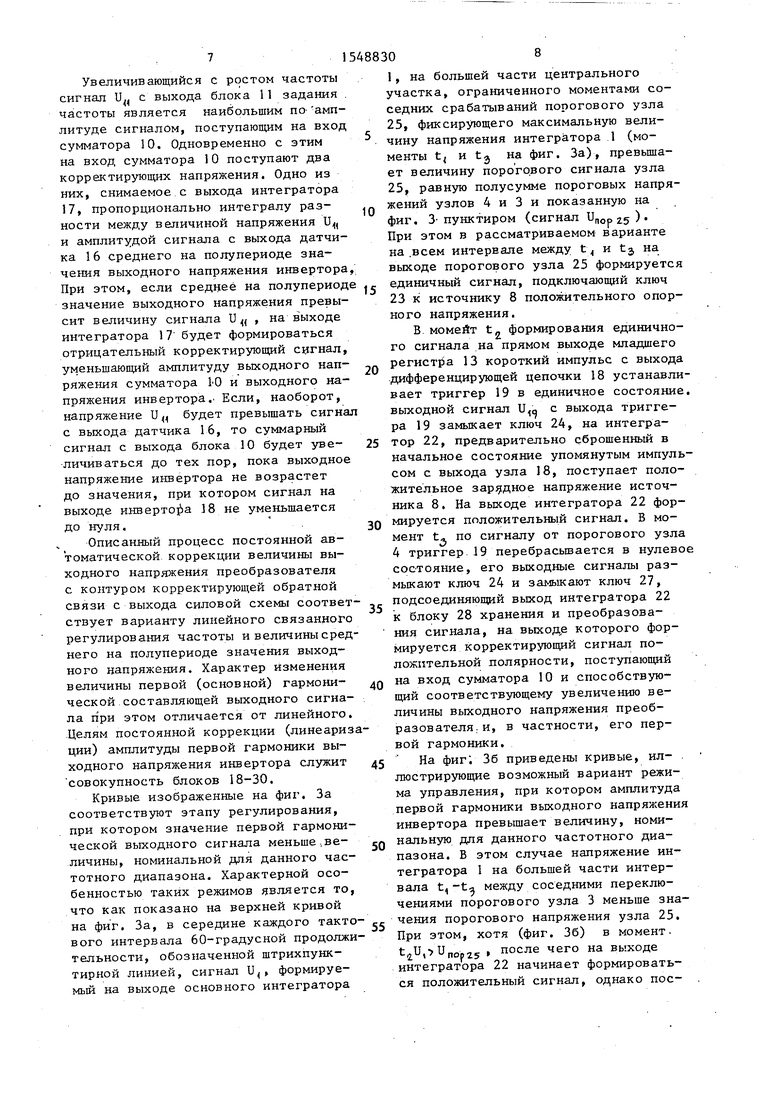

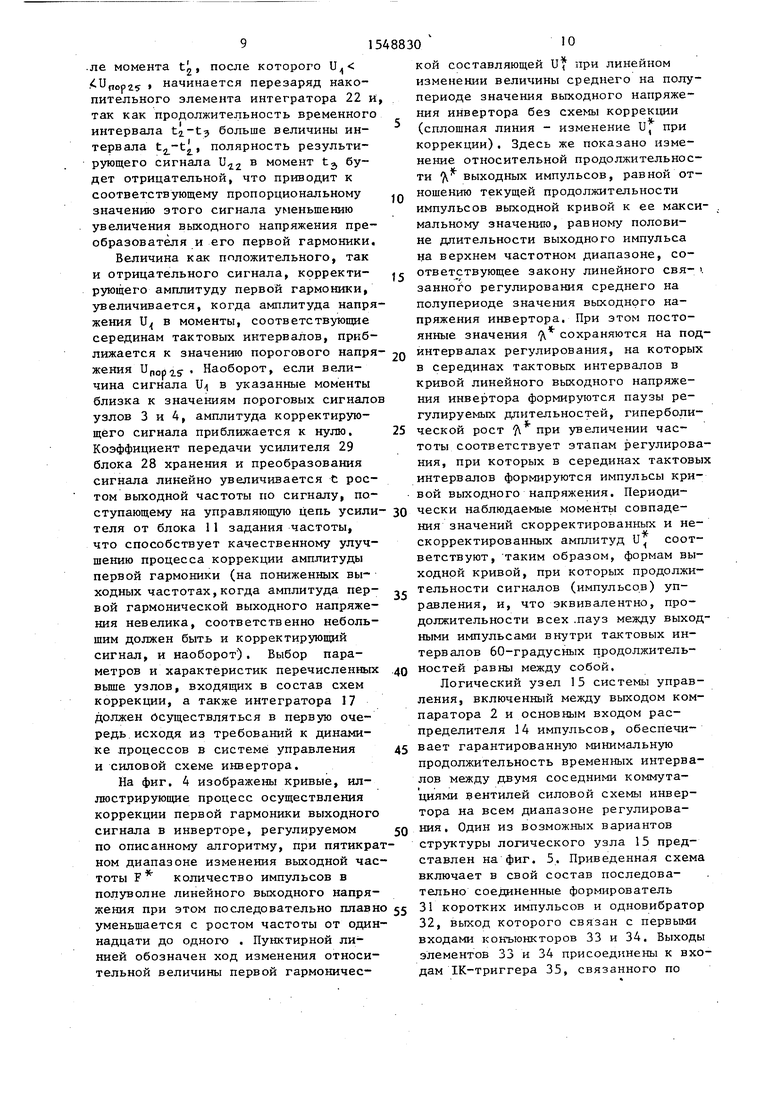

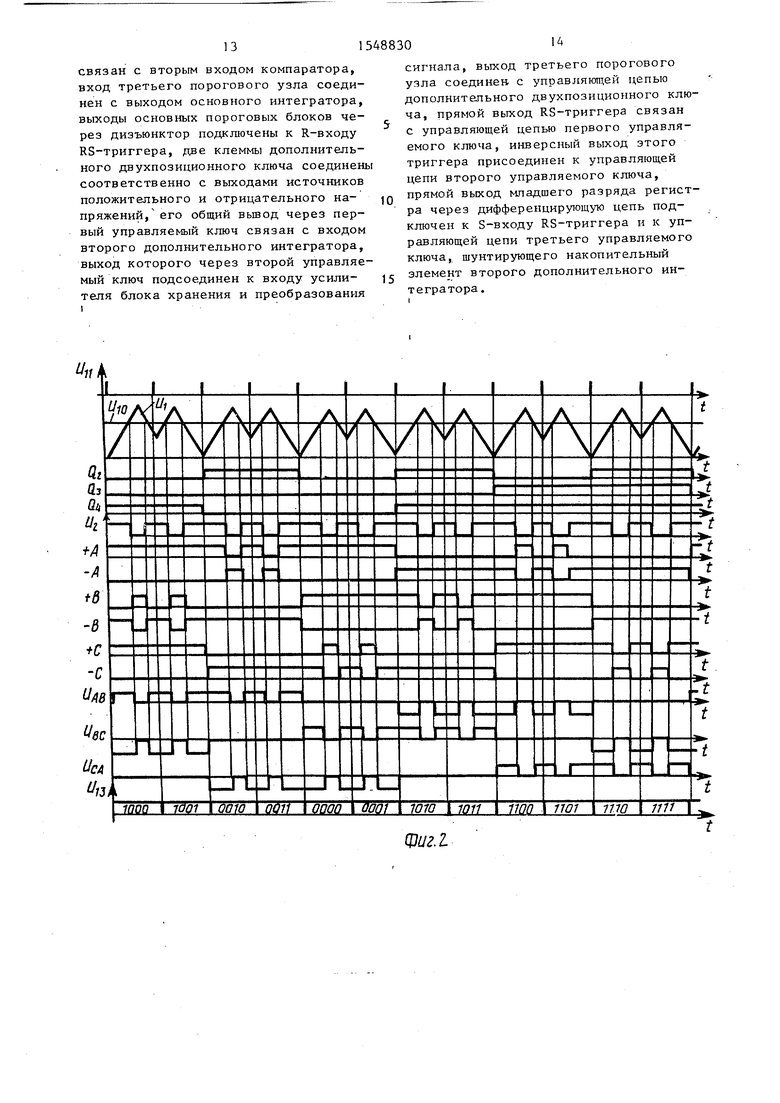

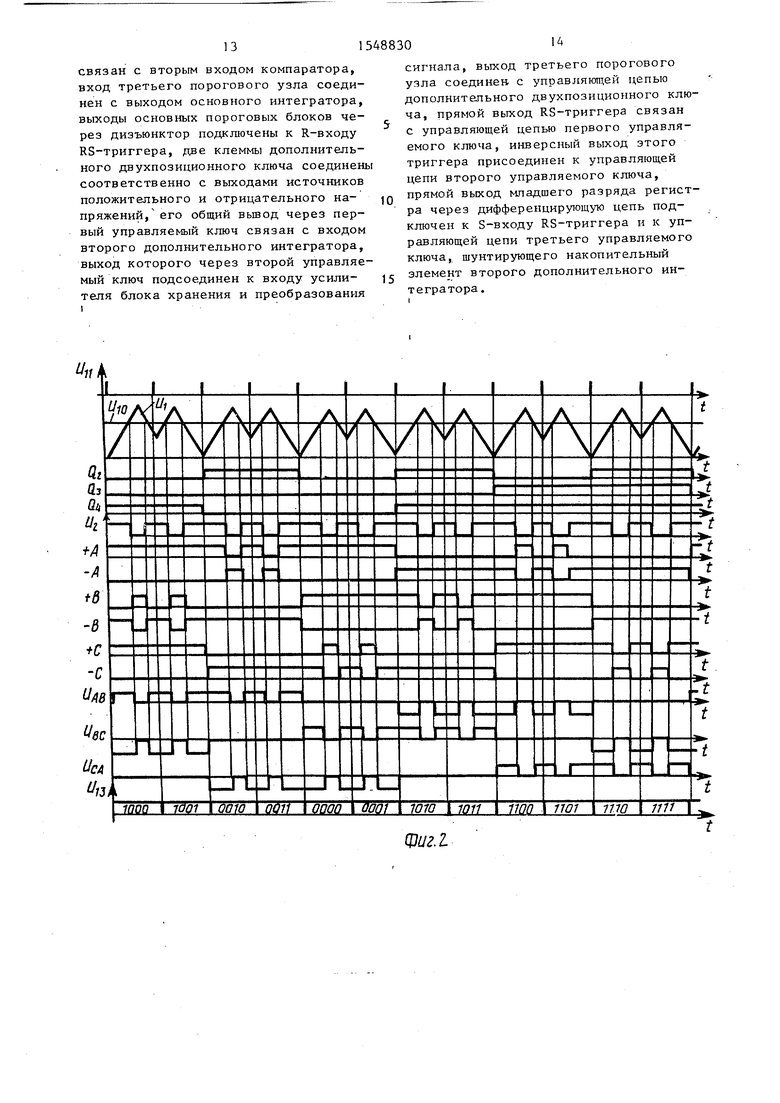

На фиг.1 представлена функциональная схема системы управления трехфаз- J5 ным инвертором; на фиг. 2 - временные диаграммы работы устройства в теение одного полупериода; на фиг. 3- ременные диаграммы, соответствующие центральным участкам тактовых 60-граусных интервалов, поясняющие принцип инеаризации закона регулирования ервой гармоники выходного напряжеия в ходе изменения выходной частоты реобразователя; на фиг. 4 - кривые, ллюстрирующие процесс осуществления оррекции первой гармоники выходного игнала; на фиг. 5 - вариант выполения логического узла.

Устройство, выполненное по верти- альному принципу, включает в свой остав основной интегратор 1, соединенный с компаратором 2 и пороговыми злами 3 и 4, фиксирующими соответстенно минимальное и максимальное знаения выходного напряжения интегратора 1, Выходы узла 4 непосредственно, а узла 3 через дизъюнктор 5 связаны соответственно с R- и S-входами счетного RS-триггера 6, выход которого присоединен к управляющей цепи двухпозиционного ключа 7, выводы оторого в свою очередь присоединены соответственно к источникам положительного 8 и отрицательного 9 напряжений и к входу интегратора 1. Второй вход компаратора 2 связан с выходом сумматора 10, амплитуда сигнала на выходе которого определяет текущую величину выходного напряжения инверг тора.

Аналоговый сигнал с выхода блока задания выходной частоты инвертора 11, пропорциональный выходной частоте преобразователя, поступает на вход генератора 12 тактовых импульсов и определяет частоту следования тактовых импульсов. Генератор 12 подключен к входу четырехразрядного регистра 13,

30

35

40

45

50

55

п ро тр ше 5 ны с ми ля ко пр бл пе ни во 17 св Пр ра

18

19 ти (к кл св ми че 22 по св кл пр лу

3 че Rтрце хо 27 22 ни со ус ме ко хо су ус бл

ра ни па то 4, пр ма

0

0

5

5

0

5

0

5

0

5

прямой выход младшего разряда которого связан с установочным входом триггера 6, а инверсный выход младшего разряда подключен к дизъюнктору 5. Прямые и инверсные выходы остальных разрядов регистра 13 связаны с соответствующими тактовыми входами логического распределителя управляющих импульсов 14. Между выходом компаратора 2 и основным входом распределителя 14 включен логический блок 15. Датчик 16 среднего на полупериоде значения выходного напряжения инвертора присоединен к минусовому входу двухвходового интегратора 17, другой плюсовой вход которого связан с блоком задания частоты 11. Прямой выход младшего разряда регистра 13 через дифференцирующую цепь

18присоединен к S-входу триггера

19и управляющей цепи ключа 20, шунтирующего накопительный элемент (конденсатор) 21 интегратора 22. Две клеммы двухпозиционного ключа 23 связаны соответственно с источниками 8 и 9, а средний вывод ключа 23 через ключ 24 соединен с интегратором 22, Третий пороговый узел 25 связан по входу с выходом интегратора 1, а своим выходом - с управляющей цепью ключа 23. Величина порогового напряжения узла 25 при этом равна полусумме пороговых напряжений узлов

3 и 4. Входы пороговых узлов 3 и 4 через дизъюнктор 26 подключены к Rвходу триггера 19. Прямой выход триггера 19 соединен с управляющей цепью ключа 24, а его инверсный выход связан с управляющей цепью ключа 27, включенного между интегратором 22 и блоком хранения и преобразования сигнала 28, включающего в свой состав в качестве основных узлов усилитель 29 постоянного тока с переменным коэффициентом передачи с емкостным накопителем 30 на входе. Выход усилителя 28 связан с входом сумматора 10, а управляющая цепь усилителя 28 присоединена к выходу блока 11 задания астоты.

Выходное напряжение U,, интегратора 1 является развертывающим напряжением в системе и сравнивается в компараторе 2 с напряжением U10 сумматора 10, Сигналы пороговых узлов 3 и 4, срабатывающих при достижении напряжением U соответственно максимального и минимального пороговых

значении, периодически переключают триггер 6, сигнал которого в свою очередь перебрасывает из одного состояния в другое двухпозиционный ключ 7, связанный с источниками 8 и 9 постоянного напряжения, равные по амплитуде и разнополярные напряжения на выходе которых являются зарядными напряжениями накопительного элемента основного интегратора 1. При этом единичный сигнал на выходе триггера 6 вызывает подключение к входу интегратора 1 положительного напряжения источника 8, при нулевом сигнале на выходе триггера 6 на интегратор 1 поступает напряжение источника 9 отрицательной полярности. Команды на формирование фронтов импульсов кривой выходного напряжения инвертора вырабатываются компаратором 2 в моменты равенства текущего значения симметричного пилообразного напряжения U,| интегратора 1 амплитуде сигнала U (0 сумматора 10. При этом рост величины выходного напряжения инвертора наблюдается при увеличении сигнала U

го

Частота следования тактовых импульсов генератора 12, определяемая величиной сигнала блока 11 задания, в двенадцать раз превышает частоту выходного сигнала инвертора. Указанные импульсы, обозначенные на верхней временной диаграмме фиг. 2 как U(i, вызывают поочередное изменение

состояния младшего разряда регистра 13, сигналы с выхода которого периодически изменяют состояние триггера 6, что приводит к изменению направления заряда накопительного элемента интегратора 1 в моменты формирования импульсов генератора 12 (кривая U на фиг. 2). Четырехразрядный регистр 13, выполняющий функции пересчетной схемы, осуществляет деление частоты импульсов, поступающих от тактового генератора 12, и распределение сигналов во времени (фазовый сдвиг сигналов) . Временные диаграммы сигналов на выходах трех старших разрядов регистра 13, обозначенных как Q, Q, 0,г приведены на фиг. 2. Соответственно в цифровой форме выходные состояния регистра 13 за период выходного напряжения можно последовательно записать как 1000, 1001, 0010, ООП, 0000, ОС/01, 1010, 1011, 1100,

488306

1101, 1110, 1111 (сигнал и на нижней временной диаграмме фиг. 2).

Логический распределитель управляющих импульсов 14 формирует трехфазную систему импульсов, соответствующую требуемому порядку переключения вентилей силовой схемы инвертора, обеспечивающему инвариантность

Ю формы выходного напряжения к параметрам нагрузки. Распределитель 14, осуществляющий режим 180-градусного управления ключами трехфазного мостового инвертора с фазами А, В, С с

15 дополнительными коммутациями на

средних 60-градусных участках, представляет собой логическую схему, в которой осуществляется логическое умножение входных сигналов с последу20 ющим логическим суммированием. Логические функции, реализуемые логическим распределителем 14, имеют следующий вид: -А 5 4+р2и,5+Рз,и,г;

25 +B QaU4+Q1Q3+Q2U 5+Q2Q, ;

+с дад4+дги,5 +Q,u,5,

где UAff- напряжение на выходе связанного с распределителем 14 логического блока 15, тождественное в болыпин30 стве режимов работы сигналу на выходе компаратора 2,

Импульсы управления на другие ключи инвертора (+А, -В, -С) получаются инвертированием соответствую35 щих фазных сигналов. Импульсы управления вентилями соответствующих фаз инвертора и кривые линейного напряжения инвертора иде, ражены на фиг. 2.

Регулирование частоты выходного напряжения трехфазного инвертора с предложенной системой управления осуществляется, как следует из кривых, приведенных на фиг. 2, последовательным плавным изменением продолжительности выходных импульсов и пауз между импульсами на центральных участках тактовых 60-градусных интервалов при практическом постоянстве средней частоты коммутации вентилей силовой схемы. Длительность выходных импуль- сов и величина выходного напряжения инвертора определяются в первую очередь амплитудой управляющего сигнала, вырабатываемого на выходе сумматора 10. Остановимся поэтому на процессе формирования напряжения более подробно.

Ув еличив ающийс я сигнал U,, с частоты

с ростом частоты выхода блока 11 задания является наибольшим по амп

литуде сигналом, поступающим на вхо сумматора 10. Одновременно с этим на вход сумматора 10 поступают два корректирующих напряжения. Одно из них, снимаемое с выхода интегратора 17, пропорционально интегралу разности между величиной напряжения U,,, и амплитудой сигнала с выхода датчика 16 среднего на полупериоде значения выходного напряжения инвертор При этом, если среднее на полуперио значение выходного напряжения превысит величину сигнала U ( , на выходе интегратора 17 будет формироваться отрицательный корректирующий сигнал уменьшающий амплитуду выходного напряжения сумматора 10 и выходного напряжения инвертора. Если, наоборот, напряжение U ц будет превышать сигн с выхода датчика 16, то суммарный сигнал с выхода блока 10 будет увеличиваться до тех пор, пока выходно напряжение инвертора не возрастет до значения, при котором сигнал на выходе инвертора 18 не уменьшается до нуля.

Описанный процесс постоянной автоматической коррекции величины выходного напряжения преобразователя с контуром корректирующей обратной связи с выхода силовой схемы соотвествует варианту линейного связанног регулирования частоты и величины сренего на полупериоде значения выходного напряжения. Характер изменения величины первой (основной) гармонической составляющей выходного сигнала при этом отличается от линейного Целям постоянной коррекции (линеариции) амплитуды первой гармоники выходного напряжения инвертора служит совокупность блоков 18-30.

Кривые изображенные на фиг. За соответствуют этапу регулирования, при котором значение первой гармонической выходного сигнала меньше величины, номинальной для данного частотного диапазона. Характерной особенностью таких режимов является то что как показано на верхней кривой на фиг. За, в середине каждого такт вого интервала 60-градусной продолжтельности, обозначенной штрихпунк

тирной линией, сигнал формируемый на выходе основного интегратора

, е л

15488308

1, на большей части центрального участка, ограниченного моментами соседних срабатываний порогового узла 25, фиксирующего максимальную величину напряжения интегратора 1 (мо0

5

0

5

0

с чения

5

0

5

0

менты tj и tj на фиг. За), превышает величину порогового сигнала узла 25, равную полусумме пороговых напряжений узлов 4 и 3 и показанную на фиг. 3 пунктиром (сигнал Unopг5 ) . При этом в рассматриваемом варианте на всем интервале между t, и t3 на выходе порогового узла 25 формируется единичный сигнал, подключающий ключ 23 к источнику 8 положительного опорного напряжения.

В момейт t формирования единичного сигнала на прямом выходе младшего регистра 13 короткий импульс с выхода дифференцирующей цепочки 18 устанавливает триггер 19 в единичное состояние, выходной сигнал с выхода триггера 19 замыкает ключ 24, на интегратор 22, предварительно сброшенный в начальное состояние упомянутым импульсом с выхода узла 18, поступает положительное зарядное напряжение источника 8. На выходе интегратора 22 формируется положительный сигнал. В момент t- по сигналу от порогового узла 4 триггер 19 перебрасывается в нулевое состояние, его выходные сигналы размыкают ключ 24 и замыкают ключ 27, подсоединяющий выход интегратора 22 к блоку 28 хранения и преобразования сигнала, на выходе которого формируется корректирующий сигнал положительной полярности, поступающий на вход сумматора 10 и способствующий соответствующему увеличению величины выходного напряжения преобразователя и, в частности, его первой гармоники.

На фиг. 36 приведены кривые, иллюстрирующие возможный вариант режима управления, при котором амплитуда первой гармоники выходного напряжения инвертора превышает величину, номинальную для данного частотного диапазона. В этом случае напряжение интегратора 1 на большей части интервала t4 -t-я между соседними переключениями порогового узла 3 меньше знапорогового напряжения узла 25. При этом, хотя (фиг. 36) в момент после чего на выходе

Чи« Т1ПОрг5

интегратора 22 начинает формироваться положительный сигнал, однако после момента tg , после которого UJ| и„0р25 , начинается перезаряд накопительного элемента интегратора 22 и так как продолжительность временного интервала tj-tj больше величины интервала , полярность результирующего сигнала в момент t3 будет отрицательной, что приводит к соответствующему пропорциональному значению этого сигнала уменьшению увеличения выходного напряжения преобразователя и его первой гармоники.

Величина как положительного, так и отрицательного сигнала, корректи- рующего амплитуду первой гармоники, увеличивается, когда амплитуда напряжения J в моменты, соответствующие серединам тактовых интервалов, приближается к значению порогового напря жения Unopls- , Наоборот, если величина сигнала U в указанные моменты близка к значениям пороговых сигнало узлов 3 и 4, амплитуда корректирующего сигнала приближается к нулю. Коэффициент передачи усилителя 29 блока 28 хранения и преобразования сигнала линейно увеличивается с ростом выходной частоты по сигналу, поступающему на управляющую цепь усили теля от блока 11 задания частоты, что способствует качественному улучшению процесса коррекции амплитуды первой гармоники (на пониженных выходных частотах, когда амплитуда пер- вой гармонической выходного напряжения невелика, соответственно небольшим должен быть и корректирующий сигнал, и наоборот). Выбор параметров и характеристик перечисленных выше узлов, входящих в состав схем коррекции, а также интегратора 17 должен осуществляться в первую очередь исходя из требований к динамике процессов в системе управления и силовой схеме инвертора.

На фиг. 4 изображены кривые, иллюстрирующие процесс осуществления коррекции первой гармоники выходного сигнала в инверторе, регулируемом по описанному алгоритму, при пятикратном диапазоне изменения выходной частоты F количество импульсов в полуволне линейного выходного напряжения при этом последовательно плавно уменьшается с ростом частоты от одиннадцати до одного . Пунктирной линией обозначен ход изменения относительной величины первой гармонической составляющей U при линейном изменении величины среднего на полупериоде значения выходного напряжения инвертора без схемы коррекции (сплошная линия - изменение U при коррекции). Здесь же показано изменение относительной продолжительности выходных импульсов, равной отношению текущей продолжительности импульсов выходной кривой к ее максимальному значению, равному половине длительности выходного импульса на верхнем частотном диапазоне, соответствующее закону линейного свя- i занного регулирования среднего на полупериоде значения выходного напряжения инвертора. При этом постоянные значения ft сохраняются на под интервалах регулирования, на которых в серединах тактовых интервалов в кривой линейного выходного напряжения инвертора формируются паузы регулируемых длительностей, гиперболической рост ft при увеличении частоты соответствует этапам регулирования, при которых в серединах тактовы интервалов формируются импульсы кривой выходного напряжения. Периодически наблюдаемые моменты совпадения значений скорректированных и нескорректированных амплитуд U ,| соответствуют, таким образом, формам выходной кривой, при которых продолжительности сигналов (импульсов) управления, и, что эквивалентно, продолжительности всех пауз между выходными импульсами внутри тактовых интервалов 60-градусных продолжитель- ностей равны между собой.

Логический узел 15 системы управления, включенный между выходом компаратора 2 и основным входом распределителя 14 импульсов, обеспечивает гарантированную минимальную продолжительность временных интервалов между двумя соседними коммутациями вентилей силовой схемы инвертора на всем диапазоне регулирования. Один из возможных вариантов структуры логического узла 15 представлен на фиг. 5. Приведенная схема включает в свой состав последовательно соединенные формирователь 31 коротких импульсов и одновибратор 32, выход которого связан с первыми входами кокъюнкторов 33 и 34. Выходы элементов 33 и 34 присоединены к входам IK-триггера 35, связанного по

Н

выходу с распределителем 14. На второй вход элемента 33 поступает сигн непосредственно с выхода компаратор 2, а поступающий на второй вход кон юнктора 34 этот же сигнал предварительно инвертируется логическим инвертором 36. Величина минимально допустимого временного интервала межд коммутациями при этом определяется длительностью выходных импульсов одновибратора 13.

Таким образом, введение в состав системы управления инвертором небольшого числа дополнительных несложных узлов позволяет обеспечить линейный характер изменения первой гармоники кривой выходного напряжения трехфазного инвертора в процесс регулирования выходной частоты. В частности, датчик среднего на полупериоде значения выходного напряжения системы может быть построен на базе выпрямительных мостовых схем с сглаживающим пульсации конденсаторо и с согласующим усилителем на выход Плавное квазилинейное изменение основной гармоники напряжения на выходе инвертора, в свою очередь, спосоствует улучшению энергетических и днамических характеристик асинхронного электродвигателя, питающегося от инвертора, работающего в режиме постоянства отношения величины напржения к частоте (в режиме постоянства момента применительно к частотно-регулируемому электроприводу переменного тока) .

Формула изобретения

Устройство для управления регулируемым мостовым инвертором, содержащее интегратор, выход которого связан с входами двух пороговых узлов и с первым входом компаратора, выход первого порогового узла соединен с R-входом счетного триггера, выход второго порогового узла связан с S-входом счетного триггера через первый вход дизъюнктора, выход триггера подключен к управляющей цепи двухпозиционного ключа, две клеммы которого связаны с источниками положительного и отрицательного постоянного напряжения, а общий вывод двупозиционного ключа подсоединен к входу интегратора, блок задания частоты, связанный с генератором такто0

5

8830

12

вых импульсов, соединенным с регистром, прямой выход младшего разряда которого связан с установочным входом счетного триггера, инверсный выход младшего разряда регистра присоединен к второму входу дизъюнктора, выходы старших разрядов регистра подключены к соответствующим тактовым входам распределителя управляющих импульсов, основной вход которого через логический блок связан с выходом компаратора, при этом логический блок состоит из последовательно соединенных формирователя коротких импульсов и одновибратора, выход которого связан с первыми входами двух конъюнкторов выходы которых подключены к входам IK-триггера, вход формирователя коротких импульсов и второй вход первого конъюнктора объединены между собой и через логический инвертор связаны с вторым входом второго конъюнктора, о тличаю- щ е е с я тем, что, с целью линеаризации закона изменения первой гармоники выходного напряжения трехфазного инвертора в процессе связанного регулирования частоты и величи- 0 ны выходного сигнала, оно снабжено

0

5

5

0

5

0

5

сумматором, датчиком среднего на полупериоде значения выходного напряжения инвертора, третьим пороговым узлом, дополнительным дизъюнктором, тремя управляемыми ключами, двумя интеграторами, дополнительным двухпо- зиционным ключом, дифференцирующей цепью, RS-триггером и блоком хранения и преобразования сигнала, включающим усилитель постоянного тока с емкостным элементом на входе, причем регистр выполнен четырехразрядным, усилитель выполнен с управляемым коэффициентом передачи, его управляющая цепь связана с выходом блока задания частоты, первый дополнительный интегратор выполнен двухвходовым, его минусовый вход соединен с выходом датчика среднего на полупериоде значения выходного напряжения, плюсовой вход первого дополнительного интегратора связан с выходом блока задания частоты, подключенного также к первому входу сумматора, второй вход сумматора соединен с выходом первого дополнительного интегратора, трети;й вход сумматора подключен к выходу усилителя блока хранения и преобразования сигнала, а выход сумматора

связан с вторым входом компаратора, вход третьего порогового узла соединен с выходом основного интегратора, выходы основных пороговых блоков через дизъюнктор подключены к R-входу RS-триггера, две клеммы дополнительного двухпозиционного ключа соединен соответственно с выходами источников положительного и отрицательного напряжений/ его общий вывод через первый управляемый ключ связан с входом второго дополнительного интегратора, выход которого через второй управляемый ключ подсоединен к входу усилителя блока хранения и преобразования

5

сигнала, выход третьего порогового узла соединен с управляющей цепью дополнительного двухпозиционного ключа, прямой выход RS-триггера связан с управляющей цепью первого управляемого ключа, инверсный выход этого триггера присоединен к управляющей цепи второго управляемого ключа, прямой выход младшего разряда регистра через дифференцирующую цепь подключен к S-входу RS-триггера и к управляющей цепи третьего управляемого ключа, шунтирующего накопительный элемент второго дополнительного интегратора .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления инвертором с переменной выходной частотой | 1983 |

|

SU1107250A1 |

| Устройство для управления автономным инвертором напряжения со слежением | 1984 |

|

SU1229931A1 |

| Устройство для управления регулируемым мостовым инвертором напряжения | 1984 |

|

SU1239809A1 |

| Устройство для управления полумостовым инвертором напряжения | 1983 |

|

SU1104638A1 |

| Способ управления трехфазным регулируемым мостовым инвертором | 1988 |

|

SU1554094A2 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

| Устройство для управления трехфазным регулируемым инвертором | 1988 |

|

SU1534700A1 |

| Способ управления трехфазным вентильным преобразователем | 1990 |

|

SU1720132A1 |

| Устройство для управления однофазным инвертором напряжения | 1982 |

|

SU1062838A1 |

| Способ управления вентильным преобразователем с широтно-кодовым регулированием | 1990 |

|

SU1777219A1 |

Изобретение относится к электронике и может быть использовано для управления автономными трехфазными инверторами. Цель изобретения - линеаризация закона изменения первой гармоники выходного напряжения инвертора в процессе связанного регулирования частоты и величины выходного сигнала. Устройство содержит основной интегратор 1, напряжение на выходе которого, являющееся развертывающим сигналом, формируется при помощи пороговых узлов 3 и 4, триггера 6, двухпозиционного ключа 7 и источников 8 и 9 и сопоставляется в компараторе 2 с выходным напряжением сумматора 10, задающим величину выходного напряжения инвертора. Канал задания выходной частоты инвертора включает блок 11 задания частоты, связанный с генератором 12 тактовых импульсов, который присоединен к четырехразрядному регистру 13. Введение в состав устройства датчика 16 среднего на полупериоде значения выходного напряжения и интегратора 17 обеспечивает близкое к линейному изменение величины среднего на полупериоде значения выходного напряжения инвертора при регулировании частоты. Пороговый узел 25, дизъюнктор 26, триггер 19, дифференцирующая цепь 18, интегратор 22, блок 29 хранения и преобразования информации, ключи 20, 23, 24 и 27 на всем диапазоне регулирования осуществляют формирование корректирующего сигнала, пропорционального величине отклонения амплитуды первой гармоники выходного напряжения инвертора от номинального значения и изменяющего. 5 ил.

Л

/

/

V

Нес

1000

TOPI uaw poll оооо QQ01 того IQII

V

V

V

1WQ П01

7770

1W

Щиг.1

Редактор Н. Лазаренко

Составитель О. Парфенова

Техред Л.Олийнык Корректор О. Кравцова

Заказ 144

Тираж 496

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг.З

фиг. 5

Подписное

| Устройство для управления однофазным инвертором напряжения | 1982 |

|

SU1062838A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления регулируемым мостовым инвертором напряжения | 1984 |

|

SU1239809A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-03-07—Публикация

1988-02-01—Подача