Изобретение относится к контрольно-измерительной технике и может быть использовано в контрольно-измерительных приборах, системах автоматического контроля и регистрации.

Цель изобретения - повышение помехоустойчивости.

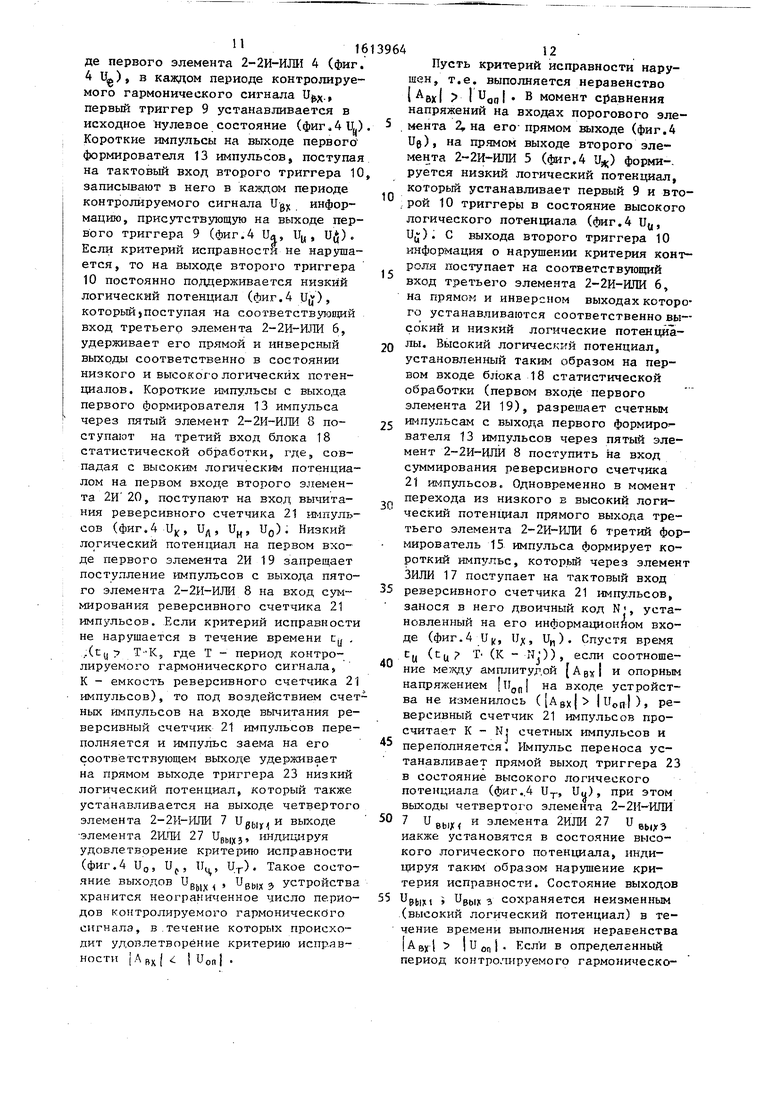

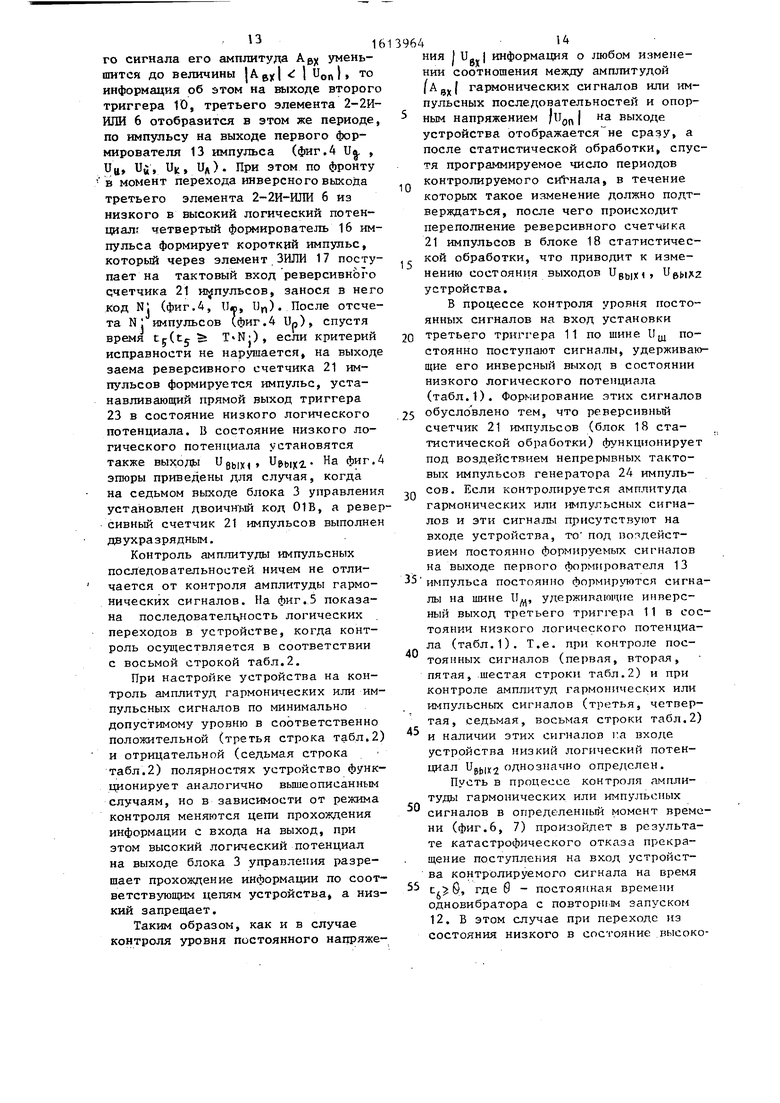

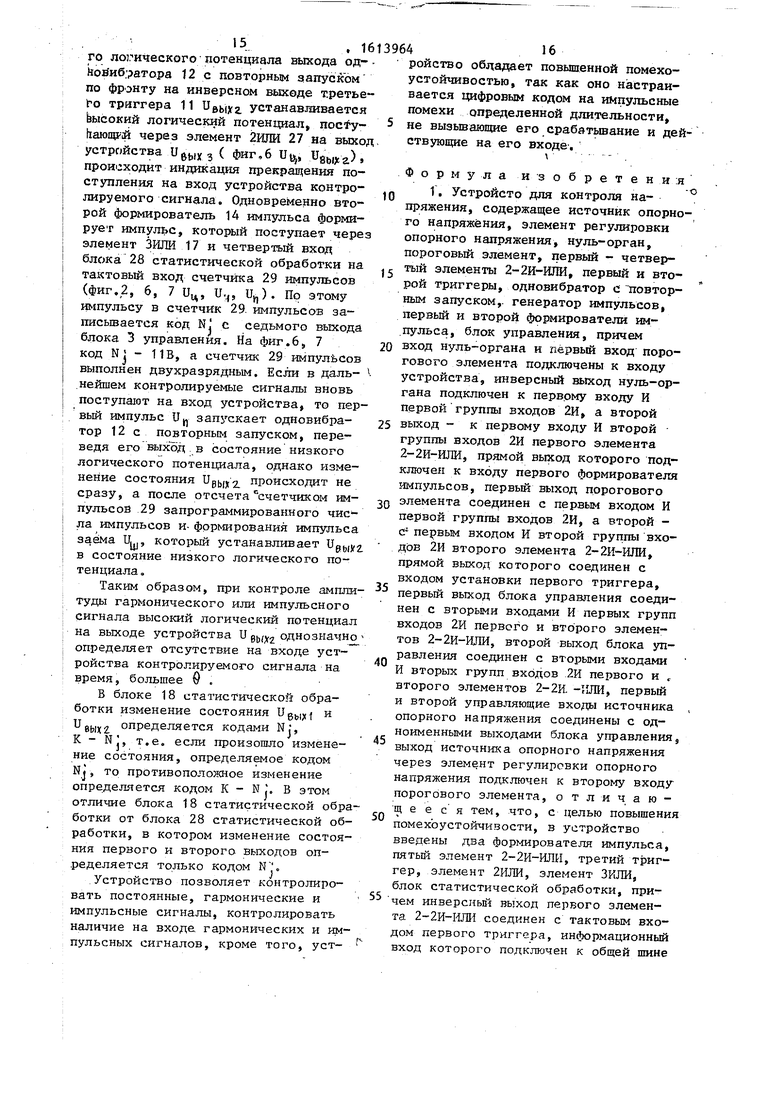

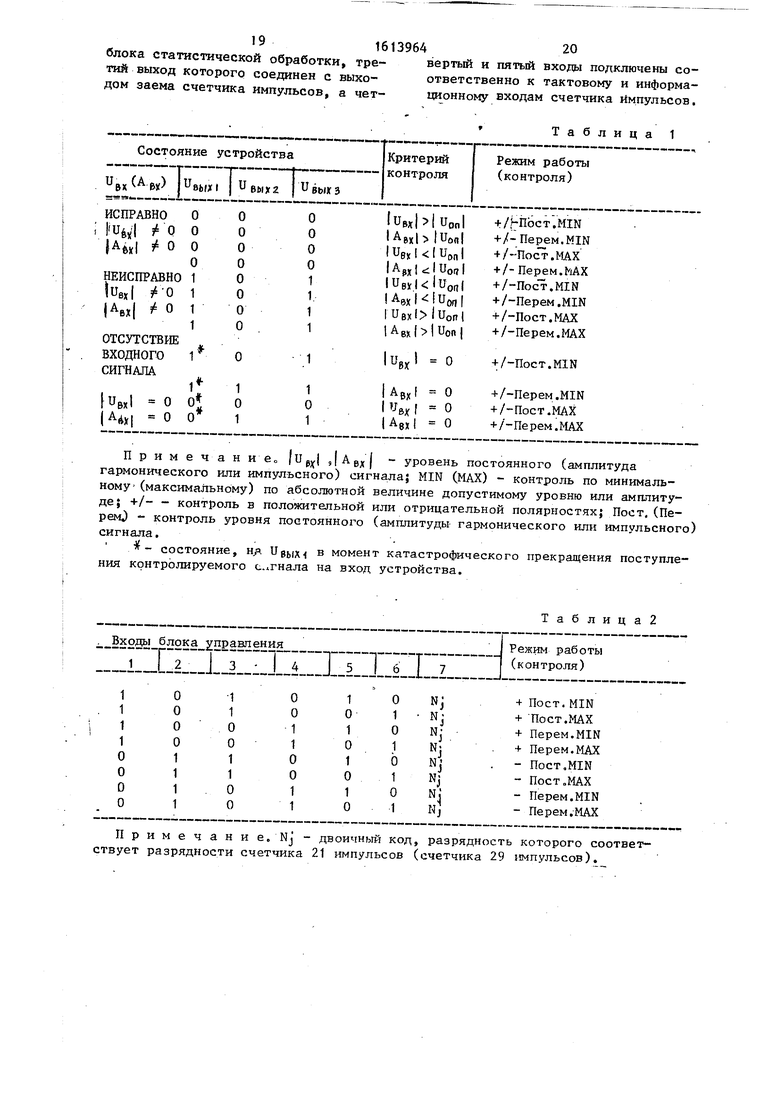

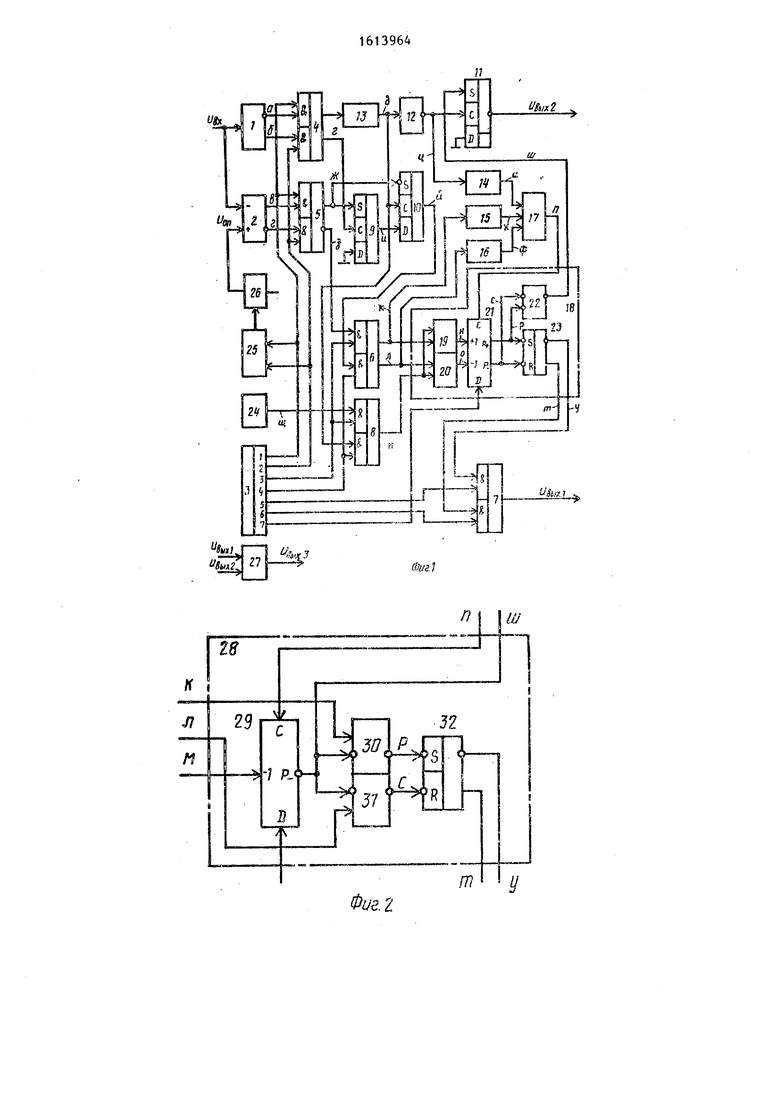

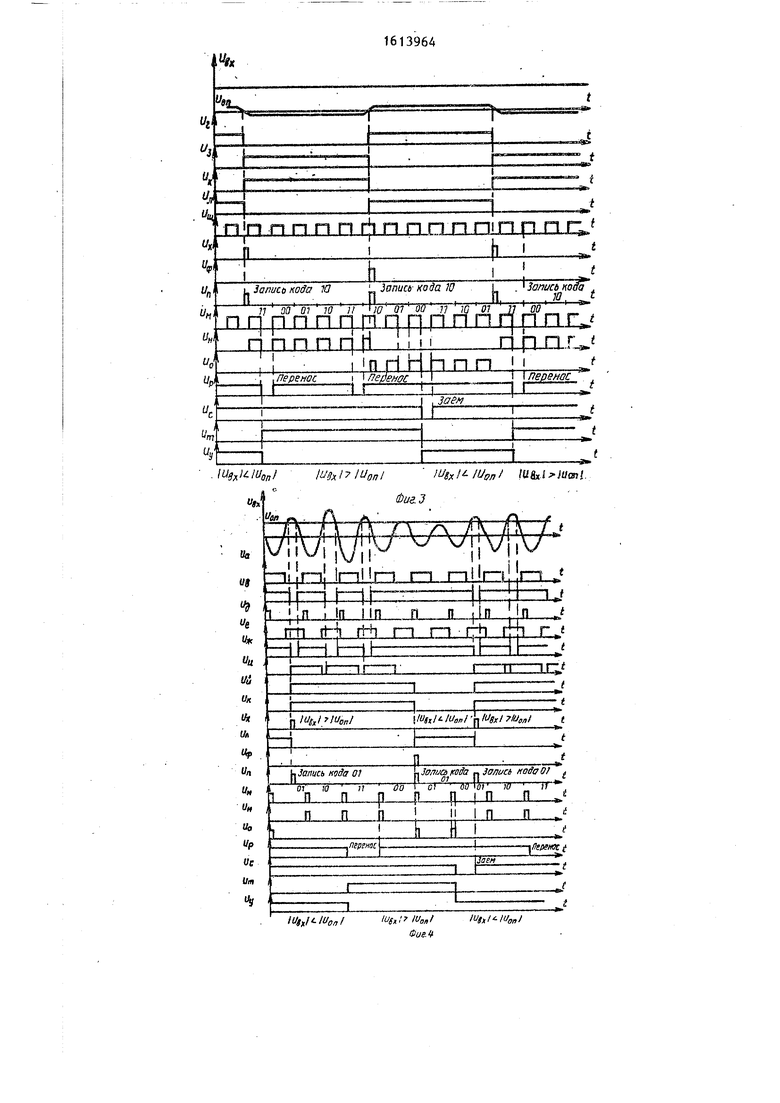

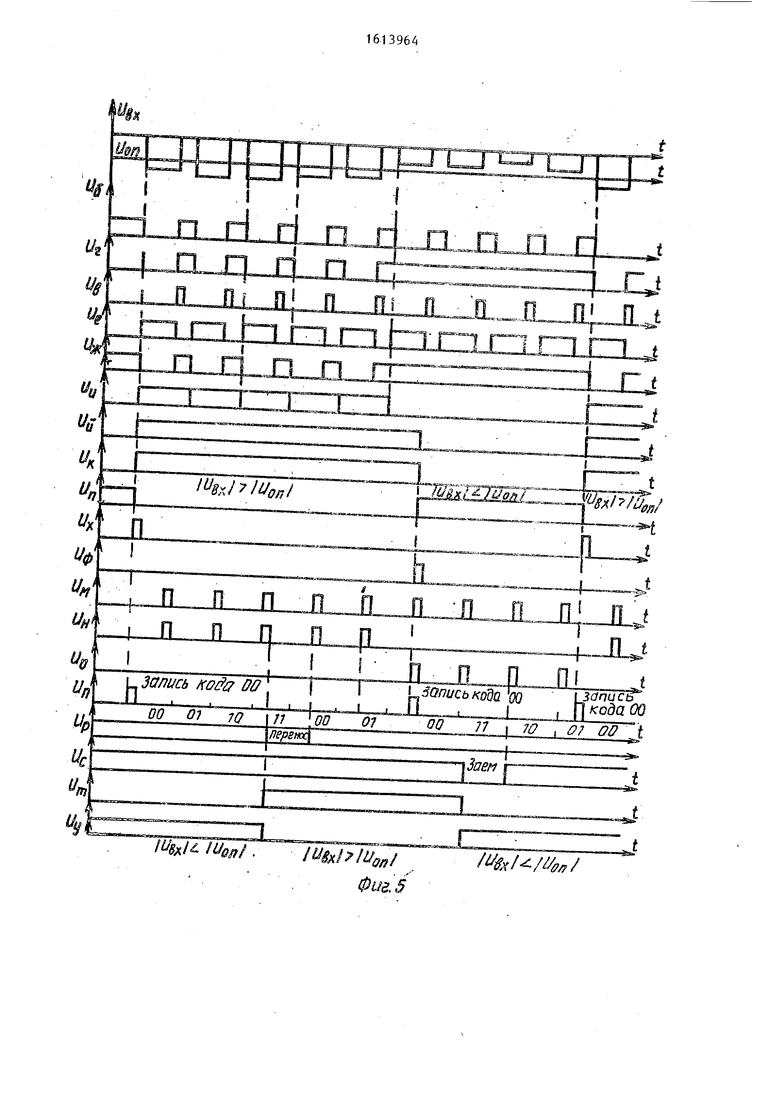

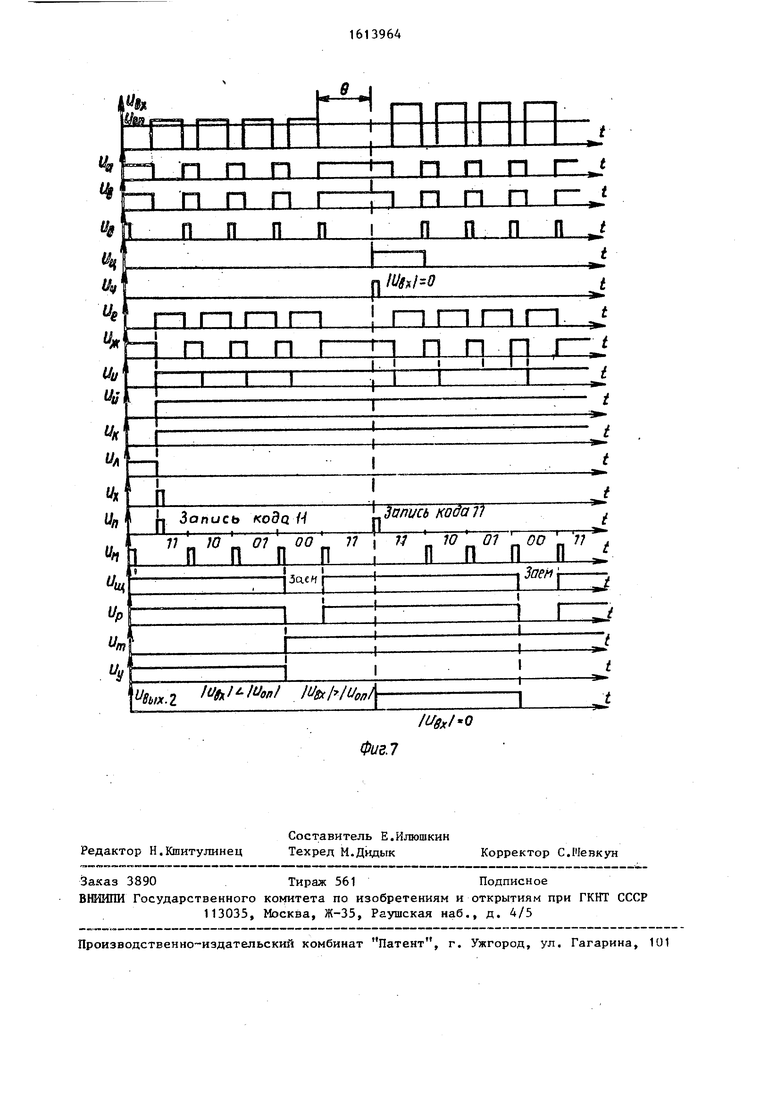

На фиг.1 представлена функциональная схема устройства для контроля напряжения} на фиг.2 - функциональная схема блока статистической обработки; на фиг.З - эпюры напряжений в характерных точках устройства при контроле уровня постоянного напряжения в отрицательной полярности; на фиг.4 - эпюры напряжений в характерных точках устройства при контроле амплитуды гармонического сигнала в положительной полярности; на фиг.5 - эпюры напряжений в характерных точках устройства при контроле амплитуды импульсов импульсной последовательности в отрицательной полярности; на фиг.6 - эпюры напряжений в характерных точках устройства при контроле амплитуды импульсов импульсной последовательности в положительной полярности для случая, когда поступление сигналов прекращается в связи с катастрофическим отказом; на фиг.7 - то же, до и после катастрофического отказа, когда соотношение между опорным напряжением и амплитудой импульсов не изменяется.

Эпюры напряжений на фиг.З - 5 даны для блока статистической обработки, изображенного па фиг.1, а на фиг.6, 7 - для блока статистической обработки, изображенного на фиг. 2.

Устройство состоит из нуль-органа 1, порогового элемента 2, блока 3 управления, первого 4, второго 5,

оо со

05

N

3

третьего 6, четвертого 7, пятого 8 элементов 2-2и-ИЛИ,первого 9, второго 10, третьего 11 триггеров, одно- вибратора 12 с повторным запуском, первого 13, второго 14, третьего 15 четвертого 16 формирователей импульса,элемента ЗИЛЙ17, блока 18 статистической обработки, состоящего из первого 19, второго 20 элементов 2И, реверсивного счетчика 21 импульсов, элемента 2ШШ 22, триггера 23; генератора 24 импульсов, источника 25 бпорного напряжения, элемента 26 регулировки опорного напряжения, элемента. 2ШШ 27.

Блок 28 статистической обработки (фиг,2) содержит счетчик 29 импульсов, первый 3Q, второй 31 элементы 2И с инверсией на первых входах и выходе, триггер 32.

Информационньй D и тактовый С входы триггеров 23 и 32 подключены к общей шине устройства, входы сброса R триггеров 9-11 подключены к источнику высокого логического потенциала (не показан).

Вход нуль-органа 1 и первый вход порогового элемента 2 соединены между собой и являются входом устройства. Инверсный и прямой выходы нуль-органа 1 подключены к первым входам И соответственно первой и второй групп входов 2И первого элемента 2-2И-ИЛИ 4, прямой выход которого через первый формирователь 13 импульса подключен к входу одновиб- ратора 12 с повторным запуском,, а его инверсный выход соединен с тактовым входом первого триггера 9. Прямой и инверсный выходы порогового элемента. 2 соединены с первыми входами И соответственно первой и второй групп входов 2И второго элемента 2-2И-ИЛИ 5, прямой выход которого подключен к входам установки первого 9 и второго 10 триггеров, а его инверсный выход соединен с первым входом И первой группы входов 2И третьего элемента 2-2И-1ШИ 6, Общая шина устройства подключена к информационному входу первого триггера 9 выход которого соединен с информа- -ционным входом второго триггера 10, Тактовый вход второго триггера 10 подключен к входу одновибратора 12 с повторным запуском и первому входу И второй группы входов 2И пятого элемента 2-2И-ИЛИ 8. Первый вход И

613964

10

15

0

5

0

5

0

5

0

5

первой группы входов 2И пятого элемента 2-2И-ИЛИ 8 связан с выходом генератора 24 импульсов. Выход второго триггера 10 подключен к первому входу И второй группы входов 2И третьего элемента 2-2И-ИЛИ 6, прямой и инверсный выходы которого подключены соответственно к первому и второму входам блока 18 статистической обработки. Выход пятого элемента 2-2И-ИЛИ 8 подключен к третьему входу блока 18 статистической обработки. Выход одновибратора 12 с повторньм запуском подключен к тактовому входу третьего триггера 11,и через второй формирователь 14 импульса - к первому входу элемента ЗИЛИ 17, второй и третий входы которого подключены к выходам третьего 15 .s, четвертого 16 формирователей импульса соответственно. Прямой и инверсный выходы третьего элемента 2-2И-ИЛИ 6 соединены соответственно с входами третьего 15 и четвертого 16 формирователей импульса. Выход элемента ЗИЛИ 17 подключен к четвертому входу блока 18 статистической обработки, пятый вход которого подключен к седьмому выходу блока 3 управления. Первый и второй выходы блока 18 статистической обработки подключены соответственно к первым входам И первой и второй j-pynn входов 2И четвертого элемента 2-2И-ИЛИ 7. Вторые входы И первой и второй групп входов 2И четвертого элемента 2-2И-ИЛИ 7 подключены соответственно к пятому и шестому выходам блока 3 управления . Первый и второй выходы блока 3 управления подключены соответственно к вторым входам И первых и вторых, групп входов 2И первого 4 и второго 5 элементов 2-2К-ИЛИ. Третий и четвертый выходы блока 3 управления подключены соответственно к вторым входам первых и вторых групп входов 2И третьего 6 и пятого 8 элементов 2-2И- ИЛИ. Второй вход порогового элемента 2 через элемент 26 регулировки опорного напряжения подключен к выходу источника 25 опорного напряжения, первый и второй управляющие входы которого соединены с одноименными выходами блока 3 управления. Третий выход блока 18 статистической обработки подключен к входу установки третьего триггера .11, информацион™ ный вход которого соединен с общей

51

точкой устройства, а выход является вторым выходом устройства и под- юпочен к второму входу элемента 2ИЛИ 27, первый вход которого является первым выходом устройства и соединен с выходом четвертого элемента 2- 2И-ИЛИ 7. Выход элемента 2ИЛИ является третьим выходом устройства. Первые входы И соответственно первого 19 и второго 20 элементов 2И являются первым и вторым входами блока 18 статистической обработки, третий вход которого соединен с вторыми входами И элементов 2И 19 и 20. Выходы первого 19 и второго 20 элементов 2И подключены соответственно к входам суммирования и вычитания реверсивного счетчика 21 импульсов, выходы переноса и заема которого соединены соответственно с входом установки и сброса триггера 23, инверсный и прямой выходы которого являются первым и выходами блока 18 статистической обработки. Выходы переноса и заема реверсивного счетчика 21 импульсов подключены к первому и второму входам элемента 2И 22 с инверсией на входах и выходе, выход которого является третьим выходом блока 18 статистической обработки, четвертый и пятый входы которого подключены к тактовому и информа1щонному входам реверсивного счетчика 21 импульсов. В блоке 28 статистической обработки вторые выходыi соответственно первого 30 и второго 31 элементов 2И с инверсией на первом входе являются первым и вторым входами блока

28статистической обработки, третий вход которого подключен к входу вычитания счетчика 29 импульсов. Тактовый и информационный входы счетчика 29 импульсов являются соответственно четвертым и пятым входами блока 28 статистической обработки. Выход заема счетчика 29 импульсов явлйется третьим выходом блока статистической обработки, первый и второй выходы которого подключены к инверсному и прямому выходам триггера 32.Входы установки и сброса триггера 32 соединены с выходами соответственно первого 30 и второго 31 элементов 2Н с инверсией на первом входе и выходе, первые входы которых соединены с входами заема счетчика

29импульсов.

964

Устройство работает следующим образом.

В зависимости от соотношения на входе устройства между контролируе- мым уровнем постоянного или амплитудой гармонического или импульсного сигнала lAeyl и опорным на- . пряжением |:ио„| устройство может

Q находиться в трех УСТОЙЧИВЫХ состояниях ИСПРАВНО/НЕИСПРАВНО/ОТСУТСТВИЕ ВХОДНОГО СИГНАЛА в соответствии с критериями и режимами работы, указанными в табл.1.

с. Блок 3 управления формирует на своих выходах логические управляющие сигналы, программирующие режим работы (контроля) устройства согласно табл.2.

0 Пусть устройство запрограммировано для контроля постоянного напряжения по максимально допустимому уров- ню в отрицательной полярности (шестая строка табл.2).

5 Контролируемое напряжение Ug поступает на первый вход порогового элемента 2, где сравнивается с опор- , ным напряжением отрицательной полярности UQJ, 5 которое формируется на

30 выходе элемента 26 регулировки опор ного напряжения путем деления выход- . него напряжения источника 25 опорного напряжения. В качестве элемента 26 регулировки опорного напряжения может быть использован цифроа)1алого- вый преобразователь (в дальнейшем ЦАП) или потенциометр. На фиг.1 цепи цифрового управления ПАП не показаны. В качестве источника 25 опорного напряжения могут быть использованы стабилитроны, формирующие отрицательное и положительное опорное напряжение, которое через коммутирующие элементы, в зависимости от полярности контролируемого сигнала, подключается на выход источника 25 опорного напряжения. Управление коммутирующими элементами осуществляется через первый и второй управляющие входы источнзша 25 опорного напряжения .

Если критерий исправности не нарушен, то высокий логический потенциал на инверсном выходе порогового элемента 2 через BTopoit 5 и третий

6 элементы 2-2И-И.М поступает на второй вход блок,1 18 статистической обработки, кромп того, низкий логический потенциал устанавливается на

40

50

первом входе блока 18 статистическо обработки. Низкий и высокий логические потенциалы на соответственно первом и втором входах блока 18 статистической обработки запрещают поступление импульсов с выхода пятого элемента 2-2И-И.ВД 8 через первый элемент 2И 19 на вход суммирования реверсивного сче гчика 21 импульсов и разрешают поступление импульсов через второй элемент 2И 20 на вход вычитания реверсивного счетчика 21 импульсов (фиг.З). Если критерий исправности не нарушается в течение времени t , (t , & К) , где { - период имЛульсов генератора 24 импульсов; К - емкость реверсивного счетчика 21 импульсов, то реверси:вный счетчик 21 импульсов переполняется и в момент перехода в нем кода из 00„..0 в 11.,.1В (В-признак двоичного кода), при действии счетного импульса на входе вычитания, на выходе заема периодически формируется импульс, равный по длительности паузе между импульсами генератора 24 импульсов. Импульс заема, поступая на-вход сброса триггера 23, удер: ш- вает его прямой : выход в состоянии низкого логического потенциала, который также удерживается на выходе ч.етвертого элемента 2-2Р1-ЕПИ 7 Ugb-., и выходе элемента 2ИЛИ 27 . Состояние UB,,, и Ugyya (низкий логн ческии потенциал) удерлшвается неизменным в течение неограниченного числа периодов генератора 24 импулъ- сов, если критерий исправности не нарутлается. Фактшгески с периодом t-К происходит подтверждение (формирование импульса заема) низкого логического потенциала Up,,,,, и.х.

При нарушении критерия V g,f. iUQ(, 1 инверсный выход порогового элемента 2 переходит в состояние низкого логического потенциала и соответственно на первом и втором входах блока 18 статистической обработки устанавливаются высокий и низкий логические потенциалы, которые через первый элемент 2И 19 разрешают поступление .импульсов на вход суммирования реверсивного счетчика 21 импульсов, а через второй элемент 2И 20 запрещают поступление импульсов на вход вычитания реверсивного счетчика 21 итульсов. По фронту в момент перехода из низкого в

8

высокий логический потенциал прямого выхода третьего элемента 2-2И-Ш1И 6 третий формирователь 15 импульса формирует короткий импульс, поступаю- - щий через элемент ЗИТШ 1 7 на четвертый вход блока 18 статистической обработки (на тактовый вход реверсивного счетчика 21 импульсов). По 10 тактовому импульсу в реверсивный счетчик 21 импульсов заносится двоичный код NJ (например, в соответствии с фиг.З код 10В, а реверсивный счетчик 21 импульсов выполнен двухразряд- 1 ным), установленный предварительно

на его информационном входе (седьмом выходе блока 3 управления, пятом входе блока 18 статистической обработки) . Если после формирования такто™ 2Q вого импульса критерзш исправности нарушаете в течение времени с, (с f. (K-Np, N/CK), то в момент перехода кода из ИВ в ООЕ при действии счетного импульса на входе сум- 25 мирования, на выходе переноса реверсивного счетчика 21 импульсов формируется короткий импульс, равный по длительности паузе между импульсами генератора 24 импульсов. Им- 3Q пульс переноса поступает на вход установки триггера 23, устанавливая его прямой выход в состояние вы- у сокого логического потенциала, которое также устанавливается на выходе четвертого элемента 2-2И-ИЛИ 7 Uau.n

btllA

и выходе элемента 2ИЛИ 27 UBI,,, ин- дс-щируя таким образом нарушения критерия исправности. Пусть нарушение критерия исправности после первого ,Q импульса переноса продолжается в

течение времени С (с- К), тогда реверсивный счетчик 21 импульсов периодически (с периодом f К) переполняется, и импульсы переноса перио- 45 Дически поступают на вход установки триггера 23, подтверждая высокий логический, потенциал на его прямом выходе. На фиг.З показано, что в момент нарушения критерия исправнос- ти на выходе третьего формирователя 15 импульса формируются импульсы которые через элемент ЗИЛЙ 17 U поступают на тактовый вход реверсивного счетчика 21 импульсов, занося в него код 11В. После первого счет35

5

ного импульса на выходе пятого элемента 2-2И-ИЛИ 8 ид, на выходе реверсивного счетчика 21 импульсов формируется импульс переноса Up, ус91

танавливаюпщй прямой выход триггера 23 и. в состояние высокого логического потенциала, которое также устанавливается на выходе четвертого элемента 2-2И-ИЛИ 7 Ugj,,, и выходе элемента 2ИЛИ 27 Ир,„ . Под воздействием счетных импульсов Uj состояние реверсивного счетчика 21 импульсов последовательно изменяется ООВ, 01В, ЮВ, 11В, после чего формируется второй импульс переноса, подтверждающий предыдущее состояние триггера 23 Up, Uf, которое-индицирует нарушение критерия исправности.

В момент перехода из низкого в высокий логический потенциал инверсного выхода третьего элемента 2-2И- ИЛИ 6, что происходит, когда контролируемое напряжение- U изменяется и происходит удовлетворение критерию контроля (lUgy(: t Uon I ), по фронту, четвертый формирователь 16 импульса формирует короткий импульс Цф, который через элемент ЗИЖ 17 и. поступает на тактовый вход реверсивного счетчика 21 импульсов, занося в него двоичный код N|, установленный на его информационном входе (в нашем примере - код 10В, а реверсивный счётчик 21 импульсов выполнен двухразрядным. Информация об изменении соотношения между напряжениями |Ug)(| и lUonI на входе устройства отображается на его выходах после второго счетного импульса U на выходе пятого элемента 2-2И-ИЛИ 8, т.е импульс заема и на выходе заема реверсивного счетчика 21 импульсов опрокидывает триггер 23 в состояние низкого логического потенциала.

Таким образом, информация о любом изменении соотношения напряжениями |Ugj| и lUflnl на входе устройства на его выходе отображается не сразу, а после статистической обработки, отсчета запрограммированного числа счетных импульсов, в течение которых осуществляется проверка соотношения I UB)(( и|идц|. Если нарушение критерия исправности длится меньше времени отсчета запрограммированного числа счетных импульсов илИуНаоборот, удовлетворение критерию исправности длится меньше времени отсчета запрограммированного числа счетных импульсов, то устройство на своем выходе не фиксирует изме- нение соотношения jUexi и I на

96410

входе, чем достигается эффективная защита от помеХ (ложных срабатываний) определенной значениями iJ, N: , К длительности.

Если устройство настраивается на контроль уровня положительного постоянного напряжения по максимуму (вторая строка, табл.2), то включаетп ся цепь прохождения информации с входа на выход устройства,описанная ранее, за исключением того, что во втором элементе 2-2И-ИЛИ 5 информация на выход поступает с инверсног го, а не прямого выхода порогового элемента 2,подается положительное напряжение (Uonl с выхода элемента 26 регулировки опорного ,напряжения, при этом пот воздействием управляю0 щих сигналов на первом и втором управляющих входах на выходе источника 25 опорного нaпpяжeнIiя устанавливается положительное напряжение. При контроле постоянного положи5 тельного напряжения по минимуму (первая строка табл.2) устройство функционирует аналогично режиму контропя соответствующему второй строке табл.2 за исключением того, что формация на выходы устройства поступает с первого выхода блока 18 статистической обработки (инверсного выхода триггера 23). Контроль уровня постоянного отрицательного напряжения по минимy iy (пятая строка табл.2)

осуществляется аналогично щему случаю, меняется только цепь прохождения информации после порогового элемента 2, полярность опорного напряжения .

Если контролируется амплитуда JAg(l синусоидального (гармонического) сигнала U еи в положительной полярности по максимуму (четвертая строка табл.2), то при каждом пере- ходе напряжения через нуль из отрицательной полярности в положительную (фиг.4) на инверсном выходе нуль-органа 1 формируется низкий логический потенциал (фиг.4 Uq), из которого на прямом выходе первого элемента 2-2И-ИЛИ 4 формируется сигнал, по передним фронтам которого первый формирователь 13 импульса короткие импульсы (фиг.4 U) в мо мент перехода контролируемого напряжения и gx из положительной в отрицательную полярность. По передним фронтам импульсов на инверсном выхо45

n

де первого элемента 2-2И-ИЛИ 4 (фиг 4 и), в каждом периоде контролируемого гармонического сигнала первый триггер 9 устанавливается в исходное нулевое состояние (фиг,4 TL) Короткие импульсы на выходе первого формирователя 13 импульсов, поступая на тактовый вход второго триггера 10 записывают в него в каждом периоде контролируемого сигнала Ug;( информацию, присутствующую на выходе первого триггера 9 (фиг.4 Ua, Uy, U). Если критерий исправности не нарушается , то на выходе второго триггера 10 постоянно поддерживается низкий логический потенциал (фиг.4 ), который)Поступая на соответству1оп 1й вход третьего элемента 2-2И-Ш 1И 6, удерживает его прямой и инверсный выходы соответственно в состоянии низкого и высокого логических потенциалов. Короткие импульсы с выхода первого формирователя 13 импульса через пятый элемент 2-2И-ИЛИ 8 поступают на третий вход блока 18 статистической обработки, где, совпадая с высоким логическим потенциалом на первом входе второго элемента 2И 20, поступают на вход вычитания реверсивного счетчика 21 ш-шуль- сов (фиг.4 и, ид, и„, UQ). Низкий логический потенциал на первом входе первого элемента 2И 19 запрещает поступление импульсов с выхода пятого элемента 2-2И-ИЛИ 8 на вход суммирования реверсивного счетчика 21 импульсов. Если критерий исправности не нарушается в течение времени Сц . ,(ty 7 Т-К, где Т - период контролируемого гармонического сигнала, К - емкость реверсивного счетчика 21 импульсов), то под воздействием счетных Импульсов на входе вычитания реверсивный счетчик 21 импульсов переполняется и импульс заема на его соответствующем выходе удерживает на прямом выходе триггера 23 низкий логический потенциал, который также устанавливается на выходе четвертого элемента 2-2И-ИЛИ 7 и выходе элемента 2ИЛИ 27 Uj, индицируя удовлетворение критерию исправности (фиг.4 Ug, U(,, l, Ц.). Такое состобых выхз устройства

яние выходов Ug,.. , U хранится неограниченное число периодов контролируемого гармонического сигнала, в .течение которых происходит удовлетворение критерию испрявностп |Лвх( : Uonl

61

. ). я 0,

10

15

30

50

396412

Пусть критерий исправности нарушен, т.е. выполняется неравенство 1 и,п . В момент сравнения напряжений на входах порогового эле- 5 мента 2, на его прямом выходе (фиг.4 U0), на прямом выходе второго элемента 2-2И-ИЛИ 5 (фиг.4 U.;) форми-. руется низкий логический потенциал, которьй устанавливает первый 9 и второй 10 триггеры в состояние высокого логического потенциала (фиг.4 U,, и). С выхода второго триггера 10 информация о нарушении критерия контроля поступает на соответствующий вход третьего элемента 2-2И-ИЛИ 6, на прямом и инверсном выходах которого устанавливаются соответственно высокий и низкий логические потенцйа20 лы. Высокий логичес1атй потенциал, установленный таким образом на первом входе блока 18 статистической обработки (первом входе первого элемента 2И 19), разрешает счетным

25 импульсам с выхода первого формирователя 13 импульсов через пятый элемент 2-2И-ИЛИ 8 поступить на вход суммирования реверсивного счетчика 21 ж пульсов. Одновременно в момент перехода из низкого Е высокий логический потенциал прямого выхода третьего элемента 2-2И-ИЛИ 6 третий формирователь 15 импульса формирует короткий импульс, котор.ый через элемент ЗИЛИ 17 поступает на тактовый вход

35 реверсивного счетчика 21 импульсов, занося в него двоичный код N , установленный на его информационном входе (фиг.4 иI;, и, и„). Спустя время

лп Ч( -U Т (к - Nj)) , если соотношение ме7кду амплитудой (АВХ и опорным напряжением Ндр на входе устройства не изменилось (АВХ| И оп1) Ре- версивный счетчик 21 импульсов просчитает К - NI счетных импульсов и переполняется. Импульс переноса устанавливает прямой выход триггера 23 в состояние высокого логического потенциала (фиг..4 , Uu), при этом выходы четвертого элемента 2-2Н--ИЛИ 7 и элемента 2ИЛИ 27 U ц, иакже установятся в состояние высокого логического потенциала, инди- 1щруя таким образом нарушение критерия исправности. Состояние выходов

55 Upj,|,(, j Upbix 3 сохраняется неизменным (высокий логический потенциал) в течение времени выполнения неравенства (A(5j(| I и о I . Если в определенный период контролируемого гармоническо13

го сигнала его амплитуда Agj; уменьшится до величины JAgjd 1 Uon I i ° информация об этом на выходе второго триггера Ю, третьего элемента 2-2И- ИЛИ 6 отобразится в этом же периоде, по импульсу на выходе первого формирователя 13 импульса (фиг.4 U|. , Utt Ui, UK , UA ). При этом по фронту в момент перехода инверсного выхода третьего элемента 2-2И-ИЛИ 6 из низкого в высокий логический потенциал; четвертый формирователь 16 импульса формирует короткий импульс, который через элемент ЗИЛИ 17 поступает на тактовый вход реверсивного счетчика 21 И1 пульсов, занося в него код N; (фиг.4, Urn, Ufl). После отсчета N: импульсов (фиг.4 Up), спустя время t(t5 Ь T«Nj), если критерий исправности не нарушается, на выходе заема реверсивного счетчика 21 импульсов формируется импульс, устанавливающий прямой выход триггера 23 в состояние низкого логического потенциала. В состояние низкого логического потенциала установятся также выхолы Ug(,ix) и&ьщг На фиг, 4 эпюры приведены для случая, когда на седьмом выходе блока 3 управления установлен двоичн ый код 01В, а ревер- сивньш счетчик 21 импульсов выполнен дв ухра 3 ря дным.

Контроль амплитуды импульсных последовательностей ничем не отличается от контроля амплитуды гармонических сигналов. На фиг.5 показана последовател1гность логических . переходов в устройстве, когда контроль осуществляется в соответствии с восьмой строкой табл.2.

При настройке устройства на контроль амплитуд гармонических или импульсных сигналов по минимально допустимому уровню в соответственно положительной (третья строка табл.2) и отрицательной (седьмая строка

табл.2) полярностях устройство функционирует аналогично вьшеописанным случаям, но в зависимости от режима контроля меняются цепи прохождения информации с входа на выход, при этом высокий логический потенциал на выходе блока 3 управления разрешает прохождение информации по соответствующим цепям устройства, а низкий запрещает.

Таким образом, как и в случае контроля уровня постоянного напряже

-

39641

ния I Ug I информация о любом изменении соотношения между амплитудой /Agjd гармонических сигналов или импульсных последовательностей и опор- 5 ным напряжением на выходе устройства отображается не сразу, а после статистической обработки, спустя программируемое число периодов контролируемого си -нала, в течение которых такое изменение должно подтверждаться, после чего происходит переполнение реверсивного счетчяка 21 импульсов в блоке 18 статистической обработки, что приводит к изменению СОСТОЯН11Я выходов Ug(,|j« , Ug(,

устройства.

В процессе контроля уровня постоянных сигналов на вход установки

20 третьего триггера 11 по шине Ищ постоянно поступают сигналы, удерживающие его инверсный выход в состоянии низкого логического потенциала (табл.1). Формирование этих сигналов

25 обусловлено тем, что реверсивный счетчик 21 импульсов (блок 18 статистической обработки) функционирует под воздействием непрерывных тактовых импульсов генератора 24 импуль-,,, сов. Если контролируется амплитуда гармонических или импульсных сигналов и эти сигналы присутствуют на входе устройства, то под воздействием постоянно формируемых сигналов на выходе первого формирователя 13

35 импульса постоянно формирчтотся сигналы на шине 11, удерживающие инверсный выход третьего триггера 11 в состоянии низкого логического потенциала (табл.1). Т.е. при контроле постоянных сигналов (первая, вторая, пятая, шестая строки табл.2) и при контроле амплитуд гармонических или импульсных сигналов (третья, четвертая, седьмая, восьмая строки табл.2) и наличии этих сигналов га входе устройства низкий логический потенциал UjjjiKj однозначно определен.

Пусть в процессе контроля амплитуды гармонических или импульсных сигналов в определенный момент времени (фиг.6, 7) произойдет в результате катастрофического отказа прекращение поступления на вход устройства контролируемого сигнала на время

55 с, б, где б - постоянная времени одновибратора с повторнгм запуском 12. Б этом случае при переходе из состояния низкого в состояние высоко40

45

50

15

го логического потенциала выхода од)10йиб;;)атора 12 с повторным запуском по фронту на инверсном выходе т.ретье о триггера 11 ивь(;гг Устанавливается Ьысокий логический потенциал, nocfy- 11ающй через элемент ЙИЛИ 27 на выхо устройства иet,,,3 фиг,6 Uy,. ). происходит индикация прекращения поступления на вход устройства контролируемого сигнала. Одновременно второй формирователь 14 импульса формирует импульс, который поступает чере элемент ЗИЛИ 17 и четвертый вход блока 28 статистической обработки на тактовый вход счетчика 29 импульсов (фиг.2, 6, 7 и,., и.

1

ц. ч

Uj,) . По этому

импульсу в счетчик 29. импульсов за- письшается код N. с седьмого выхода блока 3 управления. На фиг.6, 7 код Nj - 11В, а счетчик 29 импульсов выполнен двухразрядным. Если в даль- .нейшем контролируемые сигналы вновь поступают на вход устройства, то первый импульс Uj, запускает одновибра- тор 12 с повторным запуском, переведя его вых од . в состояние низкого логического потенциала, однако изменение состояния UB|,,2. происходит не сразу, а после отсчета счетчиком импульсов 29 запрограммированного числа импульсов и-Формирования импульса заёма UцJ, который устанавливает Ug,),2. в состояние низкого логического потенциала ,

Таким образом, при контроле амшш- туды гармонического или импульсного сигнала высокий логический потенциал на выходе устройства U gt,,x2 однознагШ определяет отсутствие на входе устройства контролируемого сигнала на время, большее О .

В блоке 18 статистической обработки изменение состояния Ugj,|j(| и Шиг определяется кодами Nj, К - Nj, т.е. если произошло изменение состояния, определяемое кодом Nj, то противоположное изменение определяется кодом К - N .. В этом

отличие блока 18 статистической обработки от блока 28 статистической обработки, в котором изменение состояния первого и второго выходов определяется только кодом N 4

Устройство позволяет контролировать постоянные, гармонические и импульсные сигналы, контролировать наличие на входе гармонических и импульсных сигналов, кроме того, уст

-

613964

16

10

I -

-35

55

ройство обладает повышенной помехоустойчивостью, так как оно настраивается цифровым кодом на импульсные помехи определенной длительности, не вызывающие его срабатьшание и действующие на его входе.

.

Формула изобретения

1. Устройсто для контроля на- пряжения, содержащее источник опорного напряжения, элемент регулировки опорного напряжения, нуль-орган, пороговый элемент, первый - четвер- ,5 тый элементы 2-2И-ИЛИ, первый и второй триггеры, одновибратор с ттовтор- ным запуском,, генератор импульсов, первый и второй формирователи им- .пульса, блок управления, причем 20 вход нуль-органа и первый вход порогового элемента подключены к входу устройства, инверсный выход нуль-органа подключен к первому входу И первой группы входов 2И, а второй 25 выход - к первому входу И второй группы входов 2И первого элемента 2-2И-ИЛИ, прямой выход которого подключен к входу первого формирователи импульсов, первый выход порогового 30 элемента соединен с первым входом И первой группы входов 2И, а второй - с первым входом И второй группы входов 2И второго элемента 2-2И-РШИ, прямой выход которого соединен с входом установки первого триггера, первый выход блока управления соединен с вторыми входами И первых групп входов 2И первого и второго элементов 2-2И-ЩШ, второй выход блока управления соединен с вторыми входами И вторых групп входов 2И первого и , второго элементов 2-2И. -ИЛИ, первый и второй управляющие входы источника опорного напряжения соединены с одноименными выходами блока управления, выход источника опорного напряжения через элемент регулировки опорного напряжения подключен к второму входу- порогового элемента, отличающееся тем, что, с целью повышения помехоустойчивости, в устройство введены два формирователя импульса, пятый элемент 2-2И-ИЛИ, третий триггер, элемент 2ИЛИ, элемент ЗКЛИ, блок статистической обработки, причем инверсиьп выход первого элемента 2-2И-ИЛИ соединен с тактовым входом первого триггера, информационный вход которого подключен к общей шине

40

45

50

17

стройства, а его выход соединен с нформационным входом второго триггеа, вход установки которого соединен одно1В4енным входом первого тригера, а тактовый вход подключен к ходу первого формирователя импульа, входу одновибратора с повторным апуском и первому входу И второй группы входов 2И пятого элемента , первый вход И первой группы входов 2И. которого соединен с выходом генератора импульсов, ноход второго триггера соединен с первым входом И второй группы входов 2И третьего элемента 2-2И-ИЛИ, первый вход И первой группы входов 2И которого подключен к инверсному выходу второго элемента 2-2И-1ШИ, третий и чет- вертый выходы блока управления соединены с вторыми входами И первых групп входов 2й третьего и пято1 о эл ементов 2-2И-ИЛИ соответственно с вторыми входами И вторых групп входов 2И третьего и пятого элемен- |та 2-2И-ЯПИ, выход одновибратора с повторным запуском подключен к тактовому входу третьего триггера и через второй формирователь импульса соединен с первым входом элемента ЗИЛИ, второй и третий входы которого соединены соответственно с выходами третьего и четвертого формирователей- импульса, входа которых соединены соответственно с прямым и инверсным выходами третьего элемента 2-2И-1 ШИ, информационный вход третьего триггера подключен к общей шине устройства, первьй и второй входы блока статистической обработки соединены с прямым и иннерсным выходами третьего элемента 2-2И-Ш1И, выход пятого элемента 2-2И-ШШ подключен к третьему входит блока статистической обработки, четвертый и пятый входы которого соединены соотретст-. венно с выходом элемента ЗИЛИ, с седьмым выходом блока управления, первый и второй выходы блока статистической обработки подключены к первым входам И соответственно первой и второй групп входов 2И четвертого элемента 2-2И-ИЛИ, вторые входы И первой и второй групп входов 2И которого связаны соответственно с пя- ть1М и шестым выходами блока управления, третий выход блока статистической обработки подключен к установочному входу третьего триггера, выхо

10

15

20

25

30

35

40

45

50

55

18 ды четвертого элемента 2-2И-ИЛИ и третьего триггера являются соответственно первым и вторым выходами устройства и подключены к входам элемента 2ИЛИ, выход которого является третьим выходом устройства. .

2, Устройство по П.1, о т л и - чающееся тем, что блок статистической обработки содержит первый и второй элементы 2И, реверсив- счетчик импульсов, четвертый триггер; элемент 2йЛИ с инверсией на входах и выходе, причем первые входа первого и второго элементов 2И являются соответственно первым и вторым входами блока статистической обработки, третий вход которого соединен с эторыми входам первого и второго элементов 2И, выходы которых соединены соответственно с входом сумГ Шрования и вычитания реверсивного счетчика, тактовый и информаци- онньй входы которого подключены соответственно к четвертому и пятому ВХОДЯ блока статистической обработки, первый и второй выходы которого соединены с инверсным вторым и прямым первьм выходами четвертого три герН; входы установки и сброса которого подключены соответственно к выходам переноса и заема реверсивного счетчика импульсов, к первому и второму входам элемента 2ИЛИ с инверсией на входах и выходе, выход которого является третьим выходом блока статистической обработки.

3. Устройство по п,1, о т л и - чающееся тем, что блок статистической обработки содержит счетчик импульсов, четвертый триггер и два элемента 2И с инверсией на первом входе и выходе, причем вторые входы соответственно первого и второго элементов 2М с инверсией на nej)- вом входе и выходе являются соответственно первым и вторым входами блока статистической обработки, третьим входом которого является вход вычитания счетчика импульсов, выход заема которого подключен к первым входам первого и второго элементов 2И с инверсией на первом входе и выходе, выходы которых подключены к входам установки и сброса соответственно четвертого триггера,инперсньй и прямой выходы которого являются соответственно первым и вторым зыходсчми

1 9

ss Lx:no TL:rL°T «™- -- - eoдом заема счетчика Гчв.° «« « венно к тактовому и информаci импульсов, а чет-ционному входам счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсных сигналов | 1984 |

|

SU1181126A1 |

| Универсальное устройство для контроля напряжения | 1983 |

|

SU1170359A1 |

| ИМИТАТОР РЕАЛИЗАЦИИ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099863C1 |

| Цифровой фазометр | 1983 |

|

SU1118935A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2276457C2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для контроля параметров | 1989 |

|

SU1605214A1 |

| Устройство для формирования импульсов | 1985 |

|

SU1285574A1 |

| Устройство для определения положения числа на числовой оси | 1984 |

|

SU1231497A1 |

Изобретение относится к контрольно-измерительной технике и может быть использовано в системах автоматического контроля и регистрации. Цель изобретения - повышение помехоустойчивости, которая достигается применением блоков статистич еской обработки элементов 2И-ИЛИ 7, ИЛИ 17, формирователей 15, 16, триггера 11, элемента ИЛИ 27. Устройство содержит также нуль-орган 1, пороговый элемент 2, элемент регулирования опорного напряжения 25, генератор 24, элементы 2И-ИЛИ 4, 5, 6, 8, триггеры 9, 10, формирователи 13, 14, одновибратор 12. 7 ил.

Приме чан и

|и

РХ

вх

уровень постоянного (амплитуда

.т--1--

jf

- состояние, ня Овых в момент катастрофического прекращения поступления контролируемого с..гнала на вход устройства. У я поступле

:252Ж 3 к§ управления

Примечание. NJ - двоичный код, разрядность которого соответствует разрядности счетчика 21 импульсов (счетчика 29 импульсов).

вх

уровень постоянного (амплитуда

--

Таблица2

Режим работы

(контроля)

yfe

- %

П

3 г-1

4, 2

Фиг.1

%/ ,

l ixl /i/ffff/

Фив. 5

Фиг. 6

/ вх/ О

| Универсальное устройство для контроля напряжения | 1983 |

|

SU1170359A1 |

| Г, 01 R 19/00, 04.04.83 | |||

| Двухпороговое устройство для контроля напряжения | 1985 |

|

SU1337785A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-12-15—Публикация

1989-01-04—Подача