05

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения логарифмического коэффициента ошибок дискретного канала связи | 1986 |

|

SU1411993A1 |

| Устройство для выбора вариантов распределения мест между исполнителями | 1984 |

|

SU1241255A1 |

| Устройство для определения логарифмического коэффициента ошибок | 1989 |

|

SU1635262A1 |

| СЧЕТЧЙК ИМПУЛЬСОВ | 1971 |

|

SU294256A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для контроля качества канала связи | 1979 |

|

SU856023A1 |

| РЕВЕРСИВНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1970 |

|

SU287120A1 |

| Индикатор состояния контролируемых параметров | 1988 |

|

SU1564493A2 |

| СЧЕТЧИК ИМПУЛЬСОВ | 1971 |

|

SU293256A1 |

| УСТРОЙСТВО ПЛАНИРОВАНИЯ ТОПОЛОГИИ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ | 2012 |

|

RU2530275C2 |

Изобретение относится к технике связи. Цель изобретения - повышение достоверности. Устройство содержит счетные блоки 1, 2, 3, блок 4 задержки и блок 5 управления счетом. Устройство работает следующим образом. Счетный блок 1 фиксирует количество счетных импульсов LOG2Z, счетный блок 2 - количество ошибок, поступающих на вход сложения X и поступивших на вход вычитания Y после задержки в блоке 4, и на выходе блока 2 формируется сигнал LOG2(X-Y), а счетный блок 3 объединяет процессы первых блоков 1, 2, и на его выходе формируется текущее значение коэффициента ошибок, равное LOG2(X-Y)-LOG2(Z), чем и достигается цель. Устройство отличается также выполнением блока 4 задержки. 2 з.п. ф-лы, 4 ил.

Фи. 1

Ю

3

Изобретение относится к технике передачи дискретных ссюб).цений.

Цель изобретения -- понышение достоверности.

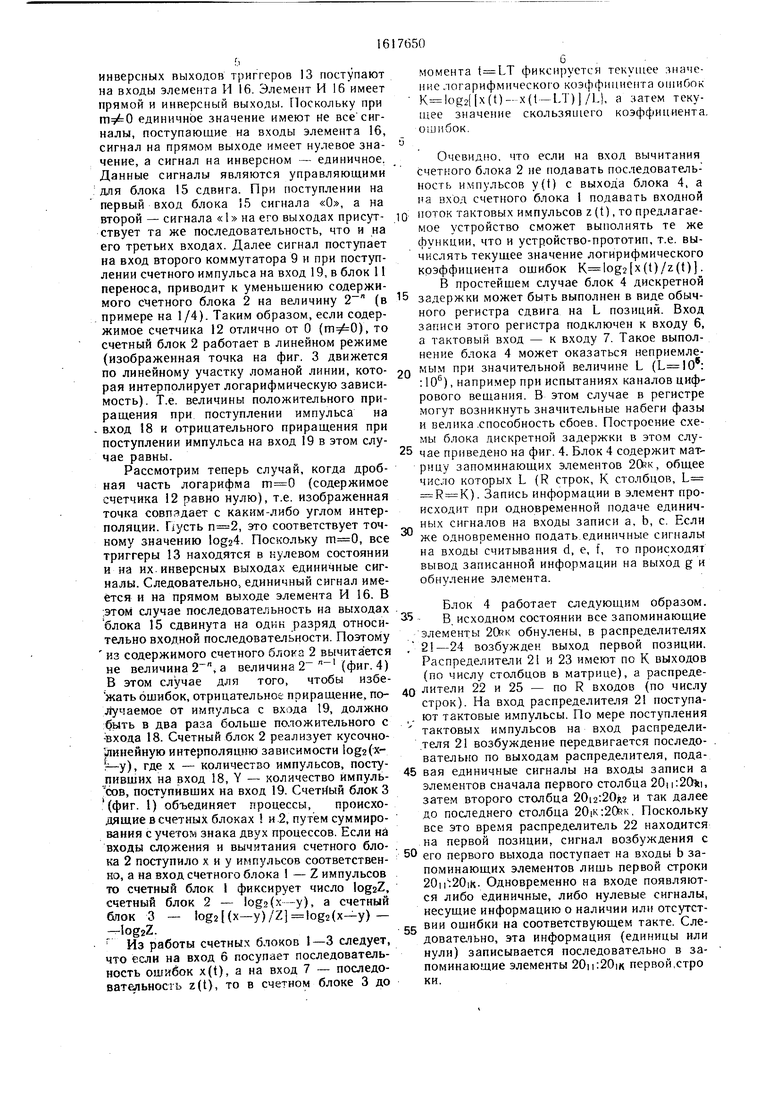

На фиг. 1 представлена электрическая структурная с.хема предлагаемого устройства; на фиг. 2 -- электрическая структурная схема второго счетного блока; на фиг. 3 - диаграмма, ноясняющая работу второго счетного блока; на фиг. 4 - электрическая структурная схема блока дискретной задержки. Устройство для определения логарифмического коэффициента ошибок дискретного канала связи (фиг. I) содержит первый , второй 2 и третий 3 счетные блоки,.блок 4 дискретной задержки, блок 5 управлени5 счетом, вход 6 сигнала ошибок и тактовый вход 7.

В состав второго счетного блока 2 : (фиг. 2) входят первый 8 и второй 9 коммутаторы, первый 10 и второй 11 блоки переноса, первый счетчик 12, включающий п триггеров 13, второй счетчик 14, блок 15 :сдвига, элемент И 16, элемент ИЛИ 17, :вход 18 сложения и вход 9 вычитания. ; Б.ПОК дискретной задержки (фиг. 4) .со- 1держит элементы 20 памяти, первый 21, вто- ;рой 22, третий 23 и четвертый 24 распреде- лители, элемент ИЛИ 25, ключевой эле- |мент 26 и элемент 27 задер.жки. Устройство работает следующим образом, i Устройство (фиг. I) имеет два входа. |На тактовый вход 7 поступает тактовая после- июпательность Z (t), каждый импульс которой соответствует одному символу испытатель- :ной последовательности, прошедшей через ;исследуемый канал. На вход 6 поступает последовательность x(t), каждый импульс :которой соответствует одной ошибке, обнару-. ;жениой в принятой испытательаой последо- :вателыюсти. При этом Г1ред1ю.лагается , что операция фиксирования ошибок уже выполнена. Очевидно, что число импульсов, поступающих на вход 6, не может превысить число импульсов, поступивших на вход 7.

Импульсы от входа 6 поступают на блок 4 дискретно задержки, задерживающий на . тактов поступающую на ;;ег о последовательность импульсов (ошибок) x(t). Таким образом, на выходе блока 4 имеется та же последовательность, что поступила на его вход, но задержанная на L тактов, т.е. если на вход поступила последовательность оп1и-. бок x(t), то на выходе имеется последовательность y(l) x(f-LT), где J - длительность элементарного снгн;1ла ис ытате 1ьной последовательности.

Последовательность x(t) с ахода 6 попадает на вход сложения счетного блока 2, а последователь юсть y(t) с выхода блока 4 понадает на вход 1 Ычитания счетного блока 2. Счетный блок 2 вычисляет текущее значение числа Iog2fx(t) v(ti - of72lx(t) - --x(t -LT)j. Таким образом, счетный блок 2 фиксирует текущее значение двоичного.ло

617650

4

гарифма числа ошибок, появившихся на бло- ке длиной в L элементов, предшествующих данному моменту времени.

Тактовые импульсы от входа 7 через блок 5 управления счетом поступают на вход первого счетного блока I. Используя информацию от блока 4, блок 5 пропускает на блок 1 первые L импульсов, а затем поступление импульсов прекращается. Если обозначить входящую последовательность (после10 довательность единиц) через Z(t)t/T, то в счетном блоке 1 фиксируется число log2Z(t), сли « После появления L-ro тактового импульса блок 5 прекращает счет, и в счетном блоке 1 остается зафиксированным чис15 ioggL.

Счетный блок 2 (фиг. 2) образован двумя последовательно соединенными счетчиками: счетчиком 12 дробной части логарифма и счетчиком 14 целой части. Счетчик 14 - обы20 чный реверсивный счетчик с входами сложения и вычитания. Отличие схемы счетчика 12 от классической заключается в том, что в блоках 7 и 8 переноса сигналов сложе - ния и вычитания установлены элементы

2g ИЛИ 17, которые позволяют вводить сигналы сложения или вычитания, начиная с любого разряда, а не только с самого младшего, как в обычной схеме. Счетные импульсы суммирования вводятся в цепь сложения через вход 18, импульсы вычитания - через

.30 вход 19. Место введения очередного счетного импульса определяется счетчиком 14, в котором хранится целая часть числа, фиксируемая счетным блоком 2. Таким образом, при подаче импульсов на вход 18 счетный блок 2 реализует кусочно-линейную интерполяцию

35 логарифма числа поступивших импульсов. Процесс .з,;е1-:ениг сосгояния счетного блока 2 и,г;л1острируется диаграммой фиг. 3,

Рассмотрим процессы, происходящие в счетном блоке 2 (фиг. 2) при подаче импуль.0 сов на вход 19. Принцип работы устройства не допускает, чтобы на вход 19 вычитания поступило импульсов больше, чем на вход 18 сложения. Предположим, что в счетном блоке 2 записано .некоторое число, целая часть

этого числа равна п, а дробная часть равна ш . усть п-2, , т.е. в счетчике 14 и в счет- члке i 2 записано число 010, что соответствует приближенному значению Iog26 (фиг. 3). При этом в счетчике 14 (фиг. 2) воздуждает- сяодин из выходов. Единичный сигнал постуr Q пает на соответствующие входы коммутатора 8 и блока 15 сдвига. При поступлении счетного импульса на вход 18 он через коммутатор 8 ггроходит в блок 10 переноса сигналов сложения и увеличивает содержимое счетного блока 2 на величину 2 (в рассмат- ,

.55 риваемом примере на 1/4). На янагрзмме

(фиг. 3) изображенная точка переходит по

соот зетствующей линии на один шаг вправо

fфиг. 4, стрелка со знаком +)- Сигналы с

нверсных выходов триггеров 13 поступают а входы элемента И 16. Элемент И 16 имеет рямой и инверсный выходы. Поскольку при единичное значение имеют не все сигналы, поступающие на входы элемента 16, сигнал на прямом выходе имеет нулевое значение, а сигнал на инверсном - единичное. Данные сигналы являются управляющими для блока 15 сдвига. При поступлении на первый вход блока 5 сигнала «О, а на второй - сигнала «1 на его выходах присутствует та же последовательность, что и на его третьих входах. Далее сигнал поступает на вход второго коммутатора 9 и при поступлении счетного импульса на вход 19, в блок 11 переноса, приводит к уменьшению содержимого счетного блока 2 на величину 2 (в примере на 1/4). Таким образом, если содержимое счетчика 12 отлично от О (), то счетный блок 2 работает в линейном режиме (изображенная точка на фиг. 3 движется по линейному участку ломаной линии, которая интерполирует логарифмическую зависимость) . Т.е. величины положительного приращения при поступлении импульса на вход 18 и отрицательного приращения при поступлении импульса на вход 19 в этом случае равны.

Рассмотрим теперь случай, когда дробная часть логарифма (содержимое счетчика 12 равно нулю), т.е. изображенная точка совпадает с каким-либо углом интерполяции. Пусть , это соответствует точному значению Iog24. Поскольку , все триггеры 13 находятся в кулевом состоянии и на их. инверсных выходах единичные сигналы. Следовательно, единичный сигнал имеется и на прямом выходе элемента И 16. В .этом случае последовательность на выходах блока 15 сдвинута на один разряд относительно входной последовательности. Поэтому из содержимого счетного блока 2 вычита1ется не величина 2, а величина 2 (фиг. 4) В этом случае для того, чтобы избе- жать ошибок, отрицательное приращение, получаемое от импульса с входа 19, должно быть в два раза больше положительного с -входа 18. Счетный блок 2 реализует кусочно- йинейную интерполяцию зависимости logzCx- ) где X - количество импульсов, поступивших на вход 18, Y - количество ймпуль- сов, поступивших на вход 19. Счетйый блок 3 (фиг. 1) объединяет процессы, происходящие в счетных блоках и.2, путем суммирования с учетом знака двух процессов. Если на входы сложения и вычитания счетного блока 2 поступило X и у импульсов соответственно, а на вход счетного блока 1 - Z импульсов то счетный блок 1 фиксирует число log2Z, счетный блок 2 - logo(х -у), а счетный блок 3 - iog2(x-y)(x-у)- -logyZ.

Из работы счетных блоков 1-3 следует, что если на вход 6 посупает последовательность ошибок x(t), а на вход 7 - последовательность z(t), то в счетном блоке 3 до

и

момента фиксируется текущее значение логарифмического коэффициента ошибок K log2{|x(t)-x(t-LT)J/LK а затем текущее значе)1ие скользяи1его коэффициента, ошибок.

Очевидно, что если на вход вычитания

счетного блока 2 не подавать последователь- ность импульсов y(t) с выхода блока 4, а на вход счетного блока 1 подавать входной

; поток тактовых импульсов Z (t), то предлагаемое устройство сможет выполнять те же функции, что и устройство-прототип, т.е. вычислять текущее значение логирифмического коэффициента ошибок (t)/z(t). В простейшем случае блок 4 дискретной

5 задержки может быть выполнен в виде обычного регистра сдвига на L позиций. Вход записи этого регистра подключен к входу 6, а тактовый вход - к входу 7. Такое выполнение блока 4 может оказаться неприемлеQ мым при значительной величине L ( : : 10®), например при испытаниях каналов цифрового вещания. В этом случае в регистре могут возникнуть значительные набеги фазы и велика .способность сбоев. Построение схемы блока дискретной задержки в этом слу5 чае приведено на фиг. 4. Блок 4 содержит матрицу запоминающих элементов 2Ок, общее число которых L (R строк, К столбцов, L R K). Запись информации в элемент происходит при одновременной подаче единичных сигналов на входы записи а, Ь, с. Если

же одновременно подать.единичные сигналы на входы считывания d, е, 1, то происходят вывод записанной информации на выход g и обнуление элемента.

Блок 4 работает следующим образом.

.5 в исходном состоянии все запоминающие

элементы 2Ок обнулены, в распределителях

21-24 возбужден выход первой позиции.

Распределители 21 и 23 имеют по К выходов

(по числу столбцов в матрице), а распреде0 лители 22 и 25 - по R входов (по числу строк). На вход распределителя 21 поступают тактовые импульсы. По мере поступления тактовых импульсов на вход распределителя 21 возбуждение передвигается последовательно по выходам распределителя, пода45 вая единичные сигналы на входы записи а элементов сначала первого столбца 20ii:20 i, затем второго столбца 20i2:20R2 и так далее до посутеднего столбца 20iK:2(K. Поскольку все это время распределитель 22 находится на первой позиции, сигнал возбуждения с 50 его первого выхода поступает на входы b запоминающих элементов лишь первой строки . Одновременно на входе появляются либо единичные, либо нулевые сигналы, несущие информацию о наличии или отсутствии ошибки на соответствующем такте. Сле- доватепьно, эта информация (единицы или нули) записывается последовательно в запоминающие элементы 20ii:20iK первой,стро ки.

По окончании записи в первую строку (это происходит тогда, когда возбуждение с последнего выхода распределителя 21 вновь переходит на его первый выход) выходной сигнал с распределителя 21 поступает на вход распределителя 22 и переводит возбуждение поступает на Ь ячеек второй теля на его второй выход. Тем самым возбуж- |дение поступает на вход b ячеек второй строки 202i:202K, и запись единиц и нулей, поступающих от входа, производится последовательно в элементы второй строки.

Указанный процесс последовательной записи информации происходит до тех пор, |пока запись не будет произведена в послед- |ний элемент последней строки 20RK. Появив- 111ГИЙСЯ при этом единичный сигнал на выходе |распределителя 22 поступает на ключевой |элемент 26, который открывается и пропус- кает тактовые импульсы на выходы считывания f всех запоминающих элементов. Поскольку в исходном состоянии у распределителей 23 и 24 возбуждены первые выходы, рдновременно на выходах считывания совпа- |аают единичные сигналы лишь у первого Элемента первой строки 20ii. Поэтому одновременно с записью информации в последний элемент 2Ок происходит считывание информации, записанной в первый элемент 20ii И очищение этого элемента. При этом выход- Ной сигнал с выхода g этого элемента, не- рущий информацию о ее содержимом, через Элемент ИЛИ 25 поступает на выход блока 4. Далее тот же сигнал с выхода элемента 26 через элемент 27 задержки попадает на вход распределителя 23 и переводит единичный сигнал с его первого выхода на второй. Таким образом, одновременно происходят запись Информации в последний элемент памяти и считывание из первого элемента 20ц и непосредственно вслед за этим подготовка к считыванию содержимого из второго элемента первой строки 20i2.

Очередной тактовый импульс с входа переводит распределители 21 и 24 в исходное состояние, цикл записи вновь начинается с первого элемента и одновременно происходит считывание содержимого их элемента 20i2. Следовательно, поступление информации на выход блока задерживается относительно поступления ее на вход на L-I такт.

Таким образом, предлагаемое устройство обеспечивает вычисление логарифма отношения числа ощибок к числу испытательных импульсов, если число испытательных сигналов Z не достигает L. Если же , то устройство фиксирует скользящий логарифмический коэффициент ошибок.

Формула изобретения 1. Устройство для определения логариф мического коэффициента ощибок дискретно5

го канала связи по авт. св. № 1411993, отличающееся тем, что, с целью повышения достоверности, тактовый вход устройства соединен с входом первого счетного блока через введенный блок управления счетом, вход сиг- на ла ощибок соединен с входом вычитания второго счетного блока через введенный блок дискретной задержки, второй вход которого соединен с тактовым входом устройства, выходы первого коммутатора второго счетного 0 блока соединены с соответствующими первыми входами первого счетчика через введенный первый блок переноса, второй выход которого соединен с входом сложения второ- - го счетчика, кроме того, введены во второй, счетный блок последовательно соединенные элементы И, входы которого соединены со всеми инверсными выходами первого счетчика, блок сдвига, второй вход которого соединен с инверсным выходом элемента И, а третьи входы соединены с соответствующими 0 ёходами второго счетчика, второй коммутатор, управляющий вход которого является входом вычитания второго счетного блока, и второй блок переноса, первые выходы которого соединены с соответствующими вторыми входами первого счетчика, второй выход & соединен с входом сложения второ-. : го счетчика, который выполнен в ви- ; де реверсивного счетчика, а вто- : рые входы соединены с соответствующими выходами первого счетчика, инверсные вы- оды которого соединены с соответствующими вторыми входами первого блока переноса: : 2. Устройство по п. 1, отличающееся тем, ; что блок дискретной задержки выполнен в виде матрицы, образованной элементами памяти, адресные входы записи и считывания g которых объединены соответственно в адресные входы записи и ;читывания строк и столбцов матрицы, тактовые входы всех элементов памяти соединены с тактовым входом матрицы, а входы всех элементов памяти соединены с входом матрицы, вход которой является 0. йходом блока дискретной задержки, содержит последовательно соединенные первый распределитель, вход которого является вторым входом блока дискретной задержки, второй распределитель, выходы первого и второ- го распределителей соединены соответствен- . но с адресными входами записи строк и столбцов матрицы, ключевой элемент, второй вход которого соединен с вторым входом бло- . на дискретной задержки, а выход соединен с тактовым входом матрицы, элемент задерж- Q кн, третий и четвертый распределители, выходы которых соединены соответственно с : адресными входами считывания строк и столбцов матрицы, а выходы всех элементов, памяти матрицы соединены с входами элементов ИЛИ, выход которого является выхо- S дом блока дискретной задержки.

1д

.

QiHrCH

Фиг. 2

Ts

IJ

10

TV

17

I

I

il

,1m

Jcnf.

| Устройство для определения логарифмического коэффициента ошибок дискретного канала связи | 1986 |

|

SU1411993A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1990-12-30—Публикация

1988-08-09—Подача