1

Изобретение относится к устройствам передачи дискретной информации и может использоваться для ан.ализа состояния телеграфных и телефонных ка налов связи,подверженных воздействию интенсивных неорганизованных и нацеленных помех,а также в адаптивных системах с автоматическим переключением каналов.

Известно устройство для контроля качества канала связи, содержащее . делитель тактовой частоты, первый выход которого подключен к входу вычитания реверсивного счетчика через первый элемент ИЛИ, к другим входам которого через последовательно соединенные блок регистрации, дешифратор и множители соответственно подключены выходы первого и второго счетчиков, к тактовым входам последних и к тактовым входам блока регистрации и дешифратора подключен второй выход делителя тактовой частоты, вход которого соединен с первым входом элемента И, к второму входу которого подключен инверсный выход RSтриггера, S-вход которого соединен с входом сложения реверсивного счетчика, который является входом ошибка устройства 1.

f Однако данное устройство имеет невысокую точность оценки состояния каналов связи с различной степенью группирования ошибок.

Целью изобретения является повышение точности оценки сосюяния каналов связи с различной степенью группирования ошибок.

Цель достигается тем, что в устрой10ство для контроля качества канала связи, содержащее делитель т.актовой частоты, первый выход которого подключен к входу вычитания реверсивного счетчика через первый элемент ИЛИ,

15 к другим входам которого через последовательно соединенные блок регистрации, дешифратор и множители соответственно подключены выходы первого и второго счетчиков, к тактовым

20 входам последних и к тактовым входс1М блока регистрации и дешифратора . подключен второй выход делителя тактовой частоты, вход которого соединен с первым входом элемента И, ко

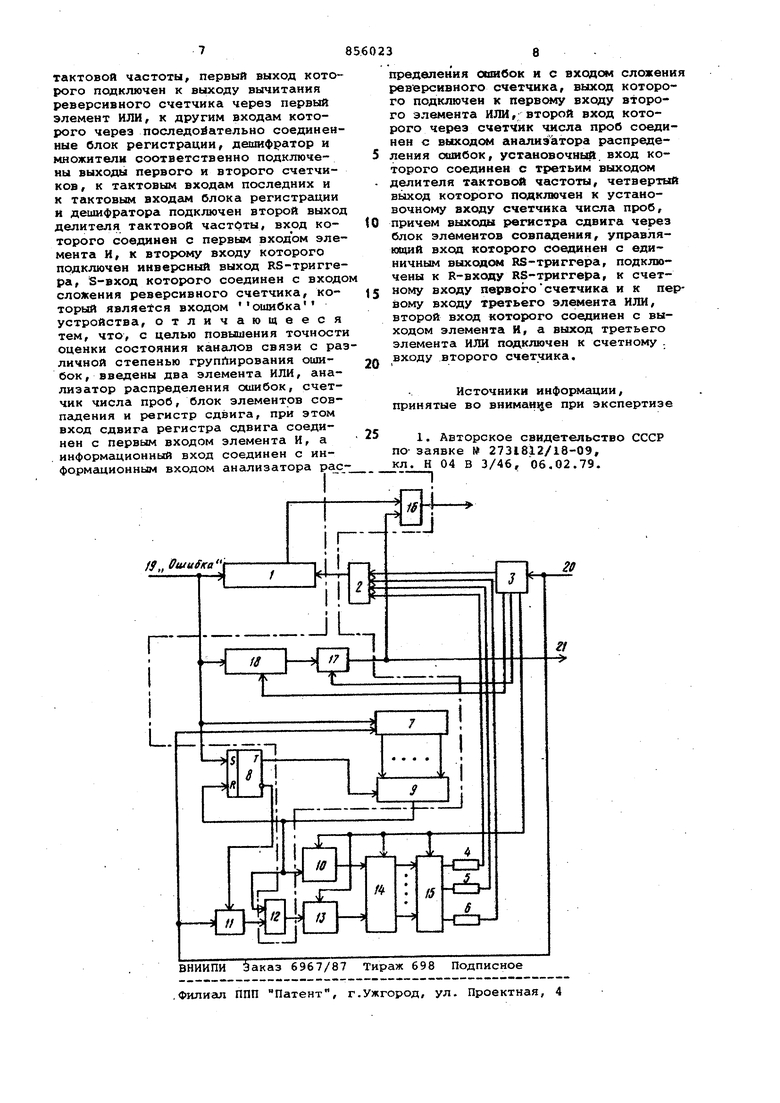

25 второму входу которого подк.точен инверсный выход RS-триггера, S-вход которого соединен с входом сложения реверсивного счетчика, который является входом ошибка устройства, 30 введены два элемента ИЛИ, анализатор распределения ошибок, счетчик .э lipoO, блок элементов совпгщеиия и {регистр сдвига, при этом вход елнига регистра сдвига соединен с первым входом элемента И, а информационный вход соединен с информационным входом анализатора распределения ошибок и с входом сложения реверсивного счетчика, выход которого подключен к первому входу второго элемента ИЛИ, второй вход которого через счетчик числа проб соединен с выходом анализатора распределения ошибок, установочный вход которого соединен с третьим выходом делителя тактовой частоты, четвертый выход которого подключен к установочному входу счетчика числа проб, причем выходы регистра сдвига Через блок ; лементов совпадения, управляющий вход которого соединенс единичным выходом RS-триггера, подключены к Н-входу RS-триггера, к счетному входу первого счетчика и к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход третьего элемеити ИЛИ подключен к счетному входу второго счетчика, ila чертеже представлена структурная электрическая схема п)едлагаемого устройства. Устройство содержит реверсивный счетчик 1, первый элемент 2 ИЛИ, делитель 3 тактовой частоты с переменным коэффициентом деления, множители 4 - 6, регистр 7 сдвига, RS-триггер 8, блок 9 элементов совпадения, первый счетчик 10, элемент 11 И, вто рой элемент 12 ИЛИ, второй счетчик 13, блок 14 регистрации, дешифратор 15, третий элемент 16 ИЛИ, счетчик 17 числа проб, аналиэатор 18 распределения ошибок; при этом на вход сложения реверсивного счетчика 1 по шине 19 поступают сигналы ошибка с выхода устройства обнаружения ошибок. Устройство также содержит вход 20 делителя.3 тактовой частоты, дополнительный выход 21 устройства. Устройство работает следукндим об разом. Входная реализация ошибок и безо шибочно принятых элементов в виде случайной последовательности (соответствующих ошибочным элемента1м и О(соответствующих правильно пр нятым элементгм)поступает по шине 1 на вход сложения реверсивного счетч ка 1,на информационный вход регистр 7 сдвига,на S-вход RS-триггера Jj Реверсивный счетчик 1 осуществля ет последовательный анализ поступаю щих по шине 19 сигналов. Если по ис течении некоторого времени разность между количеством импулЬсов, поступающих на вход сложения реверсивног счетчика 1 и вход вьлгч1итанич с выход первого элемента 2 ИЛИ превьидает установленное число А, то на его выходе появляет ля сигнал, поступаклций через элемент 16 ИЛИ на внешнюю аппаратуру перестройки радиосредств и свидетельствующий о непригодности для работы данного канала связи. Число А в реверсивном счетчике 1 уста. навливается в процессе проектирования, исходя из данной надежности оценки состояния канала связи, а постоянная составляющая порогового уровня задается частотой поступления сигналов с первого выхода делителя 3 тактовой частоты с переменным коэффициентом деления, на вход 20 которого подаются импульсы с синхронного распределителя приема. Одновременно последовательность ошибочно и безошибочно принятых элементов поступает на информационный вход регистра 7 сдбига, разрядность которого равна г (где г - интервал пакетирования), а на вход сдвига данного регистра поступают сигналы с синхронного распределителя приема, осуществляя, тем самым, запись информации в регистр 7 сдвига и ее сдвиг. При наличии в случайной последовательности, поступающей с устройства обнаружения ошибок, ошибочно принятого элемента, сигнал , поступая на З-вход RS-триггера 8, устанавливает последний в единичное состояние. Единичный потенциал с единичного выхода RS-триггера 8, подаваемый на управляющий вход блока 9 элементов совпадения, разрешает опрос показаний регистра 7, сдвига, выходы разрядов которого подключены к входам блока 9 элементов совпадения. Сигнал на выходе блока 9 элементов совпадения появляется в случае, если на управлякицем входе этого блока имеется разрешающий сигнал с единичного выхода RS-триггера 8, а во всех г-разрядных регистра 7 сдвига записаны нули. Таким образом, в момент прихода ошибки в младший разряд регистра 7 сдвига записана , соответствующая началу возникновения пакета ошибок, а в остёшьных разрядах регистра 7 сдвига-нули. Поступакяцая двоичная последовательность сдвигается каждым тактовым импульсом с синхронного распределителя приема. Причем, если в поступающей двоичной последовательности присутствует пакет ошибок с интервалом г пакетирования, то хотя бы в одном разряде регистра 7 . Последосдвига присутствует вательная запись в регистр 7 сдвига двоичной информации и ее сдвиг продолжаются до окончания пакета ошибок с интервалом г пакетирования, т.е. до начсша безошибочного интервала, а именно, до нгшичия во всех г-разрядах регистра 7 сдвига нулей. В

ЭТОМ случав на выходе блока 9 элементов совпадения, входы которого соединены с выходами соответствующих разрядов регистра, появляется сигнал, поступающий на R-вход RS-тригера 8, устанавливая последний в нулевое состояние, тем сакым сигналом с единичного выхода RS-триггвра 8 отключается блок 9 элементов совпадения; на счетный вход первого счетчика 10, в результате чего последний подсчитывает количество пакетов с критерием г пакетирования во входной последовательности; через элемент 12 ИЛИ на счетный вход второго счетчика 13, записывая в последний единицу и фиксируя, тем самым, начало промежутка между пакетами.

Сигнал с инверсного выхода RSтриггера 8, подаваемый на первый вход элемента 11 И, разрешает поступление тактовых импульсов с синхронного распределителя приема через последовательно соединенные элемент 11 И, второй элемент 12 ИЛИ на счетный вход второго счетчика 13. Последний подсчитывает число импульсов, пропорциональное длительности текущего интервала безошибочного приема (интервала безошибочного приема между пакетами ошибок, выделенных с интервалом г пакетирования).

Далее устройство работает аналогично известному. В моменты времени, определяемые сигналами с второго выхода делителя 3 тактовой частоты с переменным коэффициентом деления, поступающими на вход блока 14, ,регистрации, последний определяет среднюю длительность безошибочного интервала

X. X J, / N

где A-jj- показания второго счетчика 13,

N - показания первого счетчика 10.

В зависимости от величины X на соответствующем выходе дешифратора 15 появляется сигнал, поступающий через один из множителей 4 - б и элемент 2 ИЛИ на вход вычитания реверсивного счетчика 1, формируя, тем самым, переменную составляющую порогового уровня. В отличие от известного устройства,переменная составляющая порогового уровня в предлагаемом устройстве формируется с учетом выделения пакетов ошибок с интервалом г пакетирования/ что позволяет более точно оценивать качество дискретного канала связи.

Одновременно с изложенным процессом работает схема, состоящая из последовательно включенных анализатора 18 распределения ошибок и счетчика 17 числа проб. При воздействии организованных помех в интервале анализа Т анализатор 18 распределения ошибок, вход которого подключен к шине 19 входных сигналов Ошибка , выдает импульсный сигнал на счетчик 17 числа проб, который предназначен для повьвления достоверности оценки наличия организованных помех.

Анализатор 18 распределения ошибок может быть выполнен, например, на основе сдвигового регистра с дешифратором, фиксирующим определенные состояния и периодически сбрасывающимсяв нулевое состояние. Период Т анализа распределения ошибок определяется периодом сигнала, поступающего с третьего, выхода делителя 3 тактовой частоты и выбирается из ус5ловия Т Т где Т ДСП средняя длительность всплеска ошибок. Счетчик 17 числа проб периодически сбрасывается в нулевое состояние сигналом, поступающим с периодом TO с четверСтого выхода делителя 3 тактовой частоты. Период TO устанавливается кратным периоду Т , т.е. , где ,3,... - число проб сигнала наличия организованных помех на выходе анализатора 18 распределения

5 ошибок.

Если за интервал Т анализа количество импульсов на выходе анализатора 18 распределения ошибок превышает установленное с помощью счет0чика 17 числа проб, то счетчнк 17 числа проб выдает сигнал, который, поступая через элемент 16 ИЛИ на внешнюю аппаратуру, свидетельствует о забраковании канала и, поступая с

5 дополнительного выхода 21 на внешнюю аппаратуру пересройки радиосредств, свидетельствует о наличии организованных помех. По этому сигналу адаптивная радиолиния перестра0ивается на другой пакет волн или другую частоту, далеко отстоящую от рабочей, пораженной организованными помехами. Тем самьпи снижаются взаимные помехи радиостанциям, работающим на одной группе частот,,сохра5няется непрерывность и повышается устойчивость связи.

Таким образом, предложенное устройство повышает надежность оценки качества контролируемых каналов связи

0 за счет более точной оценки степени группирования по величине средней длительности безошибочного приема, а именно, за счет определения безошибочного интервала между пакетами,

5 образованньоми с заданным интервалом г пакетирования, повышает надежность .связи и уменьшает взаимные помехи радиостанциям, работающим на одной и той же группе частот.

0

Формула изобретения

Устройство для контроля качества канала связки, содержащее делитель

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля качества канала связи | 1990 |

|

SU1716610A2 |

| Устройство для контроля качестваКАНАлОВ СВязи | 1979 |

|

SU794743A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

| Устройство для контроля канала связи с переменными параметрами | 1980 |

|

SU924882A1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1830186A3 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 1991 |

|

RU2050693C1 |

| Устройство для контроля качества канала связи | 1990 |

|

SU1709544A1 |

| Генератор потока ошибок | 1979 |

|

SU855968A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

Авторы

Даты

1981-08-15—Публикация

1979-10-22—Подача