О

ю о со

S

Изобретение относится к ргдиотехнике и технике связи и может использоваться в устройствах когерентной обработки фазо- манипулированных сигналов.

Цель изобретения - обеспечение син- фазности входного и выходного сигналов при фазовой манипуляции- входного сигнала 180°.

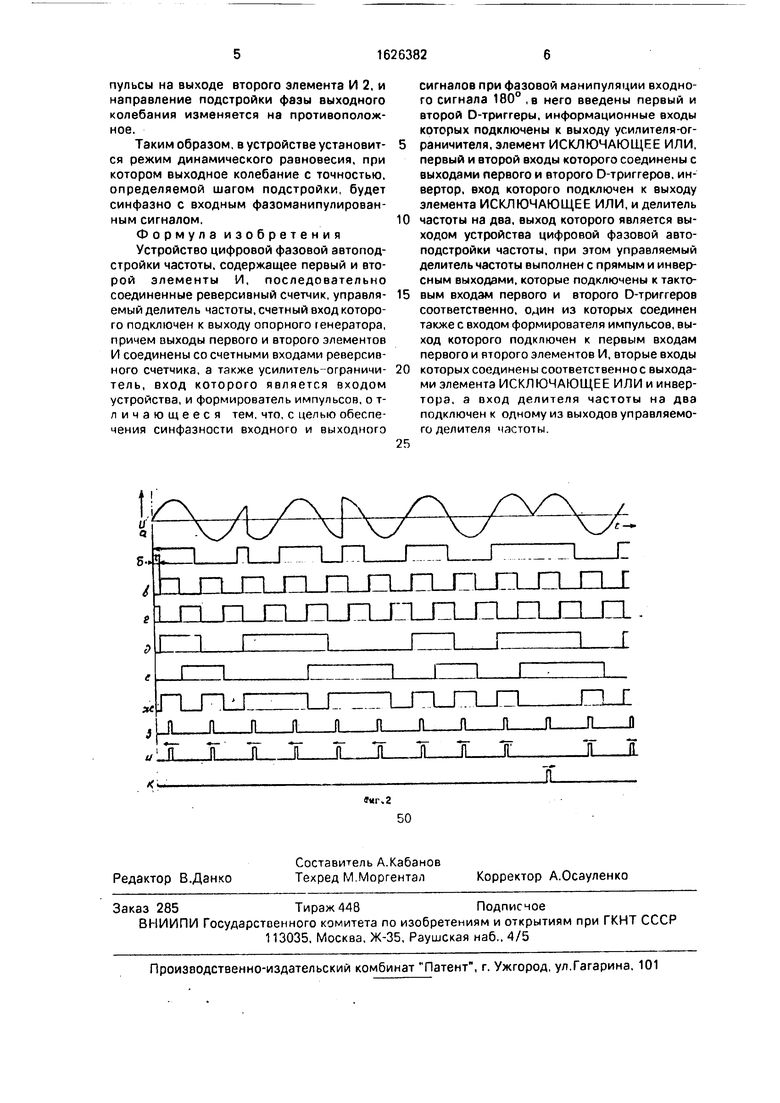

На фиг. 1 представлена структурная электрическая схема устройства цифровой фазовой автоподстройки частоты; на фиг. 2 - эпюры напряжений в различных точках схемы, поясняющие ее работу.

Устройство (фиг.1) содержит первый 1 и второй 2 элементы И, реверсивный счетчик 3, управляемый делитель 4 частоты, опорный генератор 5, усилитель-офэничитель G, формирователь 7 импульсов, первый 8 и второй 9 D-триггеры, элэмент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, инвертор 11. делитель 12 ча- стоты на два.

Устройство работает следующим образом.

Особенность работы устройства заключается в том, что для определения направ- ления подстройки фазы выходного колебания входной фазоманипулирован ный сигнал стробируется дважды за пол период, а само направление подстройки фазы находится путем сравнения знаков резуль татов первого и второго стробировьния.

Рассмотрим работу устройства для случая , когда вы одное колебание о гстае г на гот входного фазоманипулированного сиг нала Временпыедиаграммы иллюстрируют наиболее общий случай, когда длительность посылки фазоманипулированного сигнала не кратна периоду несущей L-. манипуляция производится при произвольном значении фазы несущей. Входной фазоманипулпро ванный сигнал (фиг.2а) поступает на усилитель-ограничитель 6. Полученный после ограничения двоичный сигнал (фиг.б подается на информационные входы первого 8 и второго 9 D-триггеров На тактовые входы триггеров поступают противофазные последовательности импульсов удвоенной частоты (фиг.2в,г) с выходов управляемого делителя 4 частоты. Передние фронты первой последователььости импульсов (фиг 2в) совпадают с фронтами и срезами выходного двоичного сигнага всего устройства (не показаны). В моменты, соответствующие передним фронтам этих последовспе/ ьно стей, первый 8 и второй 9 D-триггеры сраба- тывают, и таким образом осуществляется стробирование ограниченного фазоманипулированного сигнала Результаты стробиро- вания (фиг.2д,е) с выходов этих триггеров поступают на элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 10. Напряжение с его выхода (фиг.2ж) подается на вторые входи элементов И 1 и 2, на первый элемент И 1 непосредственно, а на второй элемент И 2 через инвертор 11. На первые входы первого 1 и второго 2 элементов И подаются короткие импульсы удвоенной частоты (фиг,2з) с выхода формирователя 7 импульсов. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и элементы И 1,2 с инвертором 11 выполняют операцию сравнения результатов стробировапия ограниченного входного фаосманипулированного сигнала.

Импульсы, появляющиеся нэ выходах первого 1 и второто 2 элементов И, являются сигналами, указывающими 1ре5уемое направление подстройки фазы выходного колебания. В рассматриваемом случае принято, что с фришами (моментами перехода через среди; . ,ровень) выходного колебания совмещены передние фронты первой последовательности удвоенной частоты (фиг 2о) На фиг 2 показано, что короткие импульсы удвоенной частоты (фиг2з) поступают на пероыи 1 и второй 2 элементы И на интервале времени с момента появления переднего фронта первой по ледова- тельности удвоенной частой до момента пия -ления перед иго фронта второй последовательности ,двоенн ч1 частоты (фиг 2г) При этих условиях к-: требуемое направление подстройки фа.;ы в сторону отстаивания у к ззывают импульс i ьа выхо/е первого элемента И 1 (фиг.2и).

Оедуег отметить, m на выходе элементов И 1,2 из интервале вре ени, следующем непосрсдсгвеннс за момонтом манипуляции, иозмохно ние одиночных ложи X импульсов Пример такого гпж- ного импупьса показан на диаграмме фиг 2к) Но эти миночные импульсы не нарушают ртботу устройства ттк КЗ импуль- I,L с выходов элеменгоь 11 1 2 поступают на реверсивный счетчик 3 и усредняются

Посигпг ci переполнения реверсивного счетчика 3 происходи однократноеуне- лич иие коэффициента деления управлпег- .ого депителя 11 част ;ты Фронты последовательностей уд.юи1 .ой частоты на его выходе длигсштся и с оьону запаздывания Соотве LijfcHHO ИЗМРНТСТСЯ фазп колебания но выходе делителя 12. Разность фаз г ежду входным фоз манипулиоопэн- HL Ni (.игнаюм и выхг;,;чым сигнэ/юм устройства умет шзетсп О1 ji процесс подстроки происходи до тех пор, пока по- ГПР очередногс; мгу ьса переполнения реверс lEHoro 3 выходное колебание из отстающего HP LTPH г -пер-жающим. Со- OTLOTLTBCKHO r Ю1ЦИМИ импульсы на выходе второго элемента И 2, и направление подстройки фазы выходного колебания изменяется на противоположное.

Таким образом, в устройстве установится режим динамического равновесия, при котором выходное колебание с точностью, определяемой шагом подстройки, будет синфазно с входным фазоманипулирован- ным сигналом.

Формула изобретения Устройство цифровой фазовой автоподстройки частоты, содержащее первый и второй элементы И, последовательно соединенные реверсивный счетчик, управляемый делитель частоты, счетный вход которого подключен к выходу опорного генератора, причем выходы первого и второго элементов И соединены со счетными входами реверсивного счетчика, а также усилитель-ограничитель, вход которого является входом устройства, и формирователь импульсов, о т- личающееся тем. что, с целью обеспечения синфазности входного и выходного

0

5

0

сигналов при фазовой манипуляции входного сигнала 180° , в него введены первый и второй D-триггеры, информационные входы которых подключены к выходу усилителя-ограничителя, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены с выходами первого и второго D-триггеров. инвертор, вход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, и делитель частоты на два, выход которого является выходом устройства цифровой фазовой автоподстройки частоты, при этом управляемый делитель частоты выполнен с прямым и инверсным выходами, которые подключены к тактовым входам первого и второго D-триггеров соответственно, один из которых соединен также с входом формирователя импульсов, выход которого подключен к первым входам первого и второго элементов И, вторые входы которых соединены соответственно с выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и инвертора, а вход делителя частоты на два подключен к одному из выходов управляемого делителя частоты

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифровой фазовой автоподстройки частоты | 1990 |

|

SU1732466A1 |

| Устройство восстановления несущей фазоманипулированного сигнала | 1990 |

|

SU1786659A1 |

| Демодулятор фазоманипулированного сигнала | 1987 |

|

SU1536506A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1748249A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2004 |

|

RU2257679C1 |

| Демодулятор фазоманипулированных сигналов | 1982 |

|

SU1058084A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ФАЗОМАНИПУЛИРОВАННОМУ СИГНАЛУ | 1993 |

|

RU2084080C1 |

| Фазовый манипулятор | 1983 |

|

SU1095440A1 |

| Устройство для передачи и приема информации по двупроводной линии связи | 1990 |

|

SU1836709A3 |

Изобретение относится к радиотехнике и технике связи и может исполь-зовги ся при когерентной обработке фазоманипули- рованных сигналов. Цель изобретения - обеспечение синфазности входного и выходного сигналов при фазовой манипуляции входного сигнала-180°. Устройство содержит первый 1 и второй 2 элементы И, реверсивный счетчик 3, управляемый делитель 4 частоты, опорный генератор 5, усилитель- ограничитель 6, формирователь импульсов 7, первый 8 и второй D-триггеры, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, инвертор 11, делитель 12 частоты на два. Цель достигается за счет введения D-триггеров, элемента ИС- КЛ ОЧЛЮЦ1Е ИЛИ, ингг-QTOpd и делителя частоты на два, что позволяет для определения направления подгтргйкм фтзы стробчл- р о в а ., входной -. и г и ч п дпажды за полупериод i поспедую у сравнением ре зулыатов глрэбирования Гил.

| Устройство для цифровой фазовой автоподстройкичАСТОТы | 1979 |

|

SU853796A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-07—Публикация

1987-06-15—Подача