1

Изобретение относится к технике связи и может быть использовано в однокпнальньгх и многоканальных системах связи с частотно-разнесенными канальны1-1И сигналами и фазоразност- ной модуляцией, работающих по КВ-ка- налам или составными каналами связи

Цель изобретения - повышение точности синхронизации в каналах с селективными замираниями.

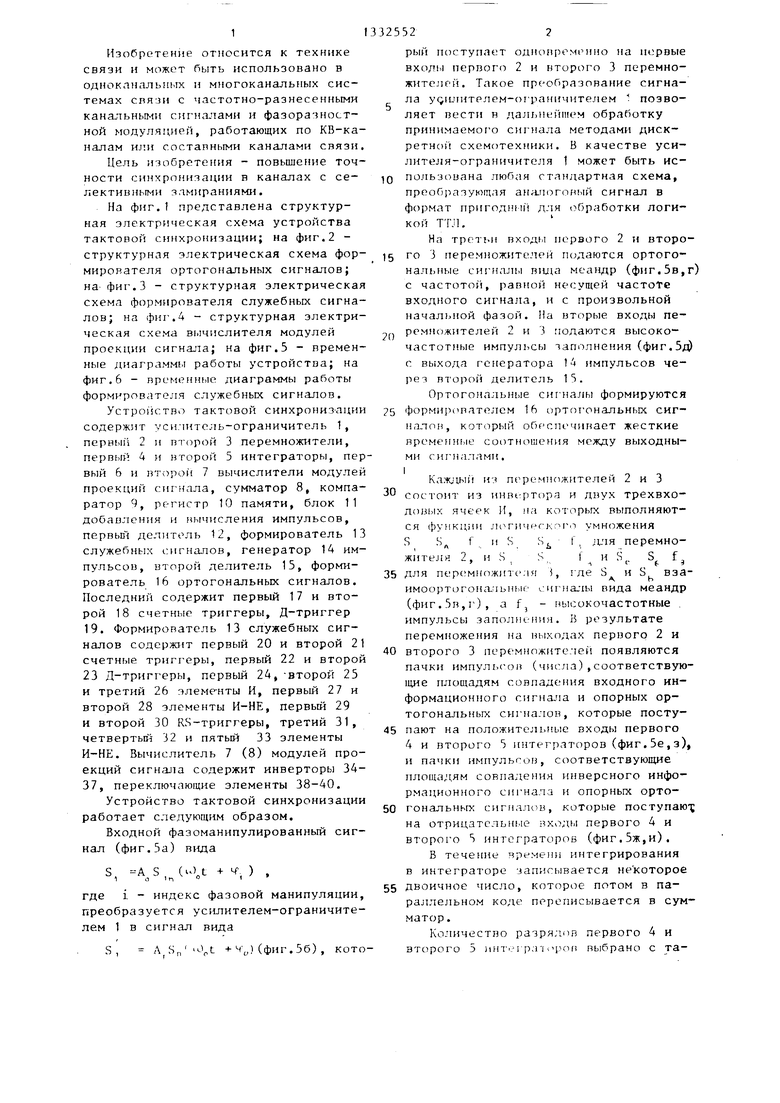

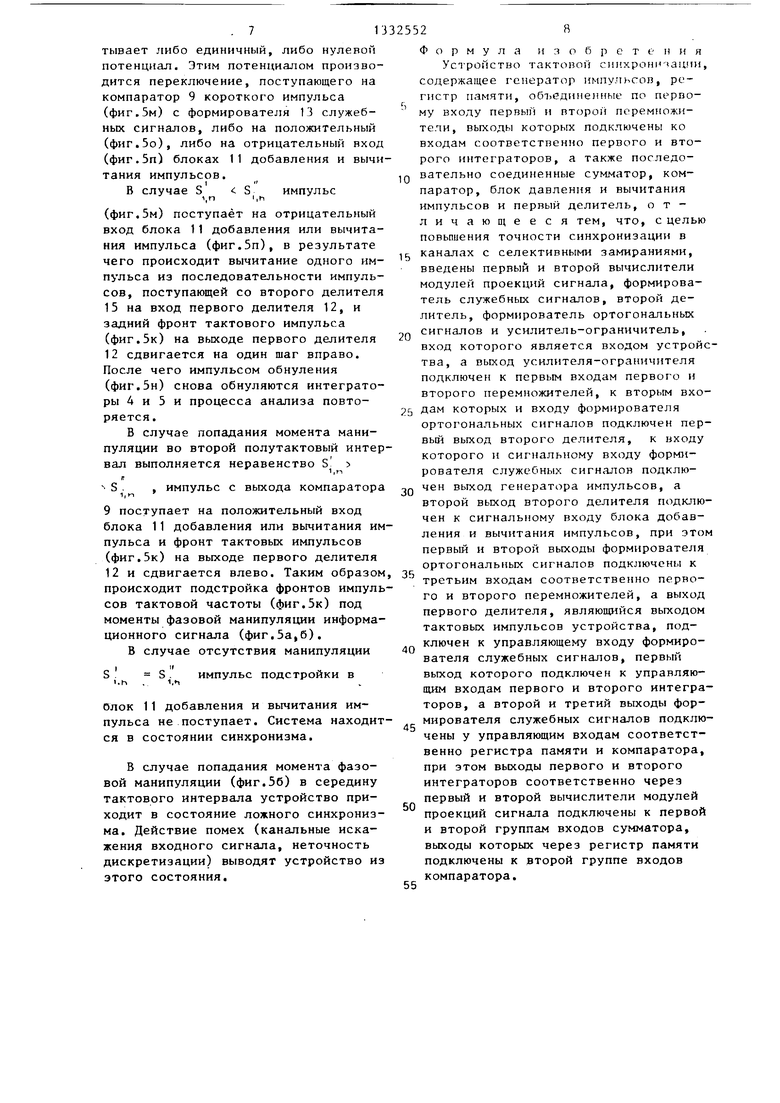

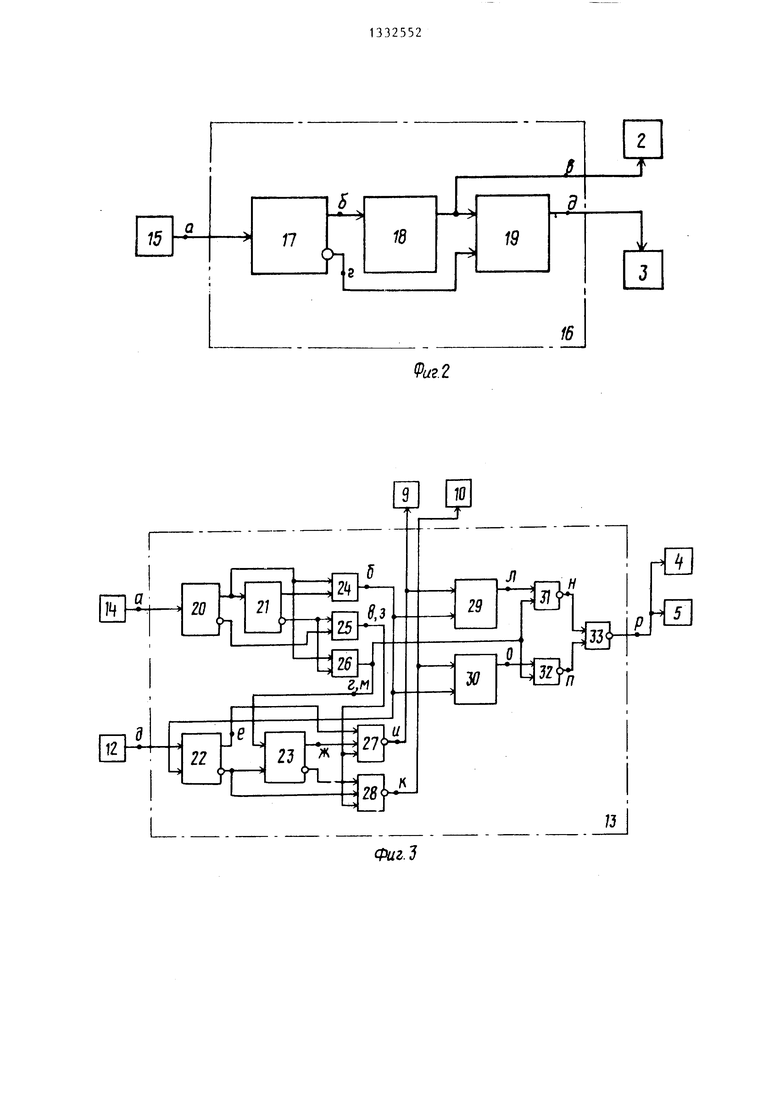

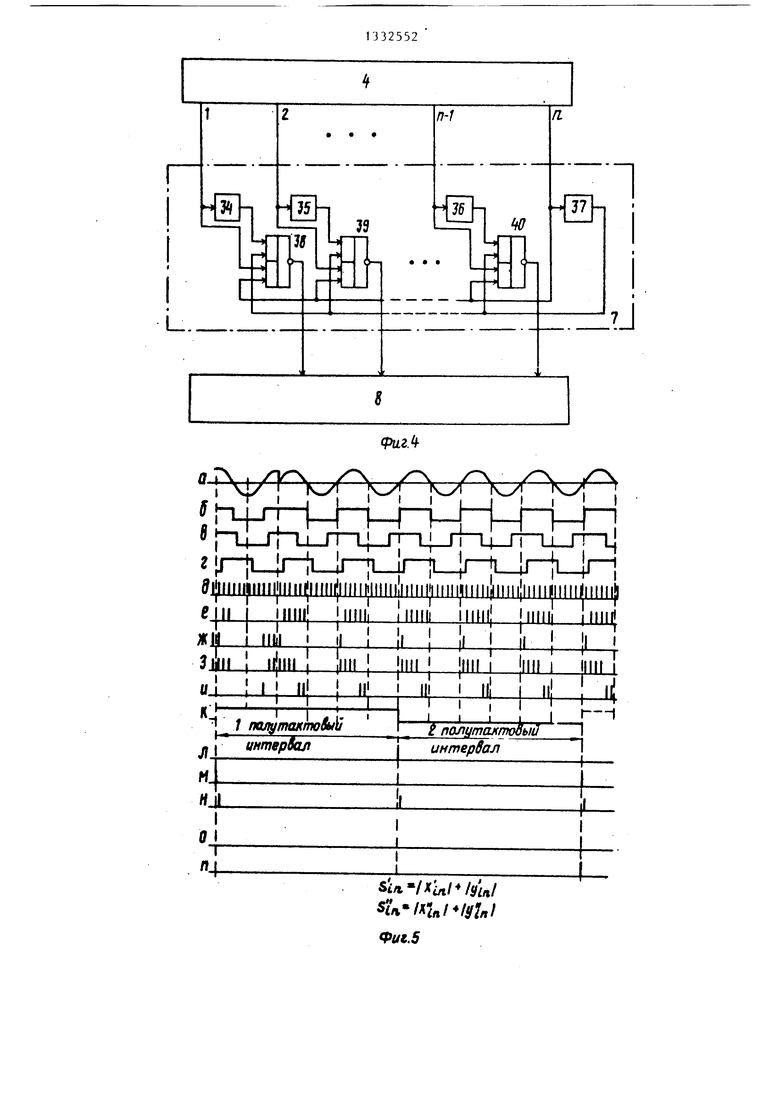

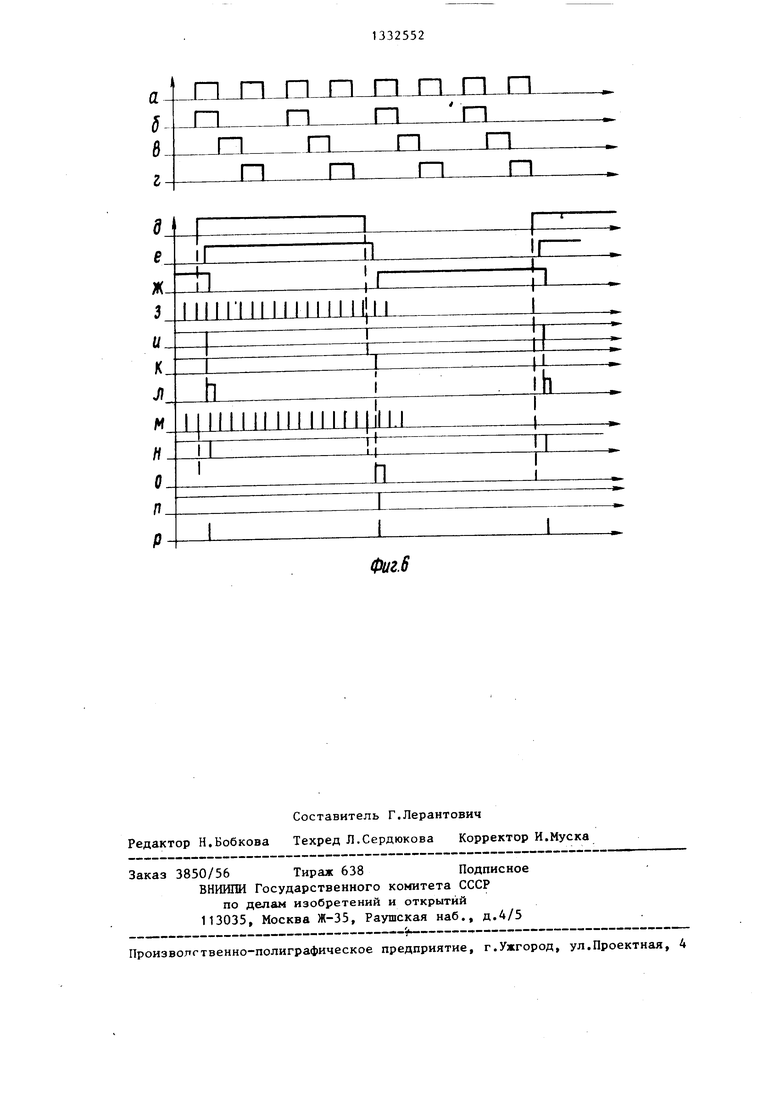

На фиг.1 представлена структурная электрическая схема устройства тактовой синхронизации; на фиг.2 - структурная электрическая схема формирователя ортогональных сигналов; на фиг.3 - структурная электрическая схема формирователя служебньсх сигналов; на фиг.4 - структурная электрическая схема вычислителя модулей проекции сигнала; на фиг.5 - временные диаграммы работы устройства; на фиг.6 - временшие диаграммы работы формирователя служебных сигналов.

Устройство тактовой синхрониз-ации содержит усилитель-ограничитель 1, первыГ 2 и второй 3 перемножители, первый 4 и второй 5 интеграторы, первый 6 и второй 7 вычислители модулей проекций сигнала, сумматор 8, компаратор 9, регистр 10 памяти, блок 11 добавления и вычисления импульсов, первьп делитель 12, формирователь 13 служебных 1:игналов, генератор 14 импульсов, второй делитель 15, формирователь 16 ортогональных сигналов. Последний содержит первый 17 и второй 18 счетные триггеры, Д-триггер 19. Формирователь 13 служебных сигналов содержит первый 20 и второй 21 счетные триггеры, первый 22 и второй 23 Д-триггеры, первый 24, -второй 25 и третий 26 элементы И, первый 27 и второй 28 элементы И-НЕ, первый 29 и второй 30 RS-триггеры, третий 31, четвертьй 32 и пятый 33 элементы И-НЕ. Вычислитель 7 (В) модулей проекций сигнала содержит инверторы 34- 37, переключающие элементы 38-40.

Устройство тактовой синхронизации работает следующим образом.

Входной фазоманипулированный сигнал (фиг.За) вида

S, -As, , ) .

где i - индекс фазовой манипуляции, преобразуется усилителем-ограничителем 1 в сигнал вида

S, Л -нЧу) (фиг.Зб) , кото325522

рый поступает одновременно на первые входы первого 2 и второго 3 перемножителей. Такое преобразование сигнала удилителем-ог раничителем позволяет вести в дальнейшем обработку принимаемог о сигнала методами диск- peTHoi i схемотехники. В качестве уси- 1штеля-ограничителя 1 может быть исTQ пользована любая стандартная схема, преобразун)|дая ана.поговый сигнал в формат пригод}1ий для обработки логикой ТТЛ.

На трет1 и входы первого 2 и второ- 15 го 3 перемножителей П(;даются ортогональные сигналы вида меандр (фиг.5в,г) с частото, равной несущей частоте входного сигнала, и с произвольной начальной фазой. На вторые входы перемножителей 2 и 3 подаются высокочастотные импульсы заполнения (фиг.5д) с выхода генератора 14 импульсов через второй делитель 15.

Ортогональные сигналы формируются

25 формирователем 16 ортогональных сиг- налои, который обеспечивает жесткие нременн 1е соотношения между выходными сиг-налами.

Каж, из перемножителей 2 и 3

20

30

состоит из инвертора и двух трехвходов1)х ячеек И, на которых выполняются функции jun-n4(: rj4or-o умножения S S f II S ь . 1- 1Я перемно- жителн 2, и S , S f и S , S f

для пер(множите,1я i, где S и S вза- имоортого 1а.;1ьныс cHDia- ibi вида меандр (фиг.5в,г), а fj - высокочастотные импульсы заполнения. В результате перемножения на выходах первого 2 и

второго 3 перемножителей появляются пачки импул1( ов (числа) ,соответствую- 1дие площадям совпадения входного информационного сигнала и опорных ортогональных сигналов, которые поступают на положительные входы первого 4 и второго 5 1снтеграторов (фиг, 5е, з), и пачки импульсов, соответствующие площадям совпадения инверсного информационного сигнала и опорных ортогональньп-; сигналов, которые поступаю- на отрицательные входы первого 4 и второго 5 интеграторов (фиг.5ж,и).

В течение времени интегрирования в интеграторе запис11 вается некоторое

двоичное число, которое потом в параллельном коде переписывается в сумматор.

Ко.чичество разрялшт первого 4 и второго 5 ) ( pofi выбрано с та. 3 133

КИМ расчетом, чтобы они не перепел-- нялись 3 время ннтегрированпя, равное Т/2 - половине длительности одной элементарной посылки, даже при полном совпадении перемножаемых сигналов. Обнуление первого А ивторого5 интеграторов производится в конце каждого, интервала интегрирования импульсами, поступающими из формирона- теля 13 служебных сигналов. Последний необходим для формирования импульсов обнуления первого А и второго 5 интеграторов, импульсов считывания для компаратора 9 и импульсов записи для регистра 10 памяти.

Формирователь 13 служебных сигналов работает следующим обраюм.

По сигнальному входу с г(;нератора 14 импульсов на формирователь 13 служебных импульсов поступают импульсы высокой частоты вида меандр (фиг.ба) При помощи делителя на четыре (счетные триггеры 20 и 21) и элементов И 24-26 формируются сдвинут(,е одна относительно другой тактовые после- довательности f (фиг.бб), f (фиг.бв)

и f (фиг.бг). По управляющему вход на формирователь поступают тактовые импульсы с периодом, равным длител)- ности информационной посьшки F, (фиг.бд). На Д-триггерах 22 и 23 осуществляется временная привязка фронтов тактовых импульсов соответственно к частотам f (фиг.бе) и f (фиг.бж). Площадь несовпадения этих сигналов (фиг,бе,ж) стробируется частотой f (фиг,6з,м), в результате чего на выходе первого элемента И-НЕ 27 вьщеляются импульсы переднего, а на выходе второго элемента И-НЕ 28 импульсы заднего фронта тактовых импульсов F (фиг.6и,к), поступающие соответственно на компаратор 9 и регистр 10 памяти. На RS- триггерах 29 и 30 (фиг . 6л, о) и третьем 31 и четвертом 32 элементах И-НЕ происходит перепривязка переднего и заднего фронтов F, к f , , что эквивалентно временной задержке фронтов. Задержанные передний (фиг.бн) и задний (фи1 .6п) фронты объединяются и инвертируются на пятом элементе И-НЕ 33. Полученный сигнал (фиг.бр) является обнуляющим сигналом для первого 4 и второго 5 интеграторов. Благодаря временной задержке обнуление интеграторов 4 и 5 происходит позже записи кода в регистр 10 памя

i,

5

0

5

0

5

0

5

ти и позже считывания импульса подстройки из компаратора 9.

Импульсы обнуления интеграторов 4 и 5 (фиг.Зн) соответствуют фронтам импульсов тактовой частоты (фиг.Зк), получаемой с выхода первого делителя 12. Они задают для первого 4 и второго 5 интеграторов интервалы интегрирования, соответствующ({е первому и второму полутактовым интервалам.

В первом 4 и втором 5 интеграторах к концу интервала интегрирования записываются двоичные коды чисел, соответствующие разности чисел импульсов, поступаюии1х по отрицательному и положительному входам интеграторов.

Знаки кодов чисел, записанньк к кон};у интервала интегрирования D первом 4 и втором 5 интеграторах, определяются на знаковых (последних) разрядах интеграторов. Выходы кодов 1гх разрядов первого 4 и второго 5 ин- TerjiaTojioB, а также их знаковых разрядов подключены к вычислителям 6 и 7 модулей проекций сигнала, каждый из которых представляет собой параллельную коммутационную схему, построенную на инверторах 34-37 и собственно переключающих элементах 38-40. Управление последними осуществляется сигналом с последнего, знакового разряда интегратора. В случае накопления положительного числа в интеграторе к концу интервала интегрирования его знаковый разряд остается в состоянии О и на выходах вычислителя 6 (7) появляется тот же двоичньш код числа, что и на выходе интегратора. Если же число, записанное в интеграторе - отрицательное, то знаковый разряд интегратора находится в состоянии 1 (типовая особенность работы цифровых интеграторов, построенных на реверсивных счетчиках) и на выходах вычислителя 7 (6) появляется инверсный или обратный двоичный код числа по отношению к двоичному коду числа на выходе интегратора. В первом случае сигналы с выходов интегратора проходят через верхнее плечо переключающих элементов 38-40, подвергаясь двойному инвертированию, но втором случае - через нижнее плечо с инверсией.

Вычислители 6 и 7 модулей проек- сигнала необходим для того.

математический

чтобы реаличопатг. горитм.

В зависимости от потенциала на выходе знакового разряда интегратора

4(5) чсреч иычислитель 7 (6) модуля проекции сигнала на соответствуюЕЦие входы сумматора 8 с выходов интегра- торг 4 (5) подается прямой или дополнительный код числа. Перепись обратного кода числа в сумматор 8 точностью до - 1 рагзноценна переписи дополнительного кода числа или математической операции вычисления модуля отрицательного числа. При высокой частоте счетньк импульсов неточностью вычисления модуля отрицательного числа, вызванной переписью обратного кода вместо дополнительного, можно преясбречь. Таким образом, происходит вычисление модуля кода числа, записанного в интеграторе 4 (5),

В сумматоре 8 происходит сложение кодов -чисел, поступивших с выходов вычислит е;1ей Ь и 7 модулей проекций сигиа.ма. В первого полутактм- вог о HHTepHrVia-, соответствующего первому HHTcpii. uiy интегрирования (фиг.Зк), код суммы с выхода сумматора 8 перепнср-щастся в регистр 10 па- мятт импу:1ь - ом (фиг.5л), поступаю1дим из форми -1онателя 13 служебных сигналов. После чего импульсом обнуления (фиг.тн) обнуляются интеграторы 4 и

5и в них начинают накапливаться новые коды чисел. В конце второго полутактового интервала, соответствующего второму интервалу интегрирования, новый код суммы с выходов сумматора 8 поступает на первую группу входов компаратора 9, на вторую группу входов которого поступают коды суммы из регистра 10 памяти. В компараторе 9 происходит сравнение кодов сумм, полученных на первом и втором полутактовьк интервалах. В конце второго пчлутактового интервала на одном из 1 ыходов компаратора 9 появляется коротки/ импульс (фиг.5о,п), поступающий в узел добавления и вычитания импульсов. Этот импульс (фиг.5о,п) свидетельствует о преобладании того или иного кода суммы.

В предлагаемом устройстве характерной особенностью интеграторов 4 и 5, построенн1,1х на реверсивньк счетчиках, являегсн то, что сумма модулей кодов чисел, получаемых в интеграторах 4 и

1332552 ал10

15

20

25

30

35

тоянной и не зависит от фазовых соот ношений между входным сигналом (фиг.5а,б) и парой опорных ортого- нальцых сиг налов (фиг.5в,г) при условии, что в интервале интегрирования отсутствует момент фазовой манипуляции входного сигнала.

В случае присутствия в интервале интегрирования момента манипуляции интервал интегрирования как бы разбивается на два подинтервала и каждо му подинтервалу ставится в соответствие свой вектор. Векторная сумма этих двух векторов есть условный вектор входного сигнала по всему интервалу интегрирования н случае присутствия на этом интервале фазовой манипуляции. В этом случае сумма его проекций, или сумма кодов чисел, записан ных в интеграторах, оказывается меньше суммы проекций входного сигнала, не содержащего в интервале интегрирования момента фазонс й манипуляции.

Таким образом, сравнение сумм модулей проекций сигнала дает возможность определять направление подстройки фазы импульсов тактовой частоты первого де,т1ителя 12 (фиг.Зк).

В пред-пагаемом устройстве знак расстройки определяеюя из неравенства .

где

1, г

X

I +

X

+ IV,

40

45

50

55

- проекция вектора одно- канального сигнала на опорную ось Cnu- t на первом полутактовом интервале;

Х, - проекция вектора одно- канального сигнала на опорную ось на втором полутактовом

интервале. I

1 - проекдая вектора одно- канального сигна.па на опорную ось на первом полутактовом интервале;

у - проекция вектора одно- канального сигнала на опорную ось Cnui,t на втором полутактовом интервале.

В результате сравнения двух кодов

чисел S

) X

I и S

5 является величиной пос- 1 X 1 +1, компаратор 9 выраба

32552 10

15

20

25

30

тоянной и не зависит от фазовых соотношений между входным сигналом (фиг.5а,б) и парой опорных ортого- нальцых сиг налов (фиг.5в,г) при условии, что в интервале интегрирования отсутствует момент фазовой манипуляции входного сигнала.

В случае присутствия в интервале интегрирования момента манипуляции интервал интегрирования как бы разбивается на два подинтервала и каждо- му подинтервалу ставится в соответствие свой вектор. Векторная сумма этих двух векторов есть условный вектор входного сигнала по всему интервалу интегрирования н случае присутствия на этом интервале фазовой манипуляции. В этом случае сумма его проекций, или сумма кодов чисел, записанных в интеграторах, оказывается меньше суммы проекций входного сигнала, не содержащего в интервале интегрирования момента фазонс й манипуляции.

Таким образом, сравнение сумм модулей проекций сигнала дает возможность определять направление подстройки фазы импульсов тактовой частоты первого де,т1ителя 12 (фиг.Зк).

В пред-пагаемом устройстве знак расстройки определяеюя из неравенства .

5

где

1, г

X

I +

X

+ IV,

0

5

0

5

- проекция вектора одно- канального сигнала на опорную ось Cnu- t на первом полутактовом интервале;

Х, - проекция вектора одно- канального сигнала на опорную ось на втором полутактовом

интервале. I

1 - проекдая вектора одно- канального сигна.па на опорную ось на первом полутактовом интервале;

у - проекция вектора одно- канального сигнала на опорную ось Cnui,t на втором полутактовом интервале.

В результате сравнения двух кодов

чисел S

) X

I и S

тывает либо единичный, либо нулевой потенциал. Этим потенциалом производится переключение, поступающего на компаратор 9 короткого импульса (фиг.5м) с формирователя 13 служебных сигналов, либо на положительный (фиг.Зо), либо на отрицательный вход (фиг.Зп) блоках 11 добавления и вычитания импульсов.

В случае S

S

1,М

импульс

(фиг.5м) поступает на отрицательный вход блока 11 добавления или вычитания импульса (фиг.Зп), в результате чего происходит вычитание одного импульса из последовательности импульсов, поступающей со второго делителя 15 на вход первого делителя 12, и задний фронт тактового импульса (фиг.Зк) на выходе первого делителя 12 сдвигается на один шаг вправо. После чего импульсом обнуления (фиг.Зн) снова обнуляются интеграторы 4 и 3 и процесса анализа повторяется .

В случае попадания момента манипуляции во второй полутактовый интервал выполняется неравенство S

1,n

S ,

1,n

, импульс с выхода компаратора

9 поступает на положительный вход блока 11 добавления или вычитания импульса и фронт тактовых импульсов (фиг.Зк) на выходе первого делителя 12 и сдвигается влево. Таким образом, происходит подстройка фронтов импульсов тактовой частоты (фиг.Зк) под моменты фазовой манипуляции информационного сигнала (фиг.За,б).

В случае отсутствия манипуляции

: g

I.

импульс подстройки в

блок 11 добавления и вычитания импульса не поступает. Система находится в состоянии синхронизма.

В случае попадания момента фазовой манипуляции (фиг.5б) в середину тактового интервала устройство приходит в состояние ложного синхронизма. Действие помех (канальные искажения входного сигнала, неточность дискретизации) выводят устройство из этого состояния.

Формула изобретения Устройство тактовой си1 хрони ации, содержащее генератор импульсов, регистр памяти, об1)единелкые по первому входу первый и второй псремпожи- тели, выходы которых подключены ко входам соответственно первого и второго интеграторов, а также последовательно соединенные сумматор, компаратор, блок давления и вычитания импульсов и первый делитель, отличающееся тем, что, с целью повьпиения точности синхронизации в каналах с селективными замираниями, введены первый и второй вычислители модулей проекций сигнала, формирователь служебных сигналов, второй делитель, формирователь ортогональных сигналов и усилитель-ограничитель, вход которого является входом устройства, а выход усилителя-ограничителя подключен к первым входам первого и второго перемножителей, к вторым вхо- дам которых и входу формирователя

ортогональных сигналов подключен первый выход второго делителя, к входу которого и сигнальному входу формирователя служебных сигналов подключен выход генератора импульсов, а второй выход второго делителя подключен к сигнальному входу блока добавления и вычитания импульсов, при этом первый и второй выходы формирователя ортогональных сигналов подключены к третьим входам соответственно первого и второго перемножителей, а выход первого делителя, являющийся выходом тактовых импульсов устройства, подключен к управляющему входу формирователя служебных сигналов, первый выход которого подключен к управляющим входам первого и второго интеграторов, а второй и третий выходы формирователя служебных сигналов подключены у управляющим входам соответственно регистра памяти и компаратора, при этом выходы первого и второго интеграторов соответственно через первый и второй вычислители модулей проекций сигнала подключены к первой и второй группам входов сумматора, выходы которых через регистр памяти подключены к второй группе входов компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| Многоканальный приемник с кодовым разделением каналов для приема сигналов с квадратурной m-ичной амплитудно-инверсной модуляцией | 2017 |

|

RU2669371C1 |

| УСТРОЙСТВО МНОГОКАНАЛЬНОЙ РАДИОСВЯЗИ | 2023 |

|

RU2809552C1 |

| Устройство тактовой синхронизации | 1975 |

|

SU570210A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1986 |

|

SU1356253A1 |

| ПАРАЛЛЕЛЬНЫЙ КОРОТКОВОЛНОВЫЙ МОДЕМ | 2004 |

|

RU2286648C2 |

| Устройство для передачи и приема многопозиционных широкополосных сигналов | 1989 |

|

SU1793551A1 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU771897A2 |

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

Изобретение может использоваться в многоканальных системах связи с частотно-разнесенными канальными сигналами и фазоразностной модуляцией и обеспечивает повышение точности синхронизации в каналах с селективными замираниями. Устр-во содержит усилитель-ограничитель 1, перемножители 2 и 3, интеграторы 4 и 5, вычислители 6 и 7 модулей проекций сигнала, сумматор 8, компаратор 9, регистр 10 памяти, блок 11 добавления и вычитания импульсов, делители 12 и 15, формирователь 13 служебных сиг1«алов, генератор 14 импульсов и формирователь 16 ортогональных сигналов. Входной фазоманипулированный сигнал преобразуется усилителем-ограничителем 1и перемножается в перемножителях 2и 3 с высокочастотными импульсами заполнения, поступающими с генератора 14 через делитель 15 и ортогональными сигналами вида меандр , формируемыми формирователем 16. В результате на выходах перемножителей 2 и 3 появляются пачки импульсов, соотв. площадям совпадения входного информационного сигнала и опорных ортогональных сигналов. Лачки импульсов интегрируются в интеграторах 4 и 5,построенных на реверсивных счетчиках. Сравнение сумм модулей проекций сигнала дает возможность определить направление подстройки фазы импульсов тактовой частоты, формируемых делителем 12. 6 ил. i (Л

33

Фиг. З

«

И

1

ад

W

1

г

}9

1

mr

г::

.d

&ifi /Xinl4yin/

Фаг. 5

Составитель Г.Лерантович Редактор Н.Бобкова Техред Л.Сердюкова Корректор И.Муска

Заказ 3850/56 Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д.4/5

Произволгтвенно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Устройство тактовой синхронизации | 1979 |

|

SU932642A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Заездный A.M., Окунев Ю.Б., Рахович Л.М | |||

| Фазоразностная модуляция и ее применение для передачи дискретной информации | |||

| - М.: Связь, 1967, с.264-267, рис.610. | |||

Авторы

Даты

1987-08-23—Публикация

1985-05-27—Подача