(Л

с

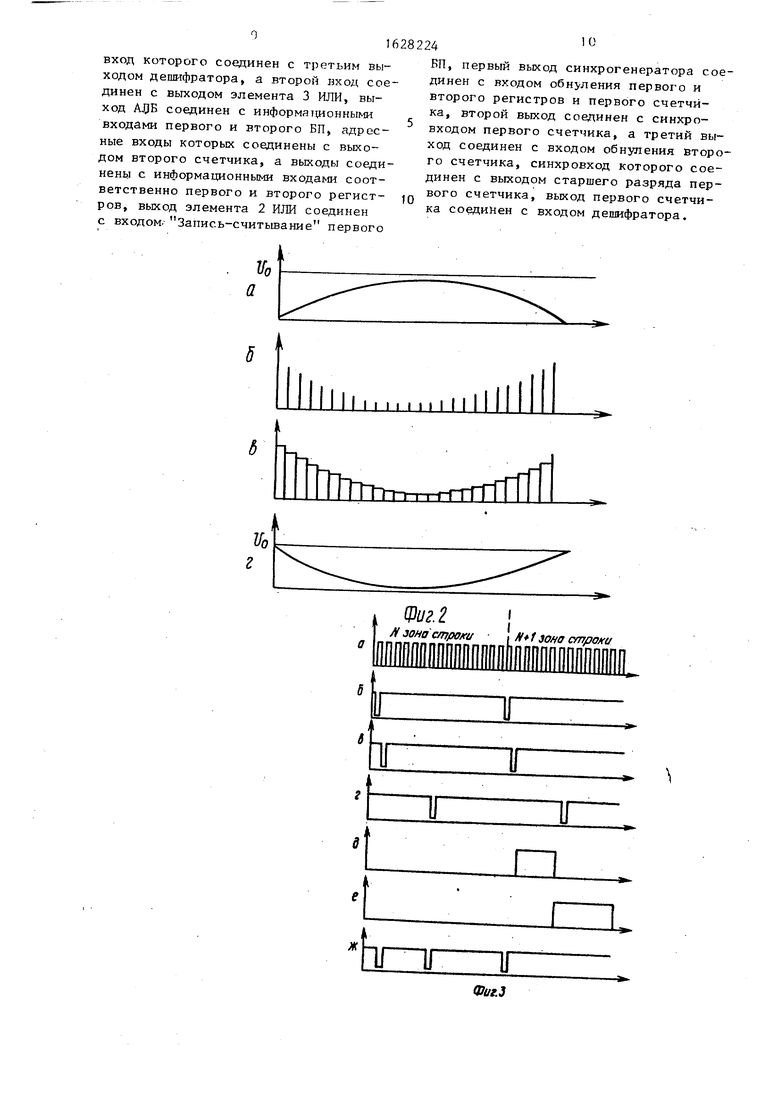

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для формирования телевизионных испытательных сигналов | 1984 |

|

SU1195486A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| ТЕЛЕВИЗИОННАЯ КАМЕРА | 1991 |

|

RU2010449C1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Устройство для считывания и отображения графической информации | 1982 |

|

SU1084839A1 |

| Устройство стабилизации амплитуды видеосигнала | 1988 |

|

SU1603538A2 |

| Устройство для цветовой коррекции кинофильмов,передаваемых по телевидению | 1984 |

|

SU1233162A1 |

| Устройство для ввода информации | 1983 |

|

SU1109728A1 |

Изобретение относится к телевидению и может быть использовано в телевизионных системах робототехни- ческих комплексов. Цель изобретения - повышение качества телевизионного изображения путем повышения его контраста в условиях пространственно- неравномерного фона. Устройство компенсирует аддитивную и мультипликативную составляющие фона. При перекрытом на время работы таймера 17 световом потоке, поступающем на внешний преобразователь (телевизионную

С& 1чЭ

00

ю ю

-U

1628

), н блоках оперативной памя- in НТО с и 10 записываются отсчеты видеосигнала, которые обрабатываются в аги Ьмет нческо-логическом блоке 20. При появлении н видеосигнале сигнала объекта после скорректированной мультипликативной составляющей сигнал с выхода умножителя 2, пройдя через кычитателъ 29 и двухполупериодный выпИзобретение относится к телевидению н может быть использовано в телевизионных, системах робототехничес- кпх комплексов.

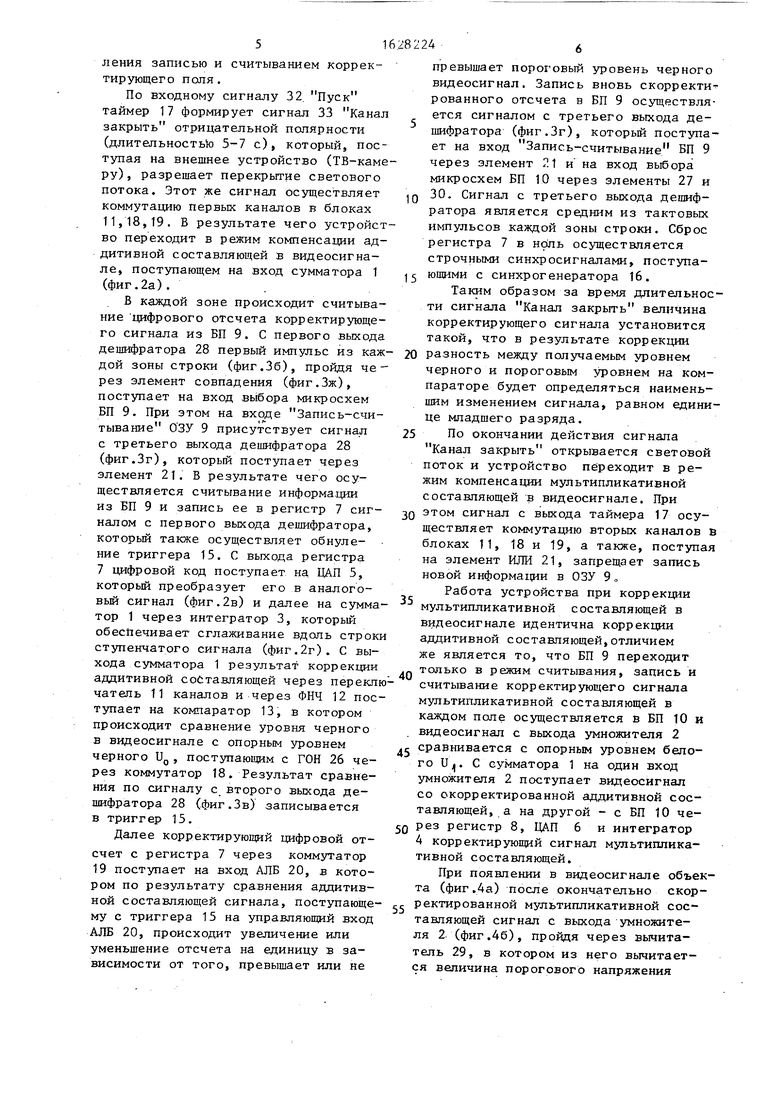

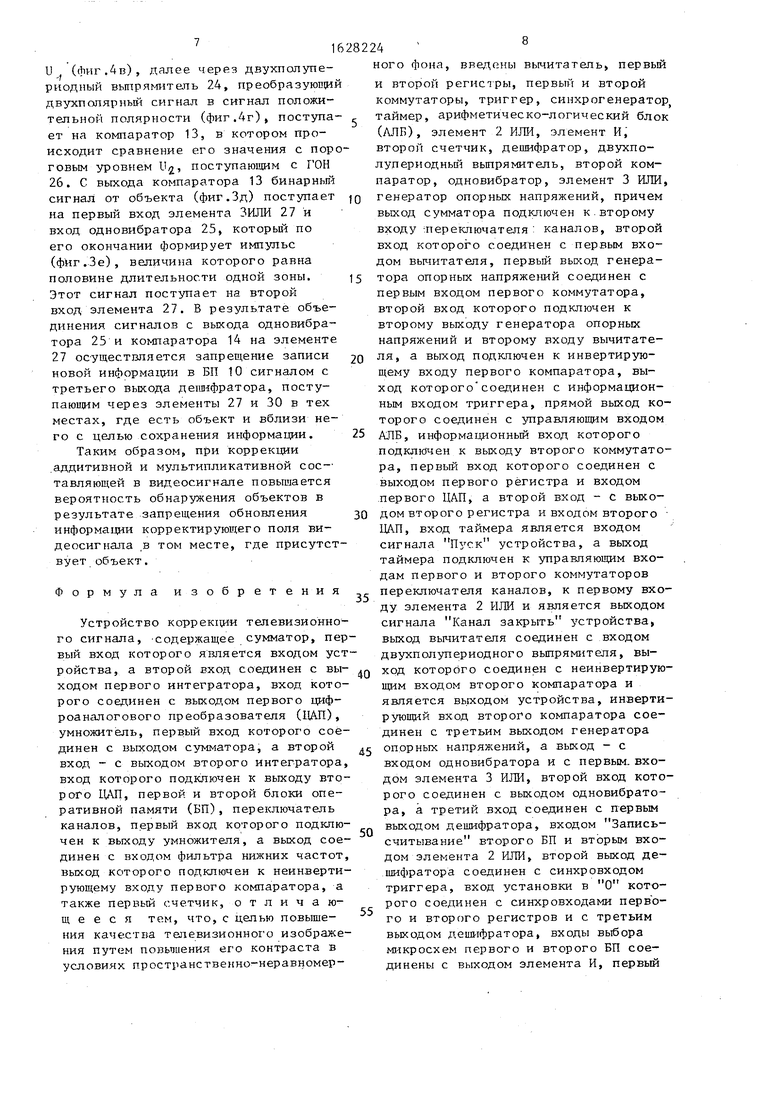

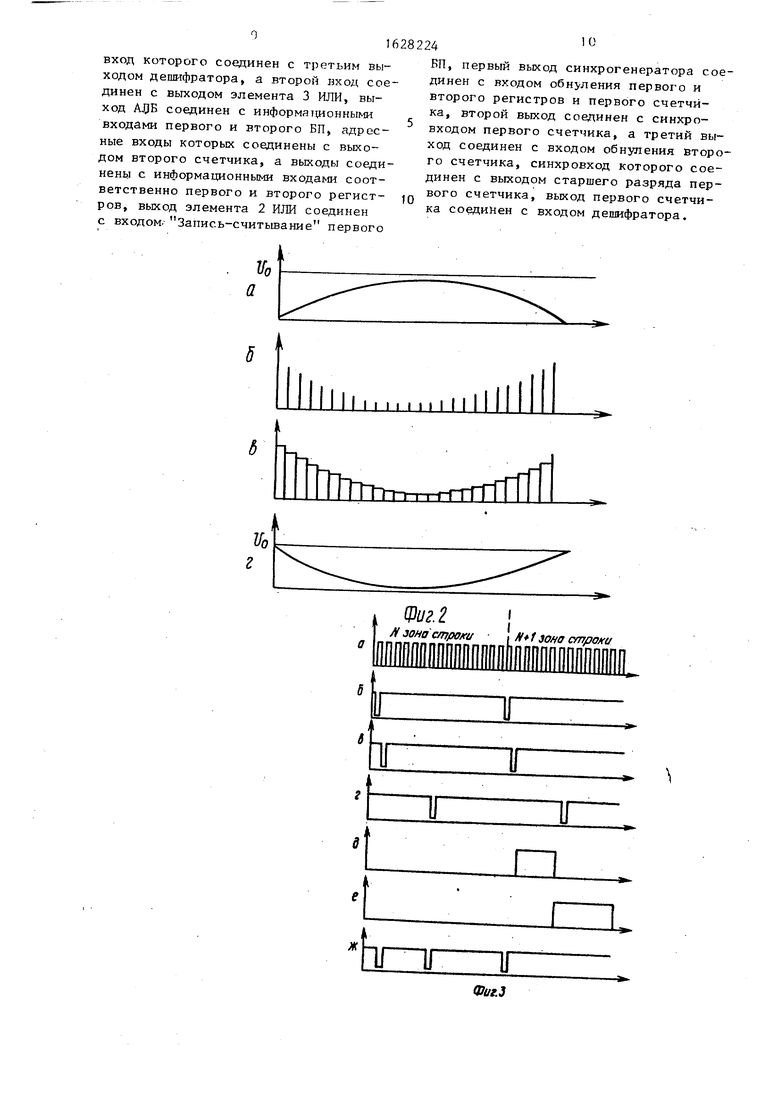

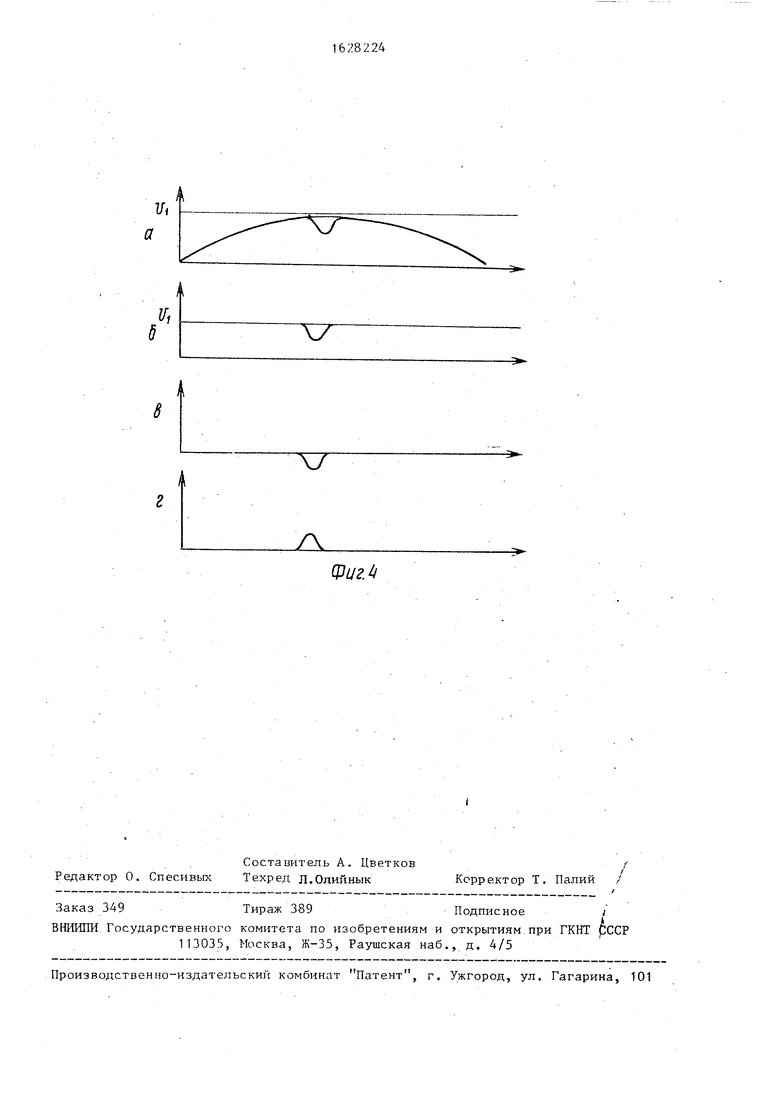

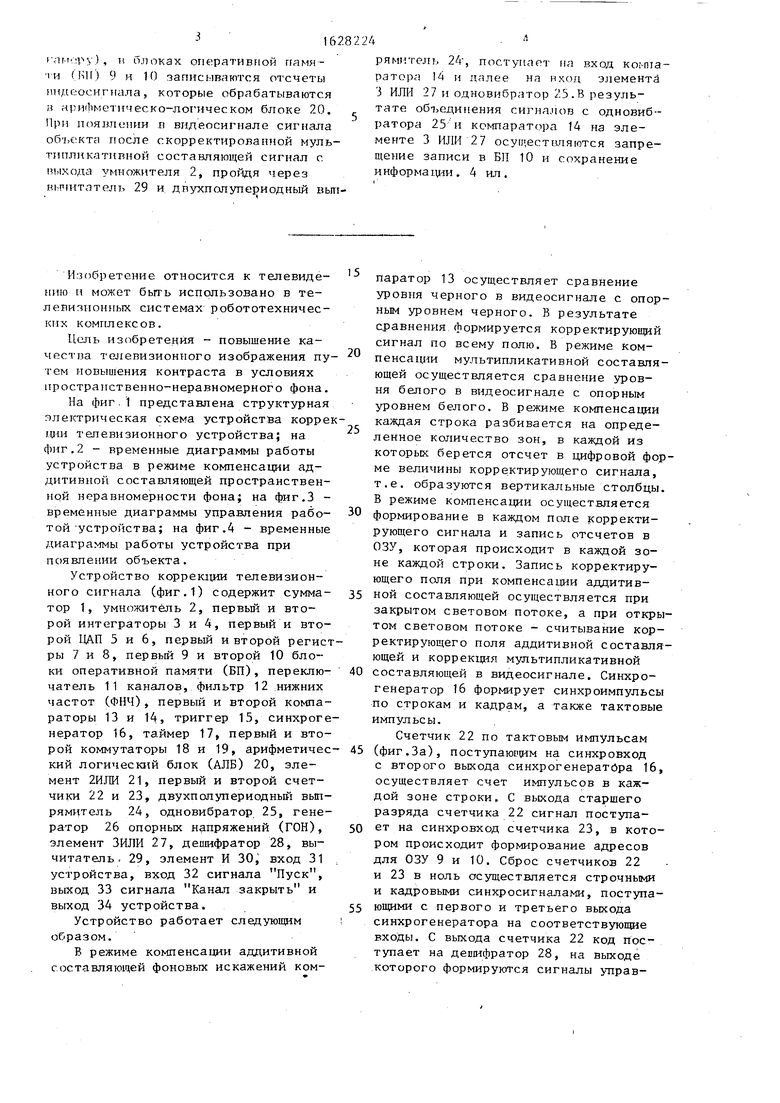

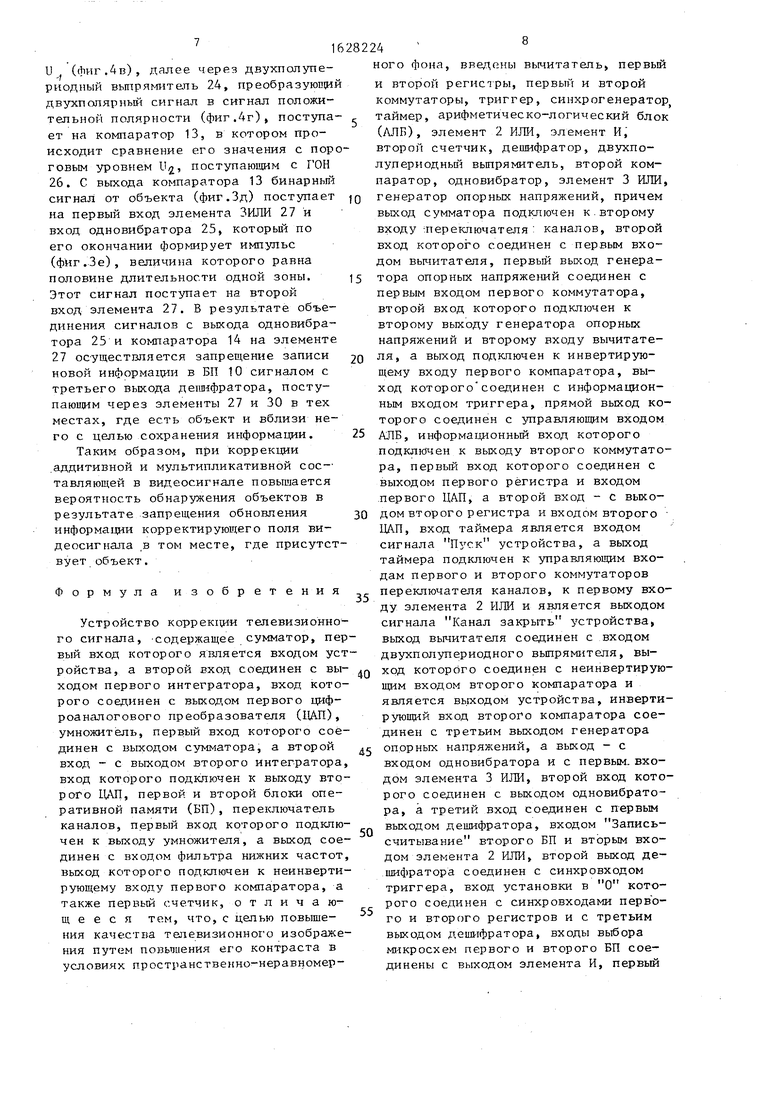

Цель изобретения - повышение качества телевизионного изображения путем повышения контраста в условиях пространственно-неравномерного фона. На фиг 1 представлена структурная электрическая схема устройства коррекции телевизионного устройства; на фиг.2 - временные диаграммы работы устройства в режиме компенсации аддитивной составляющей пространственной неравномерности фона; на фиг.З - временные диаграммы управления работой устройства; на фиг.4 - временные диаграммы работы устройства при появлении объекта.

Устройство коррекции телевизионного сигнала (фиг.1) содержит сумматор 1, умножитель 2, первый и второй интеграторы 3 и 4, первый и второй ЦАП 5 и 6, первый и второй регистры 7 и 8, первый 9 и второй 10 блоки оперативной памяти (БП), переключатель 11 каналов, фильтр 12 нижних частот (ФНЧ), первый и второй компараторы 13 и 14, триггер 15, синхроге нератор 16, таймер 17, первый и второй коммутаторы 18 и 19, арифметичес кий логический блок (АЛБ) 20, элемент 2ИЛИ 21, первый и второй счетчики 22 и 23, двухполупериодный выпрямитель 24, одновибратор 25, генератор 26 опорных напряжений (ГОН), элемент ЗИЛИ 27, дешифратор 28, вы- читатель, 29, элемент И 30 вход 31 устройства, вход 32 сигнала Пуск, выход 33 сигнала Канап закрыть и выход 34 устройства.

Устройство работает следующим образом.

В режиме компенсации аддитивной составляющей фоновых искажений ком

24й

рямнтел. 24, поступает на вход ко;-пта- ратора 14 и далее на нход элемента 3 ИЛИ 27 и одновибратор 2Ь .В результате объединения сигналов с одновиб- ратора 25 и компаратора 14 на элементе 3 ИЛИ 27 осуществляются запрещение записи в БП 10 и сохранение информации. 4 ил.

0

5

0

5

40

45

50

55

паратор 13 осуществляет сравнение уровня черного в видеосигнале с опорным уровнем черного. В результате сравнения формируется корректирующий сигнал по всему полю. В режиме компенсации мультипликативной составляющей осуществляется сравнение уровня белого в видеосигнале с опорным уровнем белого. В режиме компенсации каждая строка разбивается на определенное количество зон, в каждой из которых берется отсчет в цифровой форме величины корректирующего сигнала, т.е. образуются вертикальные столбцы. В режиме компенсации осуществляется формирование в каждом поле корректирующего сигнала и запись отсчетов в ОЗУ, которая происходит в каждой зоне каждой строки. Запись корректирующего поля при компенсации аддитивной составляющей осуществляется при закрытом световом потоке, а при открытом световом потоке - считывание корректирующего поля аддитивной составляющей и коррекция мультипликативной составляющей в видеосигнале. Синхро- генератор 16 формирует синхроимпульсы по строкам и кадрам, а также тактовые импульсы.

Счетчик 22 по тактовым импульсам (фиг.За), поступающем на синхровход с второго выхода синхрогенератора 16, осуществляет счет импульсов в каждой зоне строки, С вьсхода старшего разряда счетчика 22 сигнал поступает на синхровход счетчика 23, в котором происходит формирование адресов для ОЗУ 9 и 10. Сброс счетчиков 22 и 23 в ноль осуществляется строчными и кадровыми синхросигналами, поступающими с первого и третьего выхода синхрогенератора на соответствующие входы. С выхода счетчика 22 код поступает на дешифратор 28, на выходе которого формируются сигналы управления записью и считыванием корректирующего поля.

По входному сигналу 32 Пуск таймер 17 формирует сигнал 33 Канал закрыть отрицательной полярности (длительностью 5-7 с), который, поступая на внешнее устройство (ТВ-камеру), разрешает перекрытие светового потока. Этот же сигнал осуществляет коммутацию первых каналов в блоках 11,18,19. В результате чего устройство переходит в режим компенсации аддитивной составляющей в видеосигнале, поступающем на вход сумматора 1 (фиг.2а).

В каждой зоне происходит считывание цифрового отсчета корректирующего сигнала из БП 9. С первого выхода дешифратора 28 первый импульс из каждой зоны строки (фиг.36), пройдя через элемент совпадения (фиг.Зж), поступает на вход выбора микросхем БП 9. При этом на входе Запись-считывание ОЗУ 9 присутствует сигнал с третьего выхода дешифратора 28 (фиг.Зг), который поступает через элемент 21. В результате чего осуществляется считывание информации из БП 9 и запись ее в регистр 7 сигналом с первого выхода дешифратора, который также осуществляет обнуление триггера 15. С выхода регистра 7 цифровой код поступает на ЦАП 5, который преобразует его в аналоговый сигнал (фиг.2в) и далее на сумматор 1 через интегратор 3, который обеспечивает сглаживание вдоль строки ступенчатого сигнала (фиг.2г). С выхода сумматора 1 результат коррекции аддитивной составляющей через переключатель 11 каналов и через ФНЧ 12 поступает на компаратор 13, в котором происходит сравнение уровня черного в видеосигнале с опорным уровнем черного UQ, поступающим с ГОН 26 через коммутатор 18. Результат сравнения по сигналу с второго выхода дешифратора 28 (фиг.Зв) записывается в триггер 15.

Далее корректирующий цифровой отсчет с регистра 7 через коммутатор 19 поступает на вход АЛБ 20, в котором по результату сравнения аддитивной составляющей сигнала, поступающему с триггера 15 на управляющий вход АЛБ 20, происходит увеличение или уменьшение отсчета на единицу в зависимости от того, превышает или не

0

5

0

5

0

5

0

5

0

5

превышает пороговый уровень черного видеосигнал. Запись вновь скорректированного отсчета в БП 9 осуществляется сигналом с третьего выхода дешифратора (фиг.Зг), который поступает на вход Запись-считывание БП 9 через элемент 21 и на вход выбора микросхем БП 10 через элементы 27 и 30. Сигнал с третьего выхода дешифратора является средним из тактовых импульсов каждой зоны строки. Сброс регистра 7 в ноль осуществляется строчными синхросигналами, поступающими с синхрогенератора 16.

Таким образом за время длительности сигнала Канал закрыть величина корректирующего сигнала установится такой, что в результате коррекции разность между получаемым уровнем черного и пороговым уровнем на компараторе будет определяться наименьшим изменением сигнала, равном единице младшего разряда.

По окончании действия сигнала Канал закрыть открывается световой поток и устройство переходит в режим компенсации мультипликативной составляющей в видеосигнале. При этом сигнал с выхода таймера 17 осуществляет коммутацию вторых каналов в блоках И, 18 и 19, а также, поступая на элемент ИЛИ 21, запрещает запись новой информации в ОЗУ 9

Работа устройства при коррекции мультипликативной составляющей в видеосигнале идентична коррекции аддитивной составляющей,отличием же является то, что БП 9 переходит только в режим считывания, запись и считывание корректирующего сигнала мультипликативной составляющей в каждом поле осуществляется в БП 10 и видеосигнал с выхода умножителя 2 сравнивается с опорным уровнем белого Ujj. С сумматора 1 на один вход умножителя 2 поступает видеосигнал со скорректированной аддитивной составляющей, а на другой - с БП 10 через регистр 8, ЦАП 6 и интегратор 4 корректирующий сигнал мультипликативной составляющей.

При появлении в видеосигнале объекта (фиг,4а) после окончательно скорректированной мультипликативной составляющей сигнал с выхода умножителя 2 (фиг.4б), пройдя через вычита- тель 29, в котором из него вычитается величина порогового напряжения

U (фиг.4 в), далее через двухполупе- риодный выпрямитель 24, преобразующий

20

25

двухполярныи сигнал в сигнал положительной полярности (фиг.Аг), поступа- , ет на компаратор 13, в котором происходит сравнение его значения с пороговым уровнем U2, поступающим с ГОН 26. С выхода компаратора 13 бинарный сигнал от объекта (фиг.Зд) поступает JQ на первый вход элемента ЗИЛИ 27 и вход одновибратора 25, который по его окончании формирует импульс (фиг.Зе), величина которого равна половине длительности одной зоны.15

Этот сигнал поступает на второй вход элемента 27. В результате объединения сигналов с выхода одновибратора 25 и компаратора 14 на элементе 27 осуществляется запрещение записи новой информации в БП 10 сигналом с третьего выхода дешифратора, поступающим через элементы 27 и 30 в тех местах, где есть объект и вблизи него с целью сохранения информации.

Таким образом, при коррекции аддитивной и мультипликативной сое-1 тавляющей в видеосигнале повышается вероятность обнаружения объектов в результате запрещения обновления30

информации корректирующего поля видеосигнала в том месте, где присутствует объект.

Формула изобретения

Устройство коррекции телевизионного сигнала, содержащее сумматор, первый вход которого является входом устройства, а второй вход соединен с вы- ,Q ходом первого интегратора, вход которого соединен с выходом первого циф- роаналогового преобразователя (ПАП), умножитель, первый вход которого соединен с выходом сумматора, а второй вход - с выходом второго интегратора, вход которого подключен к выходу второго ЦАП, первой и второй блоки оперативной памяти (БП), переключатель каналов, первый вход которого подключен к выходу умножителя, а выход соединен с входом фильтра нижних частот, выход которого подключен к неинвертирующему входу первого компаратора, а также первый счетчик, отличающееся тем, что, с целью повышения качества телевизионного изображения путем повышения его контраста в условиях пространетвенно-неравномер628224 8

ного фона, введены вычитатель, первый и второй регистры, первый и второй коммутаторы, триггер, синхрогенератор

45

50

55

таймер, арифметическо-логический блок (АЛБ), элемент 2 ИЛИ, элемент И, второй счетчик, дешифратор, двухпо- лупериодный выпрямитель, второй компаратор, одновибратор, элемент 3 ИЛИ, генератор опорных напряжений, причем выход сумматора подключен к второму входу переключателя каналов, второй вход которого соединен с первым входом вычитателя, первый выход генератора опорных напряжений соединен с первым входом первого коммутатора, второй вход которого подключен к второму выходу генератора опорных напряжений и второму входу вычитателя, а выход подключен к инвертирующему входу первого компаратора, выход которого соединен с информационным входом триггера, прямой выход которого соединен с управляющим входом АЛБ, информационный вход которого подключен к выходу второго коммутатора, первый вход которого соединен с выходом первого регистра и входом первого ЦАП, а второй вход - с выходом второго регистра и входом второго ЦАП, вход таймера является входом сигнала Пуск устройства, а выход таймера подключен к управляющим входам первого и второго коммутаторов переключателя каналов, к первому входу элемента 2 ИЛИ и является выходом сигнала Канал закрыть устройства, выход вычитателя соединен с входом двухполупериодного выпрямителя, выход которого соединен с неинвертирующим входом второго компаратора и является выходом устройства, инвертирующий вход второго компаратора соединен с третьим выходом генератора опорных напряжений, а выход - с входом одновибратора и с первым, входом элемента 3 ИЛИ, второй вход которого соединен с выходом одновибратора, а третий вход соединен с первым выходом дешифратора, входом Запись- считывание второго БП и вторым входом элемента 2 ИЛИ, второй выход дешифратора соединен с синхрОБХОДОМ триггера, вход установки в О которого соединен с синхровходами перво- го и второго регистров и с третьим выходом дешифратора, входы выбора микросхем первого и второго БП соединены с выходом элемента И, первый

0

5

5

0

,Q

45

50

55

таймер, арифметическо-логический блок (АЛБ), элемент 2 ИЛИ, элемент И, второй счетчик, дешифратор, двухпо- лупериодный выпрямитель, второй компаратор, одновибратор, элемент 3 ИЛИ, генератор опорных напряжений, причем выход сумматора подключен к второму входу переключателя каналов, второй вход которого соединен с первым входом вычитателя, первый выход генератора опорных напряжений соединен с первым входом первого коммутатора, второй вход которого подключен к второму выходу генератора опорных напряжений и второму входу вычитателя, а выход подключен к инвертирующему входу первого компаратора, выход которого соединен с информационным входом триггера, прямой выход которого соединен с управляющим входом АЛБ, информационный вход которого подключен к выходу второго коммутатора, первый вход которого соединен с выходом первого регистра и входом первого ЦАП, а второй вход - с выходом второго регистра и входом второго ЦАП, вход таймера является входом сигнала Пуск устройства, а выход таймера подключен к управляющим входам первого и второго коммутаторов переключателя каналов, к первому входу элемента 2 ИЛИ и является выходом сигнала Канал закрыть устройства, выход вычитателя соединен с входом двухполупериодного выпрямителя, выход которого соединен с неинвертирующим входом второго компаратора и является выходом устройства, инвертирующий вход второго компаратора соединен с третьим выходом генератора опорных напряжений, а выход - с входом одновибратора и с первым, входом элемента 3 ИЛИ, второй вход которого соединен с выходом одновибратора, а третий вход соединен с первым выходом дешифратора, входом Запись- считывание второго БП и вторым входом элемента 2 ИЛИ, второй выход дешифратора соединен с синхрОБХОДОМ триггера, вход установки в О которого соединен с синхровходами перво- го и второго регистров и с третьим выходом дешифратора, входы выбора микросхем первого и второго БП соединены с выходом элемента И, первый

б

Им ,....|Ц||||1

Ь 1

Фиг. 2

Л зона строки зона строки

§

Vi

7

Фиг.Ь

| Рум А.В., Саратовский Ю.Л | |||

| и Смирнов М.Б | |||

| Коррекция фоновых искажений | |||

| Техника средств связи | |||

| Сер | |||

| Техника телевидения, 1985 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1991-02-15—Публикация

1988-07-08—Подача