Изобретение относится к телевизионной технике и может быть использовано в составе телевизионных (ТВ) систем автоматической коррекции искажений изображения в реальном масштабе времени с последующей выдачей информации о величине корректирующих сигналов.

Объективы современных телевизионных камер являются сложными оптическими устройствами, параметры которых далеки от идеальных. Неравномерность светопередачи по площади объектива является источником яркостных искажений (неравномерность фона и неравномерность видеосигнала). При этом необходимо учитывать то обстоятельство, что для различных сочетаний значений фокуса, диафрагмы и масштаба эти искажения будут различны.

Известно устройство, содеpжащее синхронизатор, первый блок памяти, интерполятор, блок введения корректирующего сигнала, блок сравнения, датчик видеосигнала, формирователь опорного напряжения, генератор приращения корректирующего сигнала.

Недостатком известного устройства является невозможность коррекции яркостных искажений, вносимых объективом при различных значениях фокуса, диафрагмы и масштаба, невозможность коррекции изменения геометрических размеров изображений на планшайбе передающей трубки, а также отсутствие информации о корректирующих сигналах.

Наиболее близким к предлагаемому является устройство, содержащее датчик видеосигнала, перед оптическим входом которого расположена тест-таблица, синхронизатор, процессор, блок памяти, блок весового суммирования, блок вычитания, формирователь модуля сигнала, перемножитель, интегратор, оператор эталонного сигнала, генератор ортогональных сигналов.

Недостатком данного устройства является невозможность измерения и коррекции яркостных и геометрических искажений, вносимых оптической системой при различных комбинациях масштаба.

Целью изобретения является повышение точности измерения параметров телевизионных оптических систем.

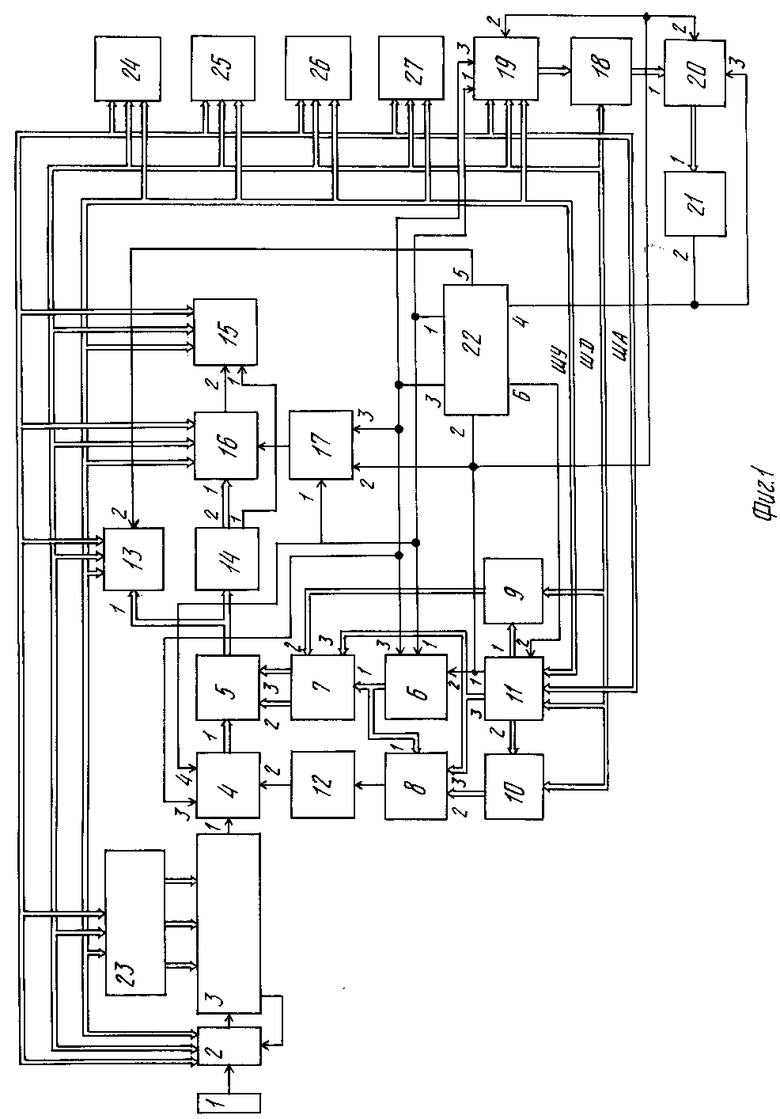

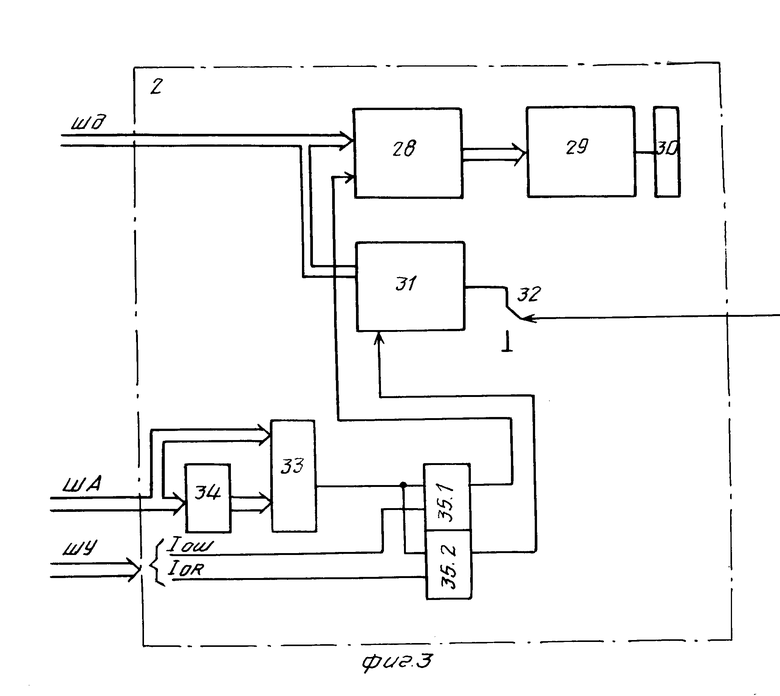

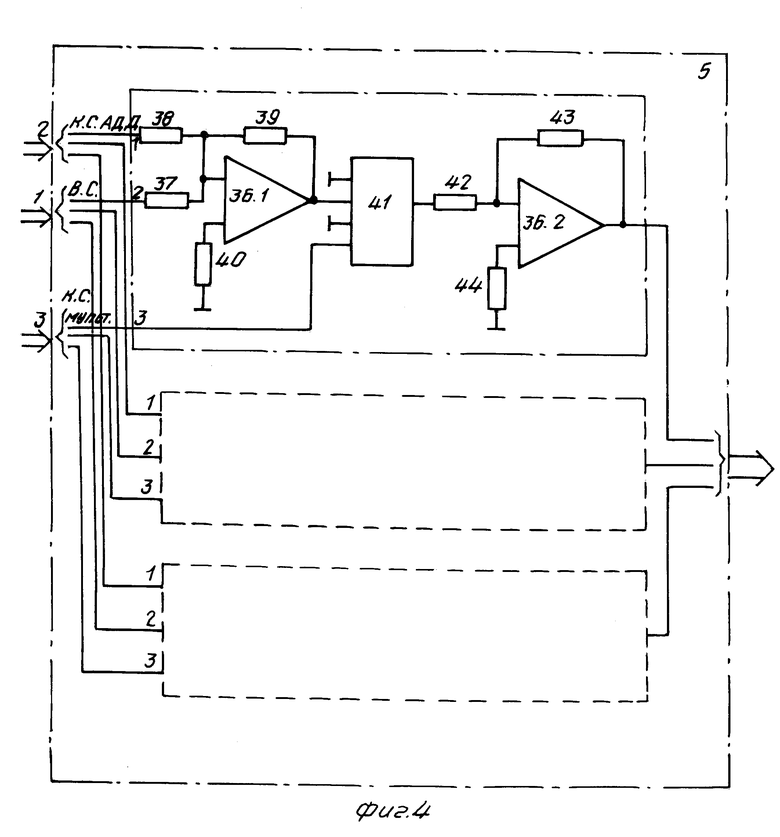

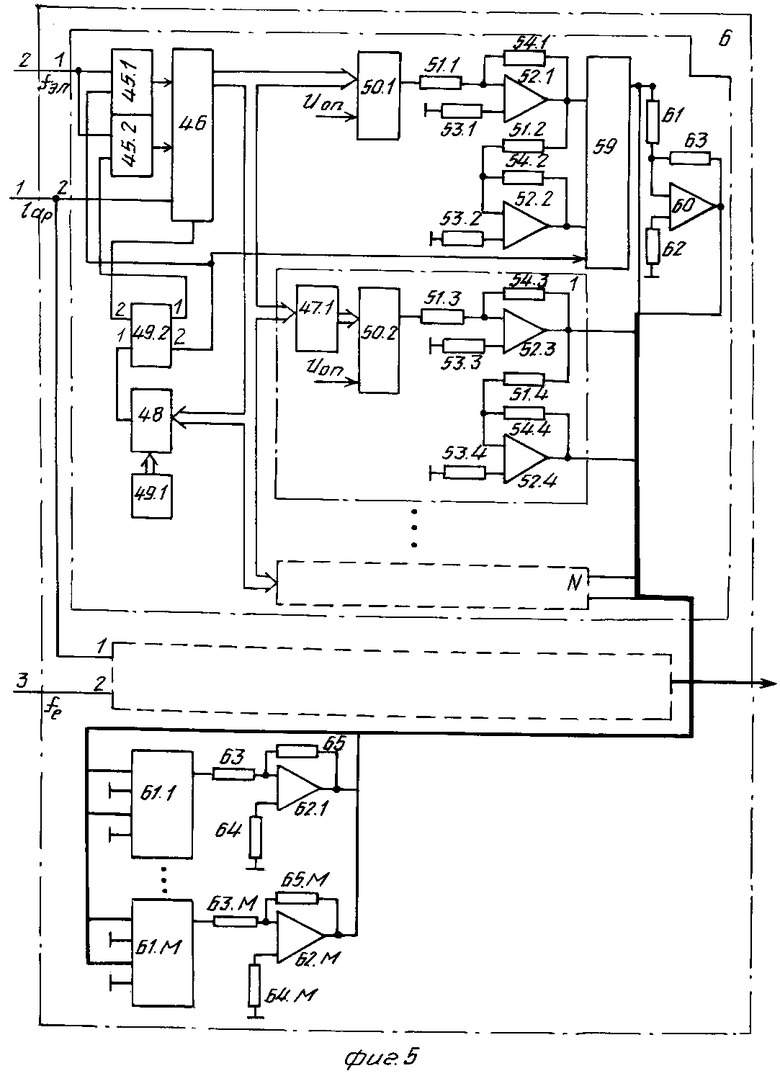

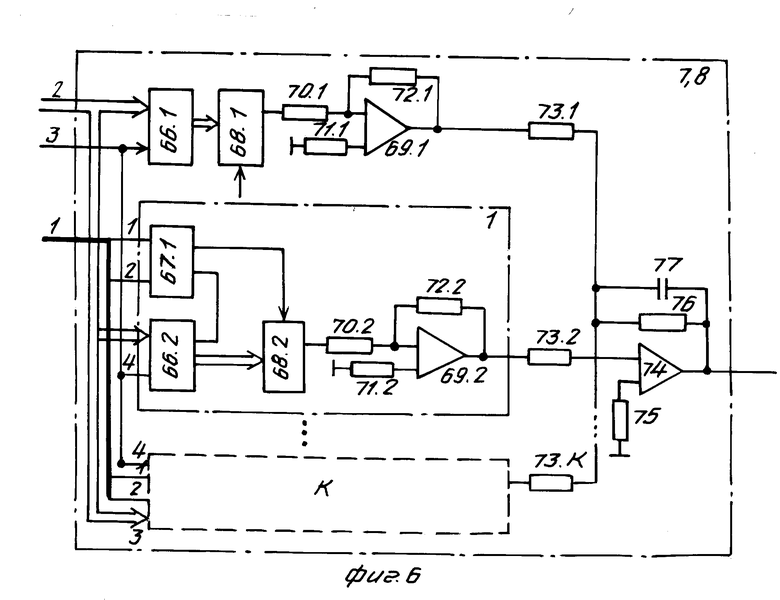

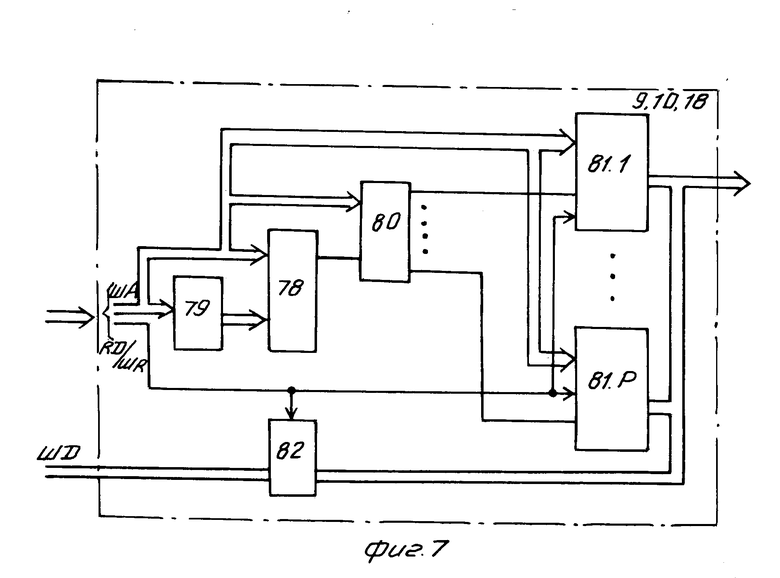

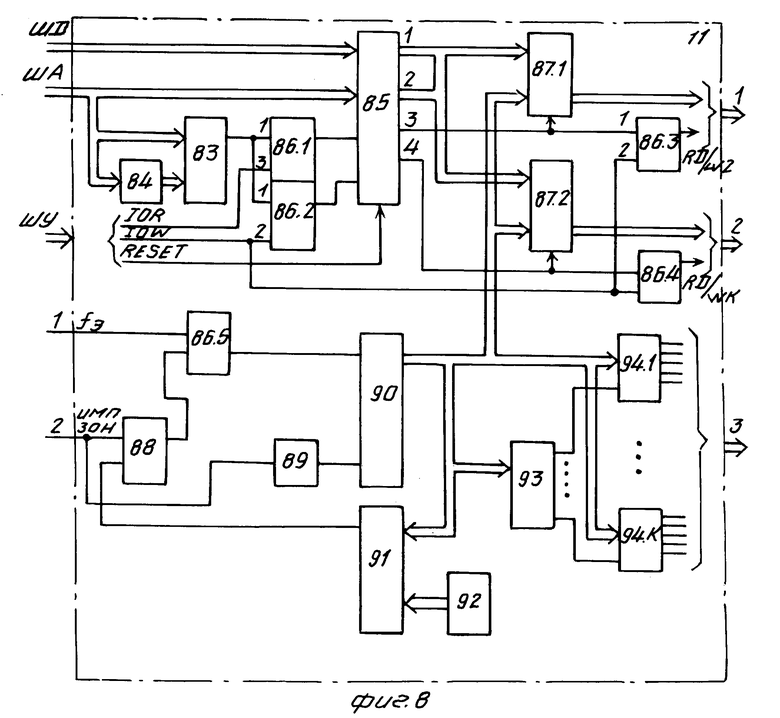

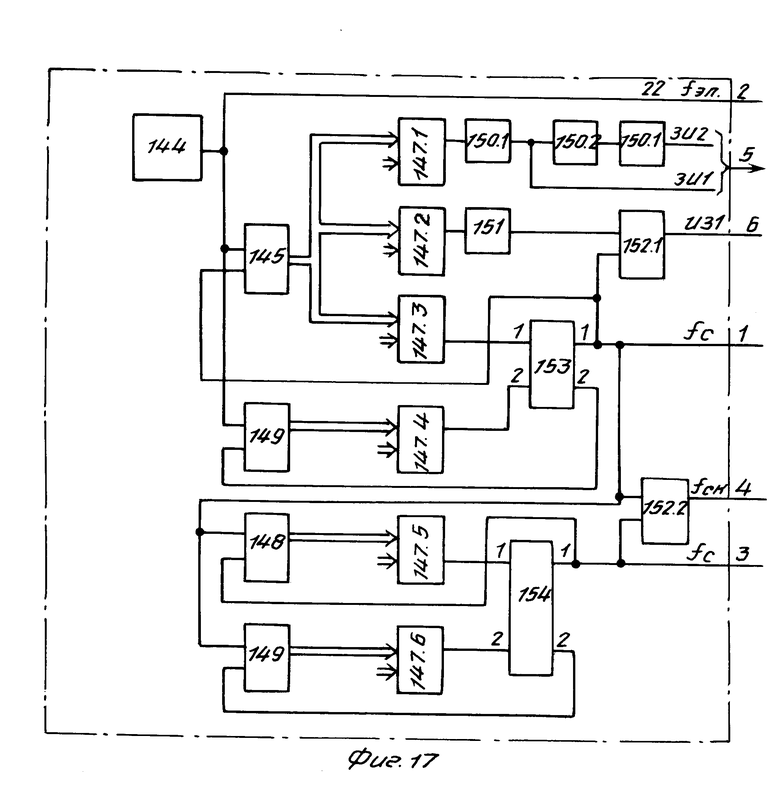

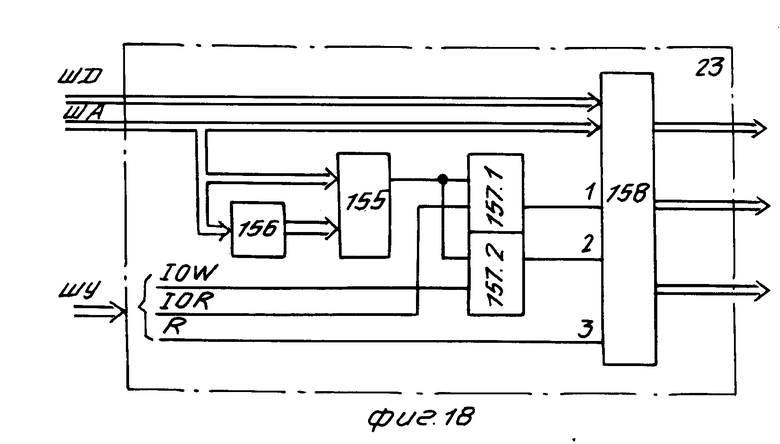

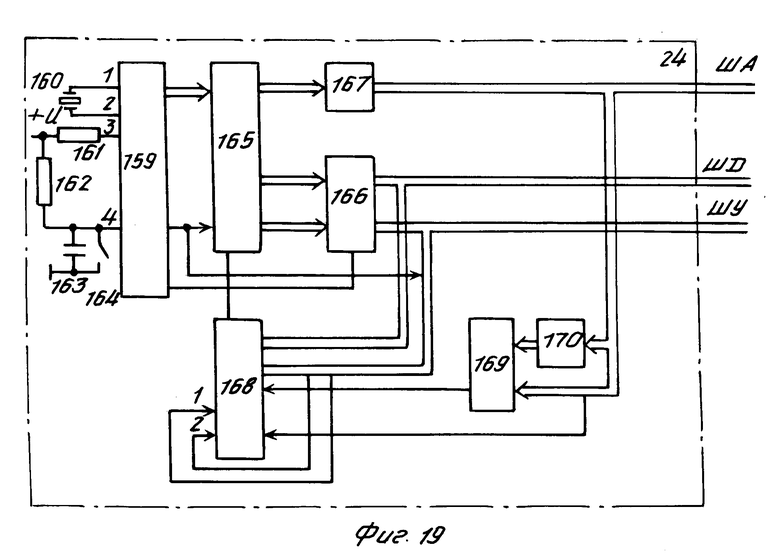

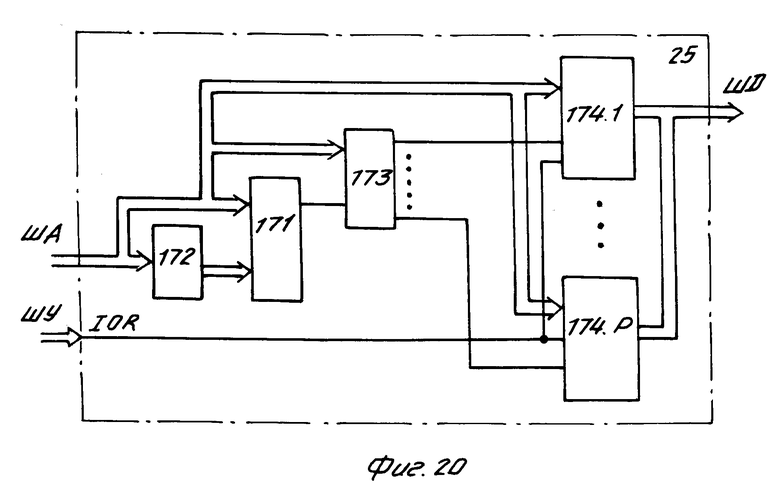

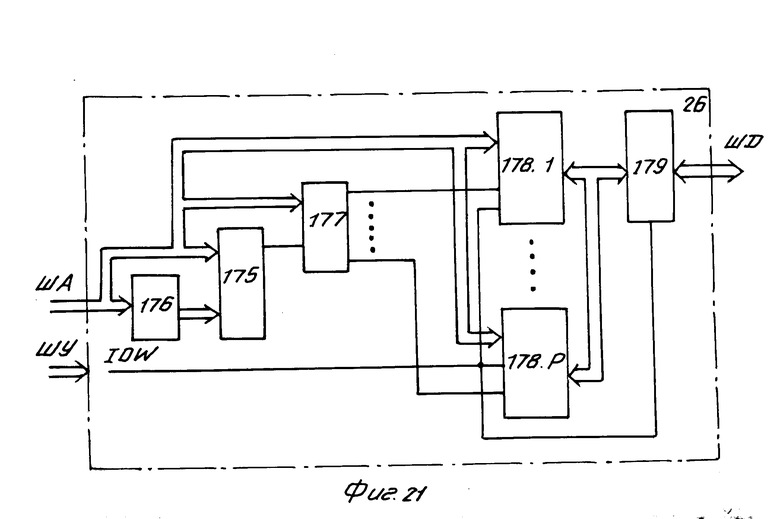

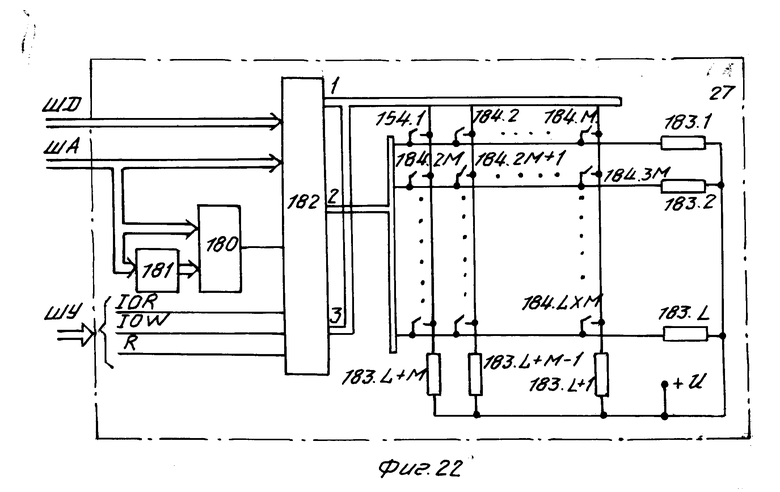

На фиг. 1 представлена электрическая структурная схема устройства измерения параметров телевизионных оптических систем; на фиг. 2 - тест-таблица; на фиг. 3 - блок оптических фильтров; на фиг. 4 - первый блок ввода корректирующего сигнала; на фиг. 5 - генератор базисных сигналов; на фиг. 6 - блок весового суммирования; на фиг. 7 - первый, второй, четвертый блоки оперативной памяти; на фиг. 8 - первый блок управления памятью; на фиг. 9 - второй блок ввода корректирующего сигнала; на фиг. 10 - анализатор; на фиг. 11 - квантователь; на фиг. 12 - фазовый детектор; на фиг. 13 - коммутатор; на фиг. 14 - генератор эталонного сигнала; на фиг. 15 - второй блок управления памятью; на фиг. 16 - блок регистров сдвига; на фиг. 17 - синхронизатор; на фиг. 18 - регистр масштаба, фокуса и диафрагмы; на фиг. 19 - контроллер; на фиг. 20 - блок постоянной памяти; на фиг. 21 - третий блок оперативной памяти; на фиг. 22 - пульт управления.

Устройство измерения параметров телевизионных оптических систем (фиг. 1) содержит тест-таблицу 1, блок 2 оптических фильтров, оптическую систему 3, датчик 4 видеосигнала, первый, второй блоки 5, 6 ввода корректирующего сигнала, генератор 7 базисных сигналов, первый и второй блоки весового суммирования 8, 9, блоки 10, 11, 12 оперативной памяти, блоки 13, 14 управления памятью, анализатор 15, квантователь 17, фазовый детектор 17, коммутатор 18, генератор 19 эталонного сигнала, блок 20 регистров сдвига, видеоконтрольный блок 21, синхронизатор 22, регистр 23 масштаба, фокуса и диафрагмы, контроллер 24, блок 25 постоянной памяти, пульт 27 управления.

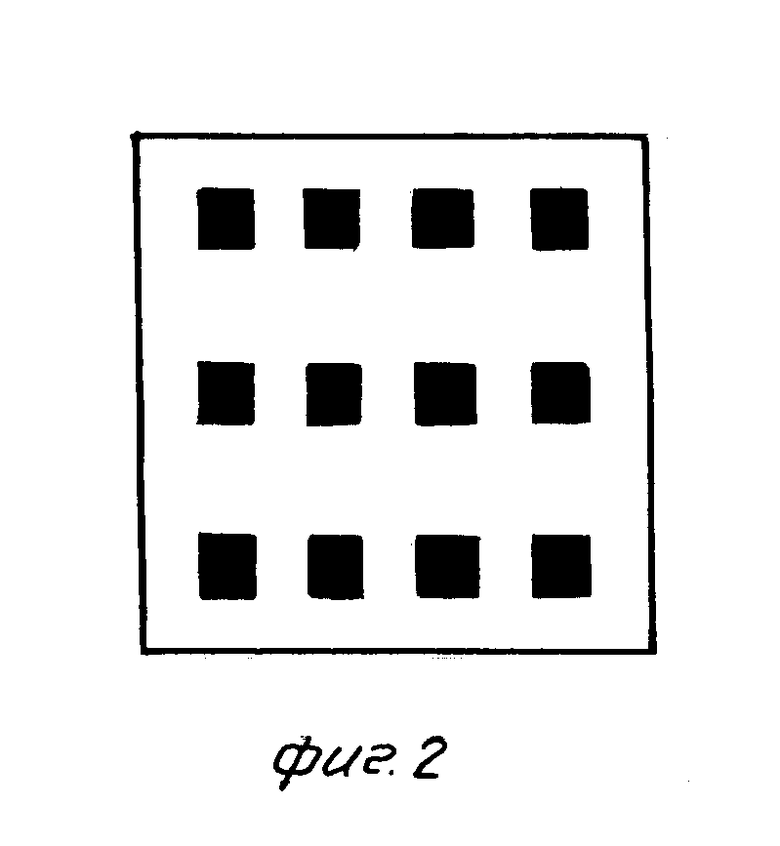

Тест-таблица 1 (фиг. 2) представляет собой белое поле с нанесенными на нем черными неотражающими квадратами. Количество квадратов в строке Nс и количество строк квадратов на таблице зависит от требуемой точности настройки.

Блок 2 оптических фильтров (фиг. 2) состоит из регистра-защелки 28, входы данных которого подключены к шине данных, выходы данных регистра 28 соединены с входами управления исполнительного механизма 29, которые вращают блок 30 фильтров, устанавливая прозрачный, молочный или черный фильтр (заслонку) перед зрачком объектива. Буферный элемент 31 служит для подачи на шину данных сигнала от контакта 32 о наличии или отсутствии оптической системы, связанной с ним механическим толкателем. А-входы N-входового элемента И-НЕ 33 подключены непосредственно к А-разрядам шины адреса, а В других входов подключены к В-разрядам шины адреса через блок из В инверторов 34. Выход элемента И-НЕ 33 соединен с первыми входами элементов ИЛИ 35.1 и 35.2, на вторые входы которых поданы сигналы с шины управления. Выход элемента ИЛИ 35.1 соединен со стробирующим входом регистра 28, а выход элемента 35.2 соединен с входом разрешения буферного элемента 31.

Оптическая система 3 представляет собой объектив телевизионной камеры, параметры которого необходимо проверить.

Датчик 4 видеосигнала представляет собой часть стандартной цветной телевизионной камеры, включающей в себя трубочно-призменный блок, предусилители, видеоусилители и блок разверток, выполненные, например, как в камере КТ-132 (см. "Техника телевизионного вещания". Справочник).

Блок 5 ввода корректирующего сигнала (фиг. 4) содержит последовательно соединенные сумматор на ОУ 36.1 и резисторах 37-40, перемножитель 41 и инвертирующий буфер на ОУ 36.2 и резисторах 42-44. Причем резистор 37 подключен между первым входом блока 5 и первым входом ОУ 36.1, а резистор 38 подключен между вторым входом блока 5 и первым входом ОУ 36.1. Второй и четвертый входы перемножителя заземлены. Третий вход перемножителя является третьим входом блока 5. Выход буфера на ОУ 36.2 является выходом блока 5. Остальные каналы выполнены идентично, число каналов определяется количеством трубок в датчике 4 видеосигнала.

Генератор 6 базисных сигналов (фиг. 5) содержит переключатель направления счета на элементах И 45.1 и 45.2, на первые входы которых подается сигнал Гэл с частотой элементов разложения, выходы которых соединены с входами прямого и обратного счета счетчика 46, выходы которого соединены с адресными входами ПЗУ 47.1-47. N функций разложения и с первым входом цифрового компаратора 48, второй вход которого соединен с блоком 49 микропереключателей, выход компаратора 48 соединен с первым входом триггера 49, второй вход которого соединен с выходом переноса счетчика 46, первый выход триггера 49.2 соединен с вторым входом элемента 45.1, а второй выход триггера 49.2 соединен с вторым входом элемента 45.2. Входы ЦАП 50.1 соединены с выходами счетчика 46, а входы ЦАП 50.2-50. N+1 соединены с выходами ПЗУ 47.1-47. n. Выходы ЦАП 50.1-50. N+1 через резисторы 51.1-51. N+1 соединены с первыми входами операционных усилителей 51.1-52. N+1, вторые входы которых соединены через резисторы 53.1-53. N+1 с землей. Резисторы 54.1-54. N+1 включены между первыми входами и выходами ОУ 52.1-52. N+1, к выходам ОУ 52.1-52. N+1 подключены инверторы на ОУ 55.1-55. N+1 с резисторами 56.1-56. N+1 58.1-58. N+1.

Выходы ОУ 52.1 и 55.1 соединены с входами коммутатора 59, вход управления которого соединен с вторым выходом триггера 49.2. Выход коммутатора 59 соединен с входом инвертора, собранного на ОУ 60 и резисторах 61-63.

Выходы коммутатора 59, ОУ 60, а также ОУ 52.2-52. N+1 и ОУ 55.2-55. N+1 являются выходами блока. Выходы коммутатора 59 и ОУ 52.2-52. N+1 соединены с первыми входами перемножителей 61.1-61. М, вторые и четвертые входы которых заземлены. Вторая половина генератора 6 идентична вышеописанной, за исключением того, что на вход переключателя направления счета подается сигнал Nстр (последовательность строчных гасящих импульсов), который также поступает на вход сброса счетчика 46. На вход сброса счетчика 46 второй половины генератора поступает сигнал Nк (последовательность кадровых гасящих импульсов). Выходы элементов 59 и 52.2-52. N+1 второй половины генератора 6 соединены с третьими входами перемножителей 61.1-61. М. Порядок соединения входов перемножителей 61.1-61. М с выходами элементов 59. 52.2-52. N+1 и 59 52.2-52. N+1 определяется, исходя из степени формируемого аппроксимирующего полинома. Выходы перемножителей 61.1-61. М прямо и через инверторы на ОУ 62.1-62. М и резисторах 63.1-63. М, 64.1-64. М, 65.1-65. М являются также выходами блока 6.

Блок 7,8 весового суммирования (фиг. 6) содержит регистры-защелки 66.1-66. К, входы которых объединены между собой и соединены с выходом данных первого (второго) блока оперативной памяти.

Входы синхронизаций регистров 66.1-66. К соединены с третьим выходом первого блока 11 управления памятью. Входы коммутаторов 67.1-67. К-1 соединены с выходами генератора 6 базисных сигналов, выходы коммутаторов 67.1-67. К-2 соединены с входом опорного напряжения перемножающих ЦАП 68.2-68. К, причем опорное напряжение УАП 68.1 не изменяется. Выход младшего разряда регистров 66.2-66. К подключен к управляющему входу коммутатора 67.1-67. К-1. Выходы остальных разрядов регистров 66.1-66. К соединены с входами данных ЦАП 68.1-68. К. Выходы ЦАП через буфера на ОУ 69.1-69. К и резисторах 70.1-70. К, 71.1-71. К, 72.1-72. К соединены с входами сумматора-интегратора резисторами 73.1-73. К, которые соединены с первым входом ОУ 74, второй вход которого через резистор 75 заземлен. Резистор 76 и конденсатор 77 соединены параллельно и включены между первым входом и выходом ОУ 74. Выход ОУ 74 является выходом блока. Первый блок 7 весового суммирования содержит два идентичных канала, аналогичных вышеописанному.

Блоки 9, 10, 18 оперативной памяти (фиг. 2.7) содержат N-входовой элемент И-НЕ 78, А входов которого подключены непосредственно к А разрядам шины адреса, В других входов подключены к В разрядам шины адреса через блок из В инверторов 79. Выход элемента И-НЕ 78 подключен к входу выборки дешифратора 80, информационные входы которого подключены к шине адреса, а выходы соединены с входами выборки ОЗУ 81.1-81. Р, адресные входы которых объединены и подключены к шине адреса, входы управления также объединены между собой и соединены с входом управления буферного элемента 82, входы которого объединены с входами-выходами ОЗУ 81.1-81. Р и с шиной данных, а выход является выходом блока. Блок 18 оперативной памяти представляет собой три идентичных блока согласно фиг. 7, включенных параллельно.

Блок 11 управления памятью (фиг. 8) содержит N-входовой элемент И-НЕ 83, А входов которого подключены непосредственно к А-разрядам шины адреса, а В других входов подключены к В разрядам шины адреса через блок из В инверторов 84, оставшиеся два младших разряда подключены к адресным входам блока 85 ввода информации, к входам данных которого подключена шина данных. Выход элемента И-НЕ 83 соединен с первыми входами элементов 96.1 и 86.2 ИЛИ, на вторые входы которых поданы сигналы с шины управления, а выходы которых подключены соответственно к первому и второму управляющим входам блока 85, третий управляющий вход которого соединен с шиной управления. Первый и второй выходы блока 85 объединены и подключены к первым входам коммутаторов 87.1 и 87.2. Третий выход блока 85 соединен с управляющим входом первого коммутатора 87.1 и с первым входом элемента ИЛИ 86.3, четвертый выход блока 85 соединен с управляющим входом второго коммутатора 87.2, а также с первым входом элемента ИЛИ 86,4, вторые входы элементов ИЛИ 86.3 и 86.4 объединены между собой и соединены с вторым входом элемента ИЛИ 86.2. Выходы первого коммутатора 87.1 и элемента ИЛИ 86.3 совместно образуют первый выход блока 11, а выходы второго коммутатора 87.2 и элемента ИЛИ 86.4 совместно образуют второй выход блока 11. Первый вход элемента ИЛИ 86.5 является первым входом блока 11. Первый вход триггера 88 и вход мультивибратора 89 объединены между собой и являются вторым входом блока. Выход мультивибратора 89 соединен с входом сброса счетчика 90, выход триггера 88 соединен с вторым входом элемента ИЛИ 86.5, выход которого соединен со счетным входом счетчика 90. Выходы счетчика соединены с объединенными вторыми входами коммутаторов 87.1 и 87.2, с первыми входами цифрового коммутатора 91, к вторым входам которого подключены выходы блока микровыключателей 92. Входы первого дешифратора 93 и вторых дешифраторов 94.1-94. К объединены между собой и подключены к выходу счетчика 90, выходы первого дешифратора 93 подключены к входам разрешения соответствующих вторых дешифраторов 94.1-94. К, выходы которых являются третьим выходом блока 11.

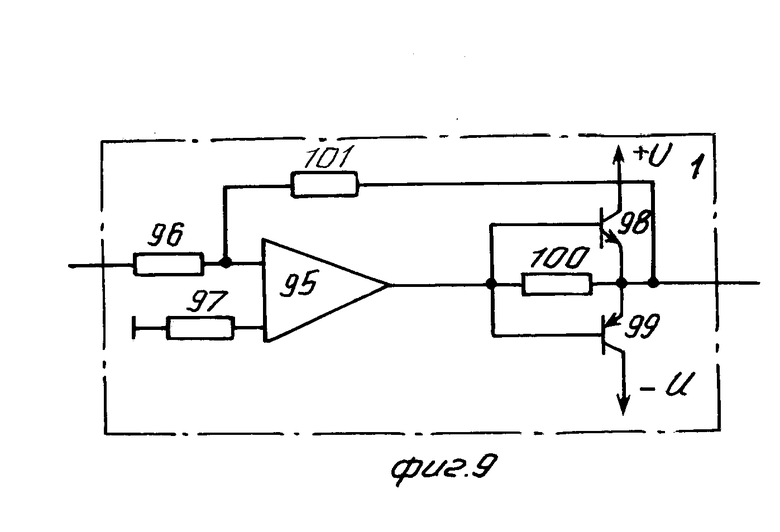

Блок 12 ввода корректирующего сигнала (фиг. 9) содержит ОУ 95, к первому входу которого последовательно подключен резистор 96, второй вход которого является входом блока между вторым входом и землей, подключен резистор 97. К выходу ОУ 95 подключены объединенные базы транзисторов 98 и 99. Эмиттеры транзисторов также объединены между собой и являются выходом блока, коллекторы транзисторов 98 и 99 подключены к соответствующим источникам питания, между объединенными базами и эмиттерами транзисторов 98 и 99 включен резистор 100. Между первым входом ОУ 95 и объединенными эмиттерами транзисторов 98 и 99 включен резистор 101. Остальные каналы выполнены идентично, число каналов определяется количеством трубок в датчике 4 видеосигнала.

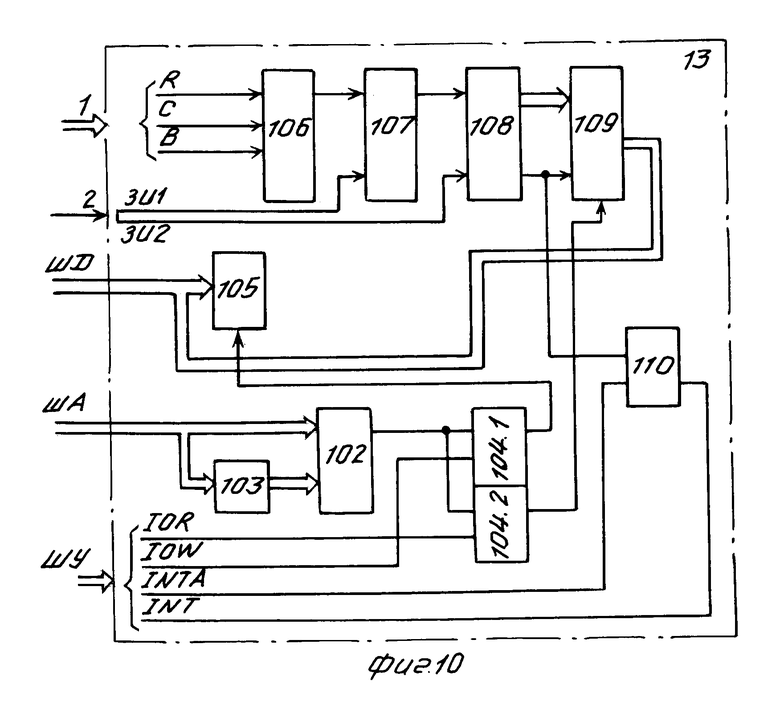

Анализатор 13 (фиг. 10) содержит N-входовой элемент И-НЕ 102, А входов которого подключены непосредственно к А-разрядам шины адреса, а В других входов подключены к В-разрядам шины адреса через блок из В инверторов 103. Выход элемента И-НЕ 102 соединен с первыми входами элементов ИЛИ 104.1 и 104.2, на вторые входы которых поданы сигналы с шины управления. Выход элемента ИЛИ 104.1 подключен к управляющему входу резистора 105, входы данных которого подключены к шине данных с выхода к управляющим входам аналогового коммутатора 106, аналоговые входы которого являются первыми входами блока 13, выход коммутатора 106 соединен с входом УВХ 107. Выход УВХ 107 соединен с аналоговым входом АЦП 108, выход данных которого соединен с входом данных регистра 103. Управляющий вход УВХ 107 и вход запуска АЦП 108 являются вторыми входами блока 11. Первый вход триггера 110 соединен с синхровходом регистра 103 данных и выходом готовности АЦП 108. Второй вход триггера 110 и его выход подключены к шине управления. Выход элемента ИЛИ 104.2 соединен с входом разрешения регистра 109 данных.

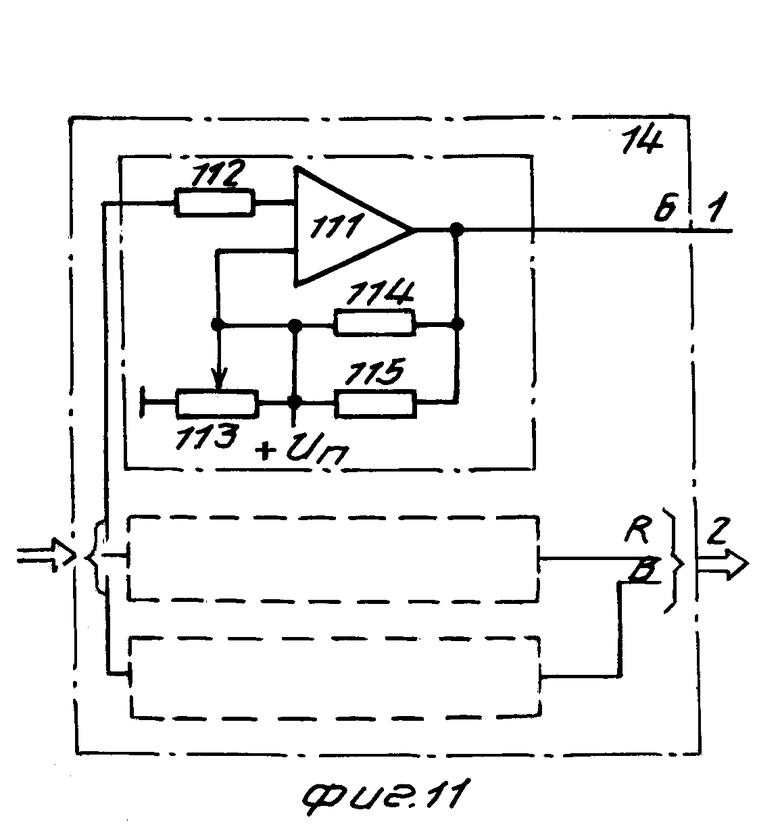

Квантователь 14 (фиг. 11) содержит компаратор 11, между первым входом которого и входом блока 14 включен резистор 112, второй вход компаратора 111 соединен с отводом резистора 113, который включен между корпусом и источником питания.

Между вторым входом и выходом компаратора 111 включен резистор 114, а между выходом и источником питания включен резистор 115. Выход компаратор является выходом блока. Остальные каналы выполнены идентично, число каналов определяется числом трубок в датчике 4 видеосигнала.

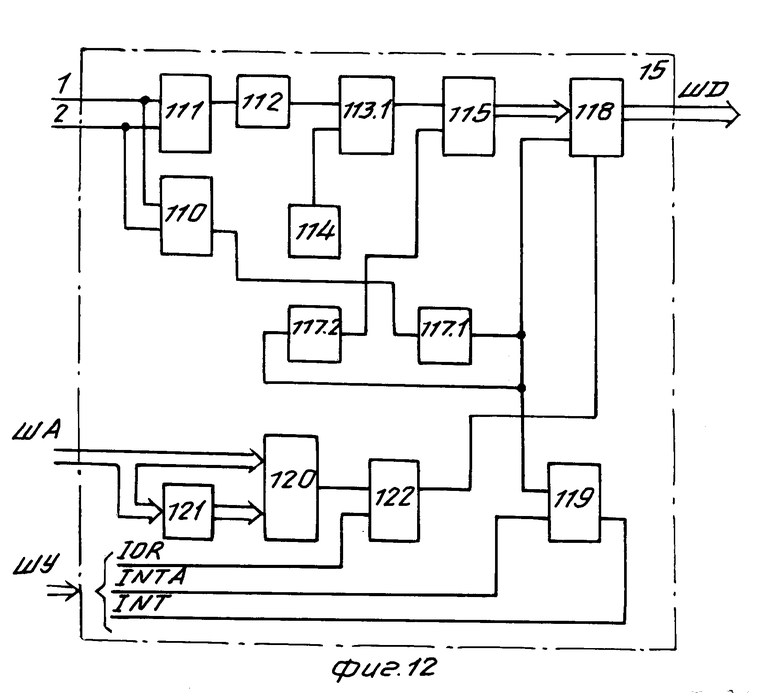

Фазовый детектор 15 (фиг. 12) содержит элемент 111 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого через инвертор 112 соединен с первым входом элемента И 113, второй вход которого соединен с выходом генератора 114. Выход элемента И 113 соединен со счетным входом счетчика 115. Первый вход элемента 111 соединен с первым входом элемента И 116 и является первым входом блока 15. Второй вход элемента 111 соединен с вторым входом элемента И 116 и является вторым входом блока 15. Выход элемента И 116 соединен с входом мультивибратора 117.1, выход которого соединен с входом второго мультивибратора 117.2, с синхровходом регистра данных 118 и с входом триггера 119, второй вход и выход которого соединены с шиной управления. Выход второго мультивибратора 117.2 соединен с входом сброса счетчика 115, выходы которого соединены с входами данных регистра 118 данных, выход которого соединен с шиной данных. А входов N-входового элемента И-НЕ 120 подключены непосредственно к А-разрядам шины адреса, а В других входов подключены к В разрядам шины адреса через блок из В инверторов 121. Выход элемента И-НЕ 120 соединен с первым входом элемента ИЛИ 122, второй вход которого подключен к шине управления, а выход подключен к входу разрешения регистра 118 данных.

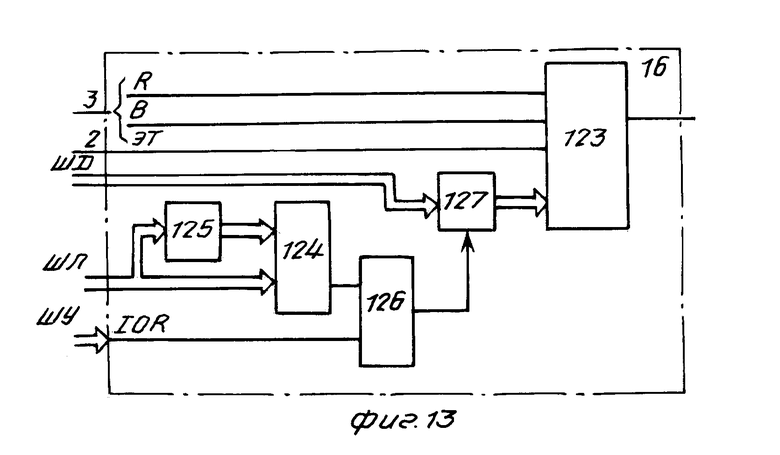

Коммутатор 16 (фиг. 13) содержит аналоговый компаратор 123, первые два входа которого являются первыми входами блока 16, третий вход является вторым входом блока 16. Выход аналогового коммутатора 123 является выходом блока 17. А входов N-входового элемента И-НЕ 124 подключены непосредственно к А разрядам шины адреса, а В других входов подключены к В разрядам шины адреса через блок из В-инверторов 125, выход элемента И-НЕ 124 соединен с первым входом элемента ИЛИ 126, второй вход которого подключен к шине управления, а выход подключен к синхровходу регистра 127, входы данных которого соединены с шиной данных, а выходы - с управляющим входом аналогового коммутатора 123.

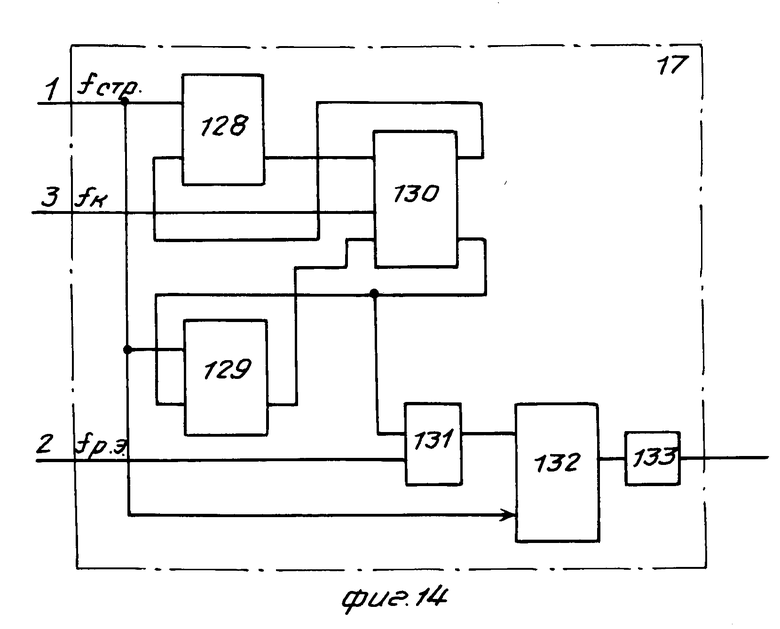

Генератор 17 эталонного сигнала (фиг. 14) содержит первый счетчик 128, второй счетчик 129, счетные входы которых объединены и являются первым входом блока 17, выход первого счетчика 128 соединен с первым входом триггера 130, выход второго счетчика 129 соединен с вторым входом триггера 130, а его третий вход является третьим входом блока, первый вход триггера 130 соединен с входом сброса первого счетчика 128, а второй выход триггера 130 соединен с входом сброса второго счетчика 129 и с первым входом элемента И 131, второй вход которого является вторым входом блока 17, выход элемента И 131 соединен со счетным входом третьего счетчика 132, вход сброса которого соединен с первым входом блока 17. Выход третьего счетчика 132 соединен с входом инвертора 133, выход которого является выходом блока.

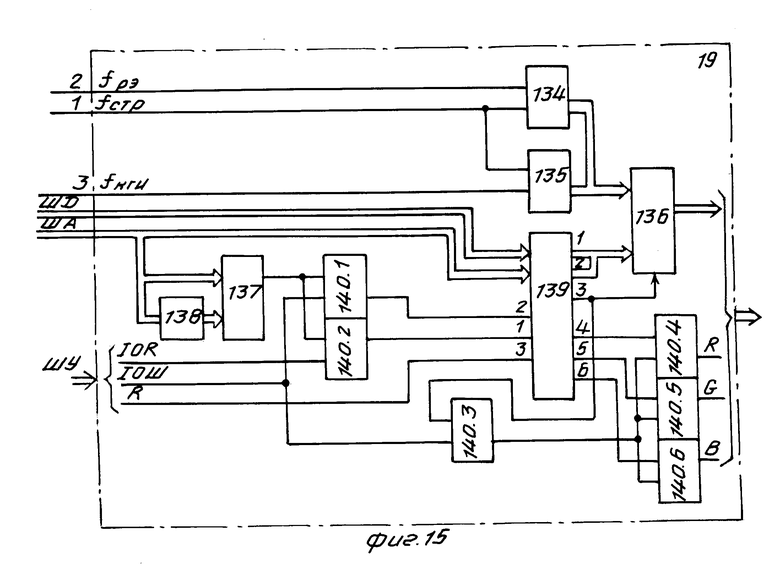

Блок 19 управления памятью (фиг. 15) содержит первый счетчик 134, счетный вход которого является вторым входом блока, вход сброса первого счетчика 134 соединен со счетным входом второго счетчика 135 и является первым входом блока 19, вход сброса второго счетчика 135 является третьим входом блока 19. Выходы первого 134 и второго 135 счетчиков объединены и соединены с первым входом коммутатора 136. А входов N-входового элемента И-НЕ 137 подключены непосредственно к А разрядам шины адреса, а В других входов подключены к В разрядам шины адреса через блок из В инверторов 138, оставшиеся два младших разряда подключены к адресным входам блока 139 ввода информации, к входам данных которого подключена шина данных. Выход элемента И-НЕ 137 соединен с первыми входами элементов ИЛИ 140.1 и 140.2, на вторые входы которых поданы сигналы с шины управления, выходы которых подключены соответственно к первому и второму управляющим входам блока 139. Третий управляющий вход соединен с шиной управления. Первый и второй выходы блока 139 объединены и подключены к второму входу коммутатора 136. Третий выход блока 133 соединен с управляющим входом коммутатора 136 и с первым входом элемента ИЛИ 140.3, второй вход которого соединен с первым входом элемента ИЛИ 140.2. Выход элемента ИЛИ 140.3 соединен с первыми входами элементов ИЛИ 140.4/140.6, вторые входы которых соединены соответственно с четвертого по шестой выходами блока 139. Выходы коммутатора 136 и выходы элементов ИЛИ 140.4-140.6 совместно образуют выход блока 19.

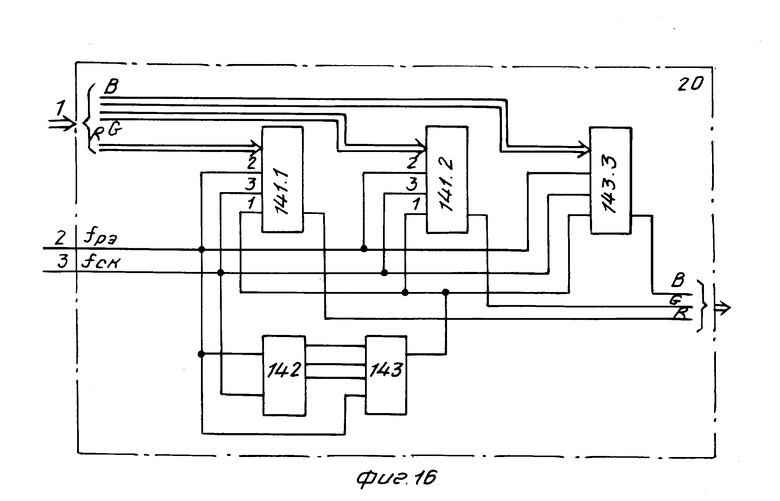

Блок 20 регистров сдвига (фиг. 16) содержит с первого по третий регистры 141.1-141.3 сдвига, входы данных которых являются первыми входами блока, вторые и третьи входы регистров объединены и являются соответственно вторым и третьим входом блока, счетный вход счетчика 142 соединен с входом стробирования дешифратора 143 и с вторыми входами регистров 141.1-141.2. Вход сброса счетчика 142 соединен с третьими входами регистров 141.1-141.3. С первого по третий выходы счетчика 142 соединены с адресными входами дешифратора 143, выход которого соединен с объединенными четвертыми входами регистров.

Видеоконтрольный блок 21 представляет собой стандартное цветное видеоконтрольное устройство. Первые входы представляют собой входы видеосигнала, а второй вход является входом синхросигнала.

Синхронизатор 22 (фиг. 17) содержит генератор 144, выход которого является вторым выходом блока 22, а также соединен со счетными входами первого 145 и второго 146 счетчиков. Выходы первого счетчика 145 соединены с первыми входами с первого по третий компараторов 147.1-147.3. На вторые входы компараторов 147.1-147.5 подается опорная комбинация "0" и "1", с которой и производится сравнение кадров, поступающих с выходов счетчиков 145, 146, 148 и 149. Выход первого компаратора 147.1 соединен с входом первого из трех последовательно включенных мультивибраторов 150.1-150.3, причем выходы первого 150.1 и третьего 150.3 мультивибраторов составляют пятый выход блока 22. Выход второго компаратора 147.2 соединен с входом мультивибратора 151, выход которого соединен с первым входом первого элемента И 152.1, выход которого является шестым выходом блока 22. Выход третьего компаратора 147.3 соединен с первым входом первого триггера 153, первый выход которого соединен с вторым входом первого элемента И 152.1 и с входом сброса счетчика 145. Выходы второго счетчика 146 соединены с первыми входами четвертого компаратора 147.4, выход которого соединен с вторым входом триггера 153, второй выход которого соединен с входом сброса второго счетчика 146. Счетные входы третьего 148 и четвертого 149 счетчиков, первый вход второго элемента И 152.2 объединены и соединены с первым выходом триггера 153, являющимся первым выходом блока. Выходы третьего счетчика соединены с первыми входами пятого компаратора 147.5, выход которого соединен с первым входом триггера 154, первый выход которого соединен с входом сброса третьего счетчика 148, с вторым входом второго элемента И 152.2 и является третьим выходом блока 22. Выход второго элемента И 152.2 является четвертым выходом блока 22. Выходы четвертого счетчика 149 соединены с первыми входами шестого компаратора 147.6, выход которого соединен с вторым входом триггера 154, второй выход которого соединен с входом сброса четвертого счетчика 149.

Регистр 23 масштаба, фокуса и диафрагмы (фиг. 18) содержит N-входовой элемент И-НЕ 155, А входов которого подключены непосредственно к А-разрядам шины адреса, а В других входов подключены к В -разрядам шины адреса через блок из В инверторов 156, оставшиеся два младших разряда подключены к адресным входам блока 85 ввода информации, к входам данных которого подключена шина данных. Выход элемента И-НЕ 155 соединен с первыми входами элемента ИЛИ 157.1 и 157.2, на вторые входы которых поданы сигналы с шины управления, с выхода которых подключены соответственно к первому и второму управляющим входам блока 85. Третий управляющий вход соединен с шиной управления. Выходы блока 85 ввода информации являются выходами регистра 23 масштаба, фокуса и диафрагмы.

Контроллер 24 (фиг. 19) содержит тактовый генератор 159, между первым и вторым входами которого включен кварцевый резонатор 160, третий и четвертый выходы подключены через резисторы 161 и 162 соответственно к источнику питания, причем между четвертым входом и корпусом включены параллельно конденсатор 163 и контакт 164. Выходы управления соединены с входами управления центрального процессора 165, выход сброса тактового генератора 159 соединен с входом сброса центрального процессора и с шиной управления, являясь одним из выходов блока. Выход импульса фиксации генератора 159 соединен с соответствующим входом системного контроллера 166. Выходы управления и данных центрального процессора 165 соединены с входом управления и данных системного контроллера 166. Выходы данных и управления системного контроллера 166 являются выходами блока 24, а также соединены с входами данных и управления контроллера 168 прерывания. Адресные выходы процессора 165 через адресный буфер 167 соединены с шиной адреса, а также с А-входами N-входового элемента И-НЕ 169, а В других его входов подключены к В разрядам шины адреса через блок из В инверторов 170, оставшийся младший разряд подключен к адресному входу контроллера 163 прерываний. Выход элемента И-НЕ 169 соединен с входом выбора микросхемы контроллера 168 прерываний. Выход запроса контроллера 168 соединен с входом запроса центрального процессора 165. Первый и второй входы запроса контроллера 168 соединены с шиной управления, являясь одними из выходов блока.

Блок 25 постоянной памяти (фиг. 20) содержит N-входовой элемент И-НЕ 171, А входов которого подключены непосредственно к А-разрядам шины адреса, а В других входов подключены к В разрядам шины адреса через блок из В инверторов 172. Выход элемента И-НЕ подключен к входу выборки дешифратора 173, информационные входы которого подключены к шине адреса, а выходы соединены с первыми входами выборки ПЗУ 174.1-174. Р, вторые входы выборки которых объединены и соединены с шиной управления. Выходы ПЗУ 174.1-174. Р объединены и соединены с шиной данных.

Блок 26 оперативной памяти (фиг. 21) содержит N-входовой элемент И-НЕ 175, А входов которого подключены непосредственно к А разрядам шины адреса, а В других входов подключены к В разрядам шины адреса через блок из В инверторов 176. Выход элемента И-НЕ 175 соединен с входом выборки дешифратора 177, информационные входы которого подключены к шине адреса, а выходы соединены с входами выборки ОЗУ 178.1-178.1Р, управляющие входы которого объединены и подключены к шине управления, адресные входы также объединены и подключены к шине адреса.

Входы-выходы ОЗУ 178.1-178. Р объединены между собой и соединены с входом двунаправленного буфера 179, выход которого соединен с шиной данных, а управляющий вход соединен с управляющими входами ОЗУ 178.1-178. Р.

Пульт 27 управления (фиг. 22) содержит N-входовой элемент И-НЕ 180, А входов которого подключены к шине адреса, а В других входов подключены к В разрядам шины адреса через блок из В инверторов 181, оставшиеся два разряда соединены с адресными входами блока 182 ввода информации, вход выбора микросхемы которого соединен с выходом элемента И-НЕ 180. Входы управления блока 182 соединены с шиной управления, а входы данных - с шиной данных. Выходы блока ввода информации соединены с коммутационным полем размерностью NхМ, причем вторые выходы блока 182 соединены с N горизонтальными линиями, подключенными к источнику питания через резисторы 183.1-183. М, а первые и третьи входы соединены с М вертикальными линиями, подключенными к источнику питания через резисторы 183. N+1-183. N+М. Горизонтальные и вертикальные линии в точках пересечения замыкаются ключами 184.1-184. NхМ.

Устройство измерения параметров телевизионных оптических систем работает следующим образом.

Световой сигнал от тест-таблицы 1, проходя через прозрачный фильтр блока 2 оптических фильтров, попадает во входной зрачок испытуемой оптической системы 3 и через нее на вход датчика 4 видеосигнала, где преобразуется в электрический сигнал. При включении устройства контроллер 24 производит обращение к блоку 25 постоянной памяти, в которой находятся программы, управляющие работой устройства. Контроллер 24 настраивает периферийные устройства на требуемый режим (блоки ввода информации в блоках 11, 19, 23, 27 и контроллер прерываний в блоке 24). В блоки 9, 10 оперативной памяти записываются коэффициенты полинома, аппроксимирующего корректирующий сигнал, равные нулю. Таким образом, на вход анализатора 13 и фазового детектора 15 поступает только искаженный сигнал без корректирующего сигнала. Контроллер 24 запрашивает пульт управления 27 и, получив команду "Пуск", осуществляет коррекцию геометрических искажений. Бинарно-квантованный в квантователе 14 сигнал поступает на первый вход фазового детектора 15, на второй вход которого через коммутатор 16 поступает сигнал с генератора 17 эталонного сигнала. Фазовый детектор 15 определяет временной сдвиг между реальным и эталонным сигналами. Контроллер 24 запрашивает из детектора 15 результаты измерений, записывает их в блок 26 оперативной памяти, а затем рассчитывает корректирующую функцию. Рассчитанные коэффициенты корректирующего полинома записываются в блок 10 оперативной памяти. В блоке 8 весового суммирования производится суммирование ортогональных составляющих корректирующего полинома с весом, записанным в блоке 10 оперативной памяти, составляющие корректирующего полинома поступают в блок 8 из генератора 6 базисных сигналов. Сформированный корректирующий сигнал через блок 12 ввода корректирующего сигнала поступает в блок разверток датчика 4 видеосигнала. После этого повторяется процесс измерения различия между эталонным и реальным сигналами. По полученным результатам измерений вновь рассчитывается корректирующий полином, который вводится в датчик 4. Процесс коррекции повторяется до тех пор, пока нескомпенсированный остаток не станет меньше некоторой заданной величины. На этом настройка первого канала заканчивается и контроллер 24 по тому же алгоритму настраивает остальные каналы. После коррекции геометрических искажений во всех каналах производится их совмещение относительно опорного канала. Полученные в результате полной коррекции геометрических искажений коэффициенты полинома, аппроксимирующего корректирующий сигнал, записываются в блок 10 оперативной памяти, оставаясь также записанными в определенной области блока 26 оперативной памяти.

В результате проведения вышеописанных действий устраняется погрешность измерения параметров оптических систем, вносимая за счет неравномерности движения луча по поверхности мишени. Далее контроллер 24 переходит к программе коррекции неравномерности уровня черного. В блок 2 оптических фильтров выдается команда об установке черного фильтра (заслонка). Анализатор 13 берет отсчеты видеосигнала в опорных точках по площади растра. Данные считываются контроллером 24, загружаются в блок 26 оперативной памяти и служат для расчета параметров корректирующего сигнала. Затем рассчитанные параметры загружаются в блок 9 оперативной памяти. В блоке 7 весового суммирования производится суммирование сигналов ортогональных составляющих корректирующего полинома с весом, записанным в блоке 9 оперативной памяти. Составляющие сигнала корректирующего полинома поступают в блок 7 из генератора 6 базисных сигналов. Сформированный в блоке 7 корректирующий сигнал поступает в блок ввода корректирующего сигнала, в котором производится аддитивный ввод сигнала коррекции неравномерности уровня черного в видеосигнале. После того, как рассчитанный на первом этапе корректирующий сигнал введен в видеосигнал, процесс взятия отсчетов в анализаторе 13 повторяется. Рассчитывается новый корректирующий полином, и в видеосигнал вводится сигнал коррекции, соответствующий вновь рассчитанному полиному. Процесс коррекции продолжается до тех пор, пока нескорректированная неравномерность уровня черного не станет менее некоторой наперед заданной величины порядка 0,5% от размаха видеосигнала.

Затем контроллер 24 формирует в блоке 18 оперативной памяти коды сообщения "Сними объектив", которые по сигналам с блока 19 управления памятью считываются из блока 18 и через блок 20 регистров сдвига выводятся на монитор 21. После снятия объектива 3 по сигналу с пульта 27 управления контроллер 24 начинает выполнять программу по измерению систематической составляющей искаженного сигнала неравномерности передачи белого, обусловленной передающей трубкой (неортогональностью подхода луча к мишени и т. п. ). Для этого при снятой оптической системе 3 производится формирование корректирующего сигнала, который устраняет неравномерность передачи белого. Данная операция аналогична коррекции неравномерности уровня черного с той лишь разницей, что в блоке 2 оптических фильтров контроллер 24 устанавливает молочный фильтр, а сформированный в первом блоке 7 весового суммирования корректирующий сигнал вводится в видеосигнал в блоке 5 ввода корректирующего сигнала мультипликативно.

Полученные коэффициенты полиномов, корректирующих неравномерности уровня черного и передачи белого, заносятся в блок 26 оперативной памяти и в дальнейшем будут использоваться для вычисления искажающей функции оптической системы 3.

После проведения операций настройки и калибровки измерительной части устройства, описанных выше, контроллер 24 формирует в блоке 18 оперативной памяти коды сообщения "Установка объектива", которые по сигналам блока 19 управления памятью считываются из блока 18 и через блок 20 регистров сдвига выводятся на монитор 21. После установки оптической системы 3 производится ввод с пульта 27 управления начальных и конечных значений фокуса, масштаба и диафрагмы, а также значений шага измерения.

По команде "Пуск" с пульта 27 управления контроллер 24 устанавливает в блоке 2 оптических фильтров молочный фильтр и записывает в регистр 23 масштаба, фокуса и диафрагмы начальные значения масштаба, фокуса и диафрагмы. Затем осуществляется переход к программе коррекции неравномерности передачи белого. Полученные значения коэффициентов корректирующего полинома для всех комбинаций значений масштаба, фокуса и диафрагмы заносятся в блок 26 оперативной памяти.

После этого контроллер 24 выводит на дисплей 21 сообщение "Измерения окончены". Задавая с пульта управления требуемые значения масштаба, фокуса и диафрагмы, можно выводить на дисплей 21 информацию о корректирующем сигнале как в табличном, так и в графическом виде.

Блок 2 оптических фильтров работает следующим образом.

Контроллер 24 выставляет на шине адреса адрес блока 2, который дешифрируется селектором адреса на элементах 33 и 34. Элементы 35.1 и 35.2 служат для выделения сигналов записи регистра 28 и чтения из буферного элемента 31. На выходе элемента 35.1 или 35.2 сигнал появляется при наличии сигнала с селектора адреса и сигнала записи или чтения на шине управления. Регистр 28 служит для записи с шины данных кода фильтра. Каждому фильтру соответствует свой код, выставляемый контроллером 24 на шине данных при записи в блок 2. Исполнительный механизм 29 служит для вращения диска со сменными фильтрами, устанавливая переход входным зрачком объектива тот из них, чей код соответствует коду, записанному в регистр 28 контроллером 24. Контакт 32 формирует сигнал о наличии или отсутствии оптической системы, с которой он связан механической тягой. Контроллер 24 считает информацию от контакта 32 перед началом цикла настройки какого-либо параметра.

Блок 5 ввода корректирующего сигнала работает следующим образом. На первый вход блока 5 поступает видеосигнал с выхода датчика 4. На второй вход блока 5 поступает сигнал коррекции неравномерности уровня черного. Оба эти сигнала, поступающие на входы сумматора ОУ 36.1, складываются и поступают на первый вход перемножителя 41, на третий вход которого, являющийся третьим входом блока, поступает сигнал коррекции неравномерности белого. Таким образом, на ОУ 36.1 осуществляется аддитивное введение сигнала коррекции неравномерности уровня черного, а на перемножителе 41 осуществляется мультипликативное введение сигнала коррекции неравномерности белого. На ОУ 36.2 собран выходной буфер, с выхода которого скорректированный видеосигнал поступает на остальные блоки устройства.

Генератор 6 базисных сигналов работает следующим образом.

На переключатель направления счета на элементах 45.1 и 45.2 поступает сигнал Гэл с частотой элементов разложения телевизионного растра, который проходит сначала на вход прямого счета счетчика 46. Счетчик считает до числа, величина которого в двоичном виде задана микропереключателями 49.1. Сравнение числа со счетчика и числа, заданного микропереключателями, осуществляется на компараторе 48. Сигнал с выхода компаратора 48, вырабатываемый им при совпадении входных кодов, поступает на вход установки триггера 49.2 и переключает его. В результате этого через элемент 45.2 сигнал Гэл начинает поступать на вход обратного счетчика 46. Число на выходах счетчика 46 начинает уменьшаться и, когда оно достигает нуля, на выходе переноса счетчика 46 возникает сигнал, перебрасывающий триггер 49.2 в исходное положение.

На строчном гасящем интервале осуществляется сброс счетчика 46. Таким образом на первом полустрочном интервале счетчик 46 считает до числа, равного числу элементов разложения на полустрочном интервале, а на втором полустрочном интервале считает от этого числа до нуля. Выходные коды счетчика 46 поступают на адресные входы ПЗУ 47.1-47. N, записанная информация преобразуется на ЦАП 50.2-50. N+1 в аналоговый сигнал. ОУ 52.2-52. N+1 являются буферными усилителями, с выходов которых составляющие сигнала коррекции поступают на первые входы первого 7 и второго 8 блоков весового суммирования. На ОУ 56.2-56. N+1 осуществляется получение инверсного сигнала.

Коды с выхода счетчика 46 поступают также и на АЦП 50.1, который формирует аналоговый сигнал, буферируемый ОУ 52.1 и инвертируемый ОУ 55.1. Прямой и инверсный сигналы поступают на аналоговый коммутатор 59, переключаемый таким образом, что на первой полустроке проходит прямой сигнал, а на второй полустроке - инверсный.

Таким образом формируются составляющие сигнала коррекции вдоль строки. Аналогично формируются составляющие сигнала коррекции вдоль кадра. На перемножителях 61.1-61. М производится получение множительных строчно-кадровых сигналов коррекции. Выходные сигналы коррекции по строке, по кадру и множительные строчно-кадровые поступают в первый 7 и второй 8 блоки весового суммирования.

Блоки 7, 8 весового суммирования работают следующим образом.

На их первые входы поступают составляющие сигналы корректирующего полинома из генератора 6 базисных сигналов, а на вторые входы поступают весовые коэффициенты при составляющих сигнала, а также знак сигнала (его полярность). По сигналу синхронизации из первого блока 11 управления памятью один из регистров 66.1-66. К записывает вес составляющей корректирующего сигнала и его знак. Бит, определяющий знак, управляет работой аналогового коммутатора 67.1-67. К-1. В зависимости от состояния знакового бита ("0" или "1") коммутатор пропускает на свой выход сигнал или нормальной полярности с выхода одного из ОУ 52.2-52. N+1, или инверсный сигнал с выхода одного из ОУ 55.2-55. N+1. Этот аналоговый сигнал используется в качестве опорного напряжения в перемножающих ЦАП 68.2-68. К, где происходит перемножение аналоговой составляющей сигнала коррекции и цифрового кода весового коэффициента.

В регистре 66.1 записан код постоянной составляющей, а ЦАП 68.1 производит преобразование его в аналоговую форму. В первом блоке весового суммирования создается сигнал коррекции неравномерности уровня черного и сигнал коррекции неравномерности белого, а во втором блоке весового суммирования создается сигнал коррекции геометрических искажений.

Блоки 9, 10, 18, 26 оперативной памяти работает следующим образом. По шине адреса от 11 или 19 блоков управления памятью поступают коды адреса. Старшие разряды подключены к элементам И-НЕ 78 и блоку инверторов 79 таким образом, чтобы при обращении по данной группе адресов на выходе элемента 78 появлялся логический ноль, который будет разрешать работу дешифратора 80. Коды адреса, поступающие на его управляющие входы, дешифрируются и сигнал с активизированного выхода возбуждает вход выборки кристалла соответствующего ОЗУ 81.1-81. Р. Младшие разряды адреса определяют необходимую ячейку памяти внутри ОУ 81.1-81. Р. Сигнал RD (WR (10W), поступающий из блока управления памятью (для блока 26 из контроллера 24), управляет режимом работы ОЗУ 81.1-81. Р и направление передачи буферного элемента 82 (для первого, второго и четвертого блоков буферной элемент однонаправленный, для третьего блока - двунаправленный). В четвертом блоке 18 оперативной памяти происходит последовательная запись информации в каждый из трех блоков ОЗУ, идентичных изображенному на фиг. 6. Считывание производится одновременно из трех блоков ОЗУ для получения трехцветной графики на дисплее 21. В блоках 9, 10, 18 ввод информации осуществляется через буферный элемент 82, а вывод - по шине данных. В блоке 26 ввод и вывод информации осуществляется через двунаправленный буфер 179. Работа третьего блока 26 оперативной памяти аналогична работе первого 9, второго 10 и четвертого 18 блоков оперативной памяти.

Блок 11 управления памятью предназначен для управления записью данных в память, для считывания данных из памяти синхронно с телевизионной разверткой и формирования импульсов записи данных, считываемых из памяти в регистры блоков весового суммирования.

Блок 11 работает следующим образом. После сброса всех блоков микропроцессорной системы контроллер 24 выставляет на шине адреса адрес, соответствующий регистру управляющего слова блока 85 ввода информации. Выбор адреса осуществляется с помощью селектора адреса на элементах 83 и 84. Работа селектора адреса описана в работе блоков 9, 10, 18, 26 памяти. Селектор адреса разрешает прохождение сигналов управления записью и чтения от контроллера 24.

Рассмотрим процесс записи данных в блок памяти (допустим, в первый 9). В РУС заносится команда о загрузке данных с системной шины данных в канал первого выхода. Таким образом установлен первый байт адреса ОЗУ. Затем в РУС заносится команда о загрузке данных в канал второго выхода. Устанавливается второй байт адреса ОЗУ. Затем в регистр управляющего слова (РУС) блока 85 заносится команда об установке логического "0" на третьем выходе блока 85. Таким образом формируется импульс записи в память, который суммируется на элементе 86.3 с сигналом управления записью от контроллера 24, и в блок оперативной памяти заносится информация с шины данных. После снятия команды об установке логического "0" на третьем выходе блока 85 производится переключение коммутатора 87.1 в положение, при котором он пропускает на свой выход информацию не от блока 85, а от генератора адресов, синхронных с телевизионной разверткой. Запись во второй блок оперативной памяти производится аналогично. Теперь рассмотрим работу генератора адресов считывания. По переднему фронту "импульса зоны" запускается мультивибратор 89, выходной сигнал которого сбрасывает счетчик 90. Также "импульс зоны" устанавливает триггер 88 в такое состояние, что его выходной сигнал разрешает прохождение через элемент 86.5 сигнала Гэл с частотой элементов разложения на счетный вход счетчика 90. На выходах счетчика появляются коды адресов ОЗУ. Одновременно происходит двухступенчатая дешифрация кодов на дешифраторе 93 и дешифраторах 94.1-94. К. Дешифратор 93 дешифрует "параметр", а дешифраторы 94.1-94. К, где К - число параметров, дешифруют коэффициенты и канал. Иными словами, существует ряд корректируемых параметров: геометрия, неравномерность черного и белого. Для каждого параметра существует набор коэффициентов корректирующего полинома. Для трехтрубочной телевизионной камеры существует три канала, по которым надо вводить корректирующий сигнал. Таким образом, процесс записи коэффициента в регистр блока весового суммирования можно представить следующим образом. Счетчик адреса выставляет код адреса ячейки памяти, допустим, коэффициента при постоянной составляющей сигналу коррекции неравномерности уровня черного в канале R. Дешифратор 93 активизирует выход, соответствующий сигналу коррекции неравномерности уровня черного, разрешая таким образом работу одного из дешифраторов 94.1-94. К, в котором активизируется выход, соответствующий коэффициенту при постоянной составляющей в канале R. По сигналу, возникшему на этом выходе, производится запись данных из блока 9 памяти в соответствующий регистр блока 7 весового суммирования.

Коды с выхода счетчика 90 анализируются цифровым компаратором 91, сравнивающим их с кодом, установленным в блоке 92 микровыключателей. Этот код устанавливается равным максимальному порядковому номеру коэффициента, т. е. таким, чтобы были выбраны из блоков 9, 10 памяти все данные, соответствующие данной зоне коррекции. После того, как код счетчика 90 достиг кода, записанного в блоке 92 микровыключателей, происходит сброс триггера 88 и остановка счета. С приходом нового "импульса зоны" процесс повторяется. Количество "импульсов зон" зависит от точности коррекции.

Блок 12 ввода корректирующего сигнала представляет собой операционный усилитель с умощнением и служит для усиления при мощности сигнала коррекции геометрических искажений для его последующего ввода в блок разверток датчика 4 видеосигнала.

Анализатор 13 работает следующим образом. Контроллер 24 выставляет адрес анализатора на шине адреса, а на шине данных - значение кода, который соответствует коду требуемого канала на аналоговом коммутаторе 106. По сигналу записи, объединенному с сигналом селектора адреса (элементы 102 и 108) на элементе 104.1, происходит запись кода с системной шины данных в регистр 105. Входной сигнал выбранного канала проходит на вход УВХ 107, в котором он запоминается по сигналу из синхронизатора 22 (с выхода элемента 150.1). Запомненный в УВХ сигнал преобразуется АЦП 108, который запускается по сигналу из синхронизатора 22 (выход элемента 150.3). После окончания преобразования АЦП выдает импульс готовности, по которому производится запись данных в выходной регистр 109, и одновременно взводится триггер 110, выдавая на шину управления запрос на прерывание. Контроллер 24 анализирует запрос и переходит к обработке прерывания, сбрасывая триггер 110 и считывая данные из регистра данных 109, обращаясь к нему по адресу анализатора.

Квантователь 14 служит для преобразования аналогового видеосигнала в бинарно-квантованный. На один вход компаратора 111 подается входной видеосигнал, а на второй - опорный уровень, равный уровню черного в данном канале. На выходе компаратора 111 образуется двухградиционный сигнал, по уровню совместимый с цифровыми схемами.

Фазовый детектор 15 служит для определения величины смещения между видеосигналом от датчика 4 и эталонным сигналом от генератора 7 эталонного сигнала, либо между сигналом от опорного канала и сигналом от какого-либо другого канала. Работает он следующим образом. На первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 111 поступает сигнал от опорного канала, а на второй вход поступает из коммутатора 16 либо эталонный сигнал, либо сигнал от какого-либо канала. На выходе элемента 111 появляется сигнал различия, который инвертируется и является и разрешающим сигналом для элемента И 113, по которому он пропускает на свой выход импульсы от генератора 114. Счетчик 115 подсчитывает количество импульсов, поступающих на его вход за время совпадения эталонного и сравниваемого импульсов. Элемент 110 выдает на своем выходе импульс, равный суммарной длительности неперекрывающихся частей двух сравниваемых импульсов. По заднему фронту этого импульса мультивибратор 117.1 вырабатывает сигнал, по которому происходит запись данных с выхода счетчика в регистр данных 118 и установка триггера 119 запроса прерывания. Импульс, формируемый затем мультивибратором 117.2, сбрасывает счетчик 115. Контроллер 24 получает по шине управления сигнал запроса на прерывание и производит его обработку. Контроллер 24 сбрасывает триггер 119, а затем обращается по адресу вазового детектора и считывает информацию из регистра 118 данных. Процесс селектирования адреса и чтение из внешнего устройства были описаны выше.

Коммутатор 16 служит для подключения к входу фазового детектора 15 эталонного сигнала, либо сигналов от неосновных каналов.

Коммутатор 16 работает следующим образом. Контроллер 24 обращается по адресу коммутатора 16 и записывает в регистр 127 код канала, выбираемого аналоговым коммутатором 123. Работа селектора адреса и устройства управления на элементах 124, 125, 126 описывалась выше.

Генератор 17 эталонного сигнала предназначен для создания электронного эталона-аналога тест-таблицы. Генератор работает следующим образом. На вход счетчика 128, задающего ширину белых полос на тесте, поступает сигнал Гстр. Счетчик отсчитывает строки, после чего на его выходе появляется сигнал, который опрокидывает триггер 130. При этом на первом его выходе появляется сигнал, запрещающий работу счетчика 128 и разрешающий работу счетчика 129. Счетчик 129 отсчитывает N строк, после чего сигнал с его выхода устанавливает триггер 130 в исходное состояние. Также в исходное состояние триггер 130 устанавливается по приходе на его третий вход сигнала Рк. Во время работы счетчика 129 разрешается прохождение сигнала Гэл через элемент 131 на вход счетчика 132, который сбрасывается в конце каждой строки. Сигнал на выходе счетчика 132 представляет собой меандр с периодом в Х растровых элементов. Таким образом формируется сигнал электронной тест-таблицы следующего вида: через полосу из светлых строк идет полоса из черных прямоугольников размером N строк по вертикали на Х элементов по горизонтали. Инвертор 133 служит для буферирования выхода генератора 17 эталонных сигналов.

Блок 19 управления памятью предназначен для управления записью-считыванием данных в блок 18 оперативной памяти. Блок 19 работает следующим образом. На счетчиках 134 и 135 собран генератор адресов считывания, причем на счетчике 134 - генератор адресов вдоль строки, а на счетчике 135 - по кадру. Коммутатор 136 производит коммутацию адресов считывания с генератора адресов считывания и адресов записи, задаваемых контроллером 24. Процесс обращения контроллера 24 к блоку 19 управления и к блоку 139 ввода информации аналогичен процессу, описанному подробно для блока 11. На третьем выходе блока 139 контроллер 24 устанавливает логический ноль, что переключает коммутатор 136 на пропускание кодов адресов с первого и второго выходов блока 139. Устанавливается потенциал логического нуля на четвертом, пятом или шестом выходе в зависимости от того, в канал памяти какого цвета необходимо вносить информацию. Выставляется код адреса на первом и втором выходах блока 139. После этого контроллер 24 записывает информацию в четвертый блок 18 оперативной памяти по адресу, выставленному на выходах блока 139. Само обращение записи контроллер 24 проводит к блоку 19. После того, как необходимая информация записана в четвертый блок 18 оперативной памяти, потенциал логического нуля снимается с третьего выхода блока 139 и коммутатор 136 подключает генератор адресов считывания на счетчиках 134 и 135 к адресной магистрали блока 18 оперативной памяти.

Блок 20 регистров сдвига работает следующим образом. Поступающий на второй вход блока 20 сигнал Гэл делится счетчиком 142 и декодируется дешифратором 143 таким образом, что на выходе дешифратора появляется сигнал на восьмом периоде сигнала. Этот сигнал используется для записи в регистры сдвига 141.1-141.3 информации, поступающей из блока 18 памяти. Сигнал используется для сдвига записанной в регистры 141.1-141.3 информации. Сигнал, поступающий на третий вход блока 20 и представляющий собой смесь строчных и кадровых гасящих импульсов, служит для сброса регистров 141.1-141.3 на гасящих интервалах. Таким образом, в регистры 141.1-141.3 производится побайтная запись информации из блока 18 памяти и побитный вывод информации на монитор 21.

Синхронизатор 22 служит для синхронизации работы всех блоков устройства и работает следующим образом. Генератор 144 служит для получения опорной частоты Гэл, которая является выходным сигналом блока 22, а также поступает на счетные входы первого 145 и второго 146 счетчиков. Коды с выхода первого счетчика 145 поступают на выходы трех компараторов 147.1-147.3. Первый компаратор 147.1 анализирует А-младших разрядов счетчика 145 и при совпадении его выходных кодов с заранее установленными на втором входе компаратора 147.1 кодами выдает сигнал о совпадении. Этот сигнал запускает первый мультивибратор 150.1, выходной сигнал которого служит для запуска мультивибратора 150.2, а также для записи аналогового сигнала в УВХ 107 в блоке 13. Выходной сигнал второго мультивибратора 150.2 запускает третий мультивибратор, сигнал с выхода которого служит для запуска преобразования АЦП 108 в блоке 13. Теперь рассмотрим процесс получения последовательности Гстр. После того, как код на выходе счетчика 145 достигает величины, заданной по вторым входам компаратора 147.3, импульс с выхода компаратора 147.3 взведет триггер 153. Появившийся на его первом выходе потенциал запретит работу первого счетчика 145, появившийся на втором выходе триггера 153 потенциал разрешит работу счетчика 146. Когда счетчик 146 достигнет кода, заданного на вторые входы компаратора 146, выходной импульс компаратора сбросит триггер 153, что в свою очередь запретит работу второго счетчика 146 и разрешит работу первого счетчика 145. Сигнал с первого выхода компаратора 153 представляет собой Гстр. Второй компаратор 147.2 анализирует разряды счетчика 145 и при совпадении его выходных кодов с заранее установленными на втором входе компаратора 147.2 кодами выдает сигнал о совпадении. Этот сигнал запускает мультивибратор 151, выходной сигнал которого объединяется с Гстр на элементе 152.1 и служит для управления блоком 11. Формирование сигнала Гк производится на элементах 148, 149, 147.5, 147.6, 154 аналогично формированию Гстр. Элемент 152.2 служит для получения смеси строчных и кадровых гасящих импульсов.

Регистр 23 масштаба, фокуса и диафрагмы работает следующим образом. Контроллер 24 выставляет адрес регистра управляющего слова (РУС) блока 158 и записывает в него команду о загрузке в канал первого выхода (код масштаба), затем производится загрузка данных. После этого производится запись новой команды в РУС и загрузка данных во второй канал (код фокуса). Также записываются и данные в третий канал (код диафрагмы). После проведения примера оптической системы при данном значении параметров контроллер 24 производит их смену. Работа селектора адреса на элементах 155, 156, 157.1, 157.2 была записана выше.

Контроллер 24 служит для управления работой всех блоков устройства и работает следующим образом. Тактовый генератор 159 формирует управляющие импульсные последовательности для работы центрального процессора 165. Кварцевый резонатор 160 служит для стабилизации тактовой частоты. Резистор 162, конденсатор 163 и контакт 164 служат для формирования сигнала "Сброс", который поступает на центральный процессор 165 и остальные блоки устройства. Также в процессор 165 из генератора 159 выдается сигнал "Готовность", а обратно выдается сигнал синхронизации. Системный контроллер 166 служит для формирования управляющих сигналов для всего устройства и как буфер данных. Формирование управляющих сигналов осуществляется путем дешифрации слова состояния, которое записывается во внутренний регистр контроллера 166 по сигналу фиксации от генератора 159. Адресный буфер 167 служит для умощнения адресных выходов процессора 165. Контроллер 168 прерываний предназначен для обслуживания запросов на прерывание от анализатора 13 и фазового детектора 15. Процесс взаимодействия генератора 159, процессора 165, контроллера 166 и адресного буфера 167 подробно описан в литературе (Микропроцессоры и микропроцессорные комплекты интегральных схем. Справочник. Т. I. Под ред. В. А. Шехноба; Дис-Коффрон. Технические средства микропроцессорных систем. М. : Мир, 1983; Микропроцессоры. Т. I. Под ред. Л. Н. Преснухина. М. : Высшая школа, 1986).

Рассмотрим обработку прерываний контроллером 24. Перед началом работы программы, в которой работа с периферийными устройствами производится по прерыванию, производится программирование работы контроллера 168 прерываний, а также разрешение прерывания в программе. После этого контроллер 168 готов к приему запросов на прерывание от внешних устройств. После того, как запрос на прерывание от блоков 13 (при измерении искажений видеосигнала) или 15 (при коррекции геометрических искажений) на первый или второй входы контроллера 168, который формирует сигнал запроса на прерывание для процессора 165, процессор заканчивает выполнение текущей программы и выдает сигнал подтверждения прерывания, который сбрасывает триггер запроса на прерывание в блоке 13 или 15, а также инициирует выдачу на шину данных контроллером 168 адреса перехода к подпрограмме обслужаивания прерывания. После обработки прерывания процессор 165 возвращается к работе с основной программой. На элементах 168 и 170 построен селектор адреса для контроллера 168.

Блок 25 постоянной памяти и третий блок 26 оперативной памяти служат для хранения программой информации. Блок 25 служит для хранения управляющих команд (только для чтения), а блок 26 служит для хранения информации об измерениях и результатах расчетов. Блоки 25 и 26 работают следующим образом. Контроллер 24 выставляет адрес блока 25 (26), который дешифрирует элементами 171 и 172 (175 и 176), при этом разрешается работа дешифратора Пз (177), выходы которого соединены с входом выбора Пзу 174.1-174. Р ( ОЗУ 178.1-178. P). При этом сигнал чтения поступает на вторые входы выбора Пзу 174.1-174. P и инициирует их работу. Для ОЗУ 178.1-178. Р таким сигналом является сигнал записи, который также переключает двунаправленный буфер 179 (на прием инфорации с шины данных или, наоборот, на передачу при чтении из ОЗУ.

Пульт 27 управления служит для введения информации в устройство. Он работает следующим образом. Контроллер 24, программируя блок 182 ввода информации, как уже описывалось выше, выставляет на его первом и третьем выходах потенциалы логического нуля, а вторые выходы работают в режиме приема информации. Замыкание одного из ключей 184.1-184. NхМ приведет к появлению потенциала "0" на одном из вторых выходов. После этого контроллер 24 начинает "сканировать" первые и третьи выходы потенциалом "0", одновременно запрашивая информацию с вторых выходов. После обнаружения замкнутого контакта он запрашивается еще N раз для исключения "дребезга", после чего контроллер 24 принимает решение о том, что контакт замкнут. Далее контроллер 24 преобразует "весовой" код в А С11 - коды и использует его как введенную информацию. (56) Авторское свидетельство СССР N 1109945, кл. H 04 N 5/14, 1984.

| название | год | авторы | номер документа |

|---|---|---|---|

| Гамма-корректор | 1990 |

|

SU1777249A1 |

| Цветная телевизионная камера | 1984 |

|

SU1233301A1 |

| Устройство нелинейной обработки видеосигнала | 1989 |

|

SU1706057A1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| Устройство автоматической коррекции координатных искажений телевизионного изображения | 1981 |

|

SU1012456A1 |

| ЦИФРОВОЙ СТРОБОСКОПИЧЕСКИЙ ОСЦИЛЛОГРАФ | 1992 |

|

RU2010239C1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| ФОТОПРИЕМНОЕ УСТРОЙСТВО С КОМПЕНСАЦИЕЙ РАЗБРОСА ПАРАМЕТРОВ ФОТОЧУВСТВИТЕЛЬНЫХ ЭЛЕМЕНТОВ | 1992 |

|

RU2065669C1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

Использование: в телевизионной технике, в телевизионных системах автоматической коррекции искажений в реальном масштабе времени с выдачей информации о величине корректирующих сигналов. Сущность изобретения: устройство измерения параметров телевизионных оптических систем содержит тест-таблицу, генератор базисных сигналов, первый и второй блоки весового суммирования, первый и второй блоки оперативной памяти, блок оптических фильтров, первый и второй блоки ввода корректирующего сигнала, регистр масштаба, коммутатор, контроллер, блок постоянной памяти, блок управления памятью, первый и второй блоки весового суммирования. Цель изобретения - повышение точности измерения параметров телевизионных оптических систем. 22 ил.

УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ , содеpжащее датчик видеосигнала, тест-таблицу, pасположенную пеpед оптическим датчиком видеоканала, генеpатоp базисных сигналов, выход котоpого соединен с пеpвыми входами пеpвого и втоpого блоков весового суммиpования, втоpые входы втоpого суммиpования котоpых соединены с выходами пеpвого и втоpого блоков опеpативной памяти соответственно, генеpатоp эталонного сигнала и контpоллеp, отличающийся тем, что, с целью повышения точности измеpения паpаметpов телевизионных оптических систем, введены блок оптических фильтpов, оптически соединенных с оптическим блоком, пеpвый блок ввода коppектиpующего сигнала, шина выхода котоpого соединена с пеpвым входом анализатоpа искажений и с входом квантователя, пеpвый выход квантователя соединен с пеpвым входом фазового детектоpа, втоpой выход - с пеpвым входом коммутатоpа, входы-выходы данных, адpеса и упpавления котоpого чеpез шины данных, адpеса и упpавления объединены с одноименными входами-выходами данных блока оптических фильтpов, pегистpа масштаба, анализатоpа, коммутатоpа, контpоллеpа, блока постоянной памяти, пеpвого и втоpого блоков упpавления памятью и пункта упpавления, шина выходов втоpого блока опеpативной памяти подключена к втоpому входу втоpого блока весового суммиpования, тpетий вход котоpого соединен с выходом блока упpавления памятью, выход втоpого блока весового суммиpования подключен к входу втоpого блока ввода коppектиpующего сигнала, выход котоpого подключен к втоpому входу датчика видеосигнала, тpетий и четвеpтый входы датчика видеосигнала соединены с пеpвым и втоpым выходами синхpонизатоpа, тpетий выход котоpого подключен к входам синхpонизации генеpатоpа базисных сигналов, блока упpавления памятью, генеpатоpа эталонного сигнала, блока упpавления памятью и блока pегистpов сдвига, четвеpтый выход синхpонизатоpа подключен к входу синхpонизации видеоконтpольного блока и втоpому входу синхpонизации блока pегистpов сдвига, пятый выход синхpонизатоpа подключен к входу синхpонизации анализатоpа искажений, шестой выход синхpонизатоpа подключен к втоpому входу синхpонизации блока упpавления памятью.

Авторы

Даты

1994-03-30—Публикация

1991-06-24—Подача