сэ ю

CD CD

ГО

Изобретение относится к вычислительной технике, а именно к устройствам управления накопителями на магнитных носителях (накопители на магнитных лентах, накопители на магнитных дисках и т.п.) в которых используется метод записи - фазовое кодирование.

. Целью изобретения является повышение помехозащищенности устройства.

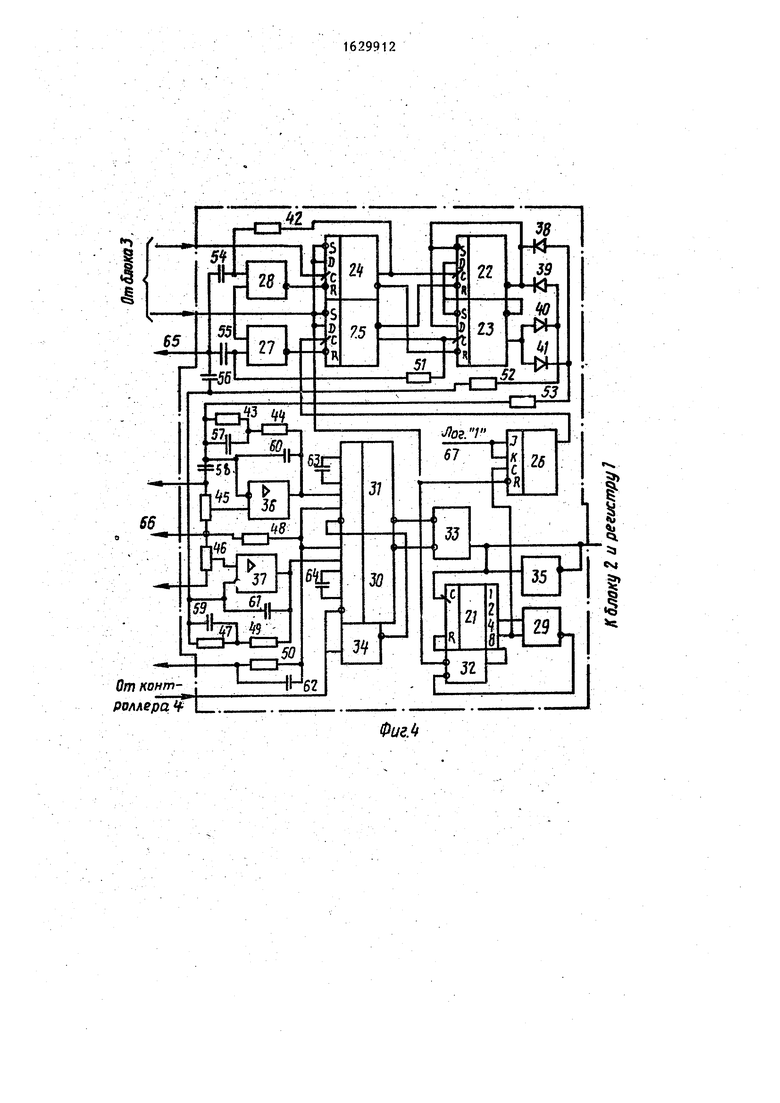

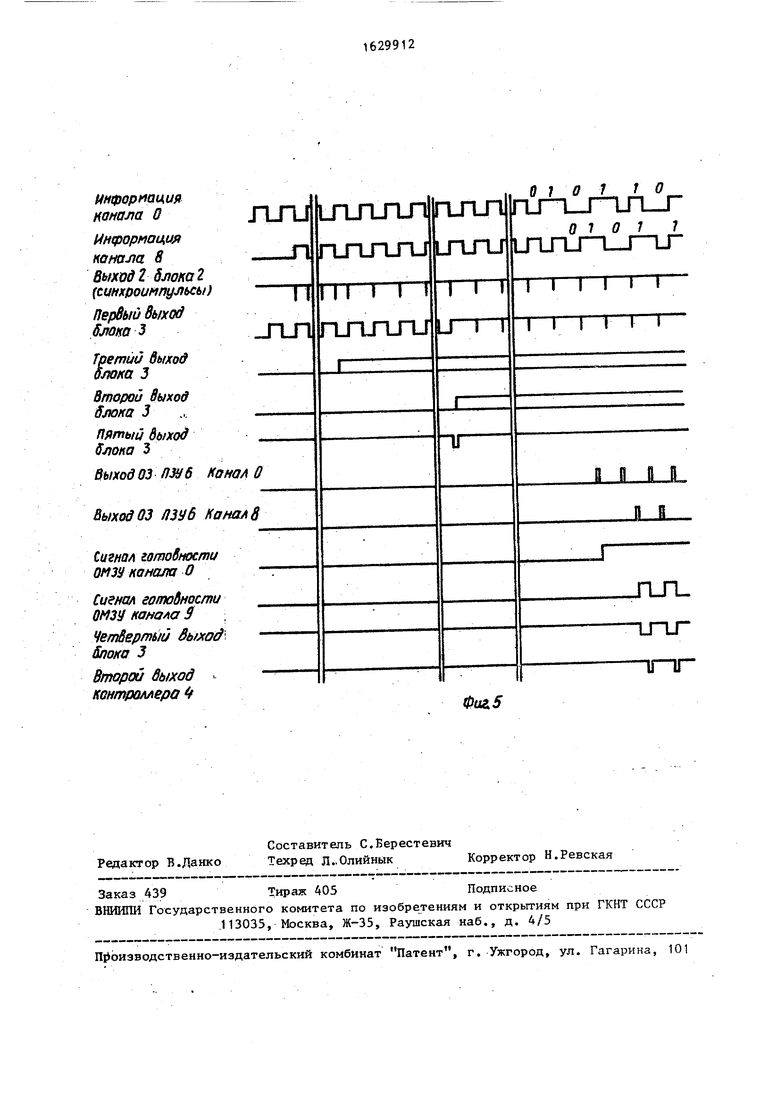

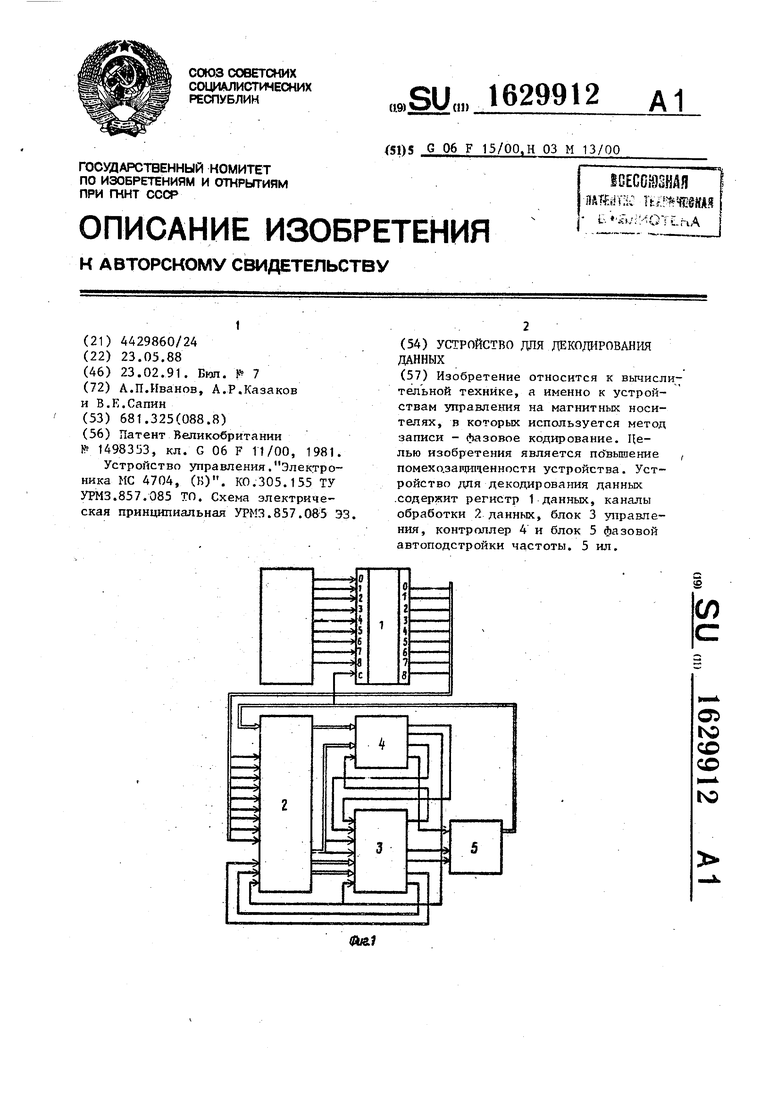

На фиг.1 изображена блок-схема устройства для декодирования данных; на фиг.2 - электрическая принципиальная схема канала обработки данных; на фиг.З - электрическая принципиальная схема блока управления; на фиг.4 электрическая принципиальная схема блока фазовой автоподстройки частоты; на фиг.З - временные диаграммы работы устройства.

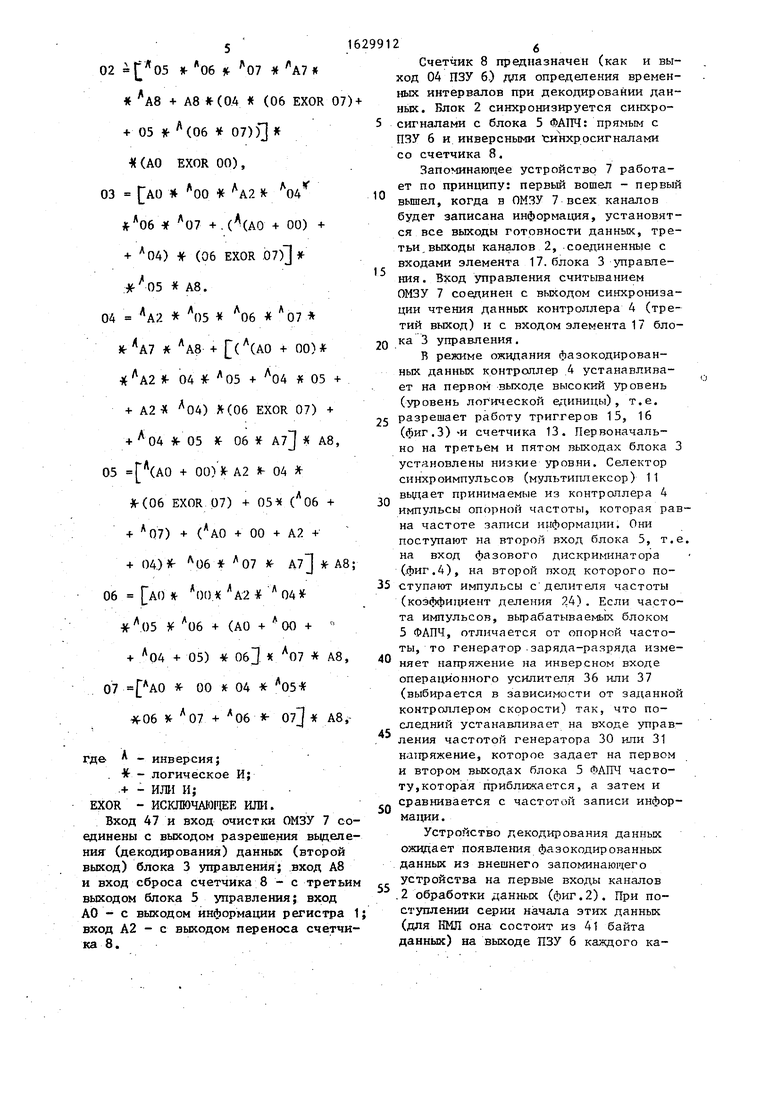

Устройство для декодирования данных (фиг.1) содержит регистр 1 данных, каналы 2 обработки данных,блок 3 управления, контроллер 4 и блок 5 фазовой автоподстройки частоты (АПЧ

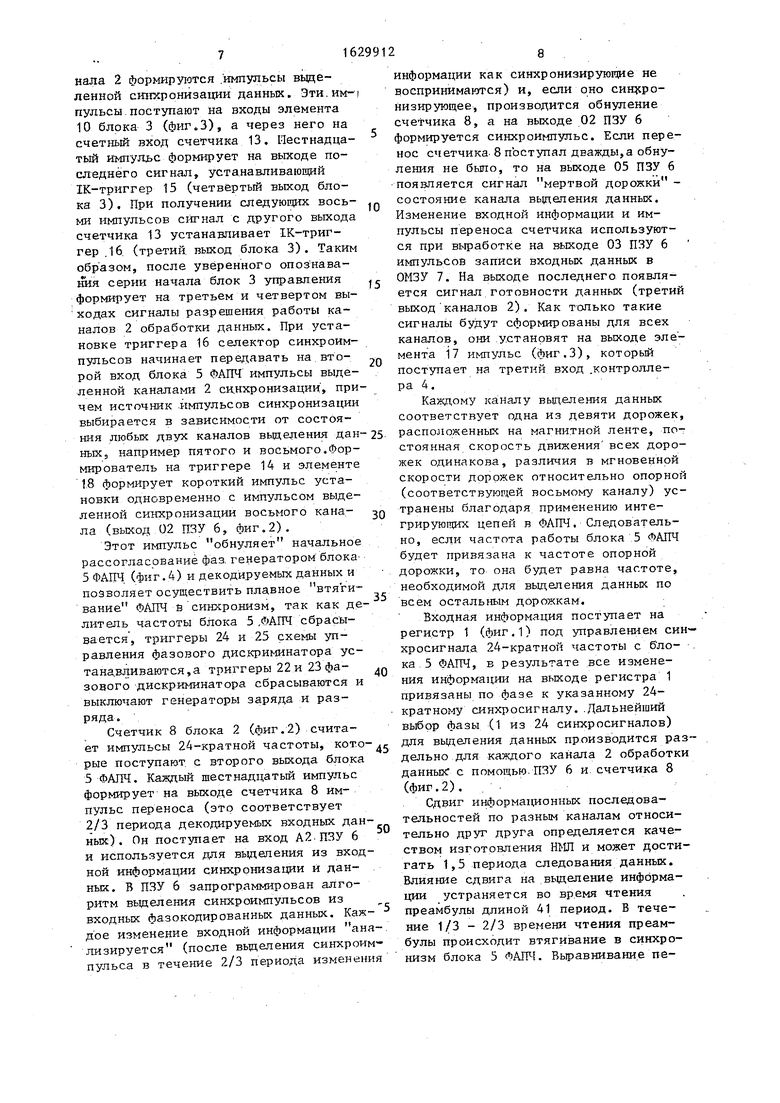

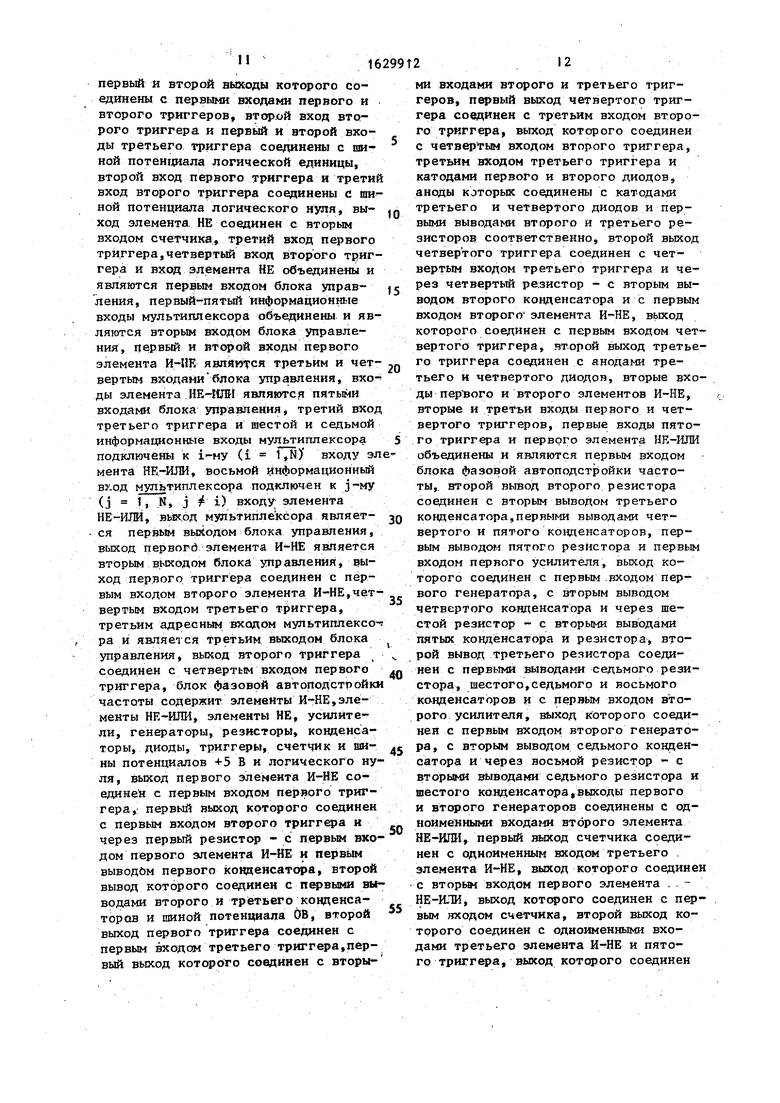

Канал обработки данных (фиг.2) содержит постоянное запоминающее устройство 6 (ПЗУ), запоминающее устройство 7 обратного магазинного типа (ОМЗУ), счетчик 8 и шину 9 потен- ,циала нуля.

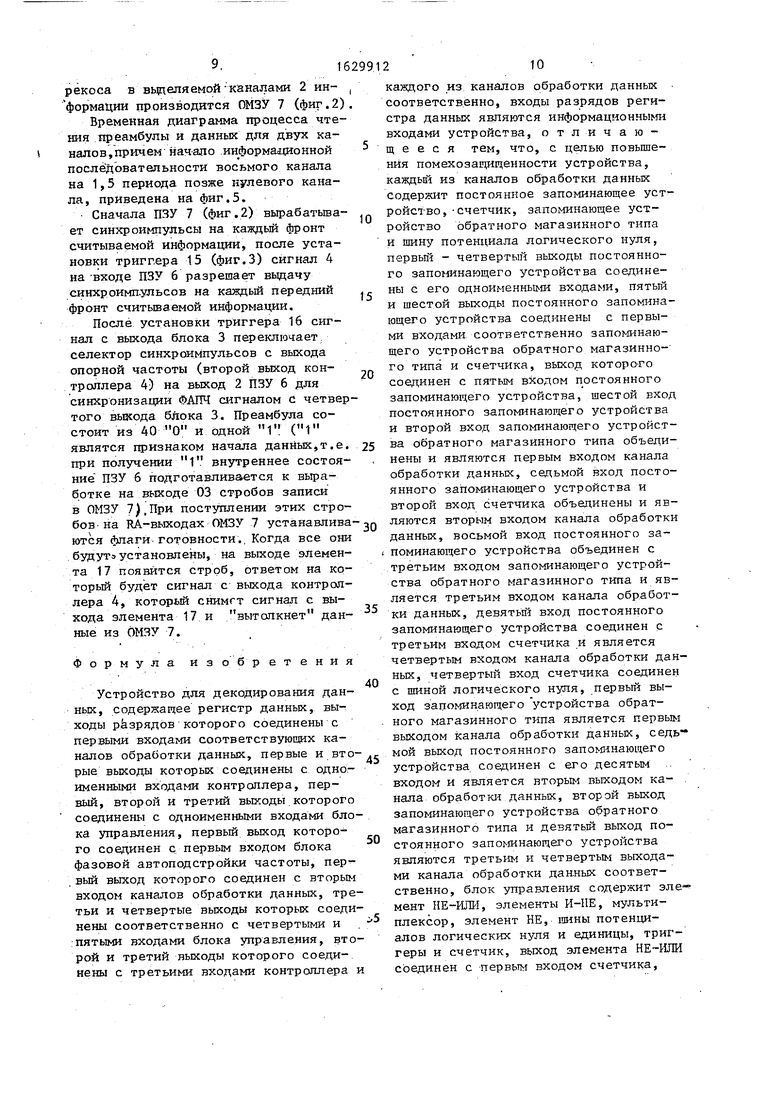

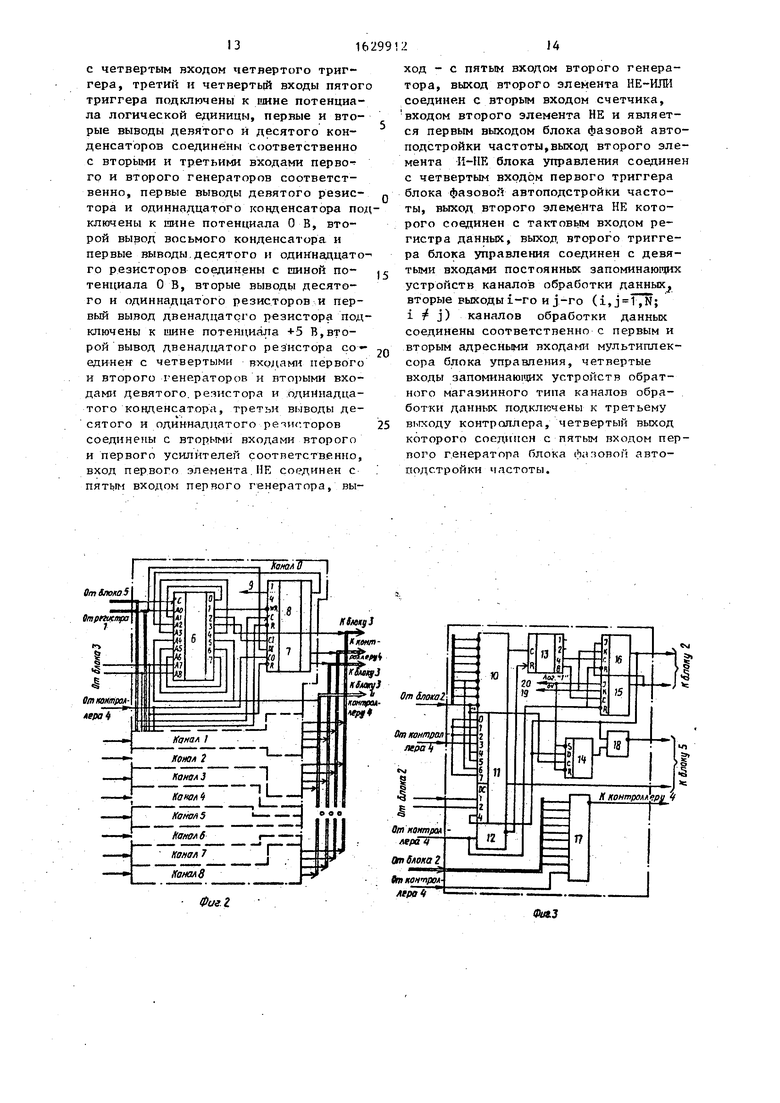

Блок управления (фиг.З) содержит элемент НЕ-ИЛИ 10, мультиплексор 11, элемент НЕ 12, счетчик 13, триггеры 14-16, элементы И-НЕ 17, 18 и шины 19, 20 потенциалов нуля и логической единица.

Блок ФА1ГЧ (фиг.4) содержит счетчи 21, триггеры 22-26, элементы И-НЕ 27 29, генераторы 30, 31, элементы НЕ-ИЛИ 32, 33, элементы НЕ 34, 35, усилители 36, 37, диоды 38-41, резисторы 42-53, конденсаторы 54-64, шин 65-67 потенциалов нуля и логической единицы +5 В.

Каналы 2 обработки данных предназначены для приема информации из внешнего запоминающего устройства, ее декодирования и формирования сигналов состояния каналов обработки данных.

Блок 3 управления предназначен для формирования сигналов, управляющих работой каналов 2, формирования импульсов сопровождения данных, считанных устройством, выработки синхроимпульсов и сигнала предустановки для блока 5 ФАПЧ.

C

5

0

5

0

5

0

5

п

5

Блок 5 предназначен для формирования синхронизирующих импульсов, которые сопровождают входные данные каналов 2 (при расхождении фаз синхроимпульса и входных данных вырабатывается сигнал рассогласования, который вызывает изменение частоты синхросигналов в сторону приближения ее к частоте входных данных).

В состав блока 5 ФАПЧ входят: фазовый дискриминатор на двух D-тригге- рах 22-23 со схемами управления, два D-триггера 24 и 25, два элемента И-НЕ 27, 28 с триггерами Шмитта на входе и элементами задержки на резисторах 42, 51, конденсаторах 54, 55, генераторы заряда-разряда - диоды 38 - 41, резисторы 52, 53, конденсаторы 56, 58, усилители 36, 37 с цепями коррекции на резисторах 43-47, 49 и конденсаторах 57, 59-61, генераторы 30,31, управляемые напряжением с элементами задания частотного диапазона, резисторами 48, 49 и конденсатором 62, объединенные по выходам элементом НЕ-ИЛИ 32, делитель частоты, который включает в себя счетчик 21, 1К-триггер 26, элементы 29,33-35.

ПЗУ 6 каналов обработки данных является автоматом с внутренними состояниями и имеет выходы:

00- задержанные на один период синхронизации входные данные (соединен с входом А1),

01- управление загрузкой счетчика 8,

02- выделейная из поступающих данных синхронизация,

03- управление записью данных в ОМЗУ 7,

04- внутреннее состояние (соединен с входом А3)ё

05- состояние канала (соединен с входом А4),

06- внутреннее состояние (соединен -с входом А5),

07- внутреннее состояние (соединен с входом Аб).

Указанные выходы функционируют по следующим формулам:

00 АО

01 (АО EXOR 00)

07 + ((06. EXOR 07) 05 + + Л06 А7 05) 04 А8,

5162991

02 ЈЛ05 Л06 % А07 # ЛА7

АА8 + А8 (04 (06 EXOR 07) + + 05 Л(06 07))5

#(АО EXOR 00),

03 ЈАО А00 ДА2 Х- А04 АОб Л07 + ((АО + 00) + + А04) # (06 EXOR 07) -/05 А8.

04 ЛА2 А05 Д06 А 07

10

15

АА7 ЛА8 + (Л(АО + 00)

АА2 - 04 - Л05 + А04 05 +

+ А2-Х Л04) (06 EXOR 07) +

+ Л04 05 06 А7 А8, 05 А(АО + 00) А2 - 04

(06 EXOR 07) + 05 (А06 +

f А07) + (ААО + 00 + А2 + + 04)- Л06 Л07 А А8;

06 АО Аоп АА2#

Х-А()5 К А06 + (АО + Л00 + « + А04 + 05) Об А07 А8,

00 04 А05

06 А 07 + А06 А8,

где Л инверсия;

# - логическое И;

+ - ИЛИ И| EXOR - ИСКЛЮЧАЮЩЕЕ ИЛИ.

Вход 47 и вход очистки ОМЗУ 7 соединены с выходом разрешения вьщеле- ния (декодирования) данных (второй выход) блока 3 управления; вход А8 и вход сброса счетчика 8 - с третьим выходом блока 5 управления; вход АО - с выходом информации регистра 1; вход А2 - с выходом переноса счетчк- ка 8.

0

5

0

5

30

5

40

45

50

5

Счетчик 8 предназначен (как и выход 04 ПЗУ 6) для определения временных интервалов при декодировании данных. Блок 2 синхронизируется синхросигналами с блока 5 АПЧ: прямым с ПЗУ 6 и инверсными синхросигналами со счетчика 8.

Запоминающее устройство 7 работает по принципу: первый вошел - первый вышел, когда в ОМЗУ 7 всех каналов будет записана информация, установятся все выходы готовности данных, третьи выходы каналов 2, соединенные с входами элемента 17.блока 3 управления . Вход управления считыванием ОМЗУ 7 соединен с выходом синхронизации чтения данных контроллера 4 (третий выход) и с входом элемента 17 блока 3 управления.

В режиме ожидания фазокодирован- ных данных контроллер 4 устанавливает на первом выходе высокий уровень (уровень логической единицы), т.е. разрешает работу триггеров 15, 16 (фиг.З) -и счетчика 13. Первоначально на третьем и пятом выходах блока 3 установлены низкие уровни. Селектор синхроимпульсов (мультиплексор) 11 выдает принимаемые из контроллера 4 импульсы опорной частоты, которая равна частоте записи информации. Они поступают на второй вход блока 5, т.е. на вход фазового дискриминатора (фиг.4), на второй вход которого поступают импульсы с делителя частоты (коэффициент деления 24). Если частота импульсов, вырабатываемых блоком 5 ФАПЧ, отличается от опорной частоты, то генератор заряда-разряда изменяет напряжение на инверсном входе операционного усилителя 36 или 37 (выбирается в зависимости от заданной контроллером скорости) так, что последний устанавливает на входе управления частотой генератора 30 или 31 напряжение, которое задает на первом и втором выходах блока 5 ЛДПЧ частоту,которая приближается, а затем и сравнивается с частотой записи информации .

Устройство декодирования данных ожидает появления фазокодированных данных из внешнего запоминающего устройства на первые входы каналов 2 обработки данных (фиг.2). При поступлении серии начала этих данных (для НМЛ она состоит из 41 байта данных) на выходе ПЗУ 6 каждого ка

нала 2 формируются импульсы выделенной синхронизации данных. Эти импульсы поступают на входы элемента 10 блока 3 (фиг.З), а через него на счетный вход счетчика 13. Пестнадца- тый импульс формирует на выходе последнего сигнал, устанавливающий 1К-триггер 15 (четвертый выход блока 3). При получении следующих восьми импульсов сигнал с другого выхода счетчика 13 устанавливает 1К-триг- гер 16 (третий выход блока 3). Таким образом, после уверенного опознавания серии начала блок 3 управления формирует на третьем и четвертом выходах сигналы разрешения работы каналов 2 обработки данных. При установке триггера 16 селектор синхроимпульсов начинает передавать на второй вход блока 5 ФАПЧ импульсы выделенной каналами 2 синхронизации, причем источник импульсов синхронизации выбирается в зависимости от состояния любых двух каналов выделения дан ныхэ например пятого и восьмого.Фор- мирователь на триггере 14 и элементе 18 формирует короткий импульс установки одновременно с импульсом выделенной синхронизации восьмого канала (выход 02 ПЗУ 6, фиг.2).

Этот импульс обнуляет начальное рассогласование фаз генератором блока 5 ФАПЧ (фиг. 4) и декодируемых данных и позволяет осуществить плавное втя ги

вание ФАПЧ в синхронизм, так как делитель частоты блока 5 ФАПЧ сбрасывается, триггеры 24 и 25 схемы управления фазового дискриминатора устанавливаются, а триггеры 22 и 23 фазового дискриминатора сбрасываются и выключают генераторы заряда и разряда.

Счетчик 8 блока 2 (фиг.2) счита

5

0

5

0

информации как синхронизирующие не воспринимаются) и, если оно синхронизирующее, производится обнуление счетчика 8, а на выходе 02 ПЗУ 6 формируется синхроимпульс. Если перенос счетчика 8 поступал дважды,а обнуления не было, то на выходе 05 ПЗУ 6 появляется сигнал мертвой дорожки - состояние канала выделения данных. Изменение входной информации и импульсы переноса счетчика используются при выработке на выходе 03 ПЗУ 6 импульсов записи входных данных в ОМЗУ 7. На выходе последнего появляется сигнал готовности данных (третий выход каналов 2). Как только такие сигналы будут сформированы для всех каналов, они установят на выходе элемента 17 импульс (фиг.З), который поступает на третий вход .контроллера 4.

Каждому каналу выделения данных соответствует одна из девяти дорожек, расположенных на магнитной ленте, постоянная скорость движения всех дорожек одинакова, различия в мгновенной скорости дорожек относительно опорной (соответствующей восьмому каналу) устранены благодаря применению интегрирующих цепей в ФАПЧ, Следовательно, если частота работы блока 5 ЛАПЧ будет привязана к частоте опорной дорожки, то она будет равна частоте, необходимой для выделения данных по всем остальным дорожкам.

Входная информация поступает на регистр 1 (фиг.1) под управлением синхросигнала 24-кратной частоты с блока 5 ФАПЧ, в результате все изменения информации на выходе регистра 1 привязаны по фазе к указанному 24- кратному синхросигналу. Дальнейший выбор фазы (1 из 24 синхросигналов)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| Цифровой термометр | 1987 |

|

SU1571427A1 |

| МОДУЛЬ СБОРА ДАННЫХ | 2008 |

|

RU2374683C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2024 |

|

RU2827940C1 |

| Широкодиапазонный синтезатор с фазовой автоподстройкой частоты управляемого генератора с переключаемыми резонаторами | 2023 |

|

RU2804407C1 |

| УСТРОЙСТВО МАГНИТНОЙ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОГО СИГНАЛА (ВАРИАНТЫ) | 1994 |

|

RU2127913C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Цифровой измеритель добротности | 1988 |

|

SU1647456A1 |

Изобретение относится к вычислительной технике, а именно к устройствам управления на магнитных носителях, в которых используется метод записи - фазовое кодирование. Целью изобретения является повышение t помехозащищенности устройства. Устройство для декодирования данных содержит регистр 1 данных, каналы обработки 2 данных, блок 3 управления, контроллер 4 и блок 5 фазовой автоподстройки частоты. 5 ил.

ет импульсы 24-кратной частоты, кото- ,с для выделения данных производится разрые поступают с второго выхода блока 5 сЬАПЧ. Каждый шестнадцатый импульс формирует на выходе счетчика 8 импульс переноса (это соответствует 2/3 периода декодируемых входных данных) . Он поступает на вход А2 ПЗУ 6 и используется для выделения из входной информации синхронизации и данных. В ПЗУ 6 запрограммирован алгоритм выделения синхроимпульсов из входных фазокодированных данных. Каждое изменение входной информации анализируется (после выделения синхроимпульса в течение 2/3 периода изменения

50

дельно для каждого канала 2 обработки данных1 с помощью ПЗУ 6 и счетчика 8 (фиг.2).

Сдвиг информационных последовательностей по разным каналам относительно друг друга определяется качеством изготовления НМЛ и может достигать 1,5 периода следования данных. Влияние сдвига на выделение информации устраняется во время чтения преамбулы длиной 41 период. В течение 1/3 - 2/3 времени чтения преамбулы происходит втягивание в синхронизм блока 5 ЛАПЧ. Выравнивание пе0

дельно для каждого канала 2 обработки данных1 с помощью ПЗУ 6 и счетчика 8 (фиг.2).

Сдвиг информационных последовательностей по разным каналам относительно друг друга определяется качеством изготовления НМЛ и может достигать 1,5 периода следования данных. Влияние сдвига на выделение информации устраняется во время чтения преамбулы длиной 41 период. В течение 1/3 - 2/3 времени чтения преамбулы происходит втягивание в синхронизм блока 5 ЛАПЧ. Выравнивание пе

у.16

рекоса в вьщеляемой-каналами 2 ин- формации производится ОМЗУ 7 (фиг,2)

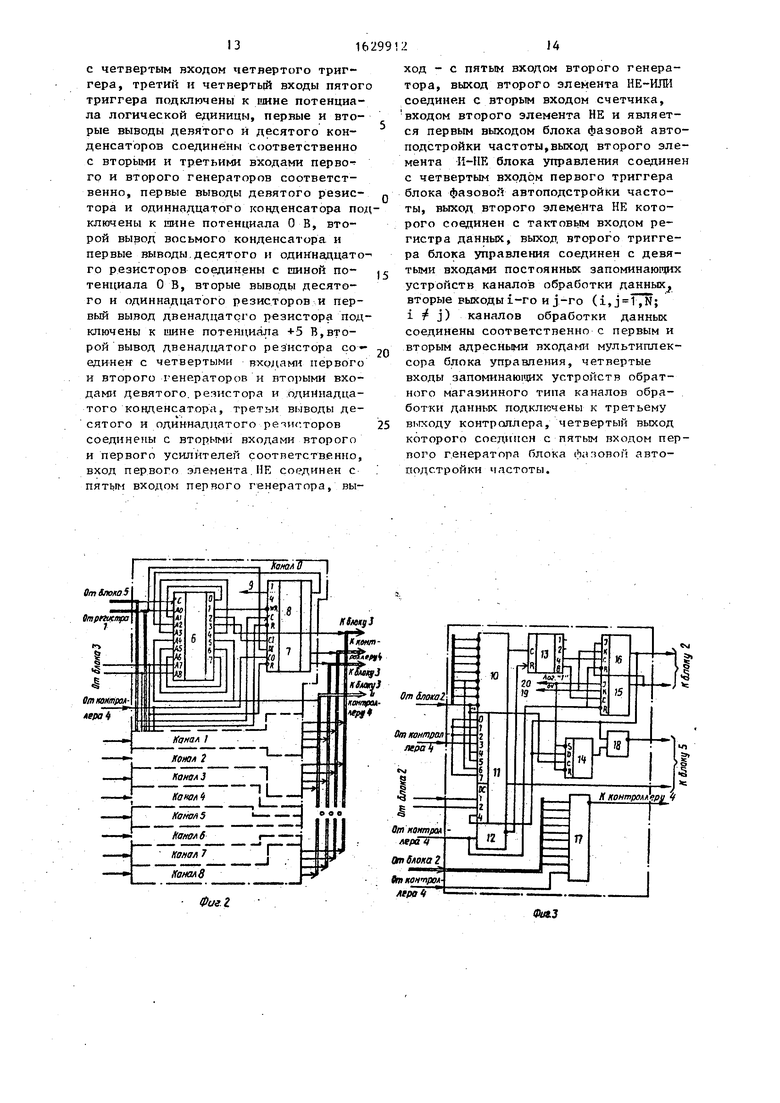

Временная диаграмма процесса чтения преамбулы и данных для двух каналов, причем начало информационной последовательности восьмого канала на 1,5 периода позже нулевого канала, приведена на фиг.5.

Сначала ПЗУ 7 (фиг.2) вырабатывает синхроимпульсы на каждый фронт считываемой информации, после установки триггера 15 (фиг.З) сигнал 4 на входе ПЗУ 6 разрешает выдачу синхроимпульсов на каждый передний фронт считываемой информации.

После установки триггера 16 сигнал с выхода блока 3 переключает селектор синхроимпульсов с выхода опорной частоты (второй выход контроллера 4) на выход 2 ПЗУ 6 для синхронизации ФАПЧ сигналом с четвертого выхода блока 3. Преамбула состоит из 40 О и одной 1 (1 являтся признаком начала данных,т.е. при получении 1 внутреннее состояние ПЗУ 6 подготавливается к выработке на выходе 03 стробов записи в ОМЗУ 7).При поступлении этих стро

бон на RA-выходах ОМЗУ 7 устанавлива

ются флаги готовности. Когда все они будут установлены, на выходе элемента 17 появится строб, ответом на который будет сигнал с выхода контроллера 4, который снимгт сигнал с выхода элемента 17 и вытолкнет дан- ные из ОМЗУ 7.

Формула изобретения

Устройство для декодирования данных, содержащее регистр данных, выходы разрядов которого соединены с первыми входами соответствующих каналов обработки данных, первые и вто- рые выходы которых соединены с одноименными входами контроллера, первый, второй и третий выходы которого соединены с одноименными входами блока управления, первый выход которого соединен с первым входом блока фазовой автоподстройки частоты, первый выход которого соединен с вторым входом каналов обработки данных, третьи и четвертые выходы которых соединены соответственно с четвертыми и пятыми входами блока управления, второй и третий выходы которого соединены с третьими входами контроллера и

12

10

0

5

5

0

0

0

,.

0

каждого из каналов обработки данных соответственно, входы разрядов регистра данных являются информационными входами устройства, отличающееся тем, что, с целью повышения помехозащищенности устройства, каждый из каналов обработки данных содержит постоянное запоминающее устройство, -счетчик, запоминающее устройство обратного магазинного типа и шину потенциала логического нуля, первый - четвертый выходы постоянного запоминающего устройства соединены с его одноименными входами, пятый и шестой выходы постоянного запоминающего устройства соединены с первыми входами соответственно запоминающего устройства обратного магазинного типа и счетчика, выход которого соединен с пятым входом постоянного запоминающего устройства, шестой вход постоянного запоминающего устройства и второй вход запоминающего устройства обратного магазинного типа объединены и являются первым входом канала обработки данных, седьмой вход постоянного запоминающего устройства и второй вход счетчика объединены и являются вторым входом канала обработки данных, восьмой вход постоянного за- поминающего устройства объединен с третьим входом запоминающего устройства обратного магазинного типа и является третьим входом канала обработки данных, девятый вход постоянного запоминающего устройства соединен с третьим входом счетчика и является четвертым входом канала обработки данных, четвертый вход счетчика соединен с шиной логического нуля, первый выход запоминающего устройства обратного магазинного типа является первым выходом канала обработки данных, седь мой выход постоянного запоминающего устройства соединен с его десятым входом и является вторым выходом канала обработки данных, второй выход запоминающего устройства обратного магазинного типа и девятый выход постоянного запоминающего устройства являются третьим и четвертым выходами канала обработки данных соответственно, блок управления содержит элемент НЕ-ИЛИ, элементы И-НЕ, мультиплексор, элемент НЕ, шины потенциалов логических нуля и единицы, триггеры и счетчик, выход элемента НЕ-ИЛИ соединен с первым входом счетчика,

1116

первый и второй выходы которого соединены с первыми входами первого и второго триггеров, второй вход второго триггера и первый и второй входы третьего триггера соединены с ши- ной потенциала логической единицы, второй вход первого триггера и третий вход второго триггера соединены с шиной потенциала логического нуля, выход элемента НЕ соединен с вторым входом счетчика, третий вход первого триггера,четвертый вход второго триггера и вход элемента НЕ объединены и являются первым входом блока управления, первый-пятый информационные входы мультиплексора объединены и являются вторым входом блока управления, первый и второй входы первого элемента И-ИК являются третьим и четвертым входами блока управления, входы элемента НЕ-НЛИ являются пятыми входами блока управления, третий вход третьего триггера и шестой и седьмой информационные входы мультиплексора подключены к i-му (i 1,Ю входу эл мента НЕ-ИЛИ, восьмой информационный вход мультиплексора подключен к j-му (J - 1 N, j 4- i) входу элемента НЕ-ИЛй, выход мультиплексора является первым выходом блока управления, выход первогб элемента И-НЕ является вторым выходом блока управления, выход первого триггера соединен с первым входом второго элемента И-НЕ,четвертым входом третьего триггера, третьим адресным входом мультиплексор ра и является третьим выходом блока управления, выход второго триггера соединен с четвертым входом первого триггера, блок фазовой автоподстройки частоты содержит элементы И-НЕ,элементы НЕ-ИЛИ, элементы НЕ, усилители, генераторы, резисторы, конденсаторы, диоды, триггеры, счетчик и ши- ны потенциалов +5 В и логического нуля, выход первого элемента И-НЕ соединен с первым входом первого триггера, первый выход которого соединен с первым входом второго триггера и через первый резистор - с первым входом первого элемента И-НЕ и первым выводом первого конденсатора, второй вывод которого соединен с первыми выводами второго и третьего конденсаторов и шиной потенциала 0В, второй выход первого триггера соединен с первым входом третьего триггера,первый выход которого соединен с вторы

Т2

12

0

5

0

,«

0

35

5

ми входами второго и третьего триггеров, первый выход четвертого триггера соединен с третьим входом второго триггера, выход которого соединен с четвертым входом второго триггера, третьим входом третьего триггера и катодами первого и второго диодов, аноды которых соединены с катодами третьего и четвертого диодов и первыми выводами второго и третьего резисторов соответственно, второй выход четвертого триггера соединен с четвертым входом третьего триггера и через четвертый резистор - с вторым выводом второго конденсатора и с первым входом второго элемента И-НЕ, выход которого соединен с первым входом четвертого триггера, второй выход третьего триггера соединен с анодами третьего и четвертого диодов, вторые входы пер вого и второго элементов И-НЕ, вторые и третьи входы первого и четвертого триггеров, первые входы пятого триггера и первого элемента НЕ-ИЛИ объединены и являются первым входом блока фазовой автоподстройки частоты, второй вывод второго резистора соединен с вторым выводом третьего конденсатора,первыми выводами четвертого и пятого конденсаторов, первым выводом пятого резистора и первым входом первого усилителя, выход которого соединен с первым входом первого генератора, с вторым выводом четвертого конденсатора и через шестой резистор - с вторыми выводами пятых конденсатора и резистора, второй вывод третьего резистора соединен с первыми выводами седьмого резистора, шестого,седьмого и восьмого конденсаторов и с первым входом второго усилителя, выход которого соединен с первым входом второго генератора, с вторым выводом седьмого конденсатора и через восьмой резистор - с вторыми выводами седьмого резистора и шестого конденсатора,выходы первого и второго генераторов соединены с одноименными входами второго элемента НЕ-ИЛИ, первый выход счетчика соединен с одноименным входом третьего элемента И-НЕ, выход которого соединен с вторым входом первого элемента НЕ-ИЛИ, выход которого соединен с первым входом счетчика, второй выход которого соединен с одноименными входами третьего элемента И-НЕ и пятого триггера, выход которого соединен

с четвертым входом четвертого триггера, третий и четвертый входы пятого триггера подключены к шине потенциала логической единицы, первые и вторые выводы девятого и десятого конденсаторов соединены соответственно с вторыми и третьими входами первого и второго генераторов соответственно, первые выводы девятого резистора и одиннадцатого конденсатора подключены к шине потенциала О В, второй вывод восьмого конденсатора и первые выводы десятого и одиннадцатого резисторов соединены с шиной потенциала О В, вторые выводы десятого и одиннадцатого резисторов и первый вывод двенадцатого резистора подключены к шине потенциала +5 В,второй вывод двенадцатого резистора соединен1 с четвертыми входами первого и второго генераторов и вторыми входами девятого резистора и одиннадцатого конденсатора, третьи выводы десятого и одиннадцатого ретисторов соединены с вторыми входами второго и первого усилителей соответственно, вход первого элемента НЕ соединен с пятым входом первого генератора, вы

Фаг1

5

ход - с пятым входом второго генератора, выход второго элемента НЕ-ИЛИ соединен с вторым входом счетчика, входом второго элемента НЕ и является первым выходом блока фазовой автоподстройки частоты,выход второго элемента И-НЕ блока управления соединен с четвертым входом первого триггера блока фазовой автоподстройки частоты, выход второго элемента НЕ которого соединен с тактовым входом регистра данных, выход второго триггера блока управления соединен с девятыми входами постоянных запоминающих устройств каналов обработки данных вторые выходы 1-го и j-го (i, j 1 ,N; i j) каналов обработки данных соединены соответственно с первым и вторым адресными входами мультиплексора блока управления, четвертые входы запоминающих устройств обратного магазинного типа каналов обработки данных подключены к третьему выходу контроллера, четвертый выход которого соединен с пятым входом первого генератора блока Лотовой автоподстройки частоты.

Фа.3

Отконт- : роллера

Информация канола О

Информация канала 8

Выход 2 блока 2 {синхроимпульсы

Первый Выход блока 3

Третий выход блока J

Второй Выход блока J

Пятый foixod блока 3

Выход03 ПЗУ 6 Кона А О

Выход 03 ПЗУ 6 Ко нал 8

Сигнал ютоВности омзу комола О

Сигнал готобнос/пи ОМЗУ канала 9

Че/пВерлк/й выход 5поко 3

Второй дыход . контроллера t

Фиг 5

| Патент Великобритании № 1498353, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Машина для подземной прокладки электрических кабелей | 1924 |

|

SU4704A1 |

| Держатель для поленьев при винтовом колуне | 1920 |

|

SU305A1 |

| Радиатор | 1925 |

|

SU857A1 |

Авторы

Даты

1991-02-23—Публикация

1988-05-23—Подача