Изобретение относится к устройствам сбора данных и их регистрации и может быть применено в технологическом оборудовании комплексов полунатурного моделирования и автоматизированного контроля для ввода/вывода аналоговых сигналов в/из ЭВМ.

Известно устройство сбора данных (см. патент на изобретение РФ №1642883, МПК G06F 17/40 (2006.01), опубл. 10.02.2006 г., по заявке №4694788/24 от 22.05.1989 г., патентообладатели Губарев В.П., Ефимов В.Б., Ковалев В.Н.), содержащее блок ввода и преобразования аналоговой информации (БВПАИ), включающий в себя N трактов преобразования, запоминающее устройство (ЗУ), управляющий вычислитель (УВ), блок синхронизации, состоящий из коммутатора сигналов внешней синхронизации, формирователя длинных и коротких импульсов, источника эталонной частоты, счетчика, двух элементов И, элемента ИЛИ, блока управления, содержащего делитель частоты, четыре триггера, таймер, элемент ИЛИ, элемент И. Существует задача, когда быстродействующее устройство ввода аналоговой информации перегружает центральный процессор. Эта задача решается в устройстве сбора данных дополнением устройства аналогового ввода операционным запоминающим устройством (ОЗУ).

Признаки аналога, совпадающие с признаками заявляемого технического решения, следующие: запоминающее устройство (ЗУ), блок синхронизации, таймер.

Причиной, препятствующей достижению заявляемого технического результата, является то, что данное устройство сбора данных имеет ограниченное быстродействие, так как ввод данных по прерыванию имеет ограниченную скорость передачи данных даже при условии, что осуществляется только передача данных без проверки условий или преобразования формата данных, и не обеспечивает преобразование цифрового кода в непрерывные электрические сигналы напряжения, масштабирование непрерывных электрических сигналов напряжения, организацию контуров управления, непрерывную регистрацию входных и выходных сигналов в привязке к единому времени, построение синхронных систем с единым временем, построение требуемых циклограмм работы.

Частично устраняет недостатки аналога известное устройство сбора данных (см. патент на изобретение РФ №2218596, МПК 7 G06F 17/40, опубл. 10.12.2003 г., по заявке №2002100959/09 от 08.01.2001 г., патентообладатель Открытое акционерное общество "Ульяновское конструкторское бюро приборостроения"), содержащее блок ввода информации, двухвходовое оперативное запоминающее устройство (ОЗУ), буфер, блок адресации, блок управления, регистр адреса, блок сравнения кодов и формирователь импульса записи. Устройство сбора данных за счет обеспечения автономного процесса опроса и преобразования данных позволяет разгрузить центральный процессор, исключить затраты машинного времени на обслуживание устройства и тем самым повысить быстродействие и имеет небольшие аппаратные затраты на реализацию по сравнению, например, с устройствами, использующими прямой доступ в память центрального процессора. Данное устройство более эффективно и надежно при использовании в системах преобразования аналоговой и дискретной информации, обслуживающих большое число контролируемых объектов.

Признаки аналога, совпадающие с признаками заявляемого изобретения, следующие: временной таймер, ОЗУ.

Причиной, препятствующей достижению заявляемого технического результата, является то, что данное устройство сбора данных не обеспечивает преобразование цифрового кода в непрерывные электрические сигналы напряжения, масштабирование непрерывных электрических сигналов напряжения, организацию контуров управления, непрерывную регистрацию входных и выходных сигналов в привязке к единому времени, построение синхронных систем с единым временем, построение требуемых циклограмм работы.

Известна наиболее близкая к заявляемому изобретению универсальная плата аналого-цифрового преобразования для IBM PCI/AT-совместимых компьютеров ЛА-1,5РСI (см. руководство по эксплуатации ВКФУ.411619.060 РЭ закрытого акционерного общества «Руднев - Шиляев»), содержащая аналого-цифровой канал, счетчик-таймер, кварцевый генератор, программируемый делитель частоты, цифровой порт ввода-вывода, внутренний интерфейс управления и конфигурации, интерфейс PCI и вторичный источник питания.

Техническое решение позволяет частично решить поставленную задачу, а именно осуществлять преобразование непрерывных (аналоговых) входных сигналов в цифровую форму, которая удобна для дальнейшей обработки сигнала при помощи персональной ЭВМ, то есть выполнять аналого-цифровое преобразование. Тем не менее, с его помощью невозможно обеспечить трансляцию и генерацию сигналов из-за отсутствия аналоговых выходов на плате, а осуществить построение синхронных систем возможно только при наличии внешнего генератора.

Признаки аналога, совпадающие с признаками заявляемого изобретения, следующие: интерфейс PCI, кварцевый генератор, внутренняя шина данных и управления.

Причиной, препятствующей достижению заявляемого технического результата, является то, что известное техническое решение не обеспечивает преобразование цифрового кода в непрерывные электрические сигналы напряжения, масштабирование непрерывных электрических сигналов напряжения, непрерывную регистрацию входных и выходных сигналов в привязке к единому времени, построение синхронных систем с единым временем, построение требуемых циклограмм работы.

Задача, на решение которой направлено заявляемое техническое решение, заключается в создании модуля сбора данных для преобразования непрерывных электрических сигналов напряжения в цифровую форму, для преобразования цифрового кода в непрерывные электрические сигналы напряжения, для масштабирования непрерывных электрических сигналов напряжения, для организации контуров управления, для регистрации входных и выходных сигналов в привязке к единому времени, для построения синхронных систем с единым временем, для построения требуемых циклограмм работы.

Технический результат, обеспечиваемый при реализации заявляемого технического решения, заключается в возможности:

- преобразования непрерывных электрических сигналов напряжения в цифровую форму за счет применения блоков измерения напряжения и синхронного динамического ОЗУ;

- преобразования цифрового кода в непрерывные электрические сигналы напряжения за счет применения генераторов сигналов произвольной формы и синхронного динамического ОЗУ с программируемой логической интегральной схемой DD3 с блоками управления всеми процессами;

- масштабирования непрерывных электрических сигналов напряжения за счет применения генератора сигналов произвольной формы с синхронным динамическим ОЗУ;

- организации контуров управления за счет применения генератора сигналов произвольной формы, синхронных динамических ОЗУ и блока измерения напряжения;

- регистрации входных и выходных сигналов в привязке к единому времени за счет применения генератора сигналов произвольной формы, синхронных динамических ОЗУ, блока измерения напряжения и входящих в состав программируемой логической интегральной схемы DD3 генератора прерываний по событиям и временного таймера;

- построения синхронных систем с единым временем за счет применения блока межмодульной синхронизации и временного таймера;

- построения требуемых циклограмм работы за счет применения блока межмодульной синхронизации.

Указанный технический результат при осуществлении изобретения обеспечивается тем, что в модуль сбора данных (МСД), содержащий ускоритель ввода/вывода, первое последовательное постоянное запоминающее устройство (ППЗУ), программируемый синтезатор частот (ПСЧ), первый блок измерения напряжения (БИН), кварцевый генератор (КГ), дополнительно введены программируемая логическая интегральная схема DD3 (ПЛИС DD3), программируемая логическая интегральная схема DD5 (ПЛИС DD5), первое синхронное динамическое ОЗУ (СДОЗУ), локальная шина (ЛШ), второе СДОЗУ, генератор сигналов произвольной формы (ГСПФ), мезонинная плата (мезонин), разъем, второе последовательное ПЗУ, блок внешнего запуска (БВЗ), причем вход-выход ПЛИС DD5, второй вход-выход ускорителя ввода/вывода и первый вход-выход ПЛИС DD3 соединены между собой через входы-выходы локальной шины, первый вход-выход ускорителя ввода/вывода соединен с входом-выходом первого последовательного ПЗУ, второй вход-выход ПЛИС DD3 соединен с входом-выходом второго синхронного динамического ОЗУ, третий вход-выход ПЛИС DD3 - с первым входом-выходом первого генератора сигналов произвольной формы, четвертый и пятый входы-выходы ПЛИС DD3 - с входами-выходами программируемого синтезатора частот, шестой и седьмой входы-выходы ПЛИС DD3 - с третьим и четвертым входами-выходами мезонина, восьмой вход-выход ПЛИС DD3 - с входом-выходом второго последовательного ПЗУ, девятый вход-выход ПЛИС DD3 - с входом-выходом первого синхронного динамического ОЗУ, десятый вход-выход ПЛИС DD3 - с первым входом-выходом первого блока измерения напряжения, одиннадцатый вход-выход ПЛИС DD3 - с входом-выходом кварцевого генератора, двенадцатый вход-выход ПЛИС DD3 - с первым входом-выходом блока внешнего запуска, тринадцатый вход-выход ПЛИС DD3 - с четвертым входом-выходом разъема, к первому и пятому входам-выходам разъема подсоединены вторые входы-выходы первого генератора сигналов произвольной формы и первого блока измерения напряжения соответственно, второй и шестой выходы разъема соединены с первым входом мезонина и вторым входом блока внешнего запуска соответственно, третий вход разъема соединен с вторым выходом мезонина, причем ПЛИС DD3 содержит первый адаптер «Локальная шина - синхронное динамическое ОЗУ» (АЛШ-СДОЗУ), второй АЛШ-СДОЗУ, первый арбитр синхронных динамических оперативных запоминающих устройств (АСДОЗУ), второй АСДОЗУ, первый контроллер синхронных динамических оперативных запоминающих устройств (КСДОЗУ), второй КСДОЗУ, генератор прерываний по событиям (ГПС), контроллер программируемого синтезатора частот (КПСЧ), контроллер первого генератора сигналов произвольной формы (КГСПФ), блок межмодульной синхронизации (БМС), набор функциональных блоков мезонина (ФБМ), загрузчик мезонина (ЗМ), контроллер локальной шины (КЛШ), временной таймер (ВТ), контроллер прерываний (КП), блок регистров (БР), блок цифровой обработки и трансляции сигналов (БЦОТС), генератор сигналов синхронизации по событиям (ГССПС), контроллер блока внешнего запуска (КБВЗ), контроллер второго последовательного ПЗУ (КППЗУ), блок задержки прерываний по переключению банков приемников (БЗПП), контроллер первого блока измерения напряжения (КБИН), регистратор событий (PC), блок программной генерации сигнала синхронизации (БПГСС), систему фазовой автоподстройки частоты (ФАПЧ), причем второй вход-выход контроллера локальной шины соединен с первыми входами-выходами второго адаптера «Локальная шина - синхронное динамическое ОЗУ», контроллера программируемого синтезатора частот, блока межмодульной синхронизации, набора функциональных блоков мезонина, загрузчика мезонина, временного таймера, с вторыми входами-выходами контроллера первого генератора сигналов произвольной формы и контроллера блока внешнего запуска, с третьими входами-выходами блока регистров и генератора прерываний по событиям, третий вход-выход контроллера локальной шины соединен с первыми входами-выходами контроллера прерываний, контроллера второго последовательного ПЗУ и первого адаптера «Локальная шина - синхронное динамическое ОЗУ», с вторыми входами-выходами регистратора событий, блока программной генерации сигнала синхронизации, с третьими входами-выходами блока цифровой обработки и трансляции сигналов, контроллера первого блока измерения напряжения, первый вход-выход блока регистров соединен с вторым входом-выходом временного таймера, второй вход-выход блока регистров соединен с вторым входом-выходом контроллера прерываний, первые входы-выходы генератора сигналов синхронизации по событиям, контроллер первого блока измерения напряжения и регистратора событий, вторые входы-выходы контроллера программируемого синтезатора частот и блока межмодульной синхронизации, третьи входы-выходы первого контроллера первого генератора сигналов произвольной формы и блока программной генерации сигнала синхронизации соединены друг с другом, первый вход контроллера первого генератора сигналов произвольной формы соединен с первым выходом блока цифровой обработки и трансляции сигналов, второй вход блока цифровой обработки и трансляции сигналов соединен с вторым выходом контроллера первого блока измерения напряжения, второй и третий входы генератора сигналов синхронизации по событиям соединены соответственно с первыми выходами блока программной генерации сигнала синхронизации и контроллера блока внешнего запуска, третий вход контроллера прерываний соединен с первым выходом блока задержки прерываний по переключению банков приемников, второй и третий входы которого соединены с четвертым и третьим выходами контроллера первого блока измерения напряжения и регистратора событий соответственно, причем мезонин содержит второй блок измерения напряжения, второй генератор сигналов произвольной формы, программируемую логическую интегральную схему DD1 (ПЛИС DD1), причем первый и второй входы-выходы ПЛИС DD1 являются вторыми входами-выходами второго блока измерения напряжения и второго генератора сигналов произвольной формы, третий вход-выход ПЛИС DD1 является третьим входом-выходом мезонина, четвертый вход ПЛИС DD1 является четвертым входом мезонина, первые вход и выход второго блока измерения напряжения и второго генератора сигналов произвольной формы являются первым и вторым входом и выходом мезонина.

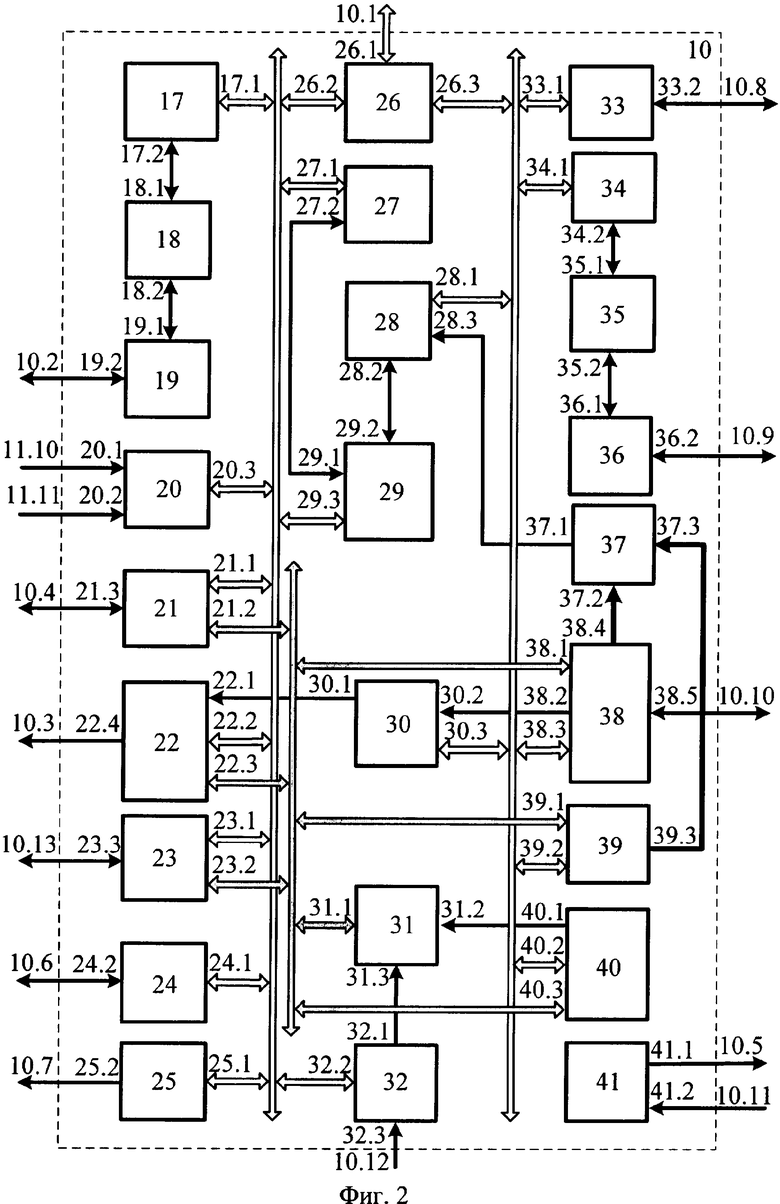

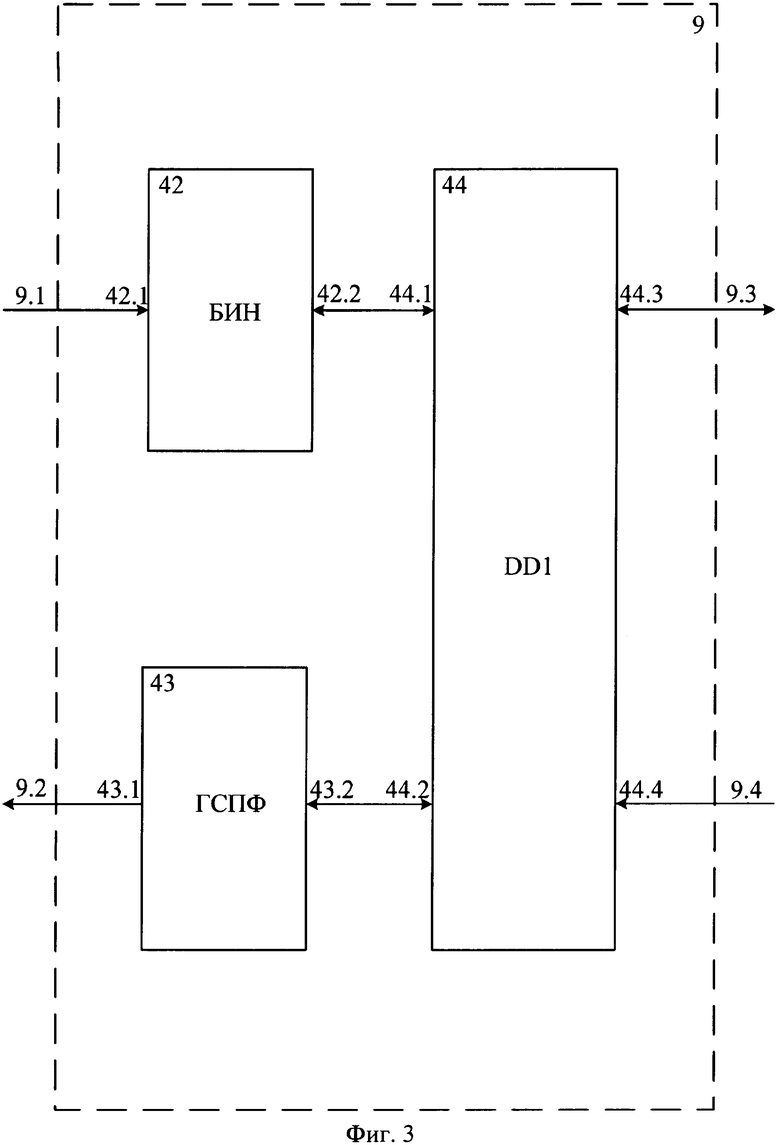

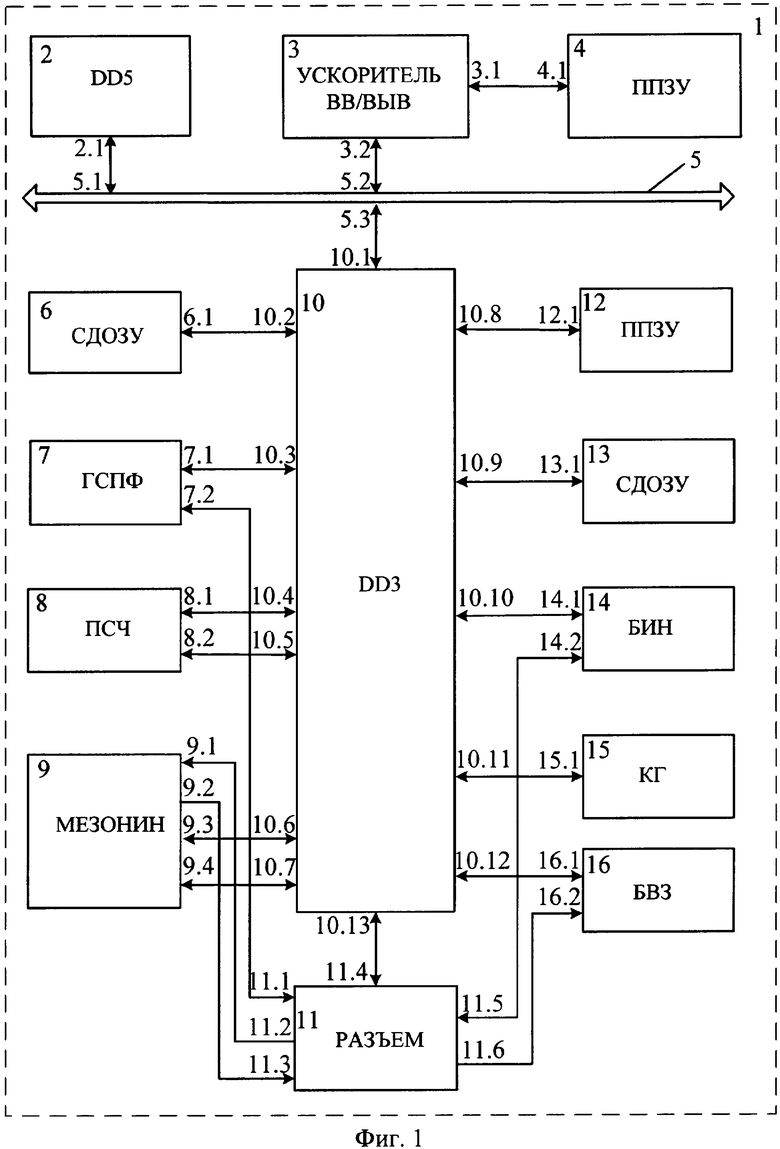

Изобретение поясняется чертежами, где на фиг.1 показана структурная схема МСД, на фиг.2 раскрыта ПЛИС DD3, на фиг.3 - мезонин.

Модуль сбора данных 1 (см. фиг.1) содержит ПЛИС DD5 2, ускоритель ввода/вывода 3, первое последовательное ПЗУ 4, локальную шину 5, второе синхронное динамическое ОЗУ 6, первый генератор сигналов произвольной формы 7, программируемый синтезатор частот 8, мезонин 9, ПЛИС DD3 10, разъем 11, второе последовательное ПЗУ 12, первое синхронное динамическое ОЗУ 13, первый блок измерения напряжения 14, кварцевый генератор 15, блок внешнего запуска 16. ПЛИС DD3 содержит второй адаптер «Локальная шина - синхронное динамическое ОЗУ» 17 (см. фиг.2), второй арбитр синхронного динамического ОЗУ 18, контроллер второго синхронного динамического ОЗУ 19, генератор прерываний по событиям 20, контроллер программируемого синтезатора частот 21, контроллер первого генератора сигналов произвольной формы 22, блок межмодульной синхронизации 23, набор функциональных блоков мезонина 24, загрузчик мезонина 25, контроллер локальной шины 26, временный таймер 27, контроллер прерываний 28, блок регистров 29, блок цифровой обработки и трансляции сигналов 30, генератор сигналов синхронизации по событиям 31, контроллер блока внешнего запуска 32, контроллер второго последовательного ПЗУ 33, первый адаптер «Локальная шина - синхронное динамическое ОЗУ» 34, второй арбитр синхронного динамического ОЗУ 35, контроллер второго синхронного динамического ОЗУ 36, блок задержки прерываний по переключению банков приемников 37, контроллер первого блока измерения напряжения 38, регистратор событий 39, блок программной генерации сигнала синхронизации 40, систему фазовой автоподстройки частоты 41. Мезонин 9 содержит второй блок измерения напряжения 42 (см. фиг.3), второй генератор сигналов произвольной формы 43, ПЛИС DD1 44, причем входы-выходы 2.1 ПЛИС DD5 2, 3.3 ускорителя ввода/вывода 3 и 10.1 ПЛИС DD3 10 соединены друг с другом с помощью входов-выходов 5.1-5.4 локальной шины 5, вход-выход 10.2 ПЛИС DD3 10 является входом-выходом 6.2 второго синхронного динамического ОЗУ 6, вход-выход 10.3 ПЛИС DD3 10 является входом-выходом 7.1 первого генератора сигналов произвольной формы 7, входы-выходы 10.4 и 10.5 ПЛИС DD3 10 являются входами-выходами 8.1 и 8.2 программируемого синтезатора частот 8, вход-выход 10.6 и 10.7 ПЛИС DD3 10 являются входами-выходами 9.3 и 9.4 мезонина 9, вход-выход 10.8 ПЛИС DD3 10 является входом-выходом 12.1 второго последовательного ПЗУ 12, вход-выход 10.9 ПЛИС DD3 10 является входом-выходом 13.1 первого синхронного динамического ОЗУ 13, вход-выход 10.10 ПЛИС DD3 10 является входом-выходом 14.1 первого блока измерения напряжения 14, вход-выход 10.11 ПЛИС DD3 10 является входом-выходом 15.1 кварцевого генератора 15, вход-выход 10.12 ПЛИС DD3 10 является входом-выходом 16.1 блока внешней записи 16, вход-выход 10.13 ПЛИС DD3 10 является входом-выходом 11.4 разъема 11, вход-выход 3.1 ускорителя ввода/вывода 3 является входом-выходом 4.1 первого последовательного ПЗУ 4, входы-выходы 11.1 и 11.5 разъема 11 являются входами-выходами 7.2 первого генератора сигналов произвольной формы 7 и 14.2 первого блока измерения напряжения 14 соответственно, вход-выход 16.2 блока внешнего запуска 16 соединен с входом-выходом 11.6 разъема 11, вход 9.1 и выход 9.2 мезонина 9 являются выходом 11.2 и входом 11.3 разъема 11 соответственно, 26.2 вход-выход контроллера локальной шины 26 (см. фиг.2) соединен с входами-выходами 17.1 второго адаптера «Локальная шина - синхронное динамическое ОЗУ» 17, 20.2 генератора прерываний по событиям 20, 21.1 контроллера программируемого синтезатора частот 21, 22.1 контроллера первого генератора сигналов произвольной формы 22, 23.1 блока межмодульной синхронизации 23, 24.1 набора функциональных блоков мезонина 24, 25.1 загрузчика мезонина 25, 27.1 временного таймера 27, 29.3 блока регистров 29, 32.2 контроллера блока внешнего запуска 32, 26.3 вход-выход контроллера локальной шины 26 соединен с входами-выходами 28.1 контроллера прерываний 28, 30.3 блока цифровой обработки и трансляции сигналов 30, 33.1 контроллера второго последовательного ПЗУ 33, 38.3 контроллера первого блока измерения напряжения 38, 39.2 регистратора событий 39, 40.2 блока программной генерации сигнала синхронизации 40, 29.1 и 29.2 входы-выходы блока регистров 29 являются входами-выходами 27.2 временного таймера 27 и 28.2 контроллера прерываний 28 соответственно, вход-выход 21.2 контроллера программируемого синтезатора частот 21 соединен с входами-выходами 22.3 контроллера первого генератора сигналов произвольной формы 22, 23.2 блока межмодульной синхронизации 23, 31.1 генератора сигналов синхронизации по событиям 31, 38.1 контроллера первого блока измерения напряжения 38, 39.1 регистратора событий 39 и 40.3 блока программной генерации сигнала синхронизации 40, 41.1 выход и 41.2 вход системы фазовой автоподстройки частоты 41 соединены с 8.2 входом программируемого синтезатора частоты 8 и 15.1 выходом кварцевого генератора 15 соответственно, 28.3 вход контроллера прерываний 28 является 37.1 выходом блока задержки прерываний по переключению банков приемников 37, 37.2 и 37.3 входы которого являются выходами 38.4 контроллера первого блока измерения напряжения 38 и 39.3 регистратора событий 39, 44.1 и 44.2 входы-выходы ПЛИС DD1 44 (см. фиг.3) являются 42.2 и 43.2 входами-выходами второго блока измерения напряжения 42 и второго генератора сигналов произвольной формы 43, 44.3 выход ПЛИС DD1 44 является входом 10.5 ПЛИС DD3 10, 42.1 вход второго блока измерения напряжения 42 и 43.1 выход второго генератора сигналов произвольной формы 43 присоединяются к входу-выходу 11.1 разъема 11.

ПЛИС DD5 2 выступает в качестве загрузчика ПЛИС DD3 10.

Ускоритель ввода/вывода 3 обеспечивает взаимодействие шины PCI и локальной шины 5 (на чертеже не показано).

Первое последовательное ПЗУ 4 хранит параметры ускорителя ввода/вывода, загружаемые при подаче на модуль сбора данных питания.

К локальной шине 5 подключены ускоритель ввода/вывода 3, загрузчик ПЛИС DD5 2 и ПЛИС DD3 10.

Второе и первое синхронные динамические ОЗУ 6 и 13 служат буферами для сбора и вывода данных.

Первый генератор сигналов произвольной формы 7, состоящий из шести независимых генераторов, предназначен для генерации сигналов произвольной формы. Он использует второе синхронное динамическое ОЗУ 6 в режиме разделения времени.

Программируемый синтезатор частоты 8, построенный по принципу прямого цифрового синтеза, предназначен для генерации сигналов синхронизации с частотой от 0 до 1 МГц с дискретностью 5 МГц. Программируемый синтезатор частоты 8 состоит из двух независимых синтезаторов и обеспечивает возможность независимой установки произвольной частоты дискретизации для аналого-цифрового и цифроаналогового преобразований.

Мезонин 9 является модулем расширения и выполнен на одной печатной плате. Мезонин 9 увеличивает число каналов измерения и формирования до 14 штук.

ПЛИС DD3 10 реализует большую часть функциональных возможностей модуля сбора данных и может динамически перепрограммироваться за счет применения загрузчика.

Разъем 11 служит для прохождения связи ПЛИС DD3 10 и ПЛИС DD1 44 мезонина.

Второе последовательное ПЗУ 12 служит для хранения калибровочной информации, которая используется для аппаратной коррекции характеристик преобразования. Аппаратная коррекция характеристик преобразования позволяет получить высокие точностные характеристики модуля сбора данных.

В первом блоке измерения напряжения 14 осуществляются аналого-цифровое преобразование, считывание кода напряжения, коррекция полученного кода напряжения и запись полученного кода в первое синхронное динамическое ОЗУ 13.

Кварцевый генератор 15 предназначен для генерации сигналов опорного сигнала для программируемого синтезатора частоты 8.

Блок внешнего запуска 16 предназначен для установки условий запуска по внешнему сигналу и генерации сигнала запуска при выполнении этих условий над сигналами на входе блока.

Устройство работает следующим образом.

Измерение напряжения входных сигналов производится следующим образом. Входные сигналы подаются на первый блок измерения напряжения 14 (см. фиг.1), который осуществляет аналого-цифровое преобразование, коррекцию данных в соответствии с калибровочной информацией и запись данных в первое синхронное динамическое ОЗУ 13. Первый блок измерения напряжения 14 по очереди работает с двумя банками памяти. Когда он работает с банком памяти «ноль», системное программное обеспечение (ПО) читает данные с банка памяти «единица». Когда первый блок измерения напряжения 14 работает с банком памяти «единица», системное ПО читает данные с банка памяти «ноль». При достижении конца банка памяти генерируется прерывание, сообщающее системному ПО о готовности очередного банка памяти.

Формирование выходных сигналов осуществляется следующим образом. ПО записывает отсчеты выходных сигналов для каждого разрешенного канала во втором синхронном динамическом ОЗУ 6. Первый генератор сигналов произвольной формы 7 для каждого разрешенного канала производит предвыборку отсчетов в буферы типа FIFO (First-In-First-Out). Затем эти отсчеты подаются на цифроаналоговый преобразователь через блоки коррекции характеристик преобразования (на чертеже не показано). Запись цифроаналоговых преобразований производится по положительному фронту сигнала синхронизации цифроаналогового преобразователя, расположенного в первом генераторе сигналов произвольной формы 7 (на чертеже не показано). При опустошении буфера FIFO производится подкачка отсчетов из второго синхронного динамического ОЗУ 6. Первый генератор сигналов произвольной формы 7 работает с двумя банками памяти для каждого разрешенного канала. При достижении конца активного банка памяти первый генератор сигналов произвольной формы 7 генерирует прерывание и начинает работать со следующим банком памяти. При этом системное ПО при получении прерывания может обновлять данные в неактивном банке.

Второй и первый адаптеры «Локальная шина - синхронное динамическое ОЗУ» 17 и 34 (см. фиг.2) обеспечивают подключение второго и первого синхронных динамических ОЗУ 6 и 13 к локальной шине 5.

Второй и первый арбитры синхронных динамических ОЗУ 18 и 35 обеспечивают арбитраж доступа к контроллерам синхронных динамических ОЗУ 19 и 36, которые реализованы в ПЛИС DD3 10.

Генератор прерывания по событиям 20 применяется для построения требуемых циклограмм работы. Он позволяет генерировать серии прерываний по событиям на шине синхронизации или на входе внешнего запуска.

Контроллер программируемого синтезатора частоты 21 и контроллер первого генератора сигналов произвольной формы 22 размещены в ПЛИС DD3 10.

Блок межмодульной синхронизации 23 предназначен для обеспечения синхронной работы функциональных блоков различных модулей, соединенных шиной синхронизации.

Набор функциональных блоков мезонина 24 выполняет функции, которые запрограммированы в ПЛИС DD1 44 мезонина 9.

Загрузчик мезонина 25 осуществляет загрузку ПЛИС DD1 44 мезонина 9.

Контроллер локальной шины 26 осуществляет управление локальной шиной 5 и реализован в ПЛИС DD3 10.

Временной таймер 27 работает как от внутреннего тактового сигнала с частотой 5 МГц, так и от сигналов с шины синхронизации. Разрядность его равна 40. Для чтения временного таймера 27 нужно сначала прочитать младшее слово таймера, при этом старшее слово сохранится в регистре, затем прочитать старшее слово.

Контроллер прерывания 28 служит для управления системой прерываний.

Блок регистров 29 предназначен для управления основными функциональными блоками модуля сбора данных 1.

Блок цифровой обработки и трансляции сигналов 30 обеспечивает динамическое масштабирование сигналов. Отсчеты сигналов с выхода блоков коррекции характеристик преобразования первого блока измерения напряжения 14 (на чертеже не показано) подаются на блок цифровой обработки и трансляции сигналов 30, который осуществляет масштабирование входных отсчетов в соответствии с коэффициентами, записанными в его буфера. Коэффициенты обновляет ПО.

Генератор сигналов синхронизации по событиям 31 предназначен для генерации сигнала запуска преобразования блоков измерения и формирования.

Контроллер блока внешнего запуска 32 и контроллер второго последовательного ПЗУ 33 реализованы в ПЛИС DD3 10.

Блок задержки прерываний по переключению банков приемников 37 предназначен для задержки прерываний, формируемых контроллером первого блока измерения напряжения 38 и регистратора событий 39. Дискретность установки времени задержки равна 1 мкс. Максимальное время задержки равно 65535 мкс. Задержка прерываний дает дополнительную гибкость в управлении загрузки шины PCI модуля сбора данных 1.

Регистратор событий 39 предназначен для регистрации событий, происходящих на входе внешней синхронизации и на линиях шины синхронизации, и внутренних событий модуля сбора данных 1. При обнаружении события записывается информация о нем и времени его возникновения. Регистратор событий 39 работает с двумя банками памяти, которые размещены в первом синхронном динамическом ОЗУ 13. Распределением памяти первого синхронного динамического ОЗУ 13 управляет ПО.

Блок программной генерации сигнала синхронизации 40 предназначен для формирования импульсов, подаваемых на блок выбора источника синхронизации (на чертеже не показан).

Система фазовой автоподстройки частоты 41 предназначена для получения сигнала с частотой 25 МГц из тактового сигнала с частотой 40 МГц.

На мезонине 9 (см. фиг.1) реализованы каналы второго блока измерения напряжения 42 и каналы второго генератора сигналов произвольной формы 43 (см. фиг.3).

ПЛИС DD1 44 является ядром мезонина и реализует большую часть функциональных возможностей модуля.

Интерфейс PCI управляет обменом данных между модулем сбора данных 1 и шиной PCI (на чертеже не показано). Платой можно управлять при помощи любого языка программирования, который имеет возможность работать с портами ввода/вывода компьютера.

Питание выходных усилителей аналоговых выходов модуля сбора данных может осуществляться либо источником питания персональной ЭВМ, в которую установлен модуль сбора данных 1, либо внешним блоком питания, что позволяет получить размах выходных сигналов до 60 В.

Таким образом, из рассмотренного материала видно, что заявляемое изобретение является новым, промышленно применимым и решает поставленную техническую задачу с заявленным техническим результатом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ ЛИНИЙ СВЯЗИ ПО МОДЕЛИ СИГНАЛА И ПЕРЕПРОГРАММИРУЕМЫМ ЭЛЕКТРИЧЕСКИМ СХЕМАМ | 2005 |

|

RU2317641C2 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| УДАЛЕННАЯ СИСТЕМА СБОРА И ОБРАБОТКИ ДАННЫХ ДЛЯ БОРТОВОЙ РЕГИСТРИРУЮЩЕЙ АППАРАТУРЫ | 2012 |

|

RU2493592C1 |

| УСТРОЙСТВО ПЕРВИЧНОЙ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2017 |

|

RU2653293C1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| СПОСОБ ЭЛЕКТРОННОЙ ОБРАБОТКИ СИГНАЛОВ ФОТОПРИЕМНИКА ПРИ ФОРМИРОВАНИИ ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2423016C1 |

| УСТРОЙСТВО ПРОГРАММНО-АППАРАТНОГО КОМПЛЕКСА ФОРМИРОВАНИЯ КЛЮЧЕВОЙ ИНФОРМАЦИИ И РАДИОДАННЫХ ДЛЯ РАДИОСТАНЦИИ | 2016 |

|

RU2634202C1 |

| КОМПЛЕКС ПРОГРАММНО-АППАРАТНЫХ СРЕДСТВ АВТОМАТИЗАЦИИ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2004 |

|

RU2279117C2 |

| Устройство для обработки изображений | 2020 |

|

RU2743773C1 |

| Плата-переходник для установки в базовые устройства с процессорным модулем форм-фактора COM EXPRESS | 2024 |

|

RU2838350C1 |

Модуль сбора данных относится к устройствам сбора данных и их регистрации и может быть применен в технологическом оборудовании комплексов полунатурного моделирования и автоматизированного контроля для ввода/вывода аналоговых сигналов в/из ЭВМ. Техническим результатом изобретения является расширение функциональных возможностей модуля за счет преобразования непрерывных электрических сигналов напряжения в цифровую форму, преобразования цифрового кода в непрерывные электрические сигналы напряжения, масштабирования непрерывных электрических сигналов напряжения, организации контуров управления, регистрации входных и выходных сигналов в привязке к единому времени, построения синхронных систем с единым временем, построения требуемых циклограмм работы. Для этого модуль сбора данных содержит программируемую логическую интегральную схему, взаимодействующую с ускорителем ввода/вывода посредством локальной шины, последовательное ПЗУ, синхронное динамическое ОЗУ, генератор сигналов произвольной формы, программируемый синтезатор частот, мезонин, программируемую логическую интегральную схему, разъем, последовательное ПЗУ, синхронное динамическое ОЗУ, блок измерения напряжения, кварцевый генератор, блок внешнего запуска. 2 з.п. ф-лы, 3 ил.

1. Модуль сбора данных, содержащий ускоритель ввода/вывода, первое последовательное постоянное запоминающее устройство (ПЗУ), программируемый синтезатор частоты, первый блок измерения напряжения, кварцевый генератор, временной таймер, причем ускоритель ввода/вывода соединен первым входом-выходом с входом-выходом первого последовательного ПЗУ, отличающийся тем, что в него дополнительно введены программируемые логические интегральные схемы (ПЛИС) DD3 и DD5, причем ПЛИС DD3 предназначена для преобразования непрерывных электрических сигналов напряжения в цифровую форму, для преобразования цифрового кода в непрерывные электрические сигналы напряжения, для масштабирования непрерывных электрических сигналов напряжения, для организации контуров управления, для регистрации входных и выходных сигналов в привязке к единому времени, для построения синхронных систем с единым временем и для построения требуемых циклограмм работы, ПЛИС DD5 предназначена для загрузки ПЛИС DD3, локальная шина, два синхронных динамических оперативных запоминающих устройства (ОЗУ), в первое из которых осуществляется запись данных с первого блока измерения напряжения, предназначенного для аналого-цифрового преобразования и коррекции данных в соответствии с калибровочной информацией, первый генератор сигналов произвольной формы, мезонин, предназначенный для увеличения числа каналов измерения и формирования модуля, разъем, второе последовательное ПЗУ, блок внешнего запуска, причем вход-выход ПЛИС DD5, второй вход-выход ускорителя ввода/вывода и первый вход-выход ПЛИС DD3 модуля сбора данных соединены между собой через входы-выходы локальной шины, второй вход-выход ПЛИС DD3 соединен с входом-выходом второго синхронного динамического ОЗУ, третий вход-выход ПЛИС DD3 - с первым входом-выходом первого генератора сигналов произвольной формы, четвертый и пятый входы-выходы ПЛИС DD3 - с входами-выходами программируемого синтезатора частот, шестой и седьмой входы-выходы ПЛИС DD3 - с третьим и четвертым входами-выходами мезонина, восьмой вход-выход ПЛИС DD3 - с входом-выходом второго последовательного ПЗУ, девятый вход-выход ПЛИС DD3 - с входом-выходом первого синхронного динамического ОЗУ, десятый вход-выход ПЛИС DD3 - с первым входом-выходом первого блока измерения напряжения, в первое синхронное динамическое ОЗУ, одиннадцатый вход-выход ПЛИС DD3 - с входом-выходом кварцевого генератора, двенадцатый вход-выход ПЛИС DD3 - с первым входом-выходом блока внешнего запуска, тринадцатый вход-выход ПЛИС DD3 - с четвертым входом-выходом разъема, первый и пятый входы-выходы разъема являются вторыми входами-выходами первого генератора сигналов произвольной формы и первого блока измерения напряжения соответственно, второй и шестой выходы разъема являются первым входом мезонина и вторым входом блока внешнего запуска соответственно, третий вход разъема является вторым выходом мезонина.

2. Модуль сбора данных по п.1, отличающийся тем, что ПЛИС DD3 содержит первый и второй адаптеры «Локальная шина - синхронное динамическое ОЗУ», два арбитра синхронных динамических ОЗУ, два контроллера синхронных динамических ОЗУ, генератор прерываний по событиям, контроллер программируемого синтезатора частот, контроллер первого генератора сигналов произвольной формы, блок межмодульной синхронизации, набор функциональных блоков мезонина, загрузчик мезонина, контроллер локальной шины, контроллер прерываний, блок регистров, блок цифровой обработки и трансляции сигналов, генератор сигналов синхронизации по событиям, контроллер блока внешнего запуска, контроллер второго последовательного ПЗУ, блок задержки прерываний по переключению банков приемников, контроллер первого блока измерения напряжения, регистратор событий, блок программной генерации сигнала синхронизации, систему фазовой автоподстройки частоты, причем второй вход-выход контроллера локальной шины соединен с первыми входами-выходами второго адаптера «Локальная шина - синхронное динамическое ОЗУ», контроллера программируемого синтезатора частот, блока межмодульной синхронизации, набора функциональных блоков мезонина, загрузчика мезонина и временного таймера, с вторыми входами контроллера первого генератора сигналов произвольной формы и контроллера блока внешнего запуска, с третьими входами-выходами блока регистров и генератора прерываний по событиям, третий вход-выход контроллера локальной шины соединен с первыми входами-выходами контроллера прерываний, контроллера второго последовательного ПЗУ, первого адаптера «Локальная шина - синхронное динамическое ОЗУ», с вторыми входами-выходами регистратора событий и блока программной генерации сигнала синхронизации, с третьими входами-выходами блока цифровой обработки и трансляции сигналов и контроллера первого блока измерения напряжения, первый вход-выход блока регистров соединен с вторым входом-выходом временного таймера, второй вход-выход блока регистров соединен с вторым входом-выходом контроллера прерываний, первые входы-выходы генератора сигналов синхронизации по событиям, контроллера первого блока измерения напряжения и регистратора событий, вторые входы-выходы контроллера программируемого синтезатора частот, блока межмодульной синхронизации, третьи входы-выходы контроллера первого генератора сигналов произвольной формы, блока программируемой генерации сигнала синхронизации соединены друг с другом, первый вход контроллера первого генератора сигналов произвольной формы соединен с первым выходом блока цифровой обработки и трансляции сигналов, второй вход блока цифровой обработки и трансляции сигналов соединен с вторым выходом контроллера первого блока измерения напряжения, второй и третий входы генератора сигналов синхронизации по событиям соединены соответственно с первыми выходами блока программной генерации сигнала синхронизации и контроллера блока внешнего запуска, третий вход контроллера прерываний соединен с первым выходом блока задержки прерываний по переключению банков приемников, второй и третий входы блока задержки прерываний по переключению банков приемников соединены с четвертым и третьим выходами контроллера первого блока измерения напряжения и регистратора событий соответственно.

3. Модуль сбора данных по п.1, отличающийся тем, что мезонин содержит второй блок измерения напряжения, второй генератор сигналов произвольной формы, ПЛИС DD1, являющуюся ядром мезонина и предназначенную для преобразования непрерывных электрических сигналов напряжения в цифровую форму и цифрового кода в непрерывные электрические сигналы напряжения, причем первый и второй входы-выходы ПЛИС DD1 являются вторыми входами-выходами второго блока измерения напряжения и второго генератора сигналов произвольной формы соответственно, третий вход-выход ПЛИС DD1 является третьим входом-выходом мезонина, четвертый вход ПЛИС DD1 является четвертым входом мезонина, первые вход второго блока измерения напряжения и выход второго генератора сигналов произвольной формы являются первым входом и вторым выходом мезонина соответственно.

| УСТРОЙСТВО СБОРА ДАННЫХ | 2002 |

|

RU2218596C2 |

| УСТРОЙСТВО ДЛЯ СБОРА, ОБРАБОТКИ И ПАКЕТНОЙ ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079881C1 |

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| JP 7177249 A, 14.07.1995. | |||

Авторы

Даты

2009-11-27—Публикация

2008-03-28—Подача