О5 00

со

Јь

СО 00

Изобретение относится к вычисли-1, тельной технике и технике связи и может быть использовано в аппаратуре передачи данных.

Цель изобретения - повышение быстродействия устройства.

На Фиг.1 изображена блок-схема устройства; на фиг.2-4 - блок счета стираний, генератор испытательных сигналов и вычислитель синдромов, соответственно..

Устройство для исправления стираний содержит буферный регистр I, блок 2 счета стираний, генератор 3 испытательных сигналов, распределитель 4 импульсов, вычислитель 5 синдромов, блок 6 замещения символов, блок 7 коррекции синдрома и блок 8 сравнения кобинаций. На фиг. 1 обо- значены информационный вход 9, вход 10 стираний, тактовый вход 11 и выход 12 устройства.

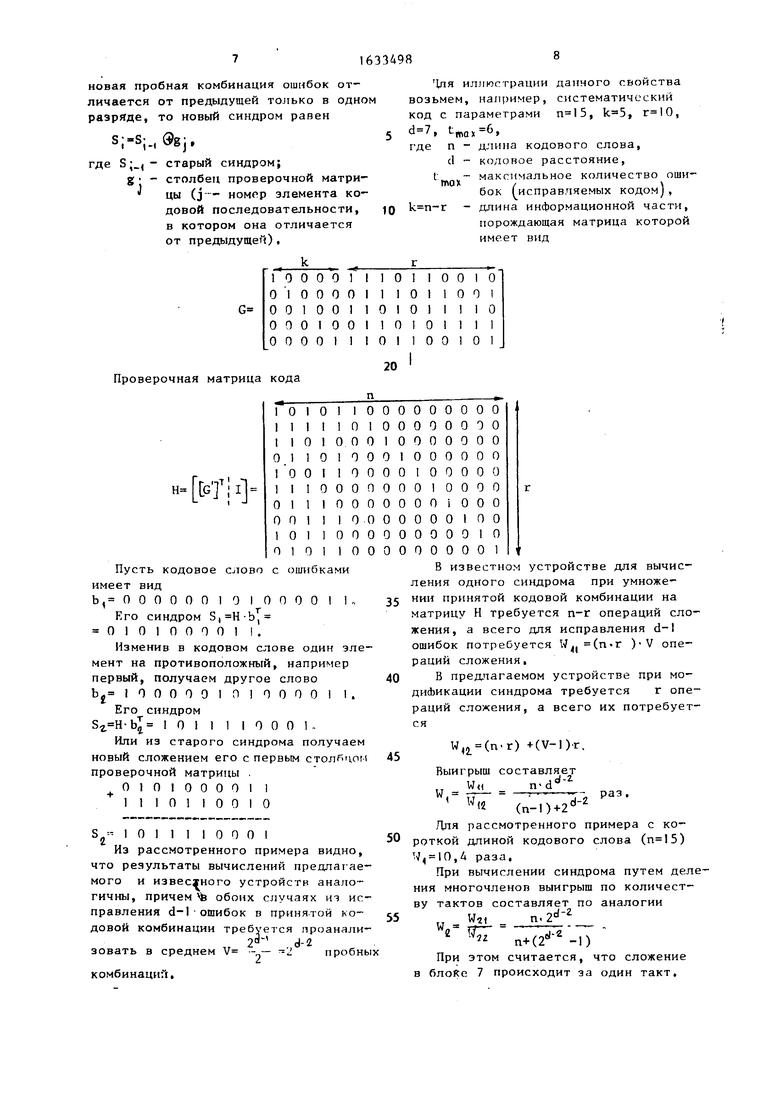

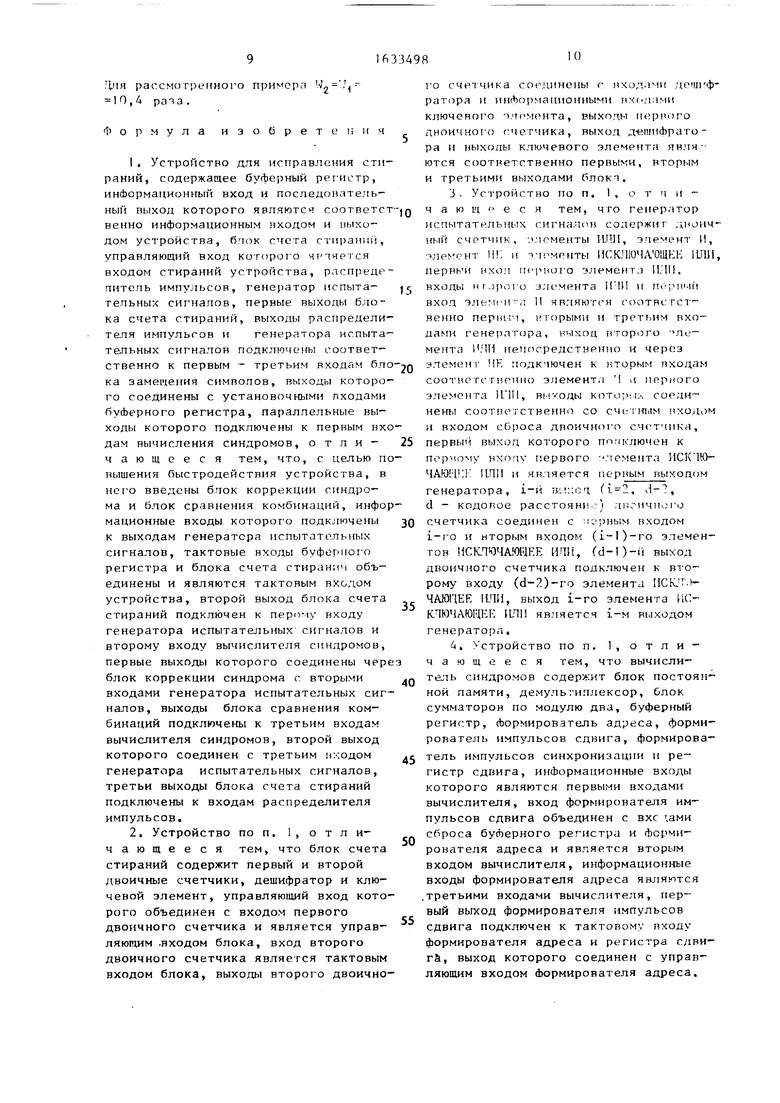

Бпок 2 счета стираний выполнен (Лиг.2) на первом 13 и втором 14 двоичных счетчиках, дешифраторе 15 и ключевом элементе 16, На фиг,2 обозначены управляющий вход 17, так- |товый вход 18, первые 19 и второй 20 и третьи 21 выходы блока 2.

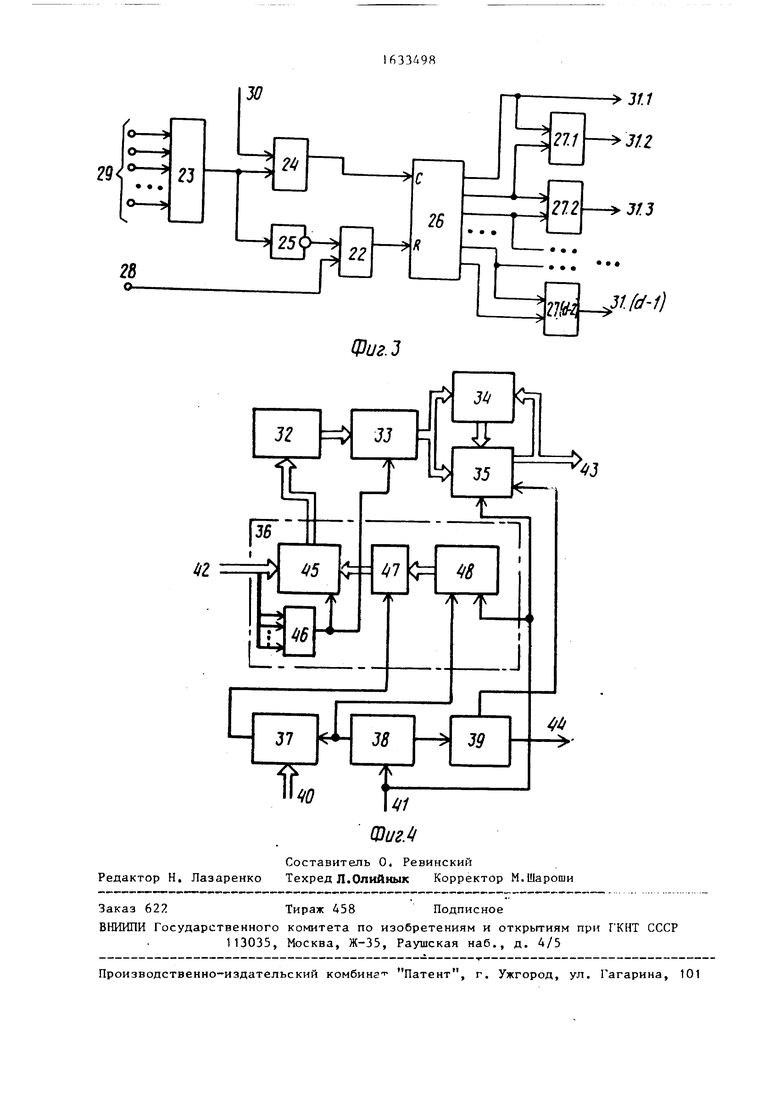

Генератор 3 испытательных сигналов включает в себя Фиг.З) первый 2 и второй 23 элементы ИЛИ, элемент И 24, элемент НЕ 25, двоичный счетчик 26 и элементы ИСК.ТОЧАЩЕЕ ИЛИ 27. На биг.З обозначены первый 28, вторые 29 и третий 30 входы и выходы 31 генератора 3. Генератор 3 представляет собой генератор кода Грея, где каждая следующая выходная комбинация отличается от предыдущей ровно в одном элементе. На фиг.З обозначено кодовое расстояние d используемого (принимаемого) кода.

Распределитель 4 импульсов пред- ставляет собой Фактически демульти- плексор, устанавливающий уровень логической единицы на выходе в соответствии с входным кодом.

I

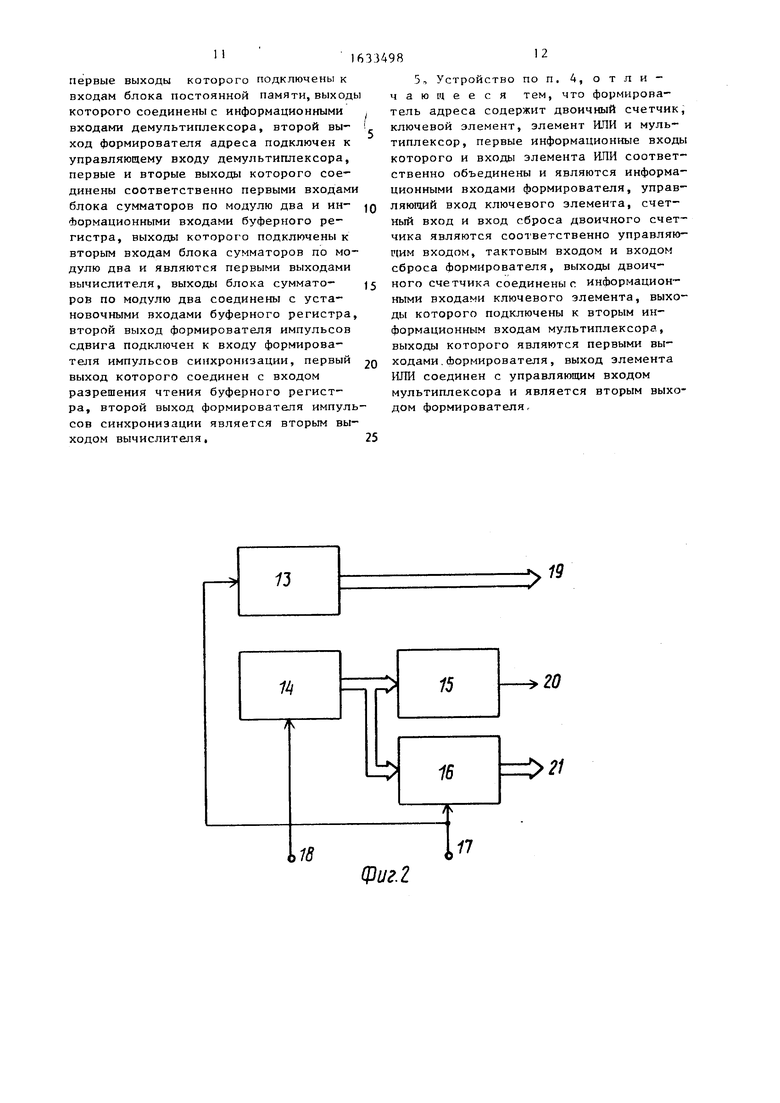

Вычислитель 5 синдромов содержит

(гоиг.4) блок 32 постоянной памяти, д мультиплексор ЗЗ, блок 34 сумматоров по модулю Хва, буферный регистр 35, Формирователь 36 адреса,, регистр 37 сдвига, Формирователь 38 импульсо сдвига и формирователь 39 импульсов синхронизации. На Фиг.4 обозначены первый 40, второй 41 и третьи 42

,

Q

5 0

5

Q

з

0

5

входы, первые 43 и второй 44 выходы вычислителя 5,

Блок 6 замещения символов выполнен так же, как комбинационная логическая схема известного устройства.

Блок 7 коррекции синдрома предназначен для заполнения синдрома и суммирования его с вектором-столбцом проверочной матрицы, реализуется в соответствии с выбранным кодом на регистрах и сумматорах по модулю два.

Блок 8 сравнения комбинаций служит для выделения отличающихся разрядов в двух следующих друг за другом испытательных сигналах, реализуется на регистрах и сумматорах по модулю два.

Формирователь 36 адреса выполнен (фиг.4) на мультиплексоре 45, элементе ИЛИ 46, ключевом элементе 47 и двоичном счетчике 48,

Сущность изобретения заключается в отказе от громоздкого вычисления синдрома для каждой, кроме первой, комбинации ошибок, заключающегося в делении многочлена принятого кодового слова на проверочный полином или в умножении его на проверочную матрицу, Вместо этой процедуры в блоке 7 коррекции синдрома используется операция сложения по модулю два ранее вычисленного синдрома с требуемым столбцом проверочной матрицы, местоположение которого определяется блоком 8 сравнения комбинаций (предыдущей и последующей ) генератора 3 испытательных сигналов.

Устройство работает следующим образом.

Кодовая комбинация поступает в регистр 1 и вычислитель 5 синдромов. Работа буферного регистра 1 и блока 2 счета стираний синхронизируется импульсами с тактового входа 11 устройства. В исходном состоянии блок 2 обнулен. Одновременно с выдачей очередного символа кодовой комбинации на блок 2 поступает с входа 10 стираний устройства сигнал стирания /вектор стираний), содержащий единицу, если в отношении этого символа в демодуляторе (не показан) ие принято определенного решения. С блока 2 в блок 6 поступает сигнал, соответствующий номеру (по порядку поступления) соответствующего стирания, а на распределитель 4 - номер разряда, в котором произошло стирание. По этому сигналу и соответствующему сигналу с распределителя 4 в блоке 6 записывается номер стертого разряда кодовой комбинации. Кроме того, блок 6 подключает к входам разрядов регистра 1, соответствующим стертым символам, выходы разрядов генератора 3, Причем к одному разряду регистра 1 подключается выход одного разряда генератора 3. После записи в регистр 1 всей принятой кодовой комбинации начинает работать генератор 3, который запускается по входу 28 сигналом Пуск, формируемым на втором выходе 20 блока 2, этим же сигналом запускается Формирователь 38 импульсов сдвига, входящий в состав вычислителя 5 синдромов (Ьнг . -() .Таким образом, вместо стертых символов в регистр 1 записываются испытательные комбинации.

Первая испытттепьная комбинация имеет вид 00...0. Она поступает с генератора 3 в блок 8 сравнения комбинаций, регистр которого перед началом работы был обнулен, а также записывается в нужные разряды регистра 1. По (d-)-разрядному сигналу сравнения вида 00...О с выходов блока 8 вычислитель 5 вычисляет г-раз- рядный синдром записанной в регистре 1 комбинации. Полученный первый синдром поступает в блок 7 кор, екции синдрома, где запоминается, а затем без изменений проходит па г-входы 2 генератора 3. Если синдром окажется нулевым, то генератор 3 останавливается и вырабатывается сигнал об окончании декодирования, Если синдром не равен нулю во всех разрядах, то на выходе генератора 3 появляется новая испытательная комбинация, отличающаяся от предыдущей ровно в одном элементе генератор 3 генерирует последвательность кода Грек). Новая испытательная комбинация Формируется генератором 3 по приходу на вход 30 им- пусьса синхронизации из вычислителя 5 синдромов и поступает в блок 6

синдромом, Вновь полученный синдром запоминается в блоке 7, а затем поступает в генератор 3. При этом вычислитель 5 больше для данной принятой комбинации синдром не вычисляет,

Синдром вычисляется путем перемножения принятого вектора (транспони-

v

poBanHoroj на проверочную матрицу

для первой (нулевой) пробной комбинации, Проверочная матрица кода записана в блоке 32 постоянной памяти. По сигналу запуска с входа 41, которым одновременна обнуляются счетчик 48

г Формирователя 36 адреса и регистр 35, запускается формирователь 38 импульсов сдвига, управляющий регистром 37 сдвига, в котором записана кодовая комбинация. Формирователь 36 адреса,

0 таь тируемый гЪгфмироиач елем 38 импульсов сдвига, выбирав из блока 32 требуемый столГ ц (сигнал нулевого разряда кодовой комбинации регистра 37 сдвига разрешает поступление

5 кода адреса столбца проверочной матрицы из счетчика 4 Я через мультиплексор 45 в блок 32), который поразрядно суммируется по модулю два в блоке 34 с содержимым регистра ЗЬ, результат остается в регио 35. По сигналу Чтение резупьтп, умножения вектора чз матрицу выдается по выходам 43 на блок 7 коррекции синдрома. Для последующих пробных комбинаций из блока 32 извлекается с помощью формирователя 36 адреса требуемый стобец без вычисления очередного синдрома (ненулевой код от блока 8 с помощью элемента ПЛИ 4Ь переключает мульти плексор 45 и поступает в блок 32 как адрес столбца, а затем вектор-столбец поступает через демультиплексор 33 сразу в регистр 35. Формирователь 39 импульсов синхронизации выдает на

с выход 44 счетные импульсы для генератора 3 испытательных сигналов, при этом учитывается задержка для вычисления первого синдрома. Счетные импульсы генерируются на основе сиг0

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для исправления ошибок | 1987 |

|

SU1501283A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для исправления стираний | 1989 |

|

SU1647916A2 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Устройство для исправления искажений в системах передачи дискретной информации | 1987 |

|

SU1603532A1 |

| Устройство для исправления стираний | 1978 |

|

SU786030A1 |

| Кодер несистематического сверточного кода | 1990 |

|

SU1695516A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в ппаратурр передачи данных позволяет повысить быстродействие. Устройство содержит буферный иегистр 1, блок 2 счета стираний, генератор 3 испытательных сигналов, распределитель 4 импульсов, вычислитель 5 синдромпя и блок 6 замещения символов, Благод1,эя введению блока 7 коррекции синдрома и блока 8 сравнения комбинаты в устройстве вместо вычисления синдрома для каждой (кроме первой)комбинации ошибок осуществляется сложение по модулю два ранее вычисленного синдрома с требуемым столбцом проверочной матрицы. 4 з.п. 4-лы, 4 ил Ј

замещения символов и блок 8 сравнения, 50 нала ормирователя 38 импульсов сдвигл, сигнал разрешения на работу которого выдает блок 2 счета стираний на своем втором выходе 20 по окончании поступления входной кодовой комбинации.

В известном устройстве вычислитель 5 осуществляет рычисление синдрома для каждой комбинации ошибок, а в предлага емом устройстве если каждая

в котором сравнивается с записанной там предыдущей комбинацией. Номер разряда с единицей, соответствующей различающимся элементам двух соседних комбинаций, однозначно связан с номером столбца проверочной матрицы, хранящейся в вычислителе 5. Найденный столбец поступает в блок 7 коррекции, где складывается с предыдущим

55

J

новая пробная комбинация ошибок отличается от предыдущей только в одно разряде, то новый синдром равен

s;-s;,06j.

где S;H- старый синдром;

g - столбец проверочной матрицы (j- номор элемента кодовой последовательности, в котором она отличается от предыдущей),

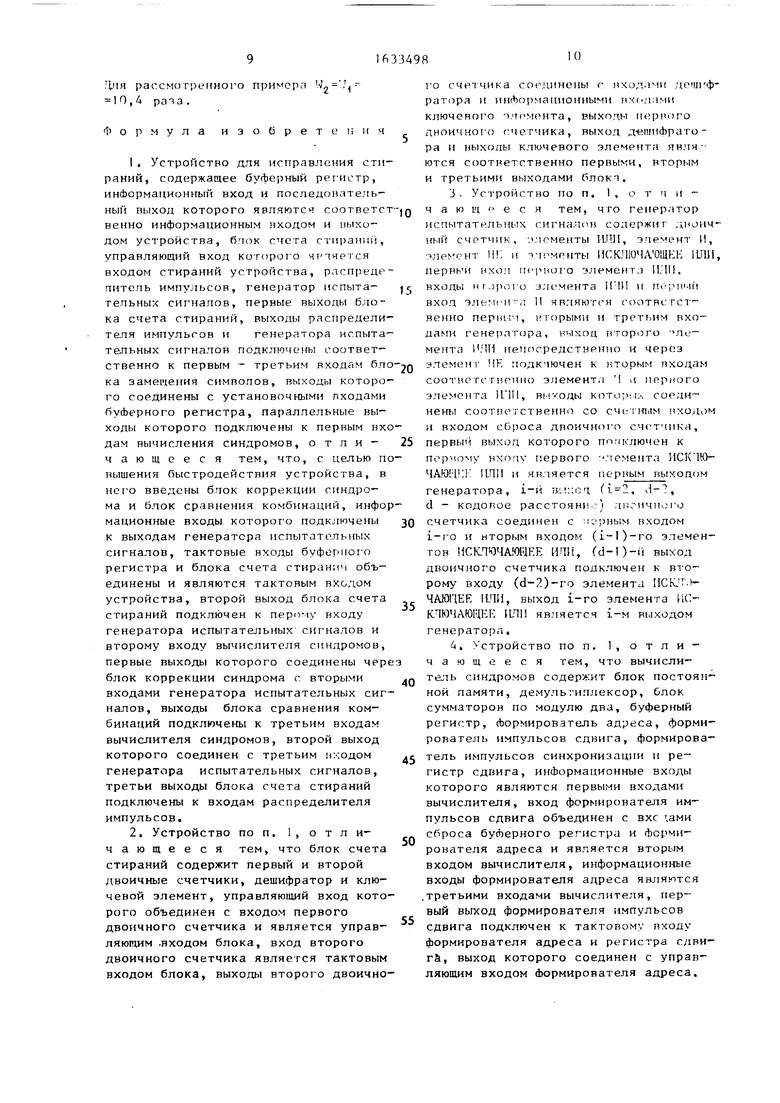

Проверочная матрица кода

-t&Tii 1 О

I 1 I 1

О 1

1

1 I О

1 0 1

0п о

1О О 001 100

о

1

о

11000

01

оо

1О

О1

000 1 О О 000 1 О О

Пусть кодовое слово с ошибками имеет вид

Ь, 000000101000011. jЕго синдром ,31 01010000 I.

Изменив в кодовом слове один элемент на противоположный, например первый, получаем другое слово Ъе 10000010100001 I.

Его синдром 101 1 1 10001.

Или из старого синдрома получаем новый сложением его с первым столоном проверочной матрицы . 010100001 I 1 1 1 0 1 1 О О I О

V

011110001 Из рассмотренного примера видно, что результаты вычислений предлагаемого и известного устройств аналогичны, причем й обоих случаях из исправления d-1ошибок в принятой кодовой комбинации требуется проанали2 d-2 зовать в среднем V -„- 2 пробны

комбинаций.

Чля иллюстрации данного свойства возьмем, например, систематический код с параметрами , , ,

где п - длина кодового слова,

Л кодовое расстояние, I максимальное количество оши( /«

бок исправляемых кодом, - длина информационной части, порождающая матрица которой имеет вид

0000000

0000000

0000000

1000000

0100000

0010000

0 0 0 i О О О

0000100

0000010

0000001

В известном устройстве для вычисления одного синдрома при умножении принятой кодовой комбинации на матрицу Н требуется n-г операций сложения, а всего для исправления d-1 ошибок потребуется W(||(n«r )-V операций сложения,

В предлагаемом устройстве при мо- дисЬикации синдрома требуется г операций сложения, а всего их потребуется

W,t (n-r) +(V-l)-r.

Выигрыш составляет n-dd Z

Для рассмотренного примера с ко- роткой длиной кодового слова () ,A раза,

При вычислении синдрома путем деления многочленов выигрыш по количеству тактов составляет по аналогии W,, п,

чи

)

При этом считается, что сложение в блоке 7 происходит за один такт.

Тля рассмотренного примера 10,4 рата .

Формула изобретении

д 5 0 « ,

5

0

го счетчика соединены с входами дешифратора и информационными входами ключевого ттомента, выходы первого дноичного счетчика, выход дешифратора и выходы ключевого элемента являются соответственно первыми, вторым и третьими выходами блокч.

первые выходы которого подключены к входам блока постоянной памяти,выходы которого соединены с информационными входами демультиплексора, второй выход формирователя адреса подключен к управляющему входу демультиплексора, первые и вторые выходы которого соединены соответственно первыми входами блока сумматоров по модулю два и информационными входами буферного регистра, выходы которого подключены к вторым входам блока сумматоров по модулю два и являются первыми выходами вычислителя, выходы блока сумматоров по модулю два соединены с установочными входами буферного регистра, второй выход формирователя импульсов сдвига подключен к входу формирователя импульсов синхронизации, первый выход которого соединен с входом разрешения чтения буферного регистра, второй выход формирователя импульсов синхронизации является вторым выходом вычислителя,

и

К

1В

0

5

5

0

5, Устройство по п. 4, отличающееся тем, что формирователь адреса содержит двоичный счетчик, ключевой элемент, элемент ИЛИ и мультиплексор, первые информационные входы которого и входы элемента ИЛИ соответственно объединены и являются информационными входами формирователя, управляющий вход ключевого элемента, счетный вход и вход сброса двоичного счетчика являются соответственно управляющим входом, тактовым входом и входом сброса формирователя, выходы двоичного счетчика соединены с информационными входами ключевого элемента, выходы которого подключены к вторым информационным входам мультиплексора, выходы которого являются первыми выходами .Формирователя, выход элемента ИЛИ соединен с управляющим входом мультиплексора и является вторым выходом формирователя,

19

15

1Ъ

16

л

17

Фиг. 2

32

$

L

V.fcf-f)

Фиг.З

f Д|

4J

| Берлекэмп Э | |||

| Алгебраическая теория кодирования | |||

| - N.: Мир, 1471, с | |||

| Заслонка для русской печи | 1919 |

|

SU145A1 |

| Блейхут Р, Теория и практика кодов, контролирующих ошибки | |||

| - fl | |||

| : Мир, 1986, с | |||

| Устройство для отыскания металлических предметов | 1920 |

|

SU165A1 |

| Устройство для исправления стираний | 1978 |

|

SU786030A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-13—Подача