Изобретение относится к технике связи и вычислительной технике и может быть использовано в системах передачи дискретной информации.

Известен помехоустойчивый кодек для передачи дискретных сообщений, содержащий кодер и декодер, кодер содержит первый и второй блоки постоянной памяти, первый и второй регистры сдвига, формирователь проверочных символов, делитель частоты, триггер, формирователь импульсов, первый и второй счетчики импульсов, элемент И. источник постоянного кода, компаратор, декодер содержит блок коррекции ошибок, первый и второй регистры сдвига, первый и второй блоки постоянной памяти, первый-третий элементы И, первый-третий счетчики импульсов, генератор импульсов, первый и второй триггеры, компаратор, дешифратор и элемент ИЛИ.

Недостатком этого устройства является снижение помехоустойчивости при возникновении ошибок, кратность которых больше корректирующей способности используемого помехоустойчивого кода с исправлением ошибок.

Целью изобретения является повышение помехоустойчивости.

Цель достигается тем, что в декодер помехоустойчивого кодека для передачи диск-. ретных сообщений введены четвертый элемент И, третий триггер и инвертор, вход которого подключен, к выходу компаратора и выход которого соединен со вторым входом четвертого элемента И, первый вход которого подключен к выходу первого счетчика импульсов, а выход соединен со вю- рым установочным входом третьего триггера, первый вход которого подключен к выходу второго счетчика импульсов, при этом решающим выходом декодера является выход третьего триггера.

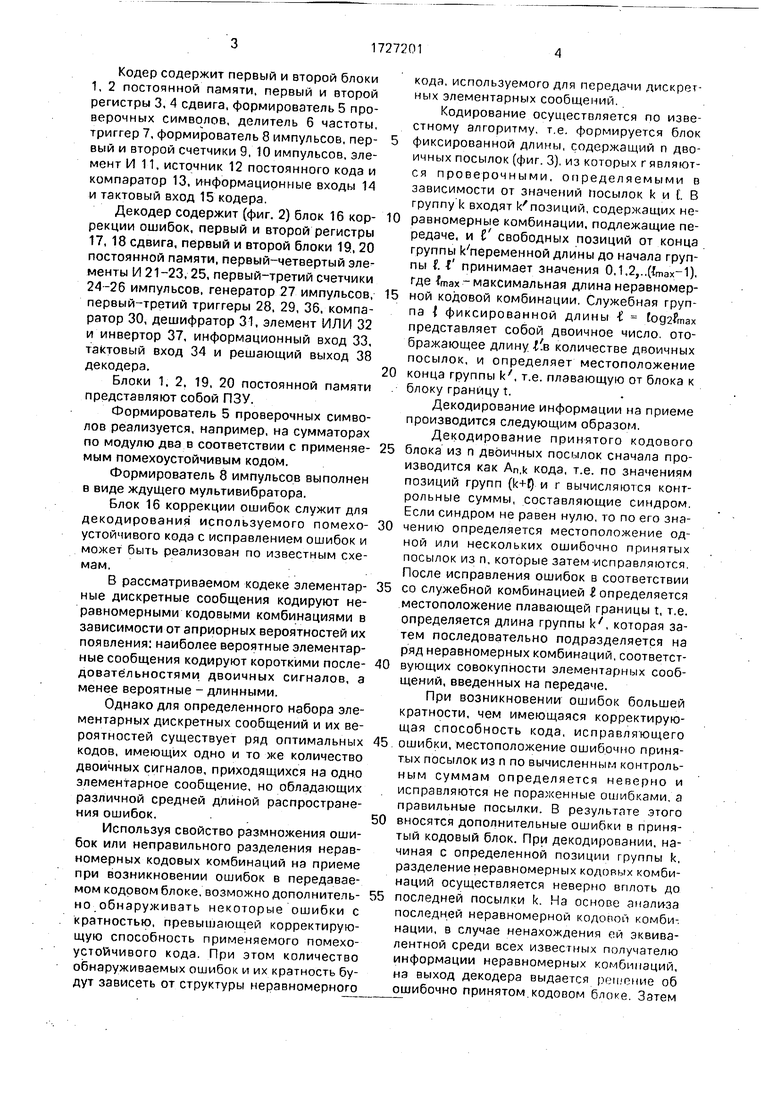

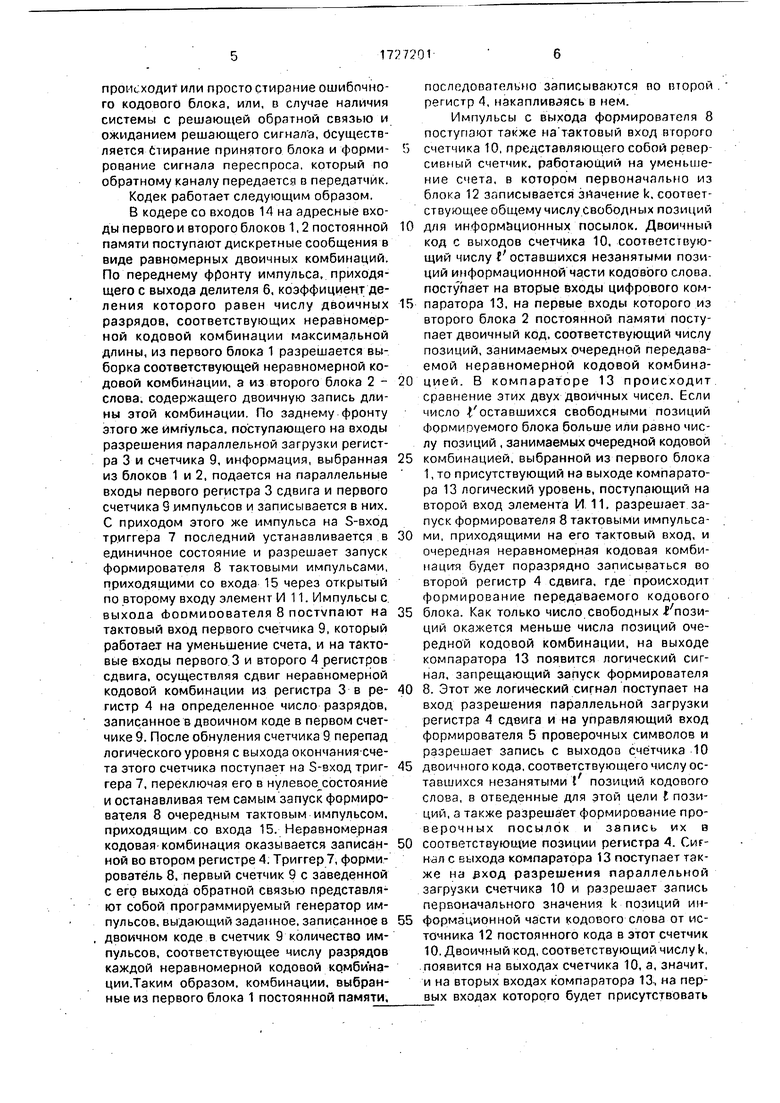

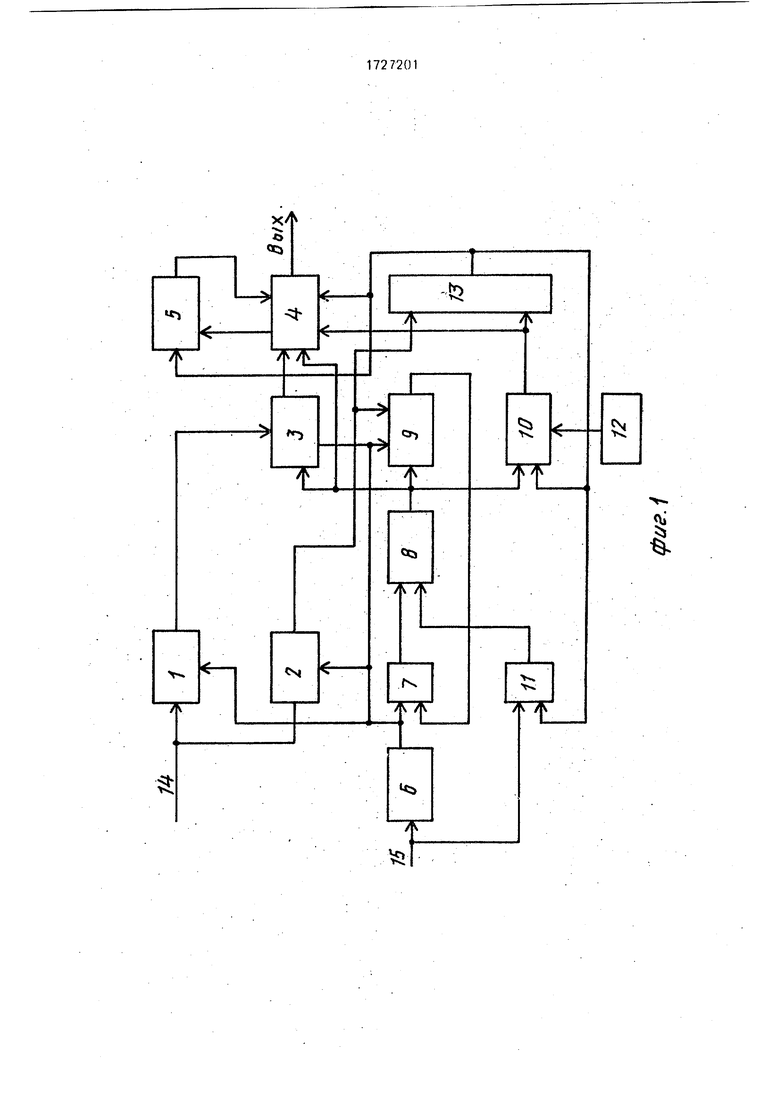

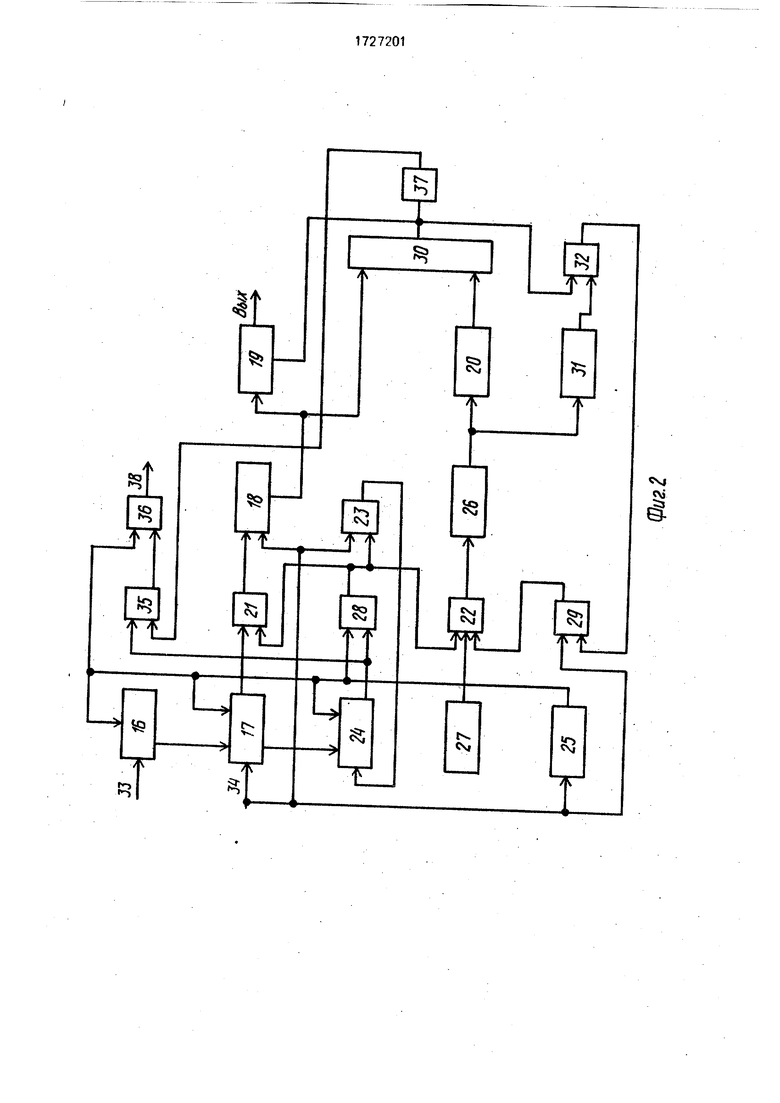

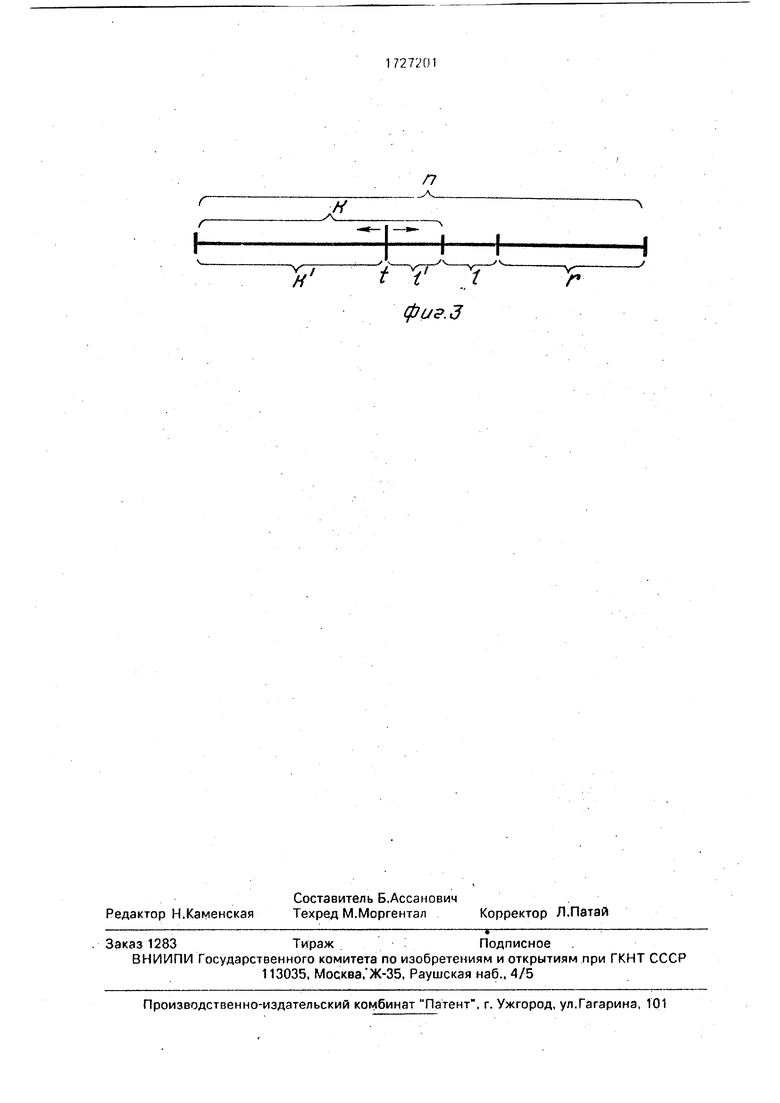

На фиг. 1 и 2 изображены блок-схемы соответственно кодера и предлагаемого декодера, входящих в помехоустойчивый кодек: на фиг. 3 иллюстрирует принцип построения кодового слова.

сл С

XJ

ю xi

ю

о

s

кэ

Кодер содержит первый и второй блоки 1, 2 постоянной памяти, первый и второй регистры 3, 4 сдвига, формирователь 5 проверочных символов, делитель б частоты, триггер 7, формирователь 8 импульсов, первый и второй счетчики 9, 10 импульсов, элемент И 11, источник 12 постоянного кода и компаратор 13, информационные входы 14 и тактовый вход 15 кодера.

Декодер содержит (фиг. 2) блок 16 коррекции ошибок, первый и второй регистры 17, 18 сдвига, первый и второй блоки 19, 20 постоянной памяти, первый-четвертый элементы И 21-23,25, первый-третий счетчики 24-26 импульсов, генератор 27 импульсов, первый-третий триггеры 28, 29, 36, компаратор 30, дешифратор 31, элемент ИЛИ 32 и инвертор 37, информационный вход 33, тактовый вход 34 и решающий выход 38 декодера.

Блоки 1, 2, 19, 20 постоянной памяти представляют собой ПЗУ.

Формирователь 5 проверочных символов реализуется, например, на сумматорах по модулю два в соответствии с применяемым помехоустойчивым кодом.

Формирователь 8 импульсов выполнен в виде ждущего мультивибратора.

Блок 16 коррекции ошибок служит для декодирования используемого помехоустойчивого кода с исправлением ошибок и может быть реализован по известным схемам.

В рассматриваемом кодеке элементарные дискретные сообщения кодируют неравномерными кодовыми комбинациями в зависимости от априорных вероятностей их появления: наиболее вероятные элементарные сообщения кодируют короткими последовательностями двоичных сигналов, а менее вероятные - длинными.

Однако для определенного набора элементарных дискретных сообщений и их вероятностей существует ряд оптимальных кодов, имеющих одно и то же количество двоичных сигналов, приходящихся на одно элементарное сообщение, но обладающих различной средней длиной распространения ошибок.

Используя свойство размножения ошибок или неправильного разделения неравномерных кодовых комбинаций на приеме при возникновении ошибок в передаваемом кодовом блоке, возможно дополнительно обнаруживать некоторые ошибки с кратностью, превышающей корректирующую способность применяемого помехоустойчивого кода. При этом количество обнаруживаемых ошибок и их кратность будут зависеть от структуры неравномерного

кода, используемого для передачи дискретных элементарных сообщений.

Кодирование осуществляется по известному алгоритму, т.е. формируется блок

фиксированной длины, содержащий п двоичных посылок (фиг. 3), из которых г являются проверочными, определяемыми в зависимости от значений посылок k и С. В группу k входят k позиций, содержащих не0 равномерные комбинации, подлежащие передаче, и I свободных позиций от конца группы переменной длины до начала группы t I принимает значения 0.1.2,..(Jmax-1). где Imax-максимальная длина неравномер5 ной кодовой комбинации. Служебная группа I фиксированной длины Ј tog2ftnax представляет собой двоичное число, отображающее длину I B количестве двоичных посылок, и определяет местоположение

0 конца группы kx, т.е. плавающую от блока к . блоку границу t.

Декодирование информации на приеме производится следующим образом.

Декодирование принятого кодового

5 блока из п двоичных посылок сначала производится как An,k кода, т.е. по значениям позиций групп (k+f) и г вычисляются контрольные суммы, составляющие синдром. Если синдром не равен нулю, то по его зна0 чению определяется местоположение одной или нескольких ошибочно принятых посылок из п, которые затем-исправляются. После исправления ошибок в соответствии

5 со служебной комбинацией I определяется местоположение плавающей границы t, т.е. определяется длина группы k , которая затем последовательно подразделяется на ряд неравномерных комбинаций, соответст0 вующих совокупности элементарных сообщений, введенных на передаче.

При возникновении ошибок большей кратности, чем имеющаяся корректирующая способность кода, исправляющего

5. ошибки, местоположение ошибочно принятых посылок из п по вычисленным контрольным суммам определяется неверно и исправляются не пораженные ошибками, а правильные посылки. В результате этого

0 вносятся дополнительные ошибки в принятый кодовый блок. При декодировании, начиная с определенной позиции группы k, разделение неравномерных кодовых комбинаций осуществляется неверно вплоть до

5 последней посылки k. На основе анализа последней неравномерной кодовой комбинации, в случае ненахождения ей эквивалентной среди всех известных получателю информации неравномерных комбинаций, на выход декодера выдается решение об ошибочно принятом.кодовом блоке. Затем

происходит или просто стирание ошибочного кодового блока, или, в случае наличия системы с решающей обратной связью и ожиданием решающего сигнал а, осуществляется стирание принятого блока и формирование сигнала переспроса, который по обратному каналу передается в передатчик.

Кодек работает следующим образом.

В кодере со входов 14 на адресные входы первого и второго блоков 1,2 постоянной памяти поступают дискретные сообщения в виде равномерных двоичных комбинаций. По переднему фронту импульса, приходящего с выхода делителя 6, коэффициент деления которого равен числу двоичных разрядов, соответствующих неравномерной кодовой комбинации максимальной длины, из первого блока 1 разрешается выборка соответствующей неравномерной кодовой комбинации, а из второго блока 2 - слова, содержащего двоичную запись длины этой комбинации. По заднему фронту этого же импульса, поступающего на входы разрешения параллельной загрузки регистра 3 и счетчика 9, информация, выбранная из блоков 1 и 2. подается на параллельные входы первого регистра 3 сдвига и первого счетчика 9.импульсов и записывается в них. С приходом этого же импульса на S-вход триггера 7 последний устанавливается в единичное состояние и разрешает запуск формирователя 8 тактовыми импульсами, приходящими со входа 15 через открытый по второму входу элемент И 11. Импульсы с. выхода Фоомиоователя 8 поступают на тактовый вход первого счетчика 9, который работает на уменьшение счета, и на тактовые входы первого. 3 и второго 4 регистров сдвига, осуществляя сдвиг неравномерной кодовой комбинации из регистра 3 в регистр 4 на определенное число разрядов, записанное в двоичном коде в первом счетчике 9. После обнуления счетчика 9 перепад логического уровня с выхода окончания-счета этого счетчика поступает на S-вход триггера 7, переключая его в нулевое состояние и останавливая тем самым запуск формирователя 8 очередным тактовым импульсом, приходящим со входа 15. Неравномерная кодовая комбинация оказывается записанной во втором регистре 4. Триггер 7, формирователь 8, первый счетчик 9 с заведенной с его выхода обратной связью представляют собой программируемый генератор импульсов, выдающий заданное, записанное в двоичном коде в счетчик 9 количество импульсов, соответствующее числу разрядов каждой неравномерной кодовой комбина- ции.Таким образом, комбинации, выбранные из первого блока 1 постоянной памяти,

последовательно записываются по второй регистр 4, накапливаясь в нем.

Импульсы с выхода формирователя 8 поступают также на тактовый вход второго Г счетчика 10, представляющего собой реверсивный счетчик, работающий на уменьшение счета, в котором первоначально из блока 12 записывается значение k. соответствующее общему числу свободных позиций 0 для информационных посылок. Двоичный код с выходов счетчика 10. соответствующий числу { оставшихся незанятыми позиций информационной части кодового слова, поступает на вторые входы цифрового ком- 5 паратора 13, на первые входы которого из второго блока 2 постоянной памяти поступает двоичный код, соответствующий числу позиций, занимаемых очередной передаваемой неравномерной кодовой комбина0 цией. В компараторе 13 происходит сравнение этих двух двоичных чисел. Если число оставшихся свободными позиций Формируемого блока больше или равно числу позиций , занимаемых очередной кодовой

5 комбинацией, выбранной из первого блока 1, то присутствующий на выходе компаратора 13 логический уровень, поступающий на второй вход элемента И. 11, разрешает запуск формирователя 8 тактовыми импульса0 ми, приходящими на его тактовый вход, и очередная неравномерная кодовая комби- наци-я будет поразрядно записываться во второй регистр 4 сдвига, где происходит формирование передаваемого кодового

5 блока. Как только число свободных Л пози- ций окажется меньше числа позиций очередной кодовой комбинации, на выходе компаратора 13 появится логический сигнал, запрещающий запуск формирователя

0 8. Этот же логический сигнал поступает на вход разрешения параллельной загрузки регистра 4 сдвига и на управляющий вход формирователя 5 проверочных символов и разрешает запись с выходов счётчика 10

5 двоичного кода, соответствующего числу оставшихся незанятыми t позиций кодового слова, в отведенные для этой цели I позиций, а также разрешает формирование про- верочных посылок и запись их в

0 соответствующие позиции регистра 4. Сигнал с выхода компаратора 13 поступает также на #ход разрешения параллельной загрузки счетчика 10 и разрешает запись первоначального значения k позиций ин5 формационной части кодового слова от источника 12 постоянного кода в этот счетчик 10. Двоичный код, соответствующий числу k, появится на выходах счетчика 10, а, значит, и на вторых входах компаратора 13-, на первых входах которого будет присутствовать

двоичный код, соответствующий числу позиций очередной подлежащей передаче кодовой комбинации.

В результате сравнения на выходе компаратора 13 произойдет смена логического сигнала, что разрешит прохождение тактовых импульсов через элемент И 11, запускающих формирователь 8. который сдвигает записанную в регистре 3 очередную кодовую комбинацию и поразрядно записывает ее в регистр 4, из которого одновременно с записью происходит поразрядная выдача посылок сформированного прежде кодового блока. Таким образом, процесс формирования и выдача в канал связи (не показан) информации будут проходить одновременно, без задержки времени. Далее периодически формируются последующие кодовые блоки из п символов.

В декодере кодовый блок из канала связи через вход 33 последовательно поступает на вход блока 16 коррекции ошибок, в котором происходит вычисление контрольных сумм составляющих синдрома. В случае, когда значение синдрома отлично от нуля, по его значению в блоке 16 коррекции происходит определение местоположения ошибочно принятых информационных посылок и их замена на правильные. В случае, когда количество пораженных ошибками посылок превышает корректирующую способность помехоустойчивого кода, их исправление происходит неверно, необнаруженные ошибки остаются и могут вноситься дополнительные ошибки в информационную часть кодового блока.

Тактовые импульсы, частота следования которых подбирается так, чтобы в момент полной записи принятого кодового блока в блок 16 полностью очистился регистр 17 сдвига длиной в n-г ячеек, поступают со входа 34 на тактовый вход счетчика 25 и на объединенные тактовые входы регистров 17 и 18 сдвига, длина которого выбирается равной максимальному числу позиций, занимаемых неравномерной кодовой комбинацией, и осуществляют сдвиг n-г инфор- мационных посылок, переписываемых каждый раз в регистр 17 из блока 16 после получения нового кодового слова.

Таким образом, после полного заполнения счетчика 25, коэффициент пересчета которого также равен n-г, на его выходе появляется логический сигнал, поступающий на управляющий вход блока 16 коррекции и на входы разрешения параллельной загрузки регистра 17 сдвига и счетчика 24. а также на S-вход триггера 35, разрешая параллельную запись из блока 16 информационных n-г посылок в регистр 17, а из

соответствующих-f позиций регистра 17 - двоичного кода, соответствующего длине, служебной группы f , в счетчик 24 и устанавливая триггер 35 в единичное состояние.

определяющее изначальное отсутствие необнаруженных ошибок в информационной части принятого кодового блока. Счетчик 24, представляющий собой двоичный счетчик с предварительной записью, коэффициент

0 пересчета которого выбирается равным k, подсчитывает число тактовых импульсов, поступающих со входа 34 на его вход через открытый по второму входу третий элемент И 23 и определяет число k/позиций, занима5 емых принятыми неравномерными кодовыми комбинациями, входящими в данный кодовый блок, а значит, и плавающую границу t для этого блока. После полного заполнения счетчика 24 на его выходе появляется

0 логический сигнал, поступающий на R-вход первого триггера 28 и перебрасывающий его в нулевое состояние, запрещая тем самым прохождение тактовых импульсов на . вход счетчика 24 через элемент И 23. Этот

5 же логический сигнал с выхода триггера 28 поступает на второй вход первого элемента И 21 и запрещает последовательное поступление во второй регистр 18 оставшихся записанными в первом регистре 17 служебных

0 групп посылок-{ и Iх. Соответствующие выходы второго регистра 18 соединены параллельно с адресными входами первого блока 19 постоянной памяти и с первыми входами цифрового компаратора 30. Тактовые им5 пульсы, поступающие на S-вход второго триггера 29, устанавливают его каждый раз в единичное состояние, разрешая тем самым прохождение импульсов с выхода генератора 27 через второй элемент И 22,

0 открытый по первому входу логическим сигналом с выхода первого триггера 28. Эти импульсы с генератора 27 начинают проходить с момента начала поразрядного поступления неравномерных кодовых

5 комбинаций очередного принятого блока во второй регистр 18. Импульсы с выхода генератора 27, частота которого выбирается больше частоты следования тактовых импульсов в число раз, равное числу всевоз0 можных неравномерных кодовых комбинаций, соответствующих алфавиту источника сообщения, подсчитываются третьим счетчиком 26, на выходах которого формируется адрес, параллельно поступаю5 щий на соответствующие адресные входы второго блока 20 постоянной памяти и на вторые входы компаратора 30.

В результате сравнения кодогюй комбинации, поразрядно записываемой вп второй регистр 18 сдвига, с выбираемыми из оторого блока 20 постоянной памяти известными получателю неравномерными кодовыми комбинациями источника, при совпадении двух комбинаций, поступающих на соответствующие входы компаратора 30, на его выходе появляется логический сигнал, приходящий на вход разрешения выборки первого блока 19, разрешая выдачу первичной информации, хранящейся в этом блоке 19 и соответствующей данной неравномерной кодовой комбинации, т.е. происходит разделение информационных посылок на неравномерные кодовые комбинации. Кроме того, этим же логическим сигналом с выхода компаратора 30, поступающим на первый вход элемента ИЛИ 32 или же (в случае ненахождения кодовой комбинации, эквивалентной записанной в этот момент во втором регистре 18) сигналом с выхода дешифратора 31, который появляется после заполнения счетчика 26 и просмотра всех возможных адресов и поступает на второй вход элемента ИЛИ 32, перебрасывается в нулевое состояние второй триггер 29, сигнал с которого поступает на третий вход второго элемента И 22 и запрещает прохождение импульсов с выхода генератора 27 на вход третьего счетчика 26. С приходом следующего тактового импульса на объединенные тактовые входы регистров 17,18 сдвига, а также на S-вход второго триггера 29 содержимое регистров 17, 18 сдвигается на одну позицию вправо, а тригер 29 перебрасывается в единичное состояние, разрешая прохождение импульсов через второй элемент И 22 на вход третьего счетчика 26 Таким образом, процесс формирования адресов счетчиком 26, просмотр содержимого второго блока 20 постоянной памяти и Сравнение кодовых комбинаций в компараторе 30 по-. вторяется снова и завершится,после поразрядного прохождения через второй регистр 18 всех информационных посылок группы k( поступающих из первого регистра 17 сдвига, до тех пор, пока не заполнится счетчик 4 и не перебросит первый триггер 28 в нулевое состояние, запрещая прохождение инормационных посылок по второму входу первого элемента И 2.1 на вход регистра 18. При возникновении в принятом блоке инфорации большего числа ошибок, чем корректирующая способность помехоустойчивого кода, разделение на неравномерные кодовые коминации и их декодирование осуществляется еверно. Тогда, в ряде подобных случаев, поле записи последней информационной поылки в регистр 18 сдвига и просмотра всех озможных неравномерных кодовых комбиаций, записанных во втором блоке 20 постонной памяти по всем адресам,

формируемым счетчиком 26, кодовая комбинация, эквивалентная записанной в регистре 18, не находится. На выходе дешифратора 31 происходит смена логиче- 5 ского сигнала, а на выходе компаратора 30 логический сигнал не изменяется и подается на вход инвертора 37. Инвертированный в блоке 37 сигнал поступает на второй вход четвертого элемента И 35, на первом входе

10 которого после полного заполнения счетчика 24 появляется логический сигнал, определяющий окончание декодирования группы к,7 т.е. границу t для данного блока . Смена логич бского сигнала на выходе элемента И

15 35, поступающего на R-вход третьего триггера 36, устанавливает его в нулевое состояние. Соответствующий логический сигнал появляется на решающем выходе38 декодера, определяя наличие ошибок в принятом

0 кодовом блоке. Тогда данный блок или стирается, или может подаваться запрос на повторную передачу этого блока.

В случае, если число ошибок в принятом кодовом блоке соответствует корректирую5 щей способности помехоустойчивого кода, или же, когда ошибки большей кратности создают такое разделение на неравномерные кодовые комбинации, что последняя посылка, записываемая в регистр 18. приводит

0 к разрешенной кодовой комбинации, которой соответствует эквивалентная комбинация из блока 20, на выходе компаратора 30 не происходит смена логического сигнала и триггер 36 остается в единичном состоянии,

5 т.е. принятый кодовый блок является безошибочным или в нем присутстауют необнаруженные ошибки. На решающем выходе 38 декодера остается прежний логический сигнал.

0 Следующий цикл обработки нового кодового блока, поступающего на вход 33 де- кодера, начнется после заполнения счетчика 25, выдачи им нового сигнала разрешения и установки триггера 36 в единич5 мое состояние.

Рассмотрим конкретный пример. Пусть символам источника соответствуют, неравномерные кодовые комбинации, показанные в таблице.

0 В качестве помехоустойчивого кода используется код Хэмминга Ai5.ii, исправляющий однокрадную ошибку. Предположим, что передаче подлежит последовательность ABC... .Тогда сформированный кодовый

5 блок в соответствии с кодом A 15,11 и приведенной таблицей, будет выглядеть следующим образом : СнСг1С4010С80110001,где Ci, C2. СА, CQ- проверочные символы, определяемые по следующим формулам:

Ci Сз©С5©С7©С9фС12®С15.

С2 - Сз©СбвС7 СюФС11ФС14 $С15, С4 С5@С6©С7ФС12ФС13ФС14ФС15. Св С9ФС10©С11®С12ФС1зб С14фС15;

и где Сз 1, Gs 0, Сб 1. С 0, Сэ - 0, Сю1 1. Cn I, Ci2 0,

Так как длина k равна 8 двоичным посылкам, тогда {и определяются соответственно как: Ci3 0, Ci4 0, Cis 1. Предположим, что в кодовом блоке после передачи в канал связи произошла двукратная ошибка и инвертировались третья и девятая посылки (т.е. Сз 1. Сэ 1). Тогда на приеме вычисленный синдром 4 будет иметь вид: S4S3S2Si 0101. После исправления ошибок и инверсии десятого разряда информационная часть принятого кодового блока (без учета комбинаций (и в ) будет разделяться на неравномерные комбинации следующим образом: 00 1 00 1 1 1 0. Последняя кодовая комбинация, полученная в результате такого (неправильного) разделения, не соответствует ни одной из записанных в блоке 20 постоянной памяти неравномерных кодовых комбинаций. Это означает, что в принятом кодовом блоке произошло более одной ошибки, и декодером получателю информации выдается сообщение об ошибочном блоке.

Таким образом, преимущество предлагаемого кодека заключается в повышении

помехоустойчивости при передаче дискретных сообщений за счет дополнительного об-. наружения ошибок, кратность которых превышает корректирующую способность используемого помехоустойчивого кода. При этом эффект достигается без введения дополнительных проверочных символов в кодовый блок за счет использования свойства размножения ошибок при декодирова- нии неравномерных кодовых комбинаций.

Формула изобретения

Помехоустойчивый кодек для передачи

дискретных сообщений по авт.св. № 1651385, от л ича ю щи йся тем, что, с целью повышения помехоустойчивости кодека, в декодер введены четвертый элемент И, третий триггер и инвертор.

вход и выход которого подключены соответственно к выходу компарат.ора и первому входу четвертого элемента И, второй вход которого подключен к выходу первого счетчика импульсов, первый и

второй установочные входы третьего триггера подключены соответственно к выходу второго счетчика импульсов и выходу четвертого элемента И, решающим выходом декодера является выход третьего триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство для регенерации телеграфных посылок | 1985 |

|

SU1338080A2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

Изобретение относится к технике связи и вычислительной технике и может быть использовано в системах передачи дискретной информации, Цель изобретения - повышение помехоустойчивости кодека. Для этого в декодер дополнительно введены четвертый элемент И. третий триггер и инвертор с соответствующими функциональными связями. 3 ил.

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-15—Публикация

1990-07-10—Подача