а

со сд

со

ND

31

Изoбpeтe шe относится к средствам Передачи дискретной информации и может быть применено для исправления четырехкратных ошибок и стираний при приеме информации из канала связи списывании ее из внешних запоми- нающих устройств.

Цель изобретения - повышение достоверности приема дискретной информа lijHH путем исправления четырехкратных бшибок и стертых комбинаций двухпо- Зиционных сигналов.

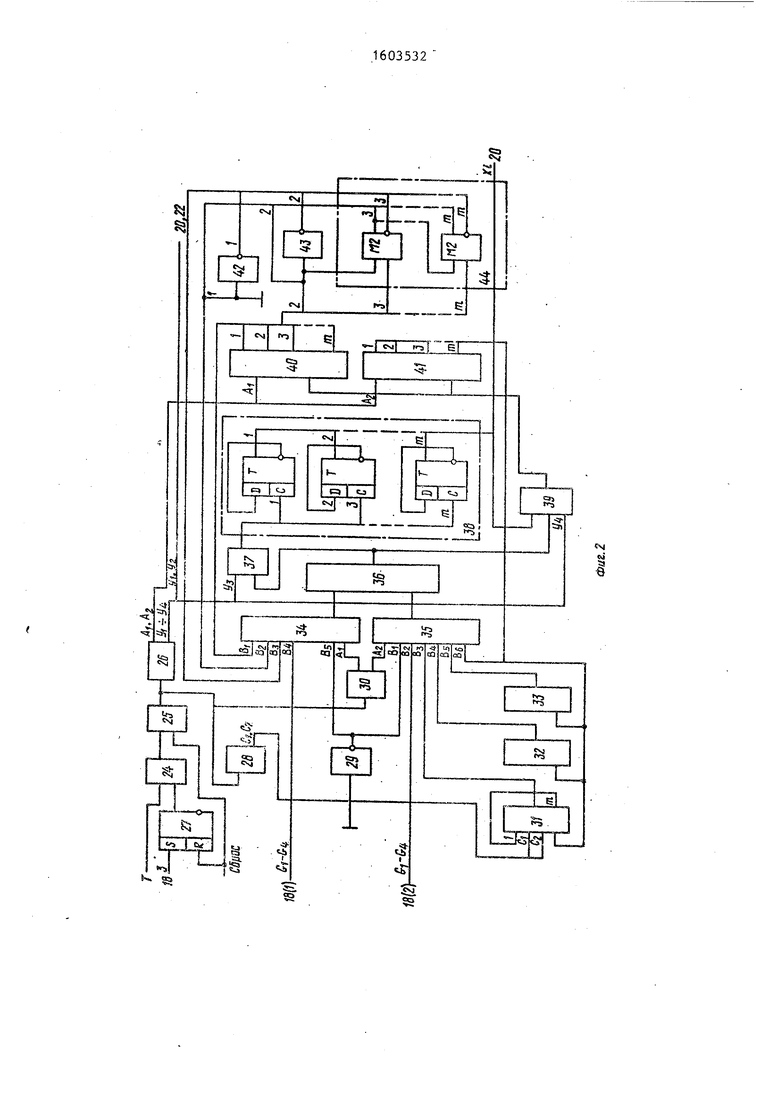

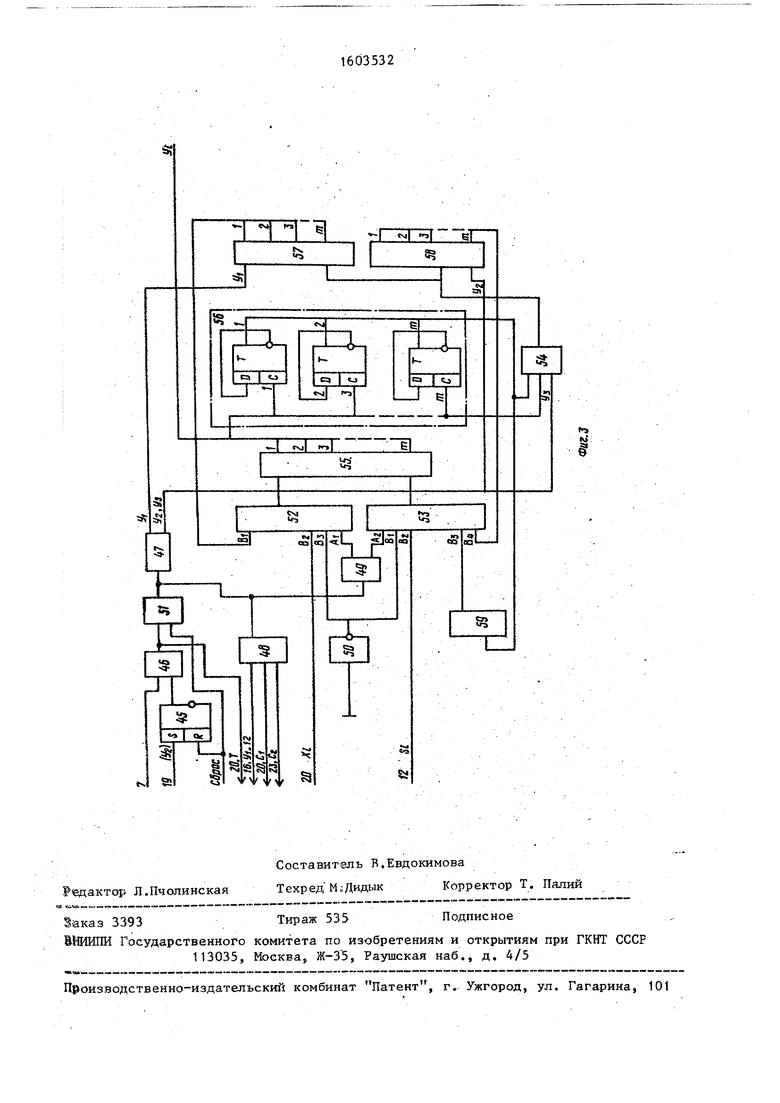

На фиго1 представлена структурная Электрическая схема устройства для исправления искажений в системах передачи дискретной информации; на фиг. 2 и 3 - блока локаторов Ошибок и блока определения искажений

Устройство для испраззления иска™ Жений в системах передачи дискретной информации содержит блок 1 приема синала, буферный накопитель 2, блок Сумматоров 3 по модулю два, блок элементов И 4, первый генератор 5 сиг- налов синдромов, первый счетчик б

импульсов, второй генератор 7 сигналов синдромов, второй счетчик 8 им- п шьсоВэ дешифратор 9 состояний, накопитель 10 сигналов синуэромов, де™ 1{шфратор 11 О ОибоКз первый коммута- top 12, накопитель 13 локаторов сти- Ьаний, блок 14 симметричесрсих функ

дий (ВСФ)з счетчик 15 стираний, блок 16 модифицированных сивдромов (ВМС)5 второй коммутатор 17, блок 18 коэффициентов ключевого уравнения, блок 19 локаторов опмбок, третий коммутатор 20, дешифратор 21 стираний, блок 22 определения искажений и элемент ИШ-1 23 „

Блок 19 покаторов ошибок содержит элемент И 24 э счетчик 25 импульсоВд ,| лервый блок 26 постоянной памяти (БГШ) триггер 27, второй БПП 28, первый инвертор 29.,, третий БПП 30., регистр 31 сдвига, четвертый 32 и пятый 33 Snilj первый 34 и второй 35 ко1-1мута- умнолштель 36, блок элементов

m триггеров 38, третий 39S первый 40 и второй

торы,

PI 37, блок коммутатор блоки оперативной пам.яти (БОП), второй 42 и третий 43 инверторы; блок 44 сумматоров по модулю два. Блок 22 определения искажений содерз шт триггер 45s, элемент И 46., первый; 47, второй 48 и третий 49 БШ1, инвертор- 50 и счетчик 51 j первый: 52 второй 53 и третий 54 коммутаторы умножитель

..

Q

5

0 5 nm

0

5

45

55

55, блок m триггеров 56, первый 57 и второй 58 БОП и четвертый БПП 59.

Устройство для исправления искажений работает следующим образом,

В устройстве декодируется блок информации, закодированный каскадным кодом, при котором кодирование осуществляется внешним и внутренним кодерами. В качестве внешнего чаще используют кодер на основе кода Рида- Соломона. Этот кодер осуществляет кодирование комбинаций т-разрядных двухпозиционных сигналов, образзтащих поле Галуа GF(2) избыточным (n,k) кодом, где k - число информационных комбинаций двухпозиционных сигналов; п общее число комбинаций в кодовом блоке. Внутренний кодер осуществляет кодирование т-разрядных символов (комбинаций) вторым избыточным кодом (т,,т), где т общее число разрядов второго кода. Таким образом, общая длина блока информации, закодированного каскадным кодером, равна

4

50

Внутренний код используется для обн аружения ошибок в комбинациях и стирания их В простейшем случае можно взять код с проверкой на четность. Информация из канала связи или блока внешней памяти поступает на блбк приема сигнала 1, в качестве которого может использован демодулятор модема. После преобразования модулированного сигнала в двоичную последовательность сигнах1ов они параллельно подаются в буферный накопитель 2 и генераторы 5 и 7. При применении кода с проверкой на четность (т+1)-разрядные комбинации во втором генераторе 7 проверяются на четность (один проверочный бит) о

Если в комбинации нечетное число двоичных единиц то на выходе второго генератора 7 появляется сигнал стн- ранияэ адрес (локатор) которого в данный момент фиксируется первьа-г счетчиком 6, Число с стираемых комбинаций, которое может исправить код Рида-Соломона c. где d кодовое расстоянн:е; t - кратность исправляемых ошибочных комбинаций. При исправлении четырех огтабочньвс комбинаций с f:::d-9 ,

Во втором генераторе 7 определяется с стираемых комбинаций а в первом генераторе 5 опред 2ляются S

09

5 . .

S.J.,; синдромы искаженных комбинаций

путем деления кодового блока на составные части образующего полинома g(x)(x+1)(x+o/)(x+6).,, ( ), где ftj - примитивный элемент поля GF(g). При этом на второй генератор 7 синдромов подаются ()-разрядные комбинации, а на первый генератор 5 и буферный накопитель 2 т-разрядныё

чивает совместно с сигналом с второго выхода дешифратора 21 запуск второго I счетчика 8. На каждую операцию при нахождении тратится 1 такт. На первом такте состояние второго счетчика 8 вьщеляется дешифратором 9, сигнал с выхода которого попадает в БСФ 14, который начинает работать

-- -t у wjJDun па ti 1 рсЮОТаТЪ

комбинации (без проверочных разрядов). ,о при наличии стертых комбинаций. Де- .п ..° записываются в накопитель шифратор 21 фиксирует при этом наличие стертых комбинаций и вьщает сигнал, который разрешает работу БСФ 14 второго счетчика 8, ВМС 16, пере- {5 кпючает второй коммутатор 17 на про10 сигналов синдромов. На выходе накопителя 10 включен дешифратор 11 ошибок, который представляет собой элемент ИЛИ. Если при делении получаются остатки, (т.е. ), то они содержат хотя бы одну 1. Тогда на выходе дешифратора 11 появляется сигнал Ошибка. Если S( , . . . S;.|,, 0, то на втором входе появляется сигнал

Нет, обозначающий отсутствие ошибочных и стертых комбинаций. При появ лении сигнала Нет информационная часть кодового блока вьщается потрехождение через него комбинаций моди- .фицированных синдромов s . БСФ 14 начинает работу и на первом такте

л.

сигналы в накопитель 13 и 20 третий коммутатор 20.

По сигналам, подаваемым в накопитель 13, списываются из него комбинации локаторов ошибок, которые с

.-----помощью других сигналов записываются

бителю через блок с шторов 3 путем- 25 в третий коммутатор 20. Одновременно подачи сигнала Нет на второй управ- в БСФ 14 начинается определение ком- ляющий вход буферного накопителя 2 и разрешающего сигнала на блок элементов И 4,

Во время записи кодового блока в буферный накопитель 2 производится также подсчет числа т-разрядных комбинаций первьм счетчиком 6 и определение синдромов ошибок во втором генераторе. 7„ Сигнал ошибки на выходе второго, генератора 7 разрешает за- пись состояния первого счетчика 6 в накопитель 13. Это состояние и является адресом (локатором) стираемых

бинации t двухпозиционных сигналов, соответствуюилих симметрическим функциям от локаторов стертых комбинаций, 30 в соответствии с выражениям- :

С, х5+Х5+х..... ., ;

,+XjX-7 А

-...+xj,, d-2t-, ;

35 7--- d-zt-x d-itH (1)

При этом процесс расчета и преобразований принятых комбинаций, каждая из которых содержит m битов в покомбинацнй в (п,1с)-кодовом блоке. Так дО е Галуа GF(2 осуществляется в нор- адресуются и другие комбинации, вмальном базисе. Все элементы (комбикоторых обнаруживаются ошиб ки вторымнации) поля GF(2) можно представить

генератором 7 синдромов.в виде степени примитивного элемента

Число сигналов оишбок (стертых Ci . Если примитивный элементен удовкомбинаций или стиргнкй) подсчитывает--,45 летворяет дополнительному условию: ся счетчиком 15 стираний и, если оно , элементы ( , oi, , ,. ,, яв- больше d-9, то сигналом Стирание с первого выхода дешифратора 21 стирается кодовый .блок в буферном накопителе 2. В противном случае сигнал, с вто- 50 рого выхода дешифратора 21 разрешает расчет элементарных симметричных функций локаторов стираний в БСФ 14

и подсчет операции преобразования комбинаций двухпозиционных сигналов вторьм счетчиком 8. После приема п-й кодовой комбинации кодового блока появляется сигнал на втором выходе первого счетчика 6, который обеспе55

ляются линейно независимыми над GF(2 ),, то они образуют нормальньш базис.

В таблицах можно выбрать пpимIiтив- ный многочлен соответст;вующей степени, корни которого линейно независимы, где ,1,2,...m-l. Тогда произвольньш элементу e GF(2) может быть представлен как некоторая степень oi и в виде разложения по нормальному базису

т-1;.

у Z (2)

1603532

чивает совместно с сигналом с второг выхода дешифратора 21 запуск второго счетчика 8. На каждую операцию при нахождении тратится 1 такт. На первом такте состояние второго счетчика 8 вьщеляется дешифратором 9, сигнал с выхода которого попадает в БСФ 14, который начинает работать

-- -t у wjJDun па ti 1 рсЮОТаТЪ

при наличии стертых комбинаций. Де- шифратор 21 фиксирует при этом наличие стертых комбинаций и вьщает сигнал, который разрешает работу БСФ 14 второго счетчика 8, ВМС 16, пере- кпючает второй коммутатор 17 на прохождение через него комбинаций моди- .фицированных синдромов s . БСФ 14 начинает работу и на первом такте

л.

в третий коммутатор 20. Одновременно в БСФ 14 начинается определение ком-

бинации t двухпозиционных сигналов, соответствуюилих симметрическим функциям от локаторов стертых комбинаций, в соответствии с выражениям- :

С, х5+Х5+х..... ., ;

,+XjX-7 А

-...+xj,, d-2t-, ;

7--- d-zt-x d-itH (1)

При этом процесс расчета и преобразований принятых комбинаций, каждая из которых содержит m битов в пое Галуа GF(2 осуществляется в нор- мальном базисе. Все элементы (комби45 летворяет дополнительному условию: , элементы ( , oi, , ,. ,, яв- 0

5

ляются линейно независимыми над GF(2 ),, то они образуют нормальньш базис.

В таблицах можно выбрать пpимIiтив- ный многочлен соответст;вующей степени, корни которого линейно независимы, где ,1,2,...m-l. Тогда произвольньш элементу e GF(2) может быть представлен как некоторая степень oi и в виде разложения по нормальному базису

т-1;.

у Z (2)

Представление элемента J в виде разложения по нормальному базису

при возведении в степень вида

о ч

г. „

НапримерJ если (комбинацию двух- яозиционных сигналов) элемент jf

loOi+ У, Уг + .- J m-, возвести в квадрат, то получает

о2-,

. К ) +(Jf,) -((fi) +..+ H-Clf.. - f {fmмCi + foOг -

..- |fm--г&i (3)

, Z(rri-i ) так как ос ОС Таким образом,

возведение в квадрат означает циклический сдвиг элемента на один разряд вправо. Это упрощает операцию возведения в квадрат и увеличивает его быстродействие.

; С выхода БСФ 14 полученные значения с , подаются в, ВМС 16 d--( Scl-г So этом блоке произ- водится определение комбинаций сигналов соответствующих модифицированных синдромов по следующим формулам:

Sd--c + + d-c 1

Sdi- ZC4l C

s;,. s -c- -Sd-c-i - --- Sj-2c c )

d-c-1 Sj.cH -f-Sj.c-2 +8 -гсч с I S; Sc +Sc., 1,+...+ S,t-,,

Возмож-но, что в кодовом

блоке не зафиксировано стираний, что определяется с помощью дешифратора 21 стираний о Тогда с-летчик 15 стираний остается в О и на выходе дешн:ф ратора стираний сигнала нет, поэтому разрешения на работу ВМС 16 не дается , вькод накопителя 10 через коммутаторы 12 и 17 подключается на вход блока 18 коэффициентов G; ключевого уравнения., Таким образом в блок 18, коэффициентов подаются синдромы S;, Независимо от тогоэ синдромы (обычные ил:и модифииированные) подаюся в блок 18 коэффициентов,, процесс нахождения локаторов оЕибок не из- меняется. Поэтому для нахождения

локаторов ошибочных комбинащ1й необходимо найти комбинаци)1 двухпозипдонных сигналов, соответствующие локаторам ошибокх - х по ключевому уравнению;

G(x) -frG X +G x+Gjj, (5) в котором

G,,;

G х, х +х, X 5+х,х +Х2Х +Х5х,;

Vjл Х Хл X д т Х . X-Х Xrt Хд Хх ( .

(6)

Корни уравнения (5) и являются локаторами х,- х ошибочных комбинаций. Коэффи1щенты G;j-G4 ключевого уравне- ния (5) определяются по системе рекуррентных уравнений в блоке 18 коэффициентов:

S6+S5G,,+84 G2.+S5G3+S G 0 5 S-r+S6G +S5G2.+S4G3+S3G4 0;

Sg+S-yG, +S6G2.+S5G,, , +S7G2.+SgG,,+S 50.0.

Найденные в блоке 18 коэффициентов комбинации двухпозиционнык сигналов, соответствующие коэффициента Gi,, подаются в блок 19 локаторов ощиёок, где начинается вычисление комбинаций х - х двухпозиционных сигналов, соответствующих локаторам ошибок Предлагается вместо трудоемкой процедуры Ченя преобразование комбинаций в соответствии с ключевым уравнением четвертой степени, которое сначалл приводится к биквадратной, а затем- к канонической формам«

Приведем процесс преобразования уравнения (5), элементы которого представлены в нормальном базисе

Для нахождения локаторов ошибоч- ных комбинаций необходимо преобразовать - фавнение:

х х G +х G G 3 ,

1 . /G «,

(8)

«/а

Подстановкой х - (--)

У Ь

мула (8) приводится к виду:

форGiГ

АО

1

-0„ (9)

Новая подстановка дает уравнеш-:е

(10)

2 -i-K, Z .0:

/ pi . - - где (Gj,G3) (--- -) ;. (ц) №i нахождения локаторов ошибочных

1 комбинаций необходимо найти величины

G(G,G,) ;(12), .,„2

-г гАо J/2 5

2 АО

IT - W

2- AT

(12) (13) (14)

h 1/к; ; (24) Кг

(T+FT

у (0, m ,, m,+in,j,. ..,m,... ,.,).(26)

Уравнение (10) можно представить в биквадратной форме

,z+K,i(z +Az+B)(zSAz+C) 0.(15)

где А + В + С 1j

А(В+С)К; ,.

(16) (17)

Эти уравнения приводятся к следу- 20 ющим видам:

+А +

+(.,0.

помощью подстановок 1

U

(18) (19)

(20) (21).

кубическое уравнерше (18) приводится к виду

/ t +K,.

Заменой переменной , Уполучают

f- Г - -г °-

2

Обозначим , тогда

V (22)

Для элементов поля ГалуаGF(2),

представленных в нормальномбазисе,

корень уравнения (22)

(0, h,h,+h2,h,+h2+h5,..., h,... +h.,)(23)

где h -i-й разряд комбинации h.

Приведем квадратно уравнение (19) к удобному для решения виду с помощью . подстановки ,(1+А ). В результате 5 получают

е Кг

У, У - ( °

, .,„2

5

h 1/к; ; (24) Кг

Ю

15

0

5

(T+FT

у (0, m ,, m,+in,j,. ..,m,... ,.,).(26)

Решают квадратное уравнение: Z +Az+B 0. Подставляя , получают

+ + . Обозначают

С0 (27)

В результате получают +СО 0.-(28)

Корни уравнения (28) получают по 30 вьфажениям:

6, (0,СО, ,(л), +«2, ...G}, + a)j,+,.,

+W.,-);(29)

2.(Uw, + i, 1+Сл), +С02...Н w,+ ...+ю„ .).(30)

40

Второе квадратное уравнение z +Az + приводят к коническому виду:

(31) (32)

Комбинации двухпозиционных сигналов, соответствуюпре корням уравнения (31)5 получают из выражений:

(0,-s),, О, +,...,-),+ }2.+ ...+ + т-, -(33)

64 (М + ,; 1+, + +

I.. ...+ 5m-i).(34)

Путем преобразования комбинаций двухпозиционных сигналов, соответст 1603532

вующих элементам поля Галуа , по Шф а

, жениям (8),-(34) находятся локаторы

ошибок Х, X fj . :. ,

Локаторы стираний к(j(j определены и записаны в блок 22 определения искажений. Необходимо опре,целить значения локаторов у- ошибочных и стер- тШх комбинаций двухпозиционньк сигналов Их определяют с помощью следующего выражения;

с .с 0 с

4Gje sst-e .,

е j

Рассмотрим подробнее работу блоков устройства для исправления при исправлении четырех ошибочных и трех стертых комбинаций двухпозиционных сигналов, имеющих m разрядов в поле Галуа GF(). При этом положим , элементы (комбинации двухпозиционных .сигналов) поля Галуа GF(2) образуют- ся с помощью полинома F(x)x®+x + .

При трех стертых комбинациях двухпозиционных сигналов формулы (1) пе- реписываются в виде:

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1552381A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для вычисления локаторов ошибок | 1990 |

|

SU1728972A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для декодирования кода Рида-Соломона | 1985 |

|

SU1332539A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

Изобретение относится к технике передачи дискретной информации. Цель изобретения - повышение достоверности приема дискретной информации. Устройство содержит блок 1 приема сигнала, буферный накопитель 2, блок сумматоров 3 по модулю два, блок элементов И 4, г-ры 5 и 7 сигналов синдромов, счетчики 6 и 8 импульсов, дешифратор 9 состояний, накопитель 10 сигналов синдромов, дешифратор 11 ошибок, коммутаторы 12, 17 и 20, накопитель 13 локаторов стираний, блок 14 симметричных ф-ций, счетчик 15 стираний, блок 16 модифицированных синдромов, блок 18 коэффициентов ключевого уравнения, блок 19 локаторов ошибок, дешифратор 21 стираний, блок 22 определения искажений и эл-т ИЛИ 23. В данном устройстве достоверность приема дискретной информации повышается путем исправления четырехкратных ошибок и стертых комбинаций двухпозиционных сигналов. Устройство по п.2 ф-лы отличается выполнением блока 19 локаторов ошибок, дана его ил. 1 з.п. ф-лы, 3 ил.

(35)

где 1 6 N) t + С|

: 5j,i.

: Определение , осуществляется пф рекуррентной формуле

.Gjv

)i(-0

(36)

где b - элементарные симметрические функции от локаторов ошибочных и стертых комбинаций двухпозиционньк сигналов.

Значения у ошибочных и стертых комбинаций определяют в блоке 22 определения искажений путем преобразо- в4ний комбинаций двухпозиционных С1|гналов в соответствии с вь ражениям:и (35) и (36). i i

: Локаторы X ; ошибочных и стертых комбинаций являются aдpeca ш искажен- HfciEx комбинаций кодового блока. Путем подачи этих адресов па буферный накопитель 2 производится считывание из него искаженных комбинаций xj, которые подаются на блок сумматоров 3 по модулю два; на вторые входы блока сумматоров 3 из блока определения искажений 22 подаются значения определенных локаторов искаженных комбинаций (ошибочных и стертых) . Сложение значения искаженных комбинаций XI с соответствующими вьгаисленкыми значениям:и у локаторов в блоке сумматоров 3 обеспечивает их .исправление lie правленные комбина1д:яи снова записываются в буферный накопитель 2 по соответствующим адресам. После этого исправленный кодовый блок спи- С1ьшается через блок сумматоров 3 по модулю 2 потребителю информации. На этом заканчивается процесс исправле- ния ошибочных и стертых комбинаций.

t, х

+х,

г 7 ;

1 I I

(3)

5

0

5

Последовательность нахождения комбинаций X,,- Хф двухпозиционных сигналов определяется по комбинациям сигналов соответствующим G.- 64/которые хранятся в блоке 18 коэффи циен- тов ключевого уравнения. При этом по окончании определения комбинации G из блока 18 коэ ффициентов вьщаётся сигнал записи, с помощью которого триггер 27 устанавливается в 1 и через элемент И 24 на счетчик 25 начинают проходить тактовые импульсы Т. БПЦ 28 и 30, подключенные на выходы счетчика 25, начинают управлять работой блока 19 локаторов ошибок. При этом, вначале определяются комбинации сигналоВз соответствующие коэффициентам АО, А2, К и К2,по выражениям (11)-(1А). Комбинации G., -- описываются из блока 18 коэф)ициен- тов.

На первом такте работы счетчика 25 из блока 18 коэффициентов считываются комбинация G, которая подается на вход коммутатора 34. БПП 30 подключает соответственно на первый вход умножителя 36 комбинацию G, а на второй вход коммутатора 35 с инвертора 29 комбинацию (х1° 11111111 (при ). Результат умножения,, т.е. 0 G(G(}. записывается через блок 37 элементов И,, открытых сигналом с выхода БПП 26, на триггеры блока 38 триггеров. На. втором такте из блока 18 коэффи1 ;иентов списьшают комбинации , а БПП 30 подключает их соответственно на первый и второй входы умножителя 36,

Полученное произведение БПП через коммутатор 39 и по первому ад ресу записывается в БОП 40.

Комбинация G, списывается из бло 18 коэффициентов на третьем такте и аналогично с помощью БПП 30 через коммутатор 34 подается на первый вход умножителя 36, на второй вход которого подается комбинация двух- позиционных сигналов oi. Произведение of , проходит через коммутатор 39 и сигналом с вькода БПП 26 записывается в БОП 41.

и

На следующем такте БПП 26 списывает из БОП 40 величину ,,, а из БОП 41 -G, Комбинация подключается с помощью БОП 30 через коммутатор 34 на первый вход умножителя 36. Комбинация G, попадает на адресный вход БПП 31. По адресу, задаваемому комбинацией G,, в БПП 32 записана комбинация 1/G, которая через коммутатор 35 подается на второй вход З множителя 36, На выходе умножителя 36 получают комбинацию двоичных сигналов, которая соответствует

,

складывается с G на триггеры бло- ка 38 триггеров. Каждый триггер этого блока работает как накапливающий сумматор по модулю два.

На пятом такте из блока 18 коэффициентов списывается и подается на первый вход умножителя 36 комбинация G а из БОП 41 списывается комбинация Gy, которая обеспечивает получение на выходе БПП 32 величины 1/G,. Эта величина подается на второй вход ум

ножителя 36

Произведение G

проходит г. через коммутатор 39 и записывается в БОП 4 к а на следующем такте списьгоается и подается на регистр 31 сдвига. На седьмом такте по С, входу с выхода БПП 28 подается .сигнал, который сдвигает содержимое регистра сдвига 31, выход которого соединен с первьп. входом, вправо. Это соответствует возведению в квадрат-величины Gj/G, , которая подается на второй вход умножителя 36. На первщй вход умножителя 36 одновременно подается комбинация oi°. Полученное произведение на восьмом такте складывается с содержимым триг геров блока 38 триггеров.

03532

6 А

|Q

14

В результате получают комбинацию в соответствии с вьражением (11),

5

20 25

ЗО

35

40

которую записывают на девятом такте в БОП 40.

Далее аналогично получают комбинацию А в соответствии с выражением (12). При этом после получения произведения G,G3Ha 11-м такте эта комбинация записывается в БОП 41 и на следующем такте переписывается на регистр сдвига 31. На 13-м такте из БПП 28 по цепи С подается сигнал Сдвиг влево. Содержимое регистра циклически сдвигается апево, что соответствует извлечению квадратного корня из . После получения комбинации Aj, она записывается на 15-м такте с помощью БПП 26 в БОП 40 и 41.

Комбинация К, получается в соответствии с (13). Для этого А списы- .вается из БОП 41 и записывается на регистр 31 сдвига. По цепи Cg из 28 на 17 такте подается .сигнал Сдвиг влево, содержимое регистра 31 сдвига циклически сдвигается в результате чего в нем,появляется комбинация А , На следующем такте из БОП 40 через коммутатор 34 на первый вход умножителя 36 подается ко; бина- ция А, а на второй, вход умножителя 36 из регистра сдвига 31 подается комбина1щя А . На выходе умножителя 36 получают величину А , которая-записывается в ВОП 41. На 19-м такте на первый вход умножителя 36 подается комбинация А из БОП 40. Комбинация А списывается из БОП41 и подается на БПП 32, на выходе ко1

торого величину. Эта

А

величина подается на второй вход умножителя 36, на выходе которого полу- 45 чают комбинацию двухпозиционных сигналов, соответствующую величине

которая проходит через комму- А,

татор 39 и записывается в БОП 41. По- 50 лученная величина на следующем такте списьшается на регистр 31 сдвига, на С -вход которого на 21-м такте подается сигнал Сдвиг влево. В регистре 31 сдвига папучают комбинацию 5 АО /г .

А 2

Комбинация G списывается на 22-м такте из блока 18 коэффициентов и

5 1603532

на первый вход умножителя 36, 1/и подается

ля 36, а на ся величина 1 умножителя 3 ся по модулю ров блока 38

на второй вход которого подается Аг .

На выходе умножителя 36

(ej2)

л 2А

получают комбинацию К., которая записывается в БОП 40 и 41 о I

Комбинацию двухпозиционных сигналов j соответствующую величине К , получают аналогично и записывает на 26-м такте в БОП 40.

Дальше получают комбинацию h в

соответствии с выражением

h. - -р.

15

Для этого из БОП 40 и БОП 41 на оба входа умножителя 36 подают -комбинацию К( и полученное произведение К, на 27-м такте записывается в БОП 41. На следующем такте К списывают из БО 41 и подают на вход БПП 32, на вы|ходе которого получают комбинацию

I/K

Згу комбинацию подают на второй вход умножителя 36 а на первый вход подключается о(° . На выходе ум - ножителя 36 получают комбинацию 1/К h5 которая записывается на 28-м такте в БОП 40. Затем комбинация h за исключением первого и второго разрядов подается на блок сумматоров 44 по модулю два, содержащего (т-2) сумматоров, второй вход каждого из кото- начиная со второго соединен с вькодом предьщущегоэ а второй вход nejpBoro сз мматора - с второй выход- ной цепью БОП 40 В результате через ко ммутатор 34 на первый вход у1-.шожи- теля 36 подается величина J , полученная в соответствии, с выражением (23)5 а на второй вход из БОП 41 -

комбинация К, На выходе умножителя 36 получарэт комбинацию ,| J , которая записывается на 29--м такте в Б ап 41.

Комбинация t списывается из БОП 4 и подается на вход ВГШ 335 на выходе которого получают величину и Цt в соответствии с выражением (21). Эт вб личина подается через коммутатор 3f на второй вход умножителя 36, а

на первый вход его подается величина (У.°о Комбинацрш сигналов, соответств п щая Uj с выхода у У Ножитепя 36 проходит через блок 37 элементов И и коммутатор 39 параллельно записывает ся на блок 38 триггеров и в БОП 41,

На 31-м такте и списывается из БОП 41 и подается на вход БПП 32 и П элученная на его выходе комбинация

16

1/и подается

0

5

0

5 0 5 40

45 50

55

на второй вход умножите- ля 36, а на первый вход вновь подается величина . Полученная на выходе умножителя 36 величина 1/и складывается по модулю два с содержимым триггеров блока 38. В результате получают

комбинацию А и+ ---, которая переписывается на 32-м такте из блока 38 триггеров через коммутатор 39 в БОП 41.

На следующем этапе определяется комбинация сигналов, соответствующая m по вьфажению (25). Вначале комбинация А списывается БОП 41 и записывается на регистр 31 сдвига, а затем из БОП 28 на 34-м такте подается сигнал С, который сдвигает содержимое регистра 31 сдвига вправо, что аналогично возведению в квадрат комбинации А, Комбйнаи ия А подается на второй , вход умножителя 36, а на первый вход подается сх1° с инвертора 29. С.выхода

умножителя 36 комбинация А записывается на триггеры блока 38 и в -БОИ 41 на 35-м такте. На следующем такте на оба входа умножителя 36 подается

величина на сложение

с выхода

с А

2подается

на триггеры блока 38л

Полученная сумма 1+А через коммутатор 39 списывается на 36-м такте в

БОП 41 а затем на регистр 31 сдвига. На вход С регистра 31 из БПП 28 подается на 38-м такте сигнал Сдвиг вправо. В регистре 31 получают вели- чину (1+A)s которая подается на второй вход умножителя 36, а на первый вход подается od,

С выхода умножитапя 36 на 39-м такте комбинация сигналов, соответствующая (I+A), записывается в БОП 41 j на следующем такте она подается на вход БПП 32. Полученная на выходе БШ1 32 комбинация l/d+A) подается на второй вход умножителя 36, а на первый вход из БОП 40 - комбинация К„. Таким образома на вьпсоде умножителя 36 получают комбинацию т, которая записьшается на 40-м такте в БОП 40, При списьшании m из БОП 40 на выходах блока 44 сумматоров по модулю ABHj второй цепи и первом входе инвертора 42 с нулевым потенциалом получают комбинацию у в соответствии с (26),, I

Далее аналогично получают величину (), на что тратится 5 такВ

тов, затем сО , которую записывают в БОП 40 на 48-м такте. На прямых выходах блока 44 сумматоров и входах инверторов 42 и 43 и на инверсных выходах блока 44 и выходах инверторов 42 и 43 получают комбинации сигналов, соответствующие коэффициентам уравнений (29) и (30) т.е. fcl и Cg.

По выражению аналогично определяют комбинации Z, и z, которые записывают в БОП 41 на 49-м и 50-м тактах.

Дальше по выражению ( 1 7) находят

комбинацию С, а затем -- . ИреА

образования по формулам (33) и (34) дают еще два коэффициента , и (. , по которым аналогично находят ZA которые также записывают в БОП 41 на 56-м и 57-м тактах.

Комбинации двухпозиционных сигналов, отображающие локаторы ошибок ., находят по выражению

.(-i) .

1

X - АО ч

, ---« .««.ш .

ч АAV

Комбинации G и А записаны в

БОП 41, а комбинация А - в БОП 40. Поэтому комбинация Ag с помощью БПП 26 списывается из БОП 41 и подается на БПП 32, на выходе которого, получают 1/А.., которую подают на второй вход умножителя З б, а на первый вход БПП 26 с помощью БПП 30 подают комбинавдю AQ. АО/А с выхода умножителя записывается на 58-м такте в БОП 41.

На следующем такте комбинация Ag / списьгаается из БОП 41 и записывается на регистр) 31. Далее на вход С подается сигнал Сдвиг влево и в регистре 31 получают комбинацию (AQ/AJ,) . i Эту комбинацию подают на второй вход умножителя 36, а на первый вход подают комбинацию сх. Полученную на выходе комбинацию (АО/А.,) записывают на 61-м такте в БОП 40. 3i a комбинация необходима для дальнейших расчетов, х -х. Затем на первый вход умножителя 36 подают комбинацию (Ao/Ag) из БОП 40, из

у, -С, +G,iS2+G,S, +G,4S

10 i +G,,x; +G,,j,x| +0,x2

tO

„

20

603532:18

БОП 41 списывают комбинацию z

1, кото35

30

Q

дЗ 50

рая попадает на вход БПП 32, комбинацию 1/z с выхода этого блока подают на второй вход умножителя 36. Полученную на выходе величину на 62-м такте записывают на триггер блока 38.

Второй суммируемый член получают так.

Из БОП 41 списывают величину G и подают на вход БПП 32 с выхода комбинацию 1/G, подают на второй вход умножителя 36, а на первый вход из блока коэффициентов 18 подают комбинацию GJ. Полученное частное записывают на 63-м такте через коммутатор .39 в БОП 41. На следующем такте ком«G3

бинация --- записывается на регистр

31 и затем сдвигается сигналом С из БПП 28 влево. На первый вход умножителя 36 подается oi , а на второй - комбинация (-;;--)

Полученн5то на выходе умножителя

36 комбинацию (----)складывают

с содержимым триггеров блока 38, в результате получают первый локатор ошибок X,, который на 67-м такте по сигналу У| с БПП 26 списьшается Б БОП через коммутатор 20 аналогично локаторам стираний. Аналогично получают локаторы ошибок этом на определение каждого из них тратится 10 тактов. Таким образом, на определение всех локаторов ошибок .тратится 107 тактов.

Далее можно пристзшить к определению комбинаций у- дв тспозиционных сигналов, соответствующих значениям ошибок и стираний х:.

По локаторам х стертых и ошибочных комбинаций двухпозиционных сигналов (локаторам ошибок и стираний), записанным в БОП коммутатора 20 и кo бинaциям синдромов S; , используя формулы (35) и (36), можно найти комбинации у;. Процедуру нахождения у- можно описать при возникновении четьгрех ошибочных и одной стертой комбинации двзпспозиционных сигналов. В этом случае выражения (35) и (36) при определении у принимают вид:

(38)

19 G,G,,+х, ( s ,3 +x, I ,4 +x, I

G,x,H-X2,

(39)

вают из .БОП коммутатора 20, а другой из БОН 58 блока 19 локаторов ошибок, /В процессе нахождения G, используют

г предварительно найденные цроизведе(40)

НИН Х,Х,

,х,х

Комбинации G

,,л .

н

1г

G 13 и GU

G2,X;,, Хз+. о 0+Х4Х5 ;

G,, х,Х2.Хз+х, +,. . |

,X2X,,X2X3X5+X2X3X4X5-.

находят по выражениям (39) и записы- ваются в БОП 57. При этом G,, G, GS 10 и Of считываются из БОП 58, а х из БОП коммутатора 20, Результаты преобразований в соответствии с (39) списываются в блока 56 триггеров и- записываются в БОП 57. Управление записью и считыванием и подача адресов осуществляется БПП 47 и 49.

45 в 1, через элемент И 46 начинаю проходить тактовые импульсы Т, кот о- рые поступают на счетчик 51 и на третий коммутатор 20. БПП 49 своими выходами через коммутаторы 52 и 53 подключает на первый вход умножителя 55 выход третьего коммутатора 20, а на второй вход с«1° 1 с выхода инвер- Tlopa 50,

; Кроме того, тактовые импульсы Т проступают также на третий коммутач О1 2:0, который вьдает сигналы считывания и адреса 5 записанных комбинаций X. На первом такте из третьего коммутатора 20 списывается х . и подается на первый вход у множит еля 55. Резулзьтат умножения Ыо V, записывается на триггеры блока 56 и в .БОП 58. Аналогично происходит выбор Ki3. БОП коммутатора 20 и умножение на комбикаьщю х,. Результат складывается по модулю два с х на триг- блока 56 Кроме того, комбина- LCHH Xg также записывается через коммутатор 54 в БОП 57о Дал;ее процесс гювторяется и после сложения последующей комбинации X j. на триггерах блока 56 получают комбина дию G, которая переписывается в БОП 58 че- рез ко№/1утатор 58, Коммутатор 58

11од1 лючает выход блока 56 на вход ВОП 57. Этот коммутатор пправляется

сигналом с БПП 47о

Также определяются комбинации

: Вначале определяются комбинации д|вухпози1шонных сигналов, соответст- в|ующие функциям G, G,,, G;j и G. по ф ормуле (40) .

: G, находят так.

; После определения последней ком- б нации, соответствзлощей локатору оши бЬк, БПП 26 подает на тригге- PjB 45 блока 22 определения искажений сигнал, который устанавливает тригге

G,)

GjHG

При этом при определе- один из сомножителей считы-НИН Х,Х,

,х,х

Комбинации G

,,л .

н

1г

G 13 и GU

5

находят по выражениям (39) и записы- ваются в БОП 57. При этом G,, G, GS и Of считываются из БОП 58, а х из БОП коммутатора 20, Результаты преобразований в соответствии с (39) списываются в блока 56 триггеров и- записываются в БОП 57. Управление записью и считыванием и подача адресов осуществляется БПП 47 и 49.

После этого приступают к определению комбинации у, при этом вначале определяют комбинацию двухпозицион- ньк сигналов, соответствзтощую числителю выражения (38), а затем комбинацию сигналов знаменателя. Для нахождения числителя комбинации двухозиционных сигналов, соответствующие

синдромам SoS,..«S4, считьшаются сигналами с БМС 16, на который начинают поступать тактовые импульсы Т после установки его управляющего триггера в 1 сигналом с выхода блока БПП 48,

Этот сигнал одновременно открывает коммутататор 12, через который списываются комбинации синдрома в блок 22 определения искажений.

Комбинации, соответствующие синдромам Sj, поступают через коммутатор 53 на второй вход умножителя 55. Ком- бинаид и G((-Gj(4 поступают через коммутатор 52 на первый вход умножителя 55, Комбинацию двухпозиционных сигналов, соответствуюгдих числителю,

получают на триггерах блока, 56 а затем переписывают в БОП 57

Комбинацию сигналов, соответствующую знаменателю, определяют анаогично и она получается на триггерах блока 56. Комбинацию числителя необ.- ходимо разделить на комбинацию знаменателя. Комбинацию числителя списывают из БОП 57 и подают на первый

вход умножителя 55, а значение комбинации знаменателя подается на адресный вход БОП 59, по которому в нем записана комбинация 1/а, где а - комбинация, соответствующая знаменателю.

Комбинация 1/а подается на второй вход умножителя 56. В результа.те на выходе умножителя 55 получают комби- нагшю у . Эта комбинация сразз подается на первый вход блока cyiviMaTopoB

21

3 по модулю два. Каждую комбинацию у, сопровождает сигнал С с выхода БПП 48, который подается в коммутатор 20, из которого считывается комбинация локатора ошибок, которая является адресом искаженной комбинации, подаваемой на адресный вход буферного някопителя 2. Разряд искаженной V4 комбинации подаются на вторые f входы сумматоров по модулю два блока 3. При сложении разрядов искажений комбинаций комбинации с у. происходит исправление. Восстановленная комбинация записывается в буферный накопитель 2 по тому же адресу. Аналогично происходит исправление остальных искажений комбинаций двухпозицион- ных сигналов. После этого исправленный кодовый блок списывается из бу- ферного накопителя 2 через блок эле- ментов И 4 по сигналу из БПП 48.

160

Формула изобре

тения

22

15

20

25

30

тор, элемент ИЛИ и блок элементов И, при этом к входу первого счетчика импульсов подключен выход блока прие- ма сигнала, дополнительный выход ко- торого через второй генератор сигналов синдромов подключен к входу счетчика стираний, выходы накопителя сигналов синдромов подключены к соот- to ветствующим входам первого коммутатора, выход второго коммутатора подключен к входу блока коэффициентов ключевого уравнения, между выходами блока локаторов ошибок и входом блока определения искажений включен третий коммутатор, к первому входу блока .элементов И и другому входу буферного накопителя подключен выход блока сумматоров по модулю два, первые и вторые информационные выходы первого коммутатора подключены соответственно к вторым входал второго коммутатора и блока определения искажений, информационный и управляющий выходы блока симметрических функций соединены с соответствующ11ми входам блока модифицированных синдромов и третьего коммутатора, к информационным входам которого подключены соответствующие выходы накопителя локаторов стираний, второй информационный выход третьего коммутатора соединен с адресным входом буферного накопителя, другие выходы блока модифицированных синдро- 35 мов соединены с адресными входами первого коммутатора и блока коэффициентов ключевого уравнения, второй выход первого счетчика импульсов соединен с первым управляющим входом 40 накопителя локаторов стираний, к второму управляющему входу которого подключен соответствующий выход блока симметричесрсих функций, управляющие выходы дешифратора состояний подклю- 5 чены к соответствую1 9{м управляющим вхс- дам блока симметрических функций и блока модифицированных синдромов, управляющие выходы депшфратора стираний нены соответственно с первьм управля- 0 входом буферного накопителя и управляющими входами второго счетчика импульсов, блока симметрических функций блока модифицированных синдромов и т второго коммутатора, другой управ- 5 ляющий выход блока локаторов ошибок соединен с соответствующим входом блока определения искажений, информационный и управляюш й выходы блока коэффициентов ключевого уравнения

соединены с информационным входом и входом записи блока локаторов ошибок,, управляющие выходы блока определения искажений соединены с соответствующими входами третьего коммутатора и соответствующими входами первого ком- му татора и блока модифицированных сидаромоВ;. инверсный выход деинфра- Toipa ошибок и второй выход блока определения искажений через элемент HJii соединен с вторым упра зляющим буферного накопителя и вторым вх1одом блока элементов И, другой вы- хЬд дешифратора Ошибок соединен с.со- о Гветствуюш 1ми входами первого ком- му татора и блока модифицированных СИ1НД ромов.

2, Устройство по n.l, о т л и - Ч:ающееся тем, что блок локаторов ошибок выполнен в виде последо-. вательно соединенных триггера S-вход которого является входом записи, элемента И, другой вход которого являет- ся входом тактовых импул1 сов, счетчи-. ка импульсов и первого блока постоянной памяти (БШ) 5 последовательно соединенных первого коммутатора, ум ножителя; блока элементов И, блока триггеров, инверсный выход каждого иэ которых соединен с своим D-входом, второго коммутатора и первого блока оперативной памяти (БОП) последовательно соединенных регистра сдвига.j m-й выход которого соединен с первым входом, к третьего коммутатора, выход которого соединен с другим входом умножит.еля, выход которого соединен с другим информационным входом второго коммутатора, выходы счетчика импульсов через второй БПП подключены соответственно к входам Сдвиг вправо и Сдвиг влево регистра сдвига5 а через третий БПП - к адресным входам первого и третьего коммутаторов, к соответствуюгдим информационным входам которык подключен выход первого инвертора, вход которого является входом нул..вого потен- иряалад к другим входам третьего коммутатора подключены соответственно выход четвертого БПП, выход пятого

0

5

5 0

БПП и выкод второго БОП, которьш соединен с соответствуюшрм входом регистра сдвига и входами четвертого и пятого БПП, а информационный вход второго БОП соединен с информационным входом первого БОП, выходы адрес ных сигналов первого БПП соединены соответственно с адресными входами и входами записи первого и второго БОП, выходы управляюш 1Х сигналов первого БПП соединены с другим входом блока элементов И и управляющим входом второго коммутатора, выходы C первого БОП соединены соответственно с первыми га входами первого коммутатора, к вторым m входам которого подключены соответственно входы второго и третьего инверторов и (т-2) прямых выходов блока сумматоров по модулю два, а к третьим m входам первого коммутатора подключен соответственно выходы второго и третьего инверторов и (т-2) инверсных выходов блока сумматоров по модулю два, к одному из входов которого подключен вход третьего инвертора, а к другим () входам блока сумматоров по мо- . дулю два подключены последние (т-2) выходы первого БОП, второй, выход которого соединен с входом третьего инвертора, причем блок сумматоров по модулю два выполнен в виде (т-2) последовательно соединенных сумматоров по модулю два, первый и второй входы первого из которых и вторые входы других сумматоров по модулю два и прямой и инверсный выходы (т-2) сумматоров по модулю два являются соответственно входами и прямыми и инверсными выходами блока сумматоров по модулю два,, вход второго инвертора является входом нулевого потен дмала, при этом информационные входы первого и третьего коммутаторов соединены между собой и являются информационным входом, установочные входы триггера и счетчика импульсов соединены между собой и являются входом сброса а выходы первого БПП и блока триггеров соответственно управляющими и информационными выходами блока локаторов ошибок.

0

| Патент США № 4142174, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-10-30—Публикация

1987-03-24—Подача