У -.uprse, t. , л i ч 1.| юль i

VI3 8р ч8Л1 ,ь I - i i v г J Гь IIP

ПОЛ-.GObE.iO h L r/ j n j,rJ

К EJ.IS 1 ИПП jitiL 3U Л io (.(ВИРМ O ie crpoii ь i ( it ft с p ii jf / Lien ко ipC M a . ,ic ,jOB

L1 i п Л1 ,j i i i j ,e , -,oci

ep-or i. a n a «I i j -&i ei n об г ечения з любых игл1 А io-Эч ,. i , :nf |1 за сче,

РОЕьЧПЙ t I i I I г П i

чепйч 8Л1 1 Ч1 /ч vOD о ri

vOHl (J,jrjc

hd rf)/1f I ,ф /1В6ПЭ -

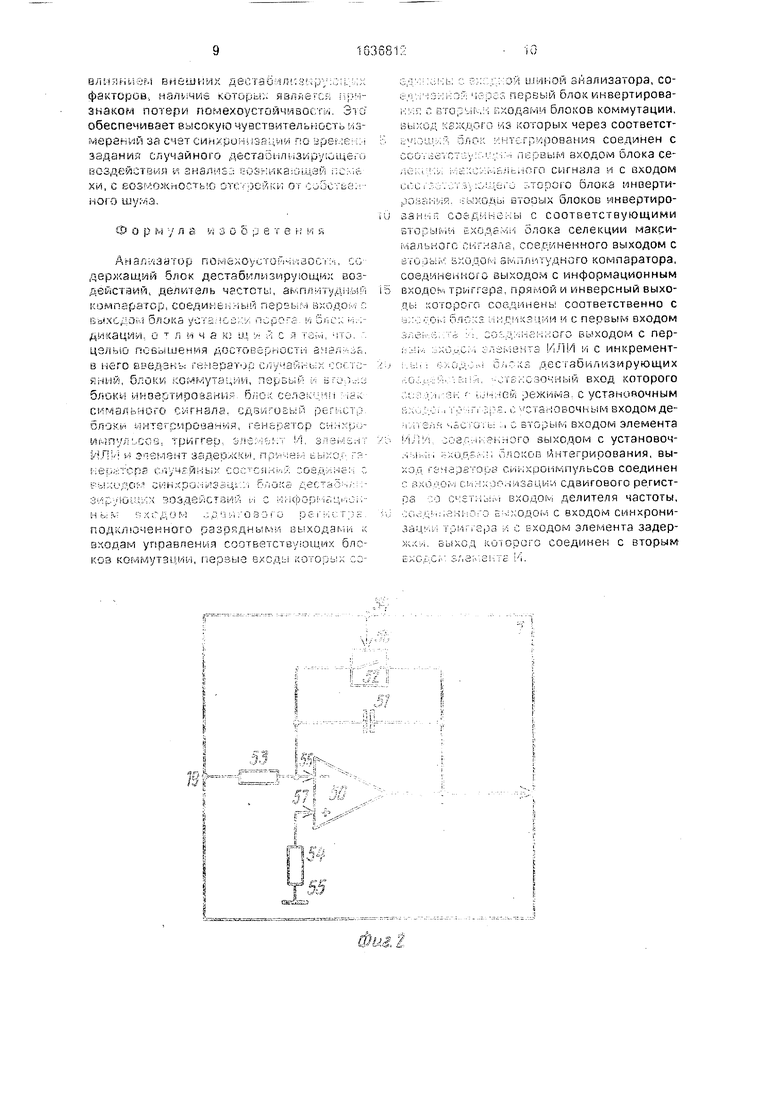

assanhsaiopa he. фи: опровани и 1 qji/tr 1 MDI, поясья ощке o Ciuiy . Анализа iop пи, хэ,. L содержи i блок i i ее ab n i де /ic i вий е1,еоаюо . г , ний сдвиговый тегисгр

Ci lHXOOl iMPyj пСОВ ПСОВ i

pOBaiiiir o/ CiCi f i

71 - n mien .juBc, i

8л i iifC&| 11 i j(o j is, ч

МЯлЬ л Г i Г i i. JM

га, 3i 1ПЛ1 i по: г

12часю( i и i C|j r

злемб 11 bi /i b i S/1JH I о эпо i I Торшер

-ЧлОГ,, 0 I j lcj li iQHPIt О -Н Ы0 BXOflt- (9 1° J fi i , H lTJi /i

possHi .F w фиП(-1аь1 lOriiibi о o i i jiirrcoa

13npqi c 7 f., /i чнрроспь1 r - пнч 101/11

, , c c e.vis

J С v, Idl IUP

I -IV.I I (( )l II 1 I

I 1 J i ЭЗ fi - X О rC - О J MtjCP n Т ,чпД i1 O lO/ 1 IJ I J 1 I It, I I

ii I

iOJ ЗЛч 8 i

О i 1 i s3 1.И i

си (i - i c- t i

11 i

i 11 т I /

11r

r Gii /i

од -О

Г|,1 З

I OO j

т--

Iv ( 3

тгсго %е м-.п т

f Г)

пестнЬ1

лизируюшчх во jOerti BWI- Uih i оО сежпг г установсчьы 5 и чод 31 гиг i усмнг оочный вход 3 пели i ел ы стгно

BO S-rJ A - /O/t3 О 1 I 3 S фЧТН Ч& ,) Ш Н.Ч

воздейг гв ой vi гп° пи с «олч J i

14 П бЛОкТ3 I г l ip ipOBfiti1

b

0

т

0

r-,

хУ

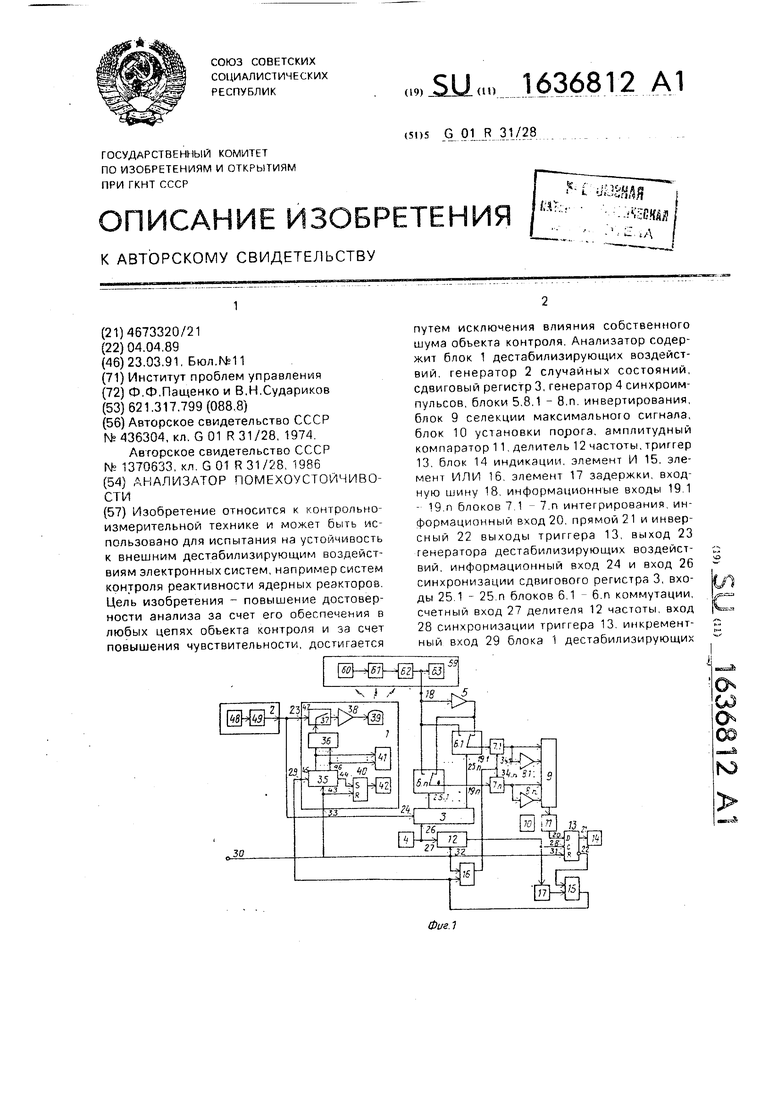

5лсч 1 цеста5ипизирующих воздейст- вий Чфи1 i) одьржиг счь1чик 35 иифроэна- Г.ОГОРЫИ преобразователь 36, ключ 37 усилитель 38 мощности блок 39 возбуждения помехи напримоп в виде электромаг- hигного изг/ атегч ipnrrep40 элемент 1 индикации амплитуды помехи и элемент 42 индикаиии режима на схеме обозначены |Экже установочный вход 43 счетчика 35, И пьреполнения скетчи1 э 35 счет- ншй вход 45 счетчика 35 рззря/iHoie выходы 6 .иксЧ Зк и вхсд 47 у авпечия j /

TGI сраи. э :/уча 1 „1У сос оаний (фи. ) „оцср || с ррп ср 48 ы ил пульсов и Tpni гер 19

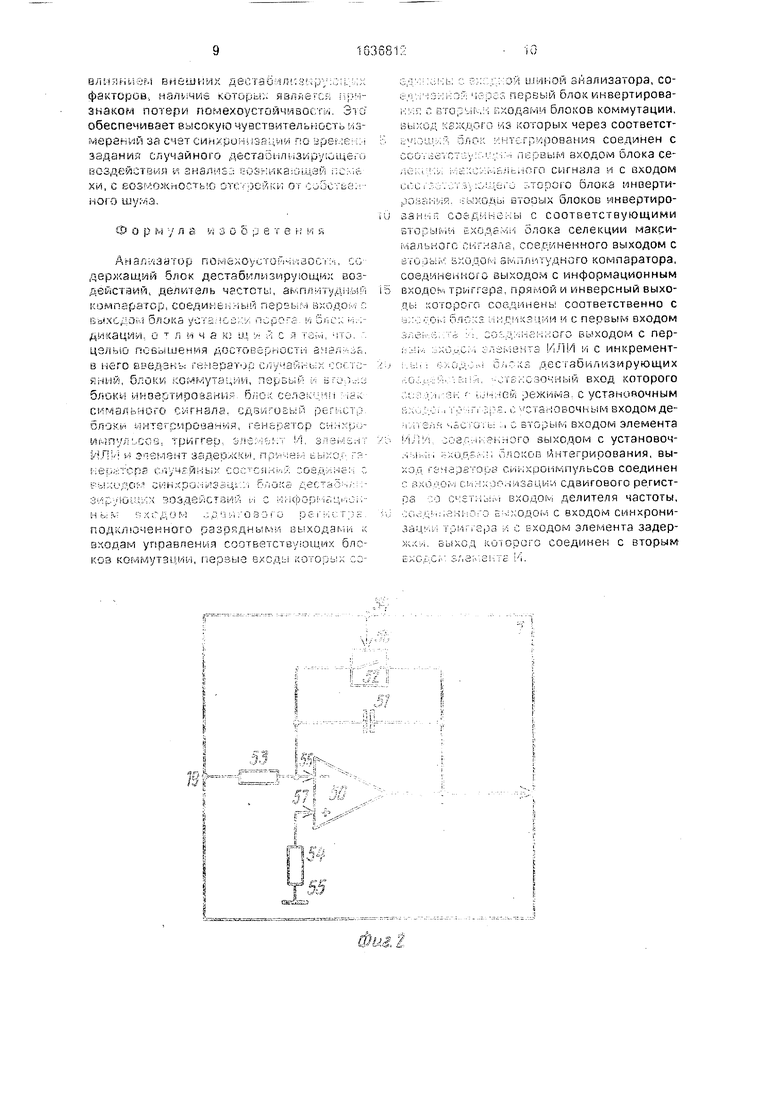

Бло i/i :те рироваьчя (фиг 2) содержит операционный усилитель 50 конденсатор 11 г:ЛгОн 5 резисторы 53 и 54 и .иину 55 мупеиого п зтс j/i&jia на схеме обозначены j vim О ппующий гтт и L скн сртир/ю i1 ii i 7 з i IN 7силитзг1я Ј0 i/i РХОД т8 /поав i гн 1 чл о i ;2

| г г jihii.nj IB соеди ена с первь ми |)одош/ блсков Ь 6 ri i- омм/1 тции а через бпо: 5 HI ертиосврн/т с вторыми входа w этих бло ов fibi NO/ кахдого из которых еоелиттен с ин орг ациониым ьходом 19 i соответствующего блока / i nmei ру.рова- u in гпдклю нс. чр о оыхолсм к одному из холпв 5 скг 9 елекц и максимальное скгналл norioi Jiif з пенно и к другому входу 3TOi о блокп че -f CODI всг ш -ощии блок 8 i HI- jpTH jjt ii и Uh ;O илика 10 установки порога uce i .L г i г пепвыг входов амплитуд -юго гомп-ip ора i I второй и зы- /о,о ко г пго ч iViifcHH соответственно с вых;ы MJ н - rcnei ии 1 ч симального curl па и н fioofiaijnoHHbiM входом 20 триггера 13 пггллюченною прямым 21 и инверсным 2 тыхопэми соответственно к бло чЧ I7 11 -i о и a vi i к первому входу злемрнгя И 15 выхот гсчеоатора 2 случайных сос-илч/и (оет/нен с входом 23 синх- ООЬИЗЭРЧИ дестабилизирующих f осцеистЕ.1/ п i-i ниюрмационным входом

24 сдзигового регистра 3, каждый из разрядных выходов которого соединен с входом 25. управления соответствующего блока 6.I коммутации. Выход генератора 4

синхроимпульсов соедине,- с сходом 26 синхронизации сдвигового регистра 3 и со счетным входом 27 делителя 12 частоты, выход которого соединен с входом Р синхронизации триггера i3 и чэрез элемент 17 задержки с вторым входом элемсн.а И 15, подключенного выходом к первому входу элемента ИЛИ 16 и к мнкрементному входу

29блока 1 дестабилизирующих воздействий. Шина 30 режима соединена с установочными входами 31 триггера 13, 32 делителя 12 частоты мЗЗ блока 1 дестабилизирующих воздействий и с вторым входог/ элемента ИЛИ ,6, выход которого соединен с установокы ии входами 34 1-34 л блоков 7 1 -7.п итегр рсвеыия

Входная шина 18 анализатора предназначена а,г)я подкую lenwa к исследуемой цепи объекта 59 контнюл которым можэ являться любая злРК рончоР с-ама, например система реп/клрзци 1 реэктив сои ядерного реактора госцс - о п шач собой последовательно гоег ч,,ь дзтчи 60 нейтронного погода, пор зл зужщи ci- литсги 61, функционала оГ преобрээозг тель 62 / ое 4стоирм ощсс /г р ,йс во 63

Анализа .ор n.iexoyc о «чнзхти работает следуюол. м образов

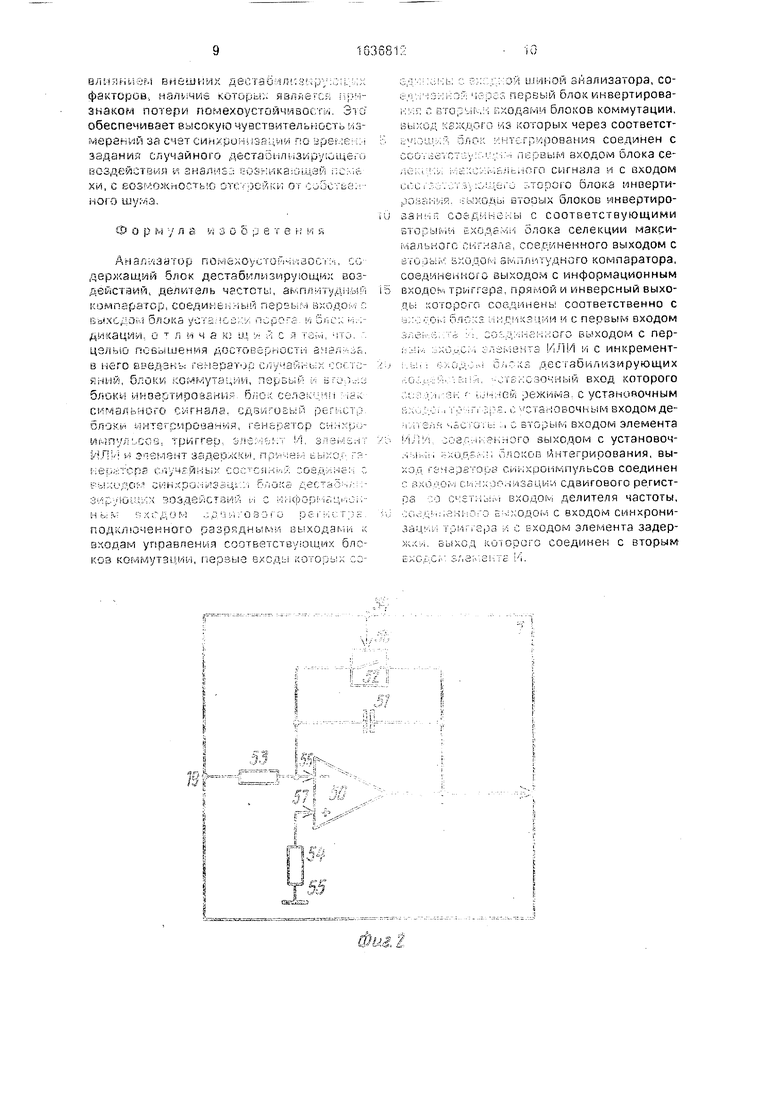

В исходном состоянии i, л ) -а и,

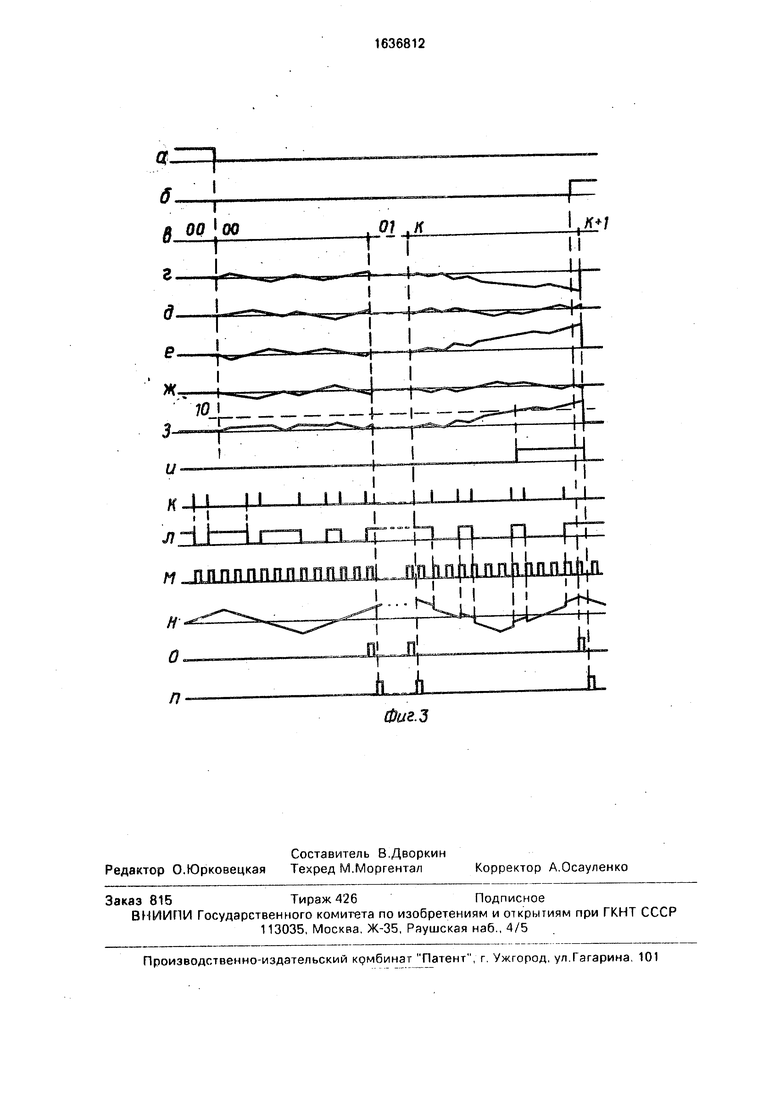

30режима прису стзует лоп чи нй 1 (фиг.За), пос упе о зя ча установочным вход 31 триггера 13 и устанавливает тл на его выходе 21 логический 0 СЈмг 36) иеиез установочный вход 33 i дес бмлизи рующих воздействий гос упающая на о од триггера 40 и устанавливающая на его выходе логический О, а также посыпающая на установочный вход 43 счетчика 35 устанавливая его разрядные выходы 46 в нулевое состояние (фиг Зв). Кроме того, сигнал с шины 30 режима поступает на установочным вход 32 делителя 12 частоты, блокируя в нем процесс счета, а также через элемент ИЛИ 16 на установочные входы 34 1 -Зл п бпоков 7.1 - 7.п интегрирования и далее {фиг ) на вход 58 управления ключа 52, что приводит к его замыканию и установлению нулевого напряжения на выходах блоков 7 1 - 7 п интегрирования (фиг Зг, д) и соответственно, на выходах блоков 8 1 - 8 п инвертирования (фиг.Зе, ж) При этом на выходе блока 9 селекции максимального сигнала также устанавливается нулевое напряжение (фиг.Зз), поступающее на вход амплитудного компаратора 11 и формирующее логический О на его выходе (фиг.Зи), который

поступает на информационный вход 20 триггера 13

Процесс измерения помехоустойчивости объекта 59 контроля начинается при установке на шине 30 режима уровня логического О (фиг За) и происходит следующим образом.

Импульсы генератора 48, возникающие в произвольный момент времени (фиг.Зк),

0 поступают на вход триггера 49, изменяя всякий раз его логическое состояние. При этом на выходе генератора 2 случайных состояний возникает бинарная последовательность случайных состояний (фиг Зл) со

5 средней скважностью q 0,5, поступающая на информационный вход 24 сдвигового регистра 3 и через вход 23 синхронизации на вход 47 управления ключа 37, переключая его в соответствующие моменты времени и

0 передавая напряжение с выхода цифроана- логового преобразователя 36 на вход усилителя 38 мощности и далее на вход блока 39 возбуждения помехи.

Импульсы синхронизации генератора 4

5 (фиг Зм) поступают на счетный вход 27 делителя 12 частоты и на вход26 синхронизации сдвигового регистра 3 периодически сдвигая вправо информацию с его входа 24. При этом на каждом из разрядных выходов сдви0 гового pei истра 3 возникает комбинация логических 1 и О, поступающая на вход 25.i упоавления соответствующего блока 6.I коммутации и поочередно соединяющая его выход с первым или вторым входами

5Сигнал с входной шины 18 (фиг.Зн), отражающий состояние диагностируемой цепи объекта 59 контроля, поступает на первые входы блоков 6 1 - 6 п коммутации непосредственно и на их вторые входы че0 рез блок 5 инвертирования При этом на выходе каждого из блоков 6 1 - 6 п коммутации образуется последовательность сигналов с входной шины 18 в прямой и инверсной формах, которая поступает на

5 информационный вход 19 i соответствующего блока 7 i интегрирования и далее через резистор 53 на инвертирующий вход 56 операционного усилителя 50, на неинвертирующий вход 57 которого через резистор 54

0 поступает нулевое напряжение с шины 55. Коммутация напряжения на информационном входе 19 i каждого из блоков 7.1 - 7.п интегрирования вызывает чередование процессов заряда и разряда конденсатора

5 51, причем в связи с тем, что, благодаря выполнению условия q 0,5 средние длительности заряда и разряда одинаковы, а сигналы на входной шине 18 и на выходе генератора 2 полностью независимы, напряжения на выходах блоков 7.1 - 7.п интегрирования (фиг.Зг, д), а также на выходах блоков 8.1 - 8.п инвертирования (фиг.Зе, ж) и на входе блока 9 селекции максимального сигнала (фиг.Зз) находятся вблизи нулевого уровня и существенно меньше напряжения на выходе блока 10, вследствие чего на выходе амплитудного компаратора 11 поддерживается логический О (фиг, Зи).

По прошествии времени, достаточного для усреднения напряжения на выходах блоков 7.1 - 7.п интегрирования на выходе делителя 12 частоты возникает импульс (фиг. Зо), поступающий на вход элемента 17 задержки и на вход 28 синхронизации триггера 13, подтверждающий логический О на его прямом выходе 21 и логическую 1 на инверсном выходе 22,- поступающую на вход элемента И 15 и поддерживающую его в открытом состоянии.

Импульс с выхода элемента 17 (фиг. Зп), задержанный на время, достаточное для переключения триггера 13, через элемент И 15 поступает на вход элемента ИЛИ 16 и далее на устчновочные входы 34.1 - 34.п блоков 7.1-7п интегрирования, возвращая их в исходное состояние и обнуляя естественное напряжение дрейфа, накопившееся на конденсаторах 51, а также через инкре- ментный вход 29 блока 1 дестабилизирующих воздействий на счетный вход 45 счетчика 35, увеличивая число на его разрядных выходах 46 (фиг.Зв) и напряжение на выходе цифроаналогового преобразователя 36, а следовательно, и уровень десталибизи- рующего воздействия, оказываемого блоком 39 возбуждения помехи на объект 59 контроля.

В дальнейшем анализатор работает аналогичным образом, периодически увеличивая амплитуду дестабилизирующих воздействий, оказываемых блоком 39 на объект 59 контроля. При этом может случиться так, что после некоторого К-ro увеличения уровень воздействий будет таким, что эффективность средств защиты объекта 59 контроля окажется недостаточной и в сигнале контролируемой в нем цепи, а следовательно, и на входной шине 18 (фиг,2м) появится случайная компонента, синхронизированная с сигналами генератора 2 случайных состояний (фиг.2л), хотя, возможно, и задержанная на некоторое время, не превышающее суммарного быстродействия блоков 60 - 62 объекта 59 контроля. В этом случае случайная компонента начинает накапливаться на одном из блоков 7. интегри- рования, например на блоке 7,1, напряжение на выходе которого начинает монотонно изменяться, например уменьшаться (фиг.Зг), а напряжение на выходе

соответствующего блока 8.I инвертирования, в данном случае на выходе блока 8.1, начинает увеличиваться (фиг.Зе), что приводит к соответствующему увеличению напряженип на выходе блока 9 селекции (фиг.Зз) и формированию логической 1 на выходе амплитудного компаратора 11 (фиг.Зи). При этом очередной импульс с выхода делителя 12 частоты (фиг.Зо) при его поступлении на

0 вход 28 синхронизации триггера устанавливает на его инверсном выходе 22 логический О, закрывающий элемент И 15 и блокирующий дальнейшее наращивание амплитуды помехи,

5На прямом выходе 21 триггера 13 устанавливается логическая 1 (фиг.Зб), поступающая на вход блока 14 индикации и возбуждающая его, что указывает на достижение предела помехозащищенности, чис0 ленное значение которого считывается по показаниям элемента 41 индикации амплитуды помехи, проградуированного непосредственно в единицах соответствующих физических величин и отражающего такой

5 уровень дестабилизирующих воздействий, при котором еще не возникает ни отказов, ни сбоев в работе, ни существенного искажения метрологических параметров объекта контроля, но уже сказывается начальное

0 влияние на режим работы его элементов, предшествующее нарушению устойчивости их функционирования

В случае, если помехоустойчивость данной цепи объекта контроля достаточно вели5 ка и ни при каком другом уровне дестабилизирующих воздействий взаимосвязи между ними и сигналами объекта не возникает, после перебора всех состояний счетчика 35 на его выходе 44 переполнения

0 возникает импульс, поступающий на второй вход триггера 40 и устанавливающий на его выходе логическую 1, что приводит к возбуждению элемента 42 индикации режима, указывающего на положительный исход ис5 пытаний, которые при необходимости могут быть повторены при подключении шины 18 к другим цепям объекта контроля или при использовании блока 39 другого, например разрядного, типа.

0Использование в анализаторе новых

элементов, а именно генератора 2 случайных состояний, блоков 6.1 - б.п коммутации, блоков 7.1 - 7 п интегрирования,блоков 5 и 8.1 - 8.п инвертирования, блока 9 селекции

5 максимального сигнала, сдвигового регистра 3, генератора 4 синхроимпульсов, триггера 13, элементов И 15 и ИЛИ 16 и элемента 17 задержки, и их связи позволяет селектировать из всей совокупности сигналов любых цепей объекта контроля сигналы, вызванные

B ll Н5, r ВиеиПЫх j&Sla |

факторов на/ii чие .от.)ри, яз/иЭч - знаком потери помехоустойчиво , Это обеспечивает в01сокую чувст витело ости , .ераипй за счет - з -i;/i , os - зацани;. случайною тесга пл-. ище j иоодей те я i ;знал 1 ,, ,. , С EOS /UXrtO Th- С ;Л1 jL vuOi j i оч nOfO UJV.O

Ф о p p, / л г i,

о О ,j о i or

АНЭ , (3d,op Г;Омч,лСУ- J dO,i rj

держащий блок / естаб лмзир/ющ л/ воздействий, ДЬ1ИгеЛЬ 4 CTCTL 3h Пл i, i ОМП-(ЗГСР COeДИ c ic -iCpSL I u, ОС I ОС ОиЭ у„ ,j

дм (аци/1 о т г h ч a v, L с i i

ЦЗЛ-ч О r BoiUeH /ifl СЬГОГСР .ОС i 5 c-,i r

а него FiUfcjbar. i о j, / т ,1 t r

f 5-QkV ..yT л Ч, IJi.oj ь ч. 1

5/ ЪК ьП Вв ОТИОО гПГ fit L СьТЭ . 1 - .

С ма/ч 1йго f, гчала „А зл ui 1 и .. i- poaaivip ,-н- - ср i. о мг.т у .v , -ригге; : -i „

JT ,1 л - i |3 -iT л - v i Гt, ( Тг 4 -ь, о iО- i IL.

- С м С J V f-,

Оv ОЗТ1- СТ1i Z-. с i „

1М -V,|Р -O l Jt I

подключенного г.а о°днь ЗЬ ХО ЧРШ входам упоавпен я ссответств, nun бл 4

КСЗ KGMrv,yT3i Ion, Г ep-UG 5/C-Ui - С

tH ohоч анализатора,со- i перс,ь и блок инвертирова- г го . и /,идам о блоков коммутации ы , о u it i,s огарых через соответст- , i , /.pOB3Hiiq соединен с

ч.ч L, г i i eD.ivi вводом блока се- ,i v го с1/1гнала 1 с сходом iiuwi. блока мнвертич. r oioodx блоков чнвертиро- зз,и сея i u ы с соответствующими ciopjii1 , i o/юкз селекции макси- пал , ч Jc (с соеслненного выходом с uiuj, uzoi 5гм днхзго компаратора, соед о-пбиьогс выходом с информационным вхоао1 TSi/n icps прямой и инверсный выхо- IL o cpcro coc iii-ienn соответственно с г, ,-,п - - г , ч- i ,и ц с пеовым входом с-ore выходом с перv. i г п I Ч И о с инкремент- ( ,v ice обигнозирующих

i.. ВХОД КОТОРОГО I, I ч .ЭеЖюмЧ С уСТЗНиРЮЧНЫМ

i CIA iDFOMiTtiM входомде- „ui i „ з i i входом элемента i a i t iv.ro выходом с установоч- Г с LC и что-риоования, вы- 1 j гч, uonN.iisTibcoB соединен , I..C ,ii-i сдвигового регистре т LCi , i схолпк делитепя частоты, ,. т одой с входом синхрони- j ji u. входом элемента задер БЫ/ЧСЧ Kuioooio соединеь с вторым

| название | год | авторы | номер документа |

|---|---|---|---|

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| Устройство для определения моментовэКСТРЕМуМОВ | 1979 |

|

SU805190A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2012 |

|

RU2498456C1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Устройство для контроля блоков управления | 1986 |

|

SU1365086A1 |

| Функциональный генератор напряжения ступенчатой формы | 1977 |

|

SU622113A1 |

| Устройство для цифрового измерения частоты медленно меняющихся процессов | 1987 |

|

SU1413542A1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

Изобретение относится к контрольно- измерительной технике и может быть использовано для испытания на устойчивость к внешним дестабилизирующим воздействиям электронных систем, например систем контроля реактивности ядерных реакторов. Цель изобретения - повышение достоверности анализа за счет его обеспечения в любых цепях объекта контроля и за счет повышения чувствительности, достигается путем исключения влияния собственного шума объекта контроля. Анализатор содержит блок 1 дестабилизирующих воздействий, генератор 2 случайных состояний, сдвиговый регистр 3, генератор 4 синхроимпульсов, блоки 5.8.1 - 8.п. инвертирования, блок 9 селекции максимального сигнала, блок 10 установки порога, амплитудный компаратор 11, делитель 12 частоты, триггер 13, блок 14 индикации, элемент И 15. элемент ИЛИ 16, элемент 17 задержки, входную шину 18, информационные входы 19 1 - 19 п блоков 7 1 - 7.п интегрирования, информационный вход 20, прямой 21 и инверсный 22 выходы триггера 13, выход 23 генератора дестабилизирующих воздействий, информационный вход 24 и вход 26 синхронизации сдвигового регистра 3, входы 25 1 - 25 п блоков 6.1 - б.п коммутации, счетный вход 27 делителя 12 частоты, вход 28 синхронизации триггера 13. инкремент- ный вход 29 блока 1 дестабилизирующих

-j- „

1Р

.t-TT. i

/

Ь

Фиг.3

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОБЛАСТИ РАБОТОСПОСОБНОСТИ ЭЛЕКТРОННЫХ СХЕМ | 1972 |

|

SU436304A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Анализатор помехоустойчивости | 1986 |

|

SU1370633A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-03-23—Публикация

1989-04-04—Подача