Изобретение относится к автоматике и вычислительной технике и может быть использовано в измерительных системах, измерительно-вычислитель- ных комплексах

Цель изобретения - повьшенне точности преобразования.

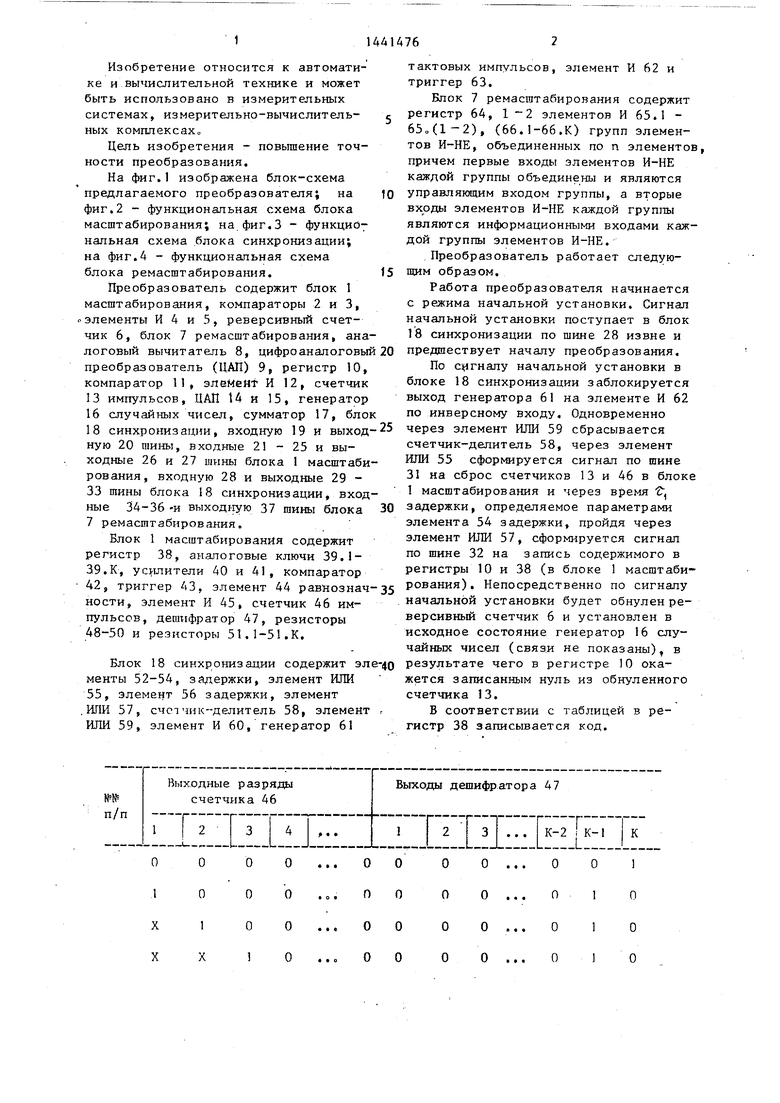

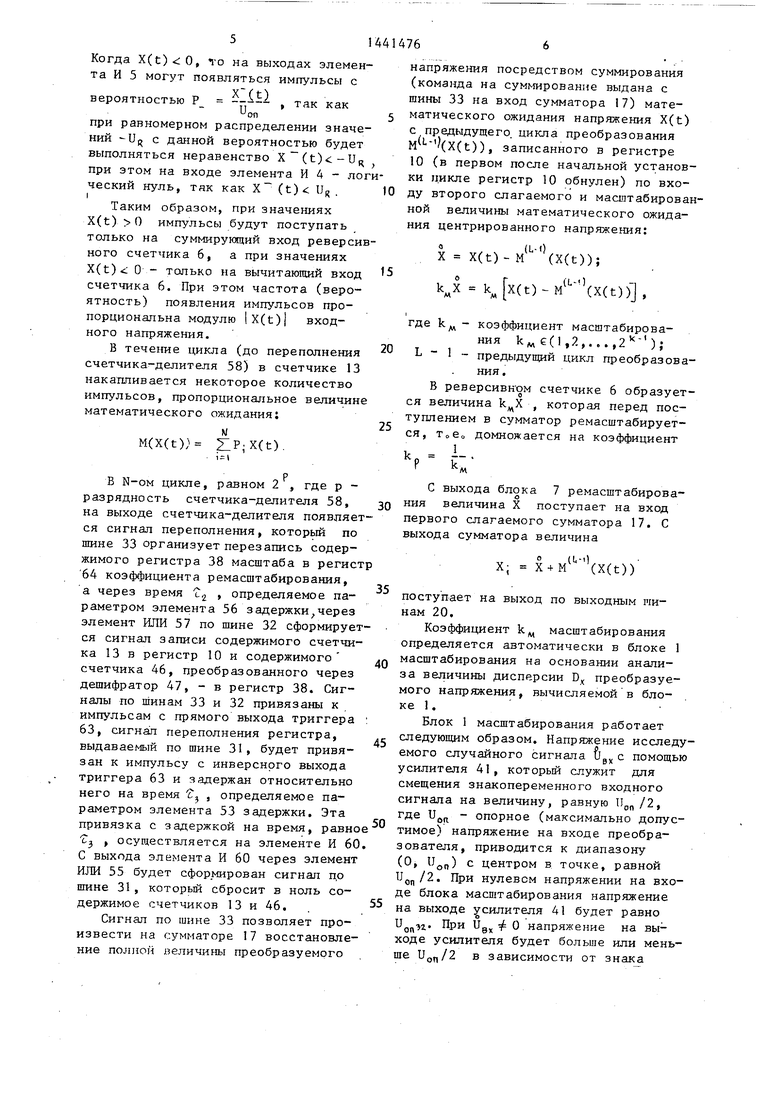

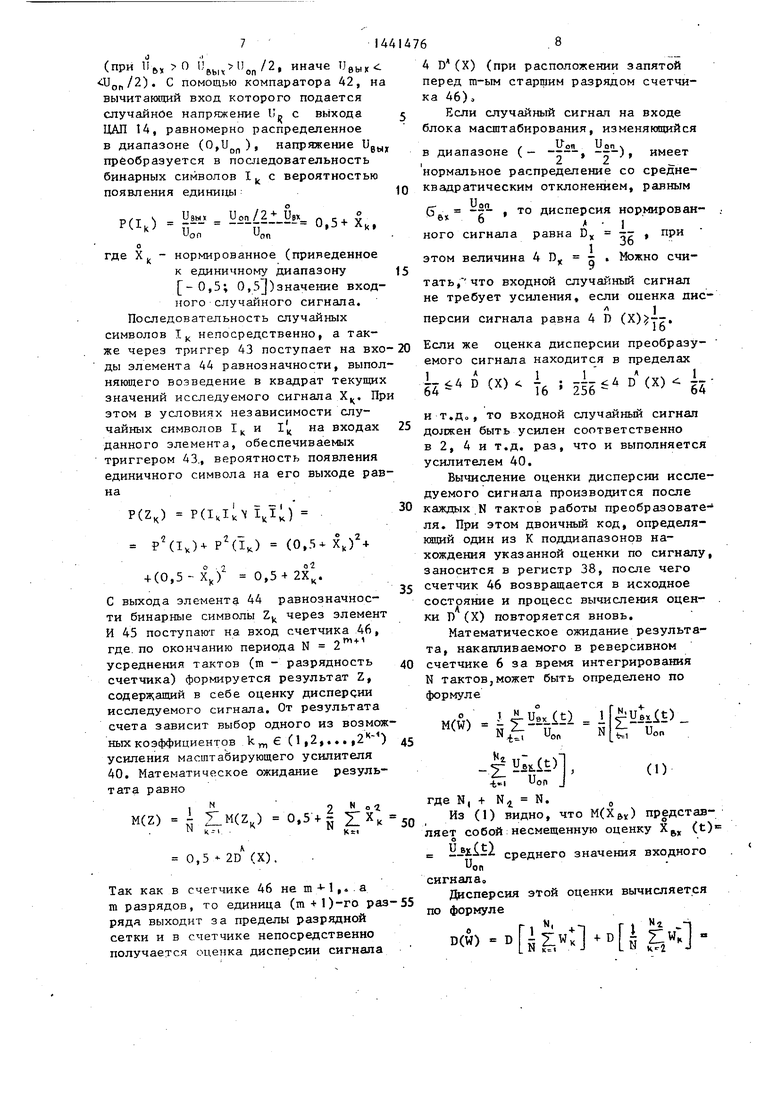

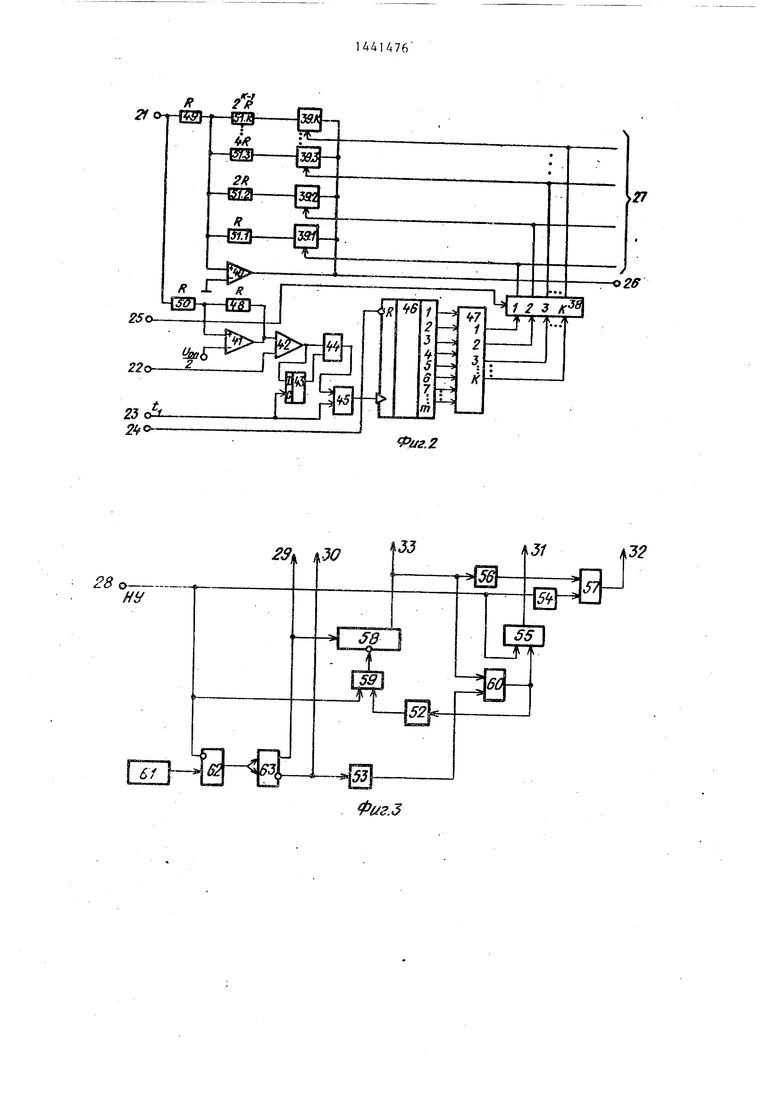

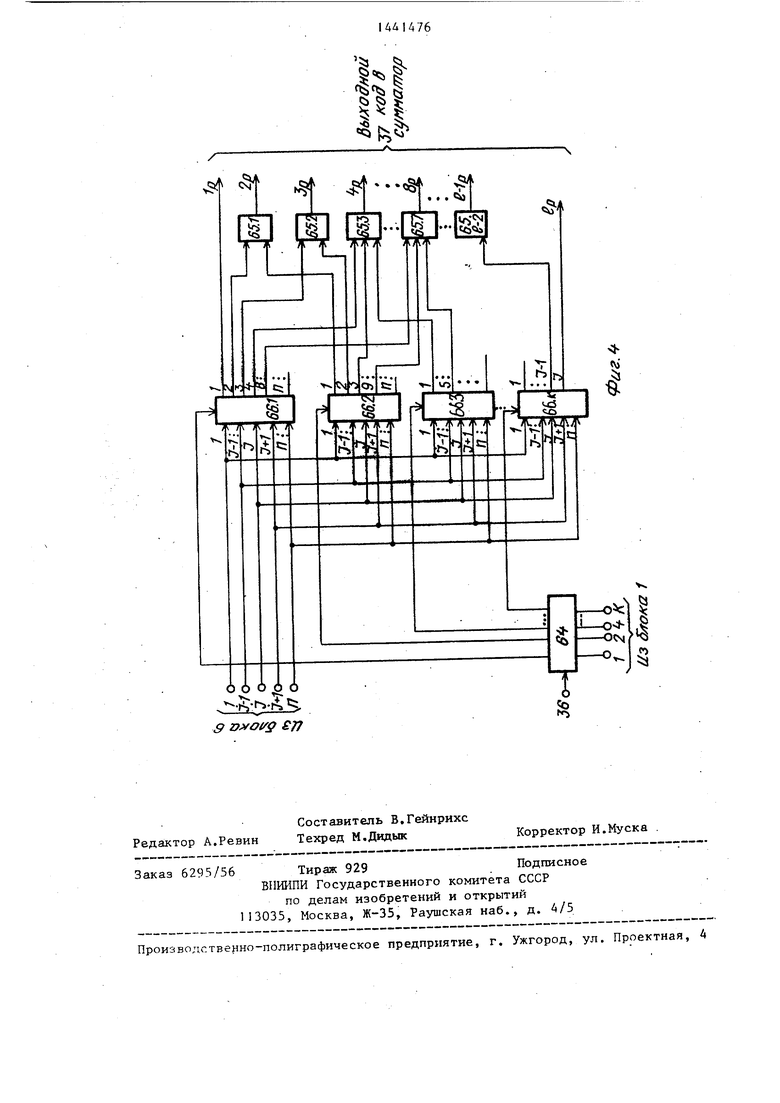

На фиг.1 изображена блок-схема предлагаемого преобразователя; на фиг,2 - функциональная схема блока масштабирования; на фиг,3 - функциональная схема блока синхронизации; на фиг,4 - функциональная схема блока ремасштабирования,

Преобразователь содержит блок 1 масштабирования, компараторы 2 и 3, элементы И 4 и 5, реверсивный счетчик 6, блок 7 ремасштабирования, аналоговый вычитатель 8, цифроаналоговый преобразователь (ДАЛ) 9, регистр 10, компаратор 1, элемент И 12, счетчик 13 импульсов, ЦАП 14 и 15, генератор 16 случайных чисел, сумматор 17, блок 18 синхронизации, входную 19 и выход ную 20 шины, входные 21 - 25 и выходные 26 н 27 шины блока 1 масштабирования, входную 28 и выходные 29 - 33 шины блока 18 синхронизации, входные 34-36 -и выходную 37 шины блока 7 ремасштабирования.

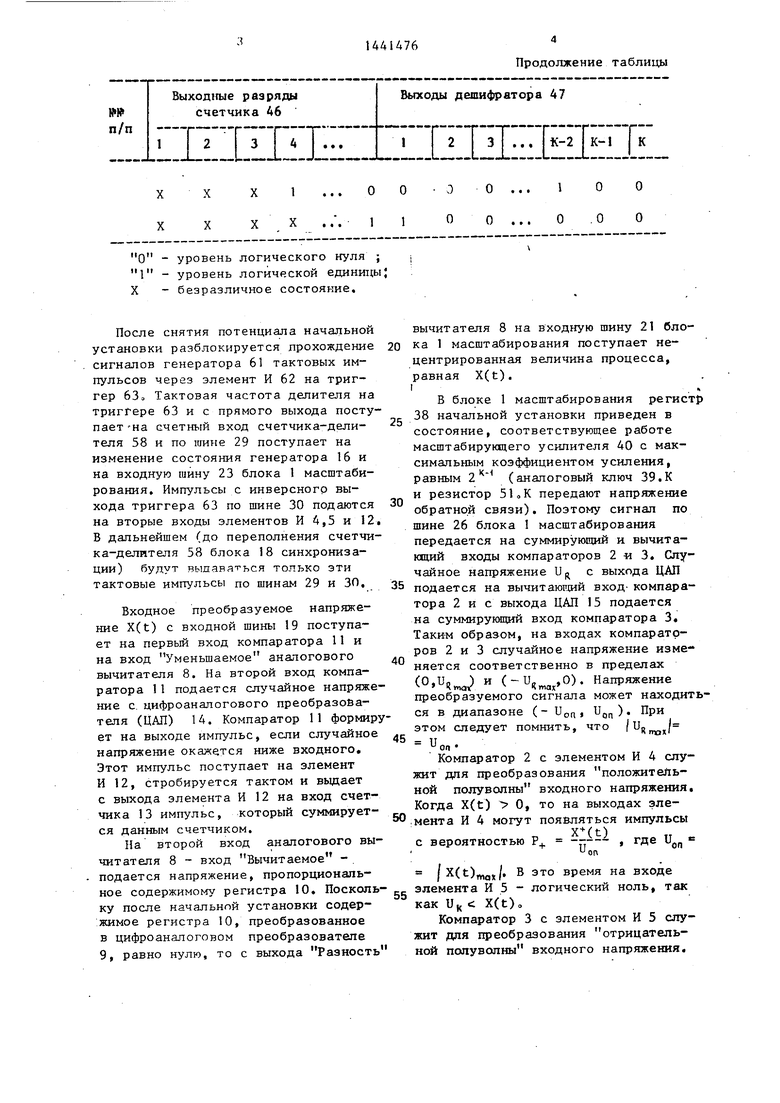

Блок 1 масштабирования содержит регистр 38, аналоговые ключи 39,1- 39,К, усршители 40 и 41 , компаратор 42, триггер 43, элемент 44 равнознач ности, элемент И 45, счетчик 46 импульсов, дешифратор 47, резисторы 48-50 и резисторы 51,1-51,К,

Блок 18 синхронизации содержит эле-( нты 52-54, задержки, элемент ИЛИ

4

0

5

0

тактовых импульсов, элемент И 62 и триггер 63,

Блок 7 ремасштабирования содержит регистр 64, 1 -2 элементов И 65,1 - 65о(1-2), (66, 1-66,К) групп элементов И-НЕ, объединенных по п элементов, причем первые входы элементов И-НЕ каждой группы объединены и являются управляющим входом группы, а вторые входы элементов И-НЕ каждой группы являются информационными входами каждой группы элементов И-НЕ,

Преобразователь работает следующим образом.

Работа преобразователя начинается с режима начальной установки. Сигнал начальной установки поступает в блок 18 синхронизации по шине 28 извне и предшествует началу преобразования.

По а гналу начальной установки в блоке 18 синхронизации заблокируется выход генератора 61 на элементе И 62 по инверсному входу. Одновременно через элемент ИЛИ 59 сбрасывается счетчик-делитель 38, через элемент ИЛИ 55 сформируется сигнал по шине 31 на сброс счетчиков 13 и 46 в блоке 1 масштабирования и через время t задержки, определяемое параметрами элемента 54 задержки, пройдя через элемент ИЛИ 57, сформируется сигнал по шине 32 на запись содержимого в регистры 10 и 38 (в блоке 1 масштаби рования), Непосредственно по сигналу начальной установки будет обнулен реверсивный счетчик 6 и установлен в исходное состояние генератор 16 случайных чисел (свяэи не показаны), в результате чего в регистре 10 окажется записанным нуль из обнуленного

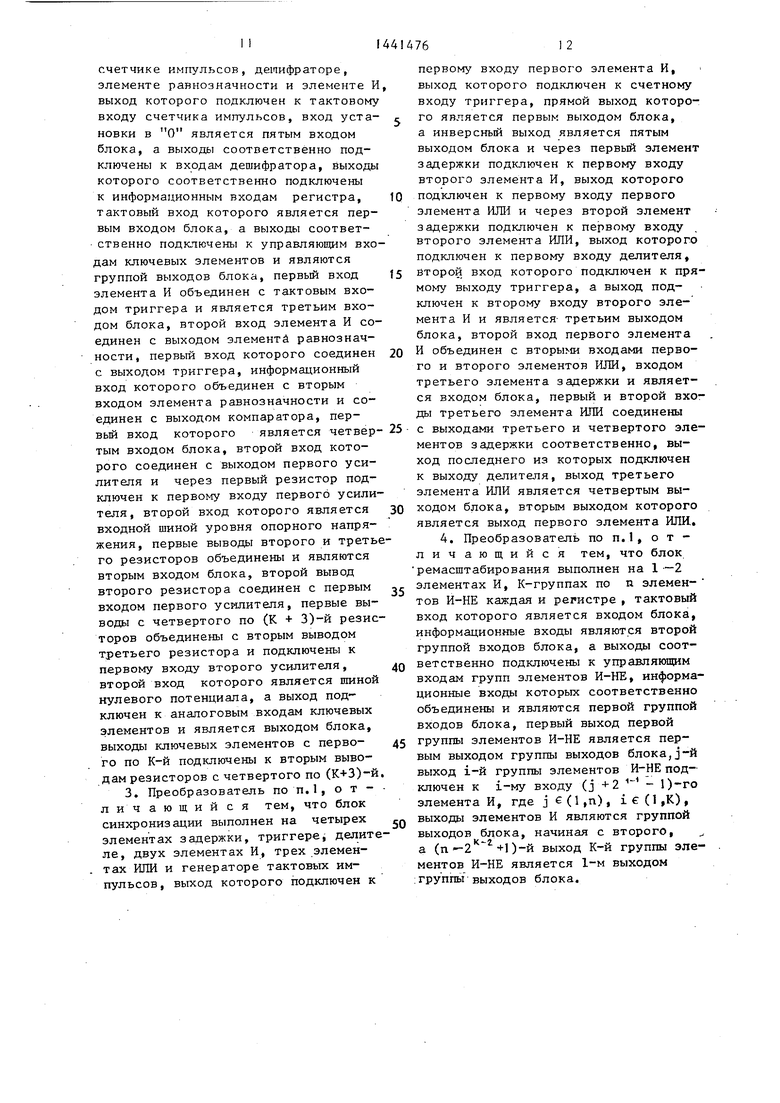

Выходные разряды счетчика 46

.L-LilLirr.::.

Продолжение таблицы Выходы дешифратора 47

I

Г 2 Т зТ.., Гк-2Тк-

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частота-код | 1987 |

|

SU1506553A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| Генератор случайного процесса | 1983 |

|

SU1111159A1 |

| Измерительное устройство | 1986 |

|

SU1365003A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1410271A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для воспроизведения функций | 1987 |

|

SU1411787A1 |

О - уровень логического нуля ; 1 - уровень логической единицы; X - безразличное состояние.

После снятия потенциала начальной установки разблокируется прохождение сигналов генератора 61 тактовых импульсов через элемент И 62 на триггер бЗо Тактовая частота делителя на триггере 63 и с прямого выхода поступает на счетный вход счетчика-дели- теля 58 и по шине 29 поступает на изменение состояния генератора 16 и на входную шину 23 блока 1 масштабирования. Импульсы с инверсного выхода триггера 63 по шине 30 подаются на вторые входы элементов И ,5 и 12 В дальнейшем (до переполнения счетчика-делителя 58 блока 18 синхронизации) будут выдаваться только эти тактовые импульсы по шинам 29 и 30.

Входное преобразуемое напряжение X(t) с входной шины 19 поступает на первьй вход компаратора 11 и на вход Уменьшаемое аналогового вычитателя 8. На второй вход компаратора 11 подается случайное напряжение с. цифроаналогового преобразователя (ЦАП) 14. Компаратор 11 формирет на выходе импульс, если случайное напряжение окажется ниже входного. Этот импульс поступает на элемент И 12, стробируется тактом и вьщает с выхода элемента И 12 на вход счетчика 13 импульс, который суммирует- ся данным счетчиком.

Па второй вход аналогового вычитателя 8 вход Вычитаемое -. подается напряжение, пропорциональное содержимому регистра 10, Посколь ку после начальной установки содержимое регистра 10, преобразованное в цифроаналоговом преобразователе 9, равно нулю, то с выхода Разность

вычитателя 8 на входную шину 21 блока 1 масштабирования поступает нецентрированная величина процесса, равная X(t). 1

В блоке 1 масштабирования регис

38 начальной установки приведен в состояние, соответствующее работе масштабирукщего усилителя 40 с максимальным коэффициентом усиления, равным (аналоговый ключ 39.К и резистор 5 К К передают напряжение обратной связи). Поэтому сигнал по шине 26 блока 1 масштабирования передается на суммирующий и вычитающий входы компараторов 2 « 3, Случайное напряжение U с выхода ЦАП подается на вычитающий вход- компаратора 2 и с выхода ЦАП 15 подается на суммирующий вход компаратора 3, Таким образом, на входах компараторов 2 и 3 случайное напряжение изменяется соответственно в пределах (0,и и (-и,0). Напряжение преобразуемого сигнала может находится в диапазоне (- Vom этом следует помнить, что / U |

и„„.

Компаратор 2 с элементом И 4 служит для преобразования положительной полуволны входного напряжения. Когда X{t) О, то на выходах элемента И 4 могут появляться импульсы

x-(t)

и.

где и,

on

с вероятностью Р

|X(t),. В это время на входе элемента И 5 - логический ноль, так как Цц е: X(t),

Компаратор 3 с элементом И 5 служит для преобразования отрицательной полуволны входного напряжения.

Когда X(t);0, то на выходах элемента И 5 могут появляться импульсы с

р . :iti

вероятностью

и.

так как

при равномерном распределении значений -и с данной вероятностью будет выполняться неравенство (t):-Ug при этом на входе элемента И 4 - лог ческий нуль, так как Х (t) Ug .

Таким образом, при значениях X(t) 0 импульсы будут поступать только на суммирующий вход реверсивного счетчика 6, а при значениях X(t); О - только на вычитающий вход счетчика 6. При этом частота (вероятность) появления импульсов пропорциональна модулю |X(t)| входного напряжения.

В тече1те цикла (до переполнения счетчика-делителя 58) в счетчике 13 накапливается некоторое количество импульсов, пропорциональное величине математического ожидания:

М

M(X(t)} PjX(t).

Р В N-OM цикле, равном 2 , где р разрядность счетчика-делителя 58, на выходе счетчика-делителя появляется сигнал переполнения, которьш по шине 33 организует перезапись содержимого регистра 38 масштаба в регист 64 коэффициента ремасштабирования, а через время , определяемое параметром элемента 56 задержки через элемент ИЛИ 57 по шине 32 сформируется сигнал записи содержимого счетчика 13 в регистр 10 и содержимого счетчика 46, преобразованного через дешифратор 47, - в регистр 38. Сигналы по шинам 33 и 32 привязаны к импульсам с прямого выхода триггера 63, сигнал переполнения регистра, выдаваемый по шине 31, будет привязан к импульсу с инверсного выхода триггера 63 и задержан относительно него на время б , определяемое параметром элемента 53 задержки. Эта привязка с задержкой на время, равно осуществляется на элементе И 60 С выхода элемента И 60 через элемент ИЛИ 55 будет сформирован сигнал п,о шине 31, которьш сбросит в ноль содержимое счетчиков 13 и 46.

Сигнал по шине 33 позволяет произвести на сумматоре 17 восстановление полной величины преобразуемого

напряжения посредством суммирования (команда на суммирование выдана с шины 33 на вход сумматора 17) математического ожидания напряжения X(t) с предыдущего, цикла преобразования (X(t)), записанного в регистре 10 (в первом после начальной установки цикле регистр 10 обнулен) по входу второго слагаемого и масштабированной величины математического ожидания центрированного напряжения:

а(L-0

X X(t)-M (X(t));

(t)(X(t)),

где kj - коэффициент масштабирования (l,2,,..,2-); L 1 - предыдущий цикл преобразования .

В реверсивном счетчике 6 образуется величина , которая перед поступлением в сумматор ремасштабирует- ся, Тое домножается на коэффициент

S г

0

С выхода блока НИН величина X

7 ремасштабирова- поступает на вход первого слагаемого сумматора 17. С выхода сумматора величина

(1.- 1,

Х4 М

(X(t))

поступает на выход по выходным шинам 20.

Коэффициент k масштабирования определяется автоматически в блоке 1 масштабирования на основании анализа величины дисперсии D,,. преобразуемого напряжения, вычисляемой в блоке 1 .

Блок 1 масштабирования работает следуюшим образом. Напряжение исследуемого случайного сигнала и с помощью усилителя 41, который служит для смещения знакопеременного входного сигнала на величину, равную , где U(j - опорное (максимально допустимое) напряжение на входе преобразователя, приводится к диапазону (О, и.,п) с центром в точке, равной . При нулевом напряжении на входе блока масштабирования напряжение на выходе усилителя 41 будет равно ех напряжение на выходе усилителя будет больше или меньше Uof,/2 в зависимости от 3Hajca

(при lift, 0 П,,, иначе Ugbtx ). С помощью компаратора 42, на вычитающий вход которого подается случайное напряжение Ь „ с выхода

ЦАП 14, равномерно распределенное в диапазоне (0,Up|), напряжение Ugyj, преобразуется в последовательность бинарных символов 1ц с вероятностью появления едини1да

р(1.5 - - 4---- ° 5

- опUnn

о

где Х - нормированное (приведенное

к единичному диапазону -0,5; 0,5)значение входного случайного сигнала. Последовательность случайных символов 1 непосредственно, а также через триггер 43 поступает на входы элемента 44 равнозначности, выполняющего возведение в квадрат текущих значений исследуемого сигнала Х. При этом в условиях независимости случайных символов 11 и I n на входах данного элемента, обеспечиваемых триггером 43., вероятность появления единичного символа на его выходе равна

p(z,) p(i,i,i,i;,)

P dx) P(IK) (0,5 X,)4 + (0,5- 0,5-b 2X.

С выхода элемента 44 равнозначности бинарные символы Z через элемент И 45 поступают на вход счетчика 46, где. по окончанию периода N 2 усреднения тактов (т - разрядность счетчика) формируется результат Z, содержащий в себе оценку дисперсии исследуемого сигнала. От результата счета зависит выбор одного из возможных коэффициентов (l|2,... ) усиления масштабирующего усилителя 40. Математическое ожидание результата равно

M(Z) i |:M(Z) 0,54 I Г

0,5 - 20 (X)..

Так как в счетчике 46 не m-t-l,..a m разрядов, то единица (га + 1)-го раз- ряда выходит за пределы разрядной сетки и в счетчике непосредственно получается оценка дисперсии сигнала

4 D(X) (при расположении запятой перед га-ым старшим разрядом счетчика 46),

Если случайный сигнап на входе блока масштабирования, изменяющийся

10

15 20 25 30

35

0 45

Uo

Uc

в диапазоне (- ---, -|-), имеет нормальное распределение со средне- квадратическим отклонением, равным

,- и 0(1

О„- - , то дисперсия нормирован- 6 1

ного сигнала равна D т , при

этом величина 4 D - . Можно считать, что входной случа1 ный сигнал не требует усиления если оценка дисл1

Персии сигнала равна 4 D (Х)--.

16

Если же оценка дисперсии преобразу- емого сигнала находится в пределах

(XX i ; -i-.)- 1

и т.До, то входной случайный сигнал должен быть усилен соответственно в 2, 4 и т.д. раз, что и выполняется усилителем 40.

Вычисление оценки дисперсии исследуемого сигнала производится после каждых N тактов работы преобразовате- ля. При этом двоичный код, определя- кнций один из К поддиапазонов нахождения указанной оценки по сигналу, заносится в регистр 38, после чего счетчик 46 возвращается в исходное состояние и процесс вычисления оцен- . ки D (X) повторяется вновь.

Математическое ожидание результата, накагшиваемого в реверсивном счетчике 6 за время интегрирования N тактов,может быть определено по формуле

м() i2:-° - - -fI:- - - N/- п„ N t; Uon

ы

-Х ukit)1

4;.|Uon J

(1)

где N, + N4 N.д

Из (1) видно, что M(XB) представляет собой несмещенную оценку Х (t)«

среднего значения входного

УОП сигналЕо

Дисперсия этой оценки вычисляется

по формуле

D(W) . Г/к

(х:.),-м(х;., м((х;,|),-«(|.„|), 5

где W ц и W j - случайные импульсы на суммирующем и вычитающем входах реверсивного счетчика 6;

M() и M(/XBX )- математическое to ожидание абсолютных значений положительных и отрицательных полуволн сигнала Xgj((t),

При симметричном распределении значений xt (t) и Хвх() имеем

15

D(W) I ) l-M(/X,j). Формула изобретения

5

o

5

0

5 о д.

40

50

которого подключен к первому входу блока масштабирования и тактовому входу регистра, входы которого соответственно соединены с выходами 1- разрядного счетчика импульсов, а выходы соответственно подключены к первой группе входов сумматора и соответствующим входам второго цифро- аналогового преобразователя, выход которого подключен к входу Вычитаемое аналогового вычитателя, вход Уменьшаемое которого соединен с входной шиной, а выход подключен к второму входу блока масштабирования, третий вход которого соединен с первым выходом блока синхронизации, четвертый вход объединен с первым входом второго компаратора и подключен к выходу первого цифроаналогового преобразователя, пятый вход соединен с вторым выходом блока синхронизации, пятый выход которого подключен к второму входу первого элемента И и первым входам второго и третьего элементов И, выходы которых соответственно подключены к входам суммирования и вычитания п-разрядного реверсивного . счетчика, выходы которого соответственно подключены к первой группе входов блока ремасштабирования, выходы которого соответственно подключены к второй группе входов сумматора, группа выходов блока масштабирования соответственно подключена к второй группе входов блока ремасштабирования, выходы генератора случай- 1ШХ чисел соответственно подключены к входам третьего цифроаналогового преобразователя, вход опорного напряжения которого является второй входной шиной уровня опорного напряже ния, а выход соединен с первым входом третьего компаратора, второй вход которого объединен с вторым Входом второго компаратора и соединен с выходом блока масштабирования, а выходы второго и третьего компараторов соответственно подключены к вторым входам второго и третьего элементов И,

счетчике импульсов, дешифраторе, элементе равнозначности и элементе И выход которого подключен к тактовому входу счетчика импульсов, вход уста- новки в О является пятым входом блока, а выходы соответственно подключены к входам дешифратора, выходы которого соответственно подключены к информационным входам регистра, тактовый вход которого является первым входом блока, а выходы соответ- ственно подключены к управляющим входам ключевых элементов и являются группой выходов блока, первый вход элемента И объединен с тактовым входом триггера и является третьим входом блока, второй вход элемента И соединен с выходом элементй равнозначности, первый вход которого соединен с выходом триггера, информационный вход которого объединен с вторым входом элемента равнозначности и соединен с выходом компаратора, первый вход которого является четвер- тым входом блока, второй вход которого соединен с выходом первого усилителя и через первый резистор подключен к первому входу первого усилителя, второй вход которого является входной шиной уровня опорного напряжения, первые выводы второго и третьего резисторов объединены и являются вторым входом блока, второй вывод второго резистора соединен с первым входом первого усилителя, первые выводы с четвертого по (К + 3)-й резисторов объединены с вторым выводом третьего резистора и подключены к первому входу второго усилителя,

второй вход которого является шиной нулевого потенциала, а выход подключен к аналоговым входам ключевых элементов и является выходом блока, выходы ключевых элементов с перво- го по К-й подключены к вторым выводам резисторов с четвертого по (К+3)й, 3. Преобразователь по п.1, о т - лич ающий ся тем, что блок синхронизации выполнен на четырех элементах задержки, триггере, делителе, двух элементах И, трех элементах ИЛИ и генераторе тактовых импульсов, выход которого подключен к

первому входу первого элемента И, выход которого подключен к счетному входу триггера, прямой выход которого является первым выходом блока, а инверсный выход является пятым выходом блока и через первьй элемент задержки подключен к первому входу второго элемента И, выход которого подключен к первому входу первого элемента ИЛИ и через второй элемент задержки подключен к первому входу второго элемента ИЛИ, выход которого подключен к первому входу делителя, Второй вход которого подключен к прямому выходу триггера, а выход подключен к второму входу второго элемента И и является- третьим выходом блока, второй вход первого элемента И объединен с вторы ш входами первого и второго элементов ИЛИ, входом третьего элемента задержки и является входом блока, первый и второй входы третьего элемента ИЛИ соединены с выходами третьего и четвертого элементов задержки соответственно, выход последнего из которых подключен к выходу делителя, выход третьего элемента ИЛИ является четвертым выходом блока, вторым выходом которого является выход первого элемента ИЛИ.. 4, Преобразователь по п.1, о т - личающийся тем, что блок ремасштабирования выполнен на 1-2 элементах И, К-группах по п элемен- тон И-НЕ каждая и регистре , тактовый вход которого является входом блока, информационные входы являются второй группой входов блока, а выходы соответственно подключены к управляющим входам групп элементов И-НЕ, информационные входы которых соответственно объединены и являются первой группой входов блока, первый выход первой группы элементов И-НЕ является первым выходом группы выходов блока,j-и выход i-й группы элементов И-НЕ подключен к i-му входу (J +2 - 1)-го элемента И, где j е (1 ,п) , i е(1,К), выходы элементов И являются группой выходов блока, начиная с второго, а (п--2 +1 )-й выход К-й группы элементов И-НЕ является 1-м выходом : группы выходов блока.

R/ /

о-Н

Iff

-Ш1--Д-

2K

f5o

O

77

-of/f

U2,Z

UJ

Фиг.З

О О О О

.

ff ($ П

5з Ч

14

| Гладкий В„Сс Вероятностные вычислительные модели | |||

| М„: Наука, 1973j с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Вероятностный преобразователь аналог-код | 1984 |

|

SU1229950A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-30—Публикация

1987-04-13—Подача