Изобретение относится к вычислительной технике и может быть использовано, например, для связи вычислительных машин с объектами управления, моделирования радиолокационных сигналов, построения управляемых ли- .ний задержки.

Цель изобретения - расширение функциональных возможностей за счет обеспечения прямого и обратного многоканального преобразования.

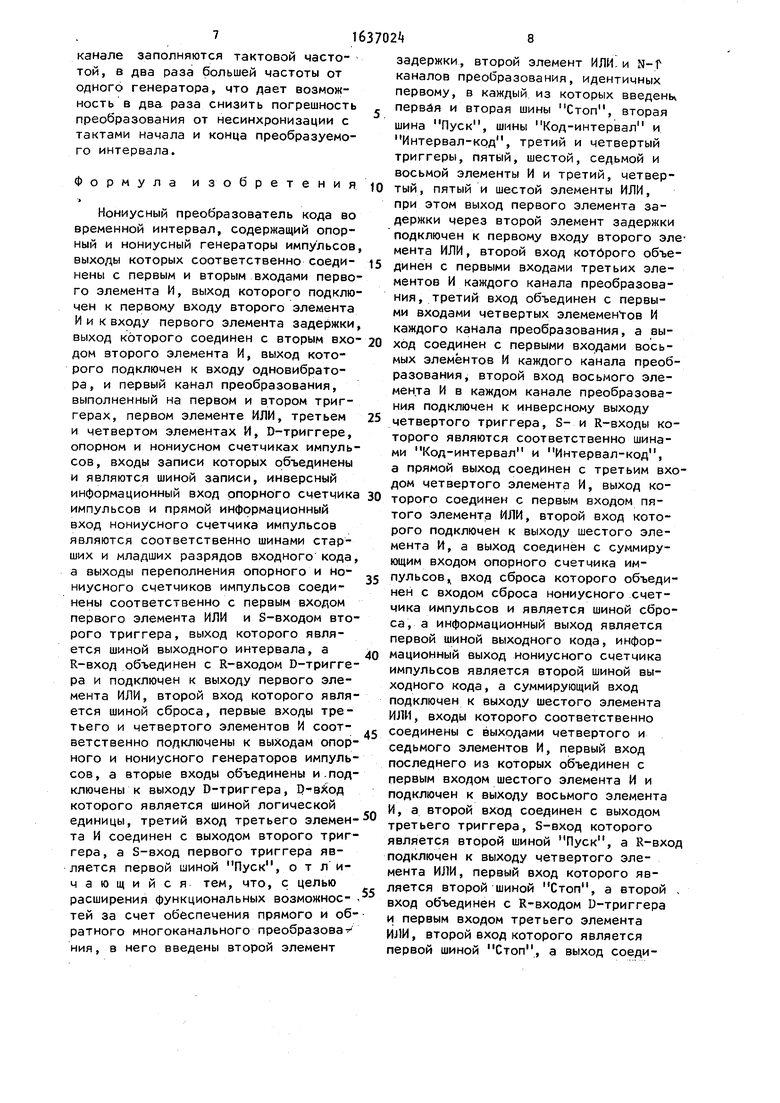

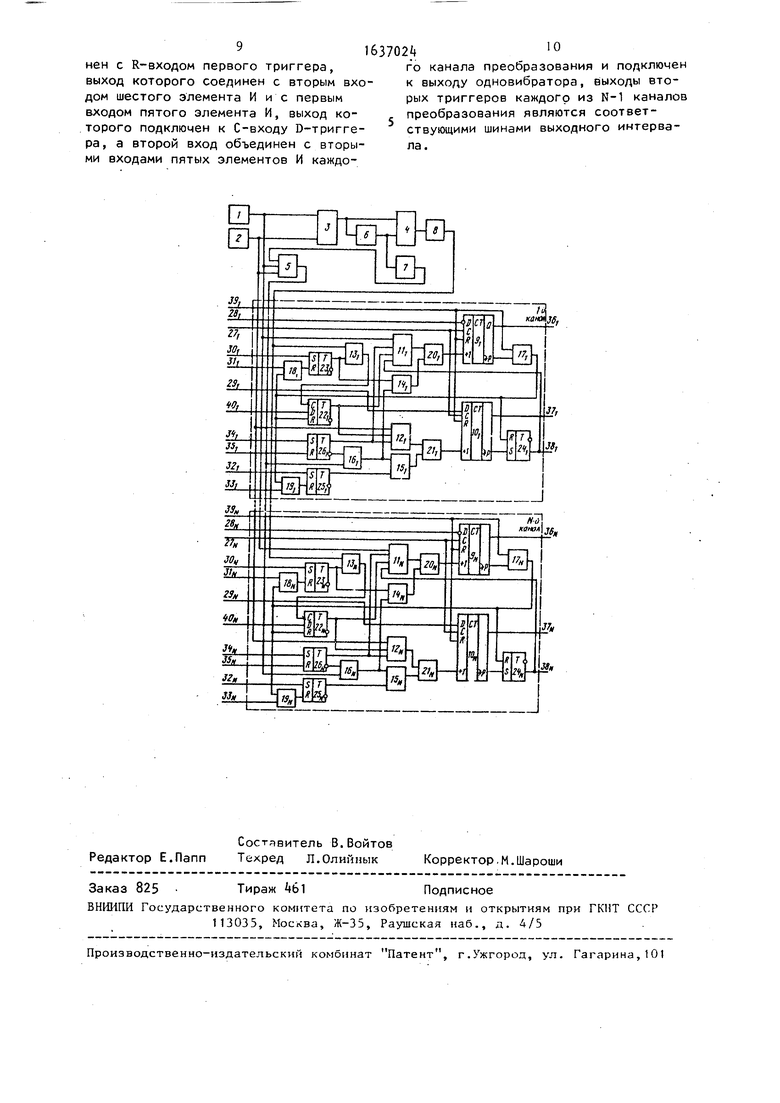

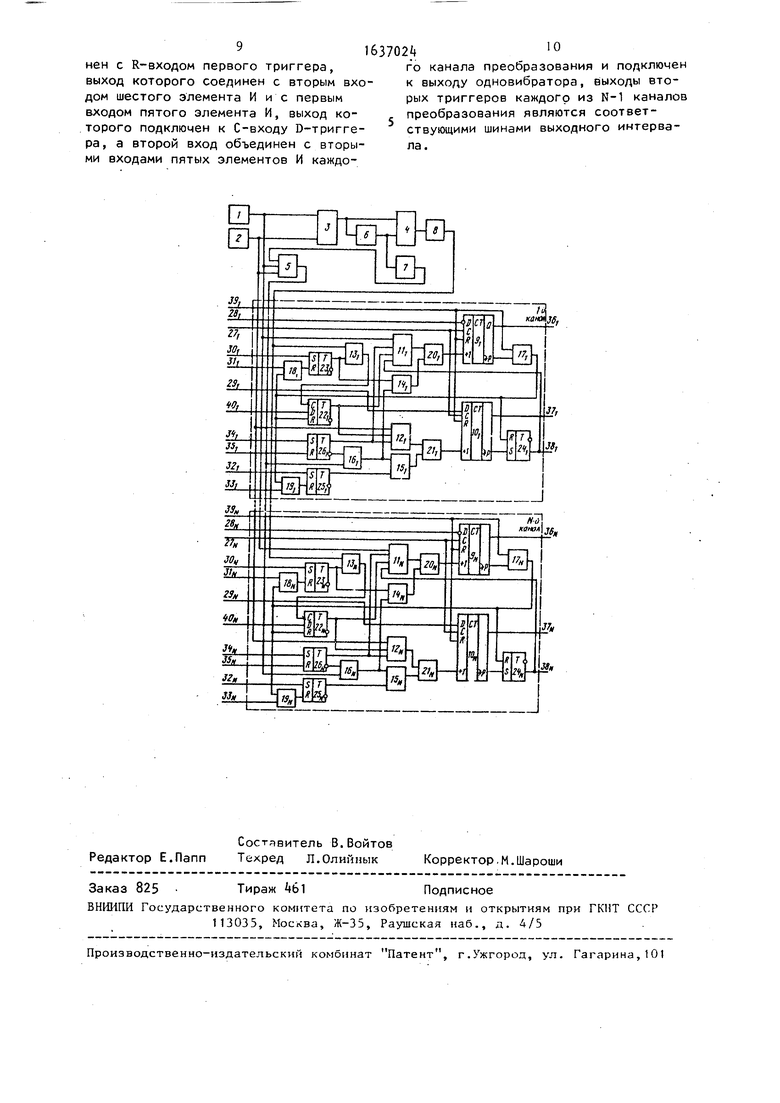

На чертеже представлена структурная схема нониусного преобразователя кода во временной интервал.

Преобразователь содержит опорный и нониусный генераторы 1 и 2 импульсов, элементы И 3 и 4, элемент ИЛИ 5, элементы 6 и 7 задержки, одновибра- тор 8 и N каналов преобразования, каждый из которых содержит опорный счетчик 9 импульсов, нониусный счетчик 10 импульсов, элементы И 11-i

16, элементы ИЛИ 17-21, D-триггер 22 триггеры 23-26, шину 27 запуска, шины 28 и 29 старших и младших разрядов входного кода, первую шину 30 Пуск, первую шину 31 Стоп, вторую шину 32 Пуск, вторую шину 33 Стоп, шину 3 Код-интервал, шину 35 Интервал-код, первую и вторую шины 36 и 37 выходного кода, шину 38 выходного интервала, шину 39 сброса и шину 0 логической едини цыс

Преобразователь работает следующим образом.

Предварительно в каждом канале устанавливается соответствующий режи преобразования. При подаче сигнала на шину 3k Код-интервал в данном канале осуществляется преобразова- ние кода в интервал с нониусной интерполяцией. При подаче сигнала на шину 35 Интервал-код в данном канале осуществляется преобразование интервала в код по двум подканалам.

Рассмотрим работу любого канала в режиме нониусного преобразования кода в интервал. Сигналом по шине 39 сброса соответствующего канала осуществляется обнуление счетчиков 9 и 10 и триггеров 22-25. Работа каждого канала осуществляется независимо дру от друга подачей соответствующих сигналов режима на шины 3 и 35о Затем по шине 27 записи соответствую- щего канала осуществляется запись инверсного кода старших разрядов в счетчик 9 с шины 28 и прямого кода младших разрядов в счетчик 10 с шины 29. Для начала преобразования подается сигнал на первую шину 30 Пуск. При этом устанавливается в единичное состояние триггер 23 и открываются элементы И 13 и Й„ От триггера 26 поступает разрешающий сигнал на элементы И 11 и 12, так как установлен режим преобразования Код-интервал с помощью установки в единичное состояние триггера 26 по шине Код-интервал 3. Генерато- ры 1 и 2 работают постоянно. Выявление полного совпадения их фаз осуществляется с помощью элементов И 3 и k, элемента 6 задержки и одновиб- ратора 8о Неполные совпадения фаз генераторов 1 и 2 имеют меньшую длительность, чем полные, поэтому с помщью элемента 6 задержки и элемента И Ь неполные совпадения блокируются и

фиксируются только полные совпадения фаз. Для этого сигнал с выхода элемента И 3 поступает на первый вход элемента И k непосредственно и на его вход - через элемент 6 задержки. Величина задержки в линии 6 задержки выбирается меньшей длительности полного совпадения фаз и большей длительности предшествующего полному совпадению фаз. Такой выбор величины задержки в элементе 6 задержки возможен так как длительности неполных совпадений фаз генераторов 1 и 2 до полного совпадения нарастают дискретно с дискретностью, определяемой выбором частот нониусного и опорного генераторов 1 и 2. При указанном выборе времени задержки элемент И 4 будет срабатывать только при полном совпадении фаз генераторов 1 и 2. При любой длительности сигнала на выходе элемента И k одновибратор 8 формирует сигнал постоянной длительности, который заканчивается после окончания импульсов генераторов 1 и 2, при которых происходит полное совпадение их необходимо для того, чтобы исключить из подсчета нониусными и опорными счетчиками 9 и 10 остатки импульсов при неполном совпадении фаз генераторов 1 и 2.

Импульсы полного совпадения фаз генераторов 1 и 2 от одновибратора 8 поступают через открытые элементы И 13 на инверсные С-входы D-тригге- ров 22. После окончания сигнала от одновибратора 8 устанавливаются в единичное состояние D-триггеры 22 тех каналов, на которые поданы сигналы с первой шины При установке в единичное состояние D-триггера 22 соответствующий канал начинает осуществлять нониусное преобразование кода во временной интервал. При этом открывается элемент И 12 и подготавливается к открыванию элемент И 11„ Импульсы нониусного генератора 2 проходят через открытый элемент И 12 и начинают суммироваться на нониусном счетчике 10, при переполнении которого устанавливается в единичное состояние триггер 2k и формируется начало выходного интервала соответствующего канала на шине 38 выходного интервала о Одновременно с этим открывается элемент И 11 и импульсы опорного генератора 1 начинают суммироваться на опорном счетчике 9, при переполнении которого устанавливаются в нулевое состояние триггеры 22-25 | и формируется конец выходного интервала соответствующего канала на шине 38о На этом цикл преобразования в соответствующем канале заканчивается0 Результат преобразования по i-му каналу определяется формулой -с(

t,; To NoiH-hT;(N4waKcrNHl)(

где Т0 - период опорного генератора; N . - число импульсов, фиксируемое опорным счетчиком 9 1-го канала до момента его перепол- .нения; h - основание системы счисления

в i-м канале;

0(; - число младших разрядов вход«- ного кода, выделяемое для нониусной интерполяции в i-м канале;

К.... - максимальное число импульсов, фиксируемое нониусным счетчиком 10 1-го канала; число импульсов, фиксируемое нониусным счетчиком 10 1-го канала до момента его переполнения „

Ч МО КС/

NHi

совпадения генераторов 1 и 2. При любом совпадении импульсов от генераторов 1 и 2 на элементе ИЛИ 5 они превращаются в один растянутый импульс и поэтому, чтобы при этом сформировать два импульса, на элементе 7 задержки любой импульс совпадения задерживается и суммируется на элементе ИЛИ 5. Суммарное время задержки на элементах 6 и 7 задержки выбирается большим длительности импульсов от генераторов 1 и 2, но меньшим периодов генераторов 1 и 2.

Таким образом, на элементе ИЛИ 5 всегда формируется суммарная частота импульсов от генераторов 1 и 2. Импульсы от элемента ИЛИ 5 через открытый элемент И 16 поступают на элементы

И 14 и 15. В каждом канале в данном режиме осуществляется преобразование интервала в код по двум подканалам. Для запуска первого подканала после сброса счетчика 9 подается сигнал

5 пуска на первую шину Пуск 30„ При этом устанавливается в единичное состояние триггер 23 и открывается элемент И 1А. Импульсы с выхода элемента И 16 через элемент ИЛИ 20 посту

| название | год | авторы | номер документа |

|---|---|---|---|

| Нониусный преобразователь кода во временной интервал | 1985 |

|

SU1320903A1 |

| Нониусный преобразователь кода во временной интервал | 1987 |

|

SU1425836A1 |

| Нониусный преобразователь кода во временной интервал | 1985 |

|

SU1275770A1 |

| Преобразователь кода во временной интервал | 1983 |

|

SU1162050A1 |

| Устройство для измерения интервалов времени | 1981 |

|

SU970302A1 |

| ИНТЕРПОЛИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ЦИФРОВОЙ КОД | 2014 |

|

RU2561999C1 |

| Преобразователь время-код | 1991 |

|

SU1785073A1 |

| Нониусный преобразователь кода во временной интервал | 1985 |

|

SU1287291A1 |

| Преобразователь код-временной интервал | 1983 |

|

SU1088115A1 |

| Устройство для измерения интервалов времени | 1985 |

|

SU1324008A1 |

Изобретение относится к вычислительной технике и может быть использовано, например, для связи вычислительных машин с объектами управления, моделирования радиолокационных сигналов, построения управляемых линий задержки. Цель изобретения - расширение функциональных возможностей. Преобразователь содержит опорный и нониусный генераторы импульсов, два элемента И, элемент ИЛИ, два элемента задержки, одновибратор и N каналов преобразования, каждый из которых содержит опорный и нониусный счетчики импульсов, шесть элементов И, пять элементов ИЛИ, D- триггер, четыре триггера, шину запуска, шины старших и младших разрядов входного кода, две шины Пуск, две шины Стоп, шины Код-интервал и Интервал-код, две шины выходного кода, шину выходного интервала, шину сброса и шину логической единицы Поставленная цель достигается за счет обеспечения прямого и обратного многоканального нониусного преобразования. Причем в режиме многоканального преобразования кода в интервал используется нониусная интерполяция, а в режиме преобразования интервал в код точность преобразования повышена за счет использования для заполнения счетчиков суммарной частоты опорного и нониусного генераторов. В обоих режимах независимо от числа каналов используются всего два автогенератора. 1 ил. S (Л оь w. j i

Таким образом, в режиме преобразо- 30 лают на суммирующий вход счетчика вания кода в интервал преобразова- 9. По окончании преобразуемого интель позволяет независимо и параллельно во времени преобразовывать нониусным способом код во временной интервал по N каналам При этом независимо от числа каналов используются всего два автогенератора - опорный 1 и нониусный 2, которые имеют более высокую стабильность частоты, чем запускаемые генераторы.

В преобразователе в любом канале возможна установка режима преобразования интервала в код. Для этого в соответствующем канале подается сигнал на шину 35 Интервал-код, который устанавливает триггер 26 в нулевое состояние. При этом закрываются элементы И 11 и 12 и открывается элемент И 1б„ В данном режиме использу35

тервала подается сигнал на первую шину Стоп 31 через элемент ИЛИ 18, триггер 23 устанавливается в нулевое состояние, закрывается элемент И И и на счетчике 9 формируется код, соответствующий входному интервалу пер вого подканала. Код со счетчика 9 поступает на первую шину 36 выходно- 40 го кода. Для запуска второго подкана ла после сброса в О счетчика 10 по дается сигнал на вторую шину Пуск 32. Триггер 25 устанавливается в еди ничное состояние, открывается элемен И 15 и импульсы от элемента И 16 поступают через элемент И 15 и элемент ИЛИ 21 на суммирующий вход счетчика 10. По окончании преобразуемого интервала подается сигнал на вторую ши

45

ется дополнительно элемент 7 задержки 50 ну 33 Стоп, через элемент ИЛИ.19 и элемент ИЛИ 5. Элемент ИЛИ 5 сумми- устанавливается в нулевое состояние рует частоты импульсов от генераторов триггер 25, закрывается элемент И 15 1 и 2. Для того, чтобы на элементе ИЛИ 5 формировалась полная сумма ча55

стот от генераторов 1 и 2, в суммарную импульсную последовательность на выходе элемента ИЛИ 5 добавляются импульсы с элемента 7 задержки, который формирует задержанные импульсы

и на счетчике 10 формируется код, соответствующий входному интервалу второго подканала. Код со счетчика 10 поступает на вторую шину 37 выход ного кода.

В режиме преобразования интервала в код счетчики каждого подканала в

5

тервала подается сигнал на первую шину Стоп 31 через элемент ИЛИ 18, триггер 23 устанавливается в нулевое состояние, закрывается элемент И И, и на счетчике 9 формируется код, соответствующий входному интервалу первого подканала. Код со счетчика 9 поступает на первую шину 36 выходно- 0 го кода. Для запуска второго подканала после сброса в О счетчика 10 подается сигнал на вторую шину Пуск 32. Триггер 25 устанавливается в единичное состояние, открывается элемент И 15 и импульсы от элемента И 16 поступают через элемент И 15 и элемент ИЛИ 21 на суммирующий вход счетчика 10. По окончании преобразуемого интервала подается сигнал на вторую ши5

ну 33 Стоп, через элемент ИЛИ.19 устанавливается в нулевое состояние триггер 25, закрывается элемент И 15

и на счетчике 10 формируется код, соответствующий входному интервалу второго подканала. Код со счетчика 10 поступает на вторую шину 37 выход ного кода.

В режиме преобразования интервала в код счетчики каждого подканала в

канале заполняются тактовой частотой, в два раза большей частоты от одного генератора, что дает возможность в два раза снизить погрешность преобразования от несинхронизации с тактами начала и конца преобразуемого интервала.

задержки, второй элемент ИЛИ и Nканалов преобразования, идентичны первому, в каждый из которых введ первая и вторая шины Стоп, втор шина Пуск, шины Код-интервал Интервал-код, третий и четверты триггеры, пятый, шестой, седьмой восьмой элементы И и третий, четв

Формула изобретения ю тый, пятый и шестой элементы ИЛИ

Нониусный преобразователь кода во временной интервал, содержащий опорный и нониусный генераторы импульсов, выходы которых соответственно соединены с первым и вторым входами первого элемента И, выход которого подключен к первому входу второго элемента И и к входу первого элемента задержки,

при этом выход первого элемента задержки через второй элемент задержки подключен к первому входу второго элемента ИЛИ, второй вход которого объе- 15 динен с первыми входами третьих элементов И каждого канала преобразования, третий вход объединен с первыми входами четвертых элемементов И каждого канала преобразования, а вывыход которого соединен с вторым вхо- 20 ход соединен с первыми входами вось- дом второго элемента И, выход кото- мых элементов И каждого канала преобразования, второй вход восьмого элемента И в каждом канале преобразования подключен к инверсному выходу 25 четвертого триггера, S- и R-входы которого являются соответственно шинами Код-интервал и Интервал-код, а прямой выход соединен с третьим входом четвертого элемента И, выход ко- информационный вход опорного счетчика 30 торого соединен с первым входом пя- импульсов и прямой информационный того элемента ИЛИ, второй вход которого подключен к входу одновибрато- ра, и первый канал преобразования, выполненный на первом и втором герах, первом элементе ИЛИ, третьем и четвертом элементах И, D-триггере, опорном и нониусном счетчиках импульсов, входы записи которых объединены и являются шиной записи, инверсный

вход нониусного счетчика импульсов являются соответственно шинами старших и младших разрядов входного кода, а выходы переполнения опорного и нониусного счетчиков импульсов соединены соответственно с первым входом первого элемента ИЛИ и S-входом второго триггера, выход которого является шиной выходного интервала, а R-вход объединен с R-входом D-тригге- ра и подключен к выходу первого элемента ИЛИ, второй вход которого является шиной сброса, первые входы третьего и четвертого элементов И соответственно подключены к выходам опорного и нониусного генераторов импульсов, а вторые входы объединены и.подключены к выходу D-триггера, D-вХод которого является шиной логической единицы, третий вход третьего элемен та И соединен с выходом второго триггера, а S-вход первого триггера является первой шиной Пуск, отличающийся тем, что, с целью расширения функциональных возможное тей за счет обеспечения прямого и обратного многоканального преобразовав ния, в него введены второй элемент

. 55

рого подключен к выходу шестого элемента И, а выход соединен с суммирующим входом опорного счетчика им35 пульсовц вход сброса которого объединен с входом сброса нониусного счетчика импульсов и является шиной сброса, а информационный выход является первой шиной выходного кода, инфор40 мационный выход нониусного счетчика импульсов является второй шиной выходного кода, а суммирующий вход подключен к выходу шестого элемента ИЛИ, входы которого соответственно соединены с выходами четвертого и седьмого элементов И, первый вход последнего из которых объединен с первым входом шестого элемента И и подключен к выходу восьмого элемента И, а второй вход соединен с выходом третьего триггера, S-вход которого является второй шиной Пуск, а R-вход подключен к выходу четвертого элемента ИЛИ, первый вход которого является второй шиной Стоп, а второй , вход объединен с R-входом П-триггера и первым входом третьего элемента ИЛИ, второй вход которого является первой шиной Стоп, а выход соеди45

.50

задержки, второй элемент ИЛИ и Nf каналов преобразования, идентичных первому, в каждый из которых введена первая и вторая шины Стоп, вторая шина Пуск, шины Код-интервал и Интервал-код, третий и четвертый триггеры, пятый, шестой, седьмой и восьмой элементы И и третий, четвертый, пятый и шестой элементы ИЛИ

при этом выход первого элемента задержки через второй элемент задержки подключен к первому входу второго элемента ИЛИ, второй вход которого объе- динен с первыми входами третьих элементов И каждого канала преобразования, третий вход объединен с первыми входами четвертых элемементов И каждого канала преобразования, а выход соединен с первыми входами вось- мых элементов И каждого канала преобразования, второй вход восьмого элемента И в каждом канале преобразования подключен к инверсному выходу четвертого триггера, S- и R-входы которого являются соответственно шинами Код-интервал и Интервал-код, а прямой выход соединен с третьим входом четвертого элемента И, выход ко- торого соединен с первым входом пя- того элемента ИЛИ, второй вход кото

5

рого подключен к выходу шестого элемента И, а выход соединен с суммирующим входом опорного счетчика им35 пульсовц вход сброса которого объединен с входом сброса нониусного счетчика импульсов и является шиной сброса, а информационный выход является первой шиной выходного кода, инфор40 мационный выход нониусного счетчика импульсов является второй шиной выходного кода, а суммирующий вход подключен к выходу шестого элемента ИЛИ, входы которого соответственно соединены с выходами четвертого и седьмого элементов И, первый вход последнего из которых объединен с первым входом шестого элемента И и подключен к выходу восьмого элемента И, а второй вход соединен с выходом третьего триггера, S-вход которого является второй шиной Пуск, а R-вход подключен к выходу четвертого элемента ИЛИ, первый вход которого является второй шиной Стоп, а второй , вход объединен с R-входом П-триггера и первым входом третьего элемента ИЛИ, второй вход которого является первой шиной Стоп, а выход соеди5

0

нен с R-входом первого триггера, выход которого соединен с вторым входом шестого элемента И и с первым входом пятого элемента И, выход которого подключен к С-входу D-тригге- ра, а второй вход объединен с вторыми входами пятых элементов И каждо163702410

го канала преобразования и подключен к выходу одновибратора, выходы вторых триггеров каждого из N-1 каналов преобразования являются соответ- 5 ствующими шинами выходного интервала.

| ПРИБОР К ЧУЛОЧНЫМ МАШИНАМ "ШТАНДАРТ" ДЛЯ ОБРАЗОВАНИЯ ДВОЙНОЙ ПОДОШВЫ И ПЯТКИ | 1925 |

|

SU3417A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Нониусный преобразователь кода во временной интервал | 1985 |

|

SU1275770A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1991-03-23—Публикация

1988-07-15—Подача