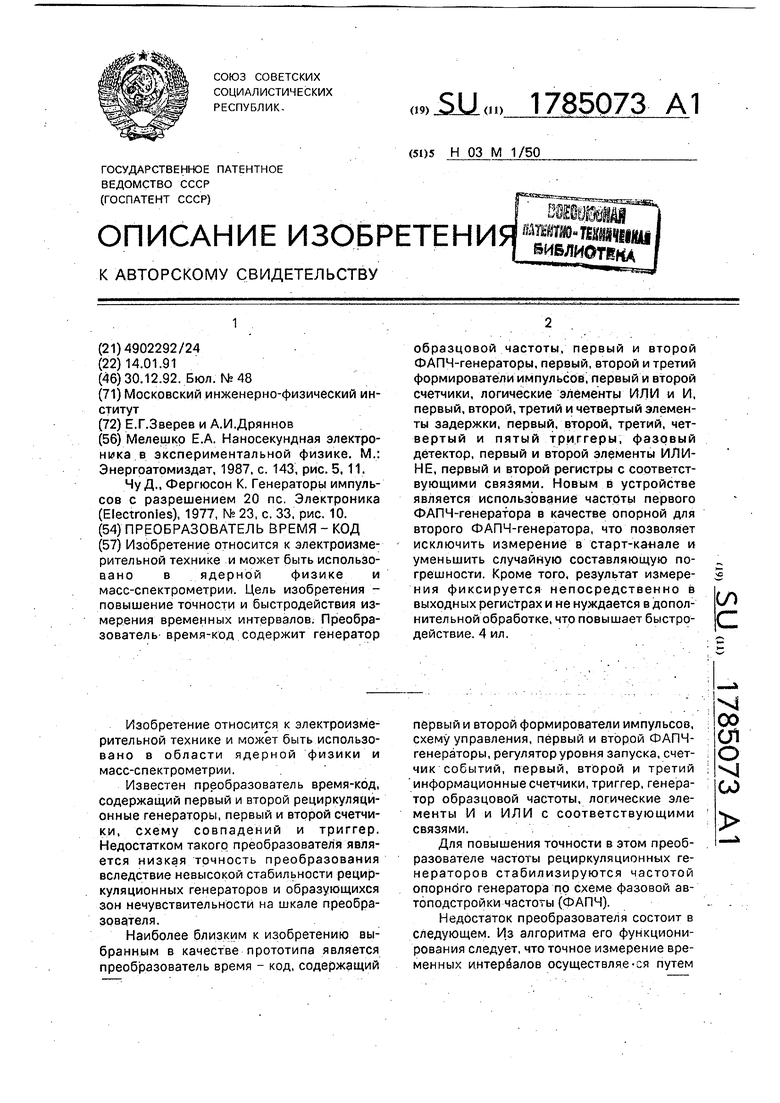

Изобретение относится к электроизмерительной технике и может быть использовано в области ядерной физики и масс-спектрометрии.

Известен преобразователь время-код, содержащий первый и второй рециркуляционные генераторы, первый и второй счетчики, схему совпадений и триггер. Недостатком такого преобразователя является низкая точность преобразования вследствие невысокой стабильности рециркуляционных генераторов и образующихся зон нечувствительности на шкале преобразователя.

Наиболее близким к изобретению выбранным в качестве прототипа является преобразователь время - код, содержащий

первый и второй формирователи импульсов, схему управления, первый и второй ФАПЧ- генераторы, регулятор уровня запуска, счетчик событий, первый, второй и третий информационные счетчики, триггер, генератор образцовой частоты, логические элементы И и ИЛИ с соответствующими связями.

Для повышения точности в этом преобразователе частоты рециркуляционных генераторов стабилизируются частотой опорного генератора по схеме фазовой автоподстройки частоты (ФАПЧ).

Недостаток преобразователя состоит в следующем. Из алгоритма его функционирования следует, что точное измерение временных интервалов осуществляв-ся путем

vi

00 01 О

XI со

совпадений импульсов опорной частоты с импульбами генераторов опорной частоты (ФАПЧ-генераторов) в старт- и стоп-кана- лах. Эти совпадения фиксируются при помощи триггера совпадения. При этом возможна ситуация, когда перепады на С- и D-входах триггера совпадения формируются практически одновременно и информация на его выходах определяется триггерными шумами.Поскольку это происходит дважды, то при измерении одного и того же временного интервала результаты могут отличаться не на один, а на два шага квантования. Кроме того, для окончательной выдачи результатов измерения необходимо дополнительно осуществлять операцию вычитания, что снижает быстродействие преобразователя. Это снижение быстродействия особенно ощутимо при оперативном накоплении информации в условиях проведения физических экспериментов.

. Целью изобретения является повышение точности и быстродействия преобразователя.

Поставленная цель достигается тем, что в преобразователь, содержащий генератор образцовой частоты, выход которбго подключен к первому входу первого генератора опорной частоты, первый формирователь импульсов, вход которого является входом старт-импульсов, второй формирователь импульсов, вход которого является входом стоп-импульсов, второй генератор опорной частоты, первый и второй счетчики, введены логические элементы ИЛИ и И. первый, второй, третий и четвертый элементы задержки, первый, второй, третий, четвертый и пятый триггеры, фазовый детектор, первый и второй инверторы, третий формирователь импульсов, первый и второй логические элементы ИЛИ-НЕ, первый и второй регистры, причем прямой выход первого формирователя соединен соответственно со вторым входом первого генератора опорной частоты и первым входом элемента ИЛИ, а инверсный выход объединен соответственно с третьим входом первого генератора опорной частоты и первым входом элемента И и через первый элемент задержки подключен ко входу управления первого счетчика, прямой выход второго формирователя объединен со вторым входом элемента ИЛИ, S- и D-зходами соответственно первого и второго триггеров, первым входом фазового детектора и через второй элемент задержки - Обходом второго триггера, а инверсный выход - с вторым входом элемента И и через третий элемент задержки подключен ко входу управления второго счетчика, вход первого инвертора подключен к выходу первого

генератора опорной частоты, а выход объединен с С-входами первого счетчика и второго триггера, первым входом второго генератора опорной частоты, вторым входом фазового детектора и через четвертый элемент задержки подключен к С-входу третьего триггера, выходы элементов ИЛИ и И соединены соответственно с вторым и третьим входами второго генератора опор0 ной частоты, выход которого через инвертор подключен ктретьему входу фазового детектора, С-входом второго счетчика, четвертого и пятого триггеров и входу третьего формирователя, выход которого соединен с D-вхо5 дом третьего триггера, выход которого подключен к четвертому входу фазового детектора, пятый вход которого объединен со- ответственно с инверсным выходом первого, S-входом третьего и R-входами чет0 вертого и пятого триггеров, а шестой вход соединен с прямым выходом первого триггера, первый и второй входы первого логического элемента ИЛИ-НЕ соединены соответственно с первым и вторым выхода5 ми фазового детектора, а третий вход подключен к прямому выходу пятого триггера, выход логического элемента ИЛИ-НЕ соединен с S-входом второго триггера, первый и второй входы второго логического элемен0 та ИЛИ-НЕ соединены соответственно с третьим выходом фазового детектора и инверсным выходом пятого триггера, D-вход которого объединен с выходом четвертого триггера, D-вход которого подключен к ши5 не с нулевым потенциалом, информационные входы первого и второго счетчиков подключены к шине с потенциалом, соответствующему уровню логической единицы, инверсный выход второго триггера подключен

0 к С-входу первого регистра, информационные входы которого соединены с соответствующими информационными выходами первого счетчика, С-вход второго регистра подключен к выходу второго элемента ИЛИ5 НЕ и С-входу первого триггера, а информационные входы соединены с соответствующими информационными выходами второго счетчика, информационный выход старшего разряда которого соединен

0 с седьмым входом фазового детектора. Кроме того, фазовый детектор содержит первый триггер, С-вход которого соединен с вторым входом фазового детектора, а R-вход соединен с R-входом второго триггера и выходом

5 элемента ИЛИ-НЕ, первый вход которого объединен с инверсным выходом первого триггера и первым входом первого логического элемента ИЛИ, а второй вход - с инверсным выходом второго триггера и первым входом второго элемента ИЛИ, С- и

D-входы второго триггера подключены соответственно к третьему и шестому входам фазового детектора, вторые входы первого и второго элементов ИЛИ соединены с инверсными выходами второго и первого элементов ИЛИ соответственно, первый вход третьего элемента ИЛИ соединен с прямым выходом первого элемента ИЛИ и первым выходом фазового детектора, а второй вход - с вторым входом первого элемента ИЛИ и вторым выходом фазового детектора, первый и второй входы второго элемента ИЛИ- НЕ подключены соответственно к прямому выходу и второму входу второго элемента ИЛИ, прямой и инверсный выходы третьего элемента ИЛИ подключены соответственно к третьему выходу фазового детектора и S- входу третьего триггера, С-вход которого подключен к седьмому входу фазового детектора, четвертый триггер, С-вход которого соединен с выходом второго элемента ИЛ И- НЕ, D- и R-входы которого подключены соответственно к шине с нулевым потенциалом и четвертому входу фазового детектора, третий элемент ИЛИ-НЕ, первый, второй и третий входы которого соединены соответственно с выходами третьего и четвертого триггеров и первому входу фазового детектора, четвертый вход объединен с R-входом третьего триггера и пятым входом фазового детектора, а выход - с D-входом первого триггера.

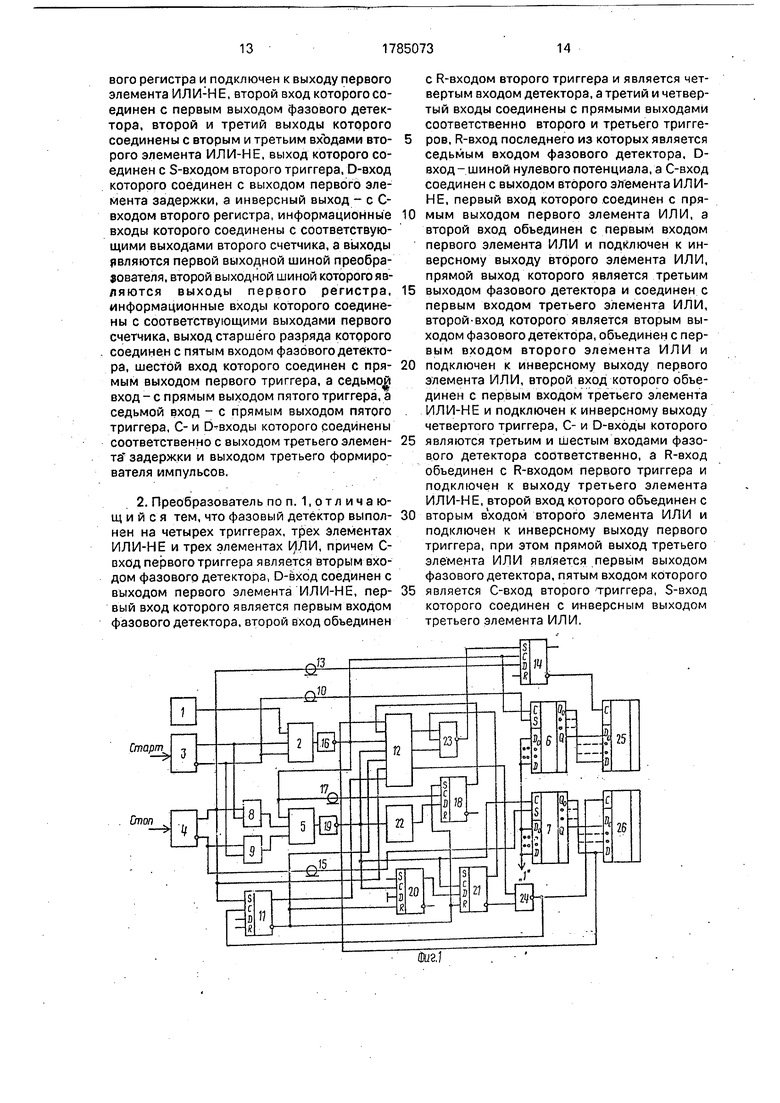

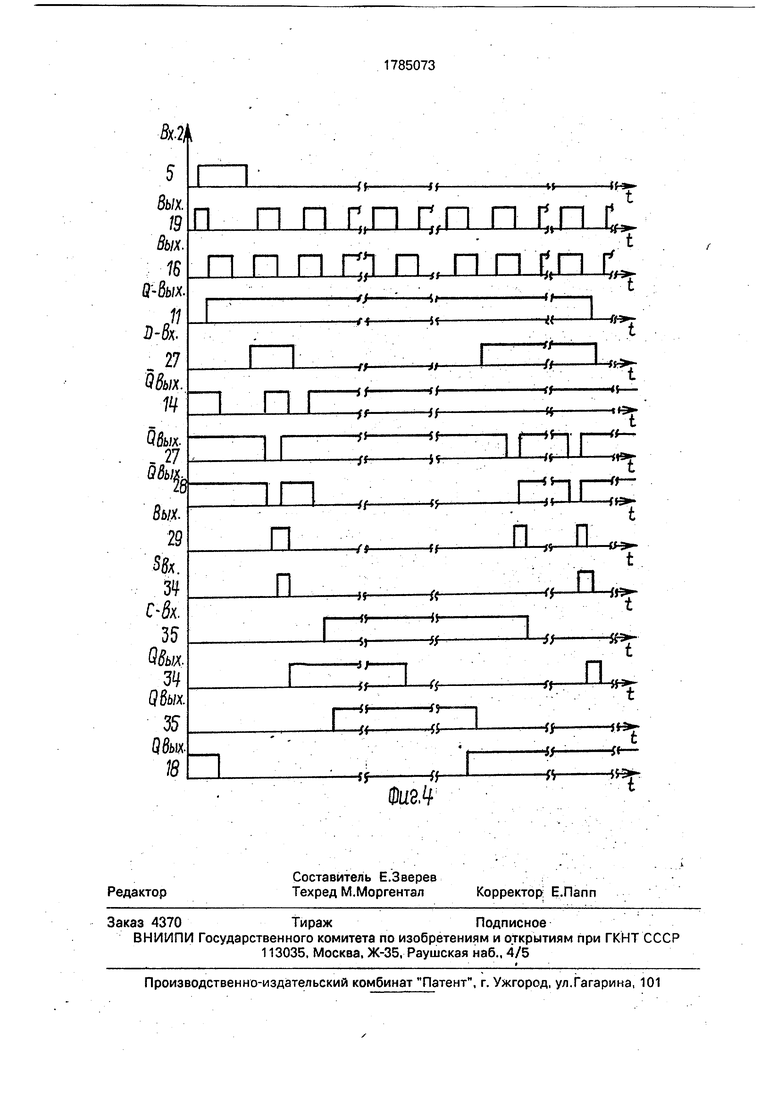

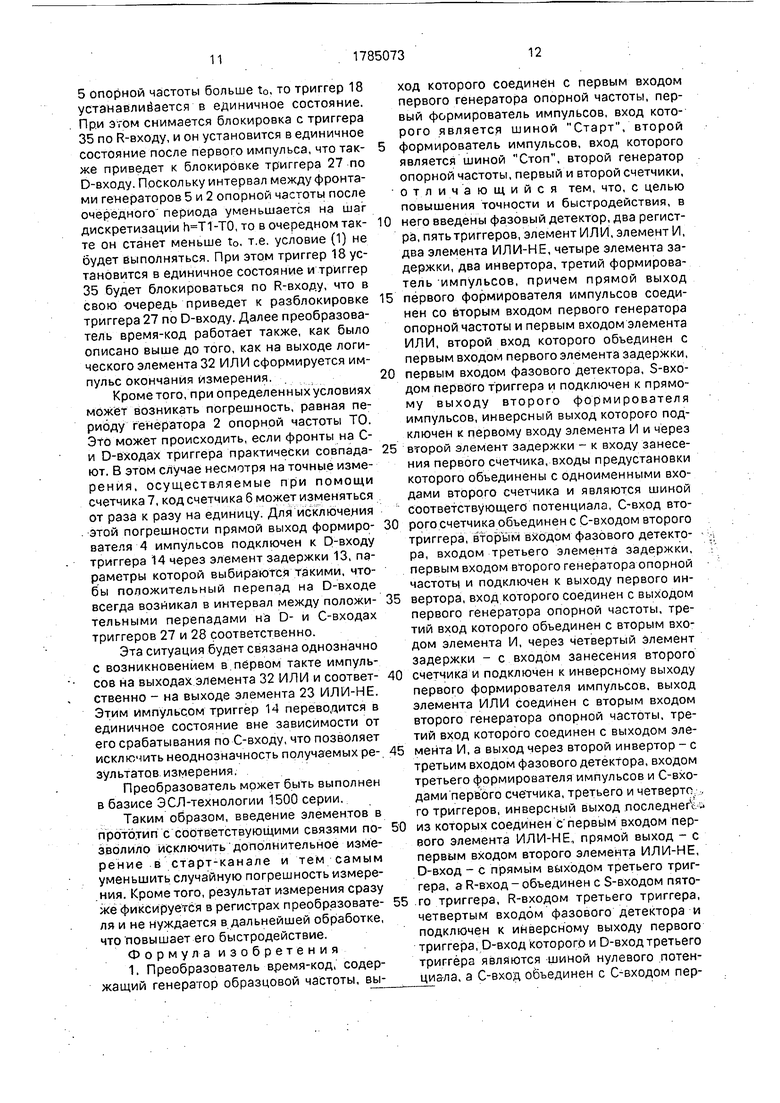

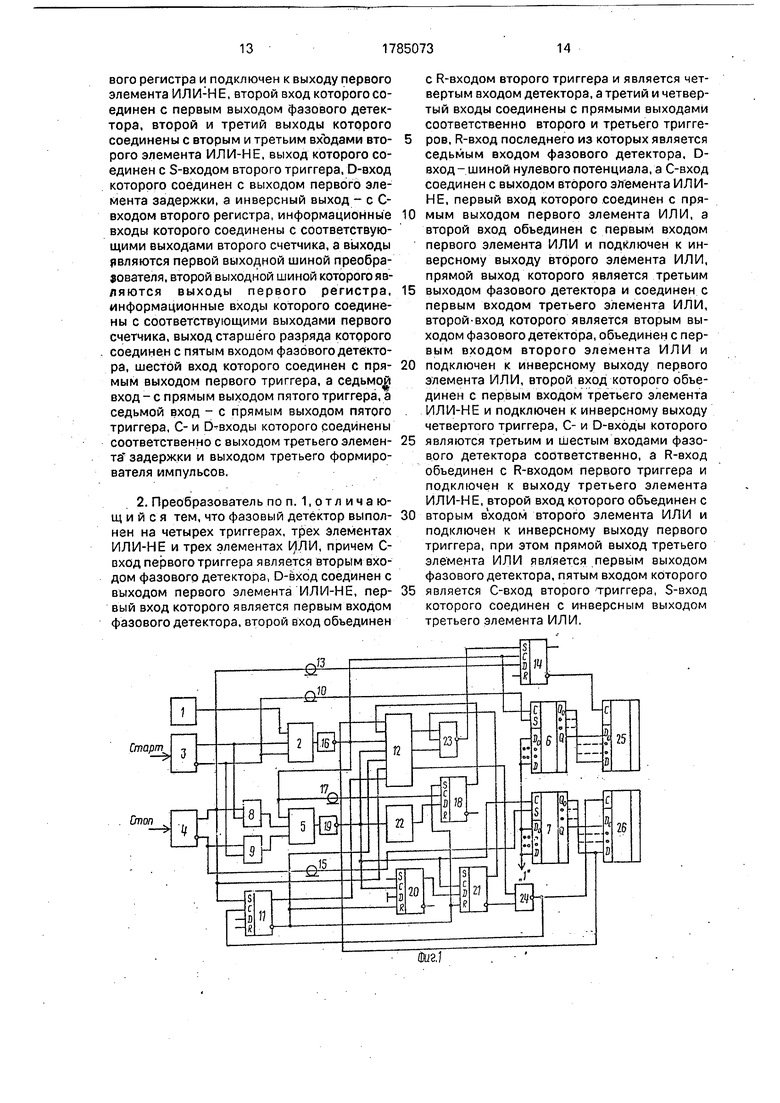

На фиг.1 приведена блок-схема преобразователя время-код; на фиг.2 - принципиальная схема фазового детектора; на фиг.З и 4 - временные диаграммы, поясняющие алгоритм функционирования преобразователя время-код.

Преобразователь время-код содержит генератор 1 образцовой частоты, выход которого подключен к первому входу генератора опорной частоты, формирователь 3 импульсов, вход которого является входом старт-импульсов, формирователь 4 импульсов, вход которого является входом стоп- импульсов, генератор 5 опорной частоты, счетчики 6 и 7, причем прямой выход формирователя 3 импульсов соединен соответственно со вторым входом генератора 2 опорной частоты и первым входом элемента 8 ИЛИ, а инверсный выход объединен соответственно с третьим входом генератора 2 опорной частоты и первым входом элемента 9 И и через элемент задержки 10 подключен ко входу управления счетчика б, прямой выход формирователя 4 импульсов подключен ко второму входу элемента 8 ИЛИ, S-входу триггера 11, первому входу фазового детектора 12 и через элемент задержки 13 - D-входу триггера 14, а инвер с -

ный выход - ко второму входу элемента 9 И

и через элемент задержки 15 - ко входу

управления счетчика 7, инвертор 16, вход

которого подключен к выходу генератора 2

5 опорной частоты, а выход объединен с С- входами счетчика 6 и триггера 14, первым входом генератора 5 опорной частоты, вторым входом фазового детектора 12 и через элемент задержки 17 подключен к С-входу

0 триггера 18, выходы элементов 8 и 9 ИЛИ и И соединены соответственно со вторым и третьим входами генератора 5 опорной частоты, выход которого через инвертор 19 под кл ючен к третье му входу фазового детек5 тора 12, С-входам счетчика 7 и триггеров 20 и 21 и входу формирователя 22 импульсов, выход которого соединен с D-входом триггера 18, выход которого подключен к четвертому входу фазового детектора 12, пятый

0 вход которого объединен с инверсным выходом и S-входом соответственно триггеров

11и 18 и R-входами триггеров 20 и 21, а шестой вход соединен с прямым выходом триггера 11, логический элемент 23 ИЛИ5 НЕ, первый и второй входы которого соединены соответственно с первым и вторым выходами фазового детектора 12, а третий вход подключен к прямому выходу триггера 21, выход логического элемента 23 ИЛИ-НЕ

0 соединен с S-входом триггера 14, логический элемент 24 ИЛИ-НЁ, первый и второй входы которого соединены соответственно с третьим выходом фазового детектора 12 и инверсным выходом триггера 21, D-вход ко5 торого объединен с выходом триггера 20, D-вход которого подключен к шине с нулевым потенциалом, информационные входы счетчиков б и 7 подключены к шине с потенциалом, соответствующему уровню логиче0 ской единицы, инверсный выход триггера 14 подключен к С-входу регистра 25, информационные входы которого соединены соответствующими информационными выходами счетчика 6, второй регистр 26,

5 С-вход которого подключен к выходу элемента 24 ИЛИ-НЕ и С-входу триггера 11, а информационные входы соединены с соответствующими информационными выходами счетчика 7, информационный выход

0 старшего разряда которого соединен с седьмым входом фазового детектора 12, при этом первый, второй и третий входы генератора 2 опорной частоты и генератора 5 опорной частоты являются соответственно его

5 входами Запуск, Сброс, и Опорная частота, а выход- выходом Фазосдвигающий генератор, кроме того, фазовый детектор

12содержит триггер 27, С-вход которого соединен с вторым входом фазового детектора 12, а R-вход соединен с R-входом триггера 28 и выходом элемента 29 ИЛИ-НЕ, первый вход которого объединенЧГинверс- ным выходом триггера 2 и первым входом логического элемента 30 ИЛИ, а второй вход - с инверсным выходом триггера 28 и первым входом элемента 31 ИЛИ, С- и D-входы триггера 28 подключены соответственно к третьему и шестому входам фазового детектора 12, вторые входы элементов ИЛИ 30 и 31 соединены с инберсными выходами элементов ИЛИ 31 и 30 соотв ё тШге нно, элемент ИЛИ 32, первый в/бдлкоторого соединен с прямым выходом элемента ИЛИ 30 и первым выходом фазового детектора 12, а второй вход - со вторым входом элемента ИЛИ 30 и вторым выходом фазового детектора 12, элемент ИЛИ-НЕ 33, первый и второй входы которого подключены соответственно к прямому выходу и второму входу элемента 31 ИЛИ, прямой и инверсный выходы элемента ИЛИ 32 подключены соответственно к третьему выходу фазового детектора 12 и S-входу триггера 34, С-вход которого подключен к седьмому входу фазовою детектора 12, триггер 35, С-вход которого соединен с выходом элемента 33 ИЛИ-НЕ, D- и R-входы которого подключены соответственно к шине с нулевым потенциалом и четвертому входу фазового детектора 12, элемент 36 ИЛИ-НЕ, первый, второй и третий входы которого соединены соответственно с выходами триггеров 34 и 35 и первому входу фазового детектора 12, четвертый вход объединен с К ходом триггера 34 и пятым входом фазового детектора 12, а выход - с D-входом триггера 27.

Преобразователь время-код работает следующим образом.

После поступления на вход формирователя 3 старт-импульса на его выходах формируются биполярные импульсы, которые поступают на вход генератора 2 опорной частоты, приостанавливают на короткое время колебания на его выходе, после чего они возобновляются в фазе со старт-импульсами аналогично как в прототипе. Кроме того, инверсный импульс пбстумает также на вход управления счетчика 6, что приводит к его сбросу в начальное состояние. Основное отличие заявленного устройства заключается в том, что в генераторе 5 Опорной частоты в качестве опорной используется частота генератора 2 опорной частоты. Дело- в том, что исследования показали, что стабильность ФАПЧ-генераторов практически не отличается от стабильности кварцевых генераторов вплоть до урозня . Если в прототипе в качестве грубого квантователя шкалы используются колебания кварцевого генератора, а первый и второй генераторы опорной частоты используются в качестве нониусных генераторов, в заявленном устройстве в качестве грубого квантователя используется первый генератор 2 опорной частоты, а второй генератор 5 опорной частоты - в качестве нониусного измерителя. Это позволяет исключить оценку доли периода в старт-канале. Поскольку синхронизация в старт-канале приводит к

0 изменению фазовых соотношений в стоп- канале, то генератор 5 опорной частоты также синхронизируется старт-импульсом (через логические элементы 8 и 9 ИЛИ и И). После прихода стоп-импульса на вход фор5 мирователя 4 на его выходах формируются парафазные импульсы.

При этом на инверсном выходе триггера 14, который синхронизируется импульсами генератора 2 опорной частоты, формирует0 ся импульс записи текущего содержимого счетчика 6 в регистр 25. Кроме того, при этом осуществляется повторное фазирова- ние генератора 5 опорной частоты,перевод триггера 11 в единичное состояние по входу

5 и сброс нониусного счетчика 7 (по входу управления) в исходное состояние. После установки триггера 11 в единичное состояние на D-входах триггеров 27 и 28 (фиг.2) фазвого детектора 12 (соответственно по

0 пятому входу через логический элемент 36 ИЛИ-НЕ и шестому входу) формируются высокие уровни и начинается цикл измерения при помощи нониусного счетчика 7 (напомним, что старшие разряды, соответствую5 щие коду данного измеряемого интервала, хранятся в регистре 6). Это иллюстрируется временными диаграммами на фиг.З. Триггеры 27 и 28 срабатывают после каждого положительного перепада на С-входах

0 импульсов генераторов 2 и 5 опорной частоты. После установки на инверсных выходах триггеров 27 и 28 уровня логического нуля на выходе логического элемента 29 ИЛИ-НЕ формируется короткий импульс, который

5 возвращает триггеры в исходное состояние. Перепады на выходах триггеров 27 и 28 поступают на входы логических элементов 30 и 31 ИЛИ, имеющих парафазные выходы, соответствующее объединение входов и вы0 ходов которого образуют триггер, В исходном состояТГий на инверсных выходах элементов 30 и 31 ИЛ И установлены уровни логического нуля.

После срабатывания триггеров 27 и 28

5 уровень логической единицы установится на инверсном выходе того элемента 30 или 31 ИЛИ, перепад на входе которого опережает перепад на входе другого на время, которое для интегральных элементов, выполненных по ЭСЛ-технологии. составляет

менее 20 пс. Логические элементы 32 ИЛИ и 33 ИЛИ-НЕ используются для подавления ложных импульсов, которые могут формироваться на выходах элементов 30 и 31 из-за конечных задержек их срабатывания. После очередных положительных перепадов на выходах генераторов 2 и 5 опорной частоты интервалы между ними сокращаются на квант, соответствующий шагу дискретизации h T1-TO, где ТО и Т1 - периоды колебаний соответственно первого и второго генераторов 2 и 5 опорной частоты.

На фиг.З приведены временные диаграммы, соответствующие такому фазовому соотношению между старт- и стоп-импуль- сами, когда в течение двух тактов перепад на С-входе триггера 28 опережает по времени перепад на С-входе триггера 27, а в третьем такте происходит смена знака разности фаз. Это иллюстрируется двумя импульсами на выходе логического элемента ИЛИ-НЕ 33 (на С-входе триггера 35), а после смены знака разности фаз между импульсами генераторов 2 и 5 опорной частоты - на выходах логического элемента 32 ИЛИ (на S-входе триггера 34). При этом импульсом с выхода логического элемента 32 ИЛИ через логический элемент 24 ИЛИ-НЕ информация из нониусного счетчика 7 переписывается в регистр 26. Этим импульсом также триггер 11 сбрасывается в нулевое состояние.На этом цикл измерения временного интервала заканчивается. При этом в счетчиках б и 7 фиксируется информация, соответствующая старшим и младшим разрядам кода временного интервала. Элементы задержки 10 и 15 включены для формирования необходимых фазовых соотношений между импульсами на С- и S-входах счетчиков б и 7. Поскольку на запись информации в счетчики 6 и 7 тратится один такт, то на их информационные входы подаются уровни логической единицы, а не нуля, чтобы скомпенсировать результат измерения на единицу. Однако вследствие задержек, возникающих в ФАПЧ-генераторах между импульсами синхронизации и выходными колебаниями возможна ситуация, когда фронт на С-входе триггера 27 оказывается между фронтом на его D-входе и фронтом на С-входе триггера 28 (фиг.З). В этом случае возникает ложное срабатывание фазового детектора 12, когда уже в первом такте происходит запись информации в нониусный счетчик 7 и сброс триггера 11 в нулевое состояние. При этом возникает погрешность, близкая по значению к периодам генераторов 2 и 5 опорной частоты. Кроме того, если интервал между фронтами генераторов опорной частоты превышает

некоторое значение, то возникает ситуация, когда в момент формирования следующего фронта генератора 5 опорной частоты на R-входах триггеров будет присутствовать 5 уровень логической единицы с выхода логического элемента ИЛИ-НЕ 29, который сформировался в предыдущем такте. В этом случае триггер 28 не сработает, а после формирования положительного перепада на С0 входе триггера 27 на его инверсном выходе установится уровень Логического нуля первым по отношению к выходу триггера 28, что также приведет к окончанию измерения, т.е. неправильному результату. Для исключения

5 этих погрешностей в схему введены триггеры 20 и 21. Их введение разрешает сброс триггера 11 в нулевое состояние только после второго такта колебаний генератора 5 опорной частоты.

0 Кроме того, в схему фазового детектора 12 введены триггеры 34 и 35. Если в первом такте формируются импульсы на выходах элемента ИЛИ 32, а не на выходе элемента 33, то триггер 34 переводится в единичное

5 состояние, что приводит к блокировке триггера 27 по D-входу. Поскольку это означает, что результат измерения, фиксируемый но- ниусным счетчиком 7, будет близким к свое- му максимальному значению (интервал

0 между первыми импульсами генератора 2 и 5 опорной частоты близок к их периодам), то триггер 34 может быть сброшен после заполнения счетчика 7, например, до половины своего содержимого. В данном случае

5 после формирования в старшем разряде счетчика 7 уровня логической единицы триггер 34 сбрасывается в нулевое состояние по С-входу. Триггер 35 при этом всегда устанавливается в единичное состояние (при

0 этом также осуществляется блокировка триггера 27 по входу D), когда интервал to между фронтами импульсов генераторов 5 и 2 опорной частоты удовлетворяет условию

45 t0 Trt2-2(ti+t2),

0)

где Ti и t2 - соответственно задержки триггера 27 и логического элемента 29 ИЛИ-НЕ. Это позволяет исключить погрешность

измерения, обусловленную совпадениями фронтсч импульсов генератора 5 опорной частоты с моментами времени, когда на R- входах триггеров 27 и 28 присутствует уровень логической единицы. Достигается это

следующим образом. После каждого перепада на выходе генератора 5 опорной частоты запускается формирователь 22 импульсов, время выдержки которого несколько меньше, чем Т0. Если интервал между перепадами на выходах генераторов 2 и

5 опорной частоты больше to, то триггер 18 устанавливается в единичное состояние. При этом снимается блокировка с триггера 35 по R-входу, и он установится в единичное состояние после первого импульса, что также приведет к блокировке триггера 27 по D-входу. Поскольку интервал между фронтами генераторов 5 и 2 опорной частоты после очередного периода уменьшается на шаг дискретизации h T1-TO, то в очередном такте он станет меньше to, т.е. условие (1) не будет ЁЫПОЛНЯТЬСЯ. При этом триггер 18 установится в единичное состояние и триггер 35 будет блокироваться по R-входу, что в свою очередь приведет к разблокировке триггера 27 по D-входу. Далее преобразователь время-код работает также, как было описано выше до того, как на выходе логического элемента 32 ИЛИ сформируется импульс окончания измерения.

Кроме того, при определенных условиях может возникать погрешность, равная периоду генератора 2 опорной частоты ТО. Это может происходить, если фронты на С- и D-входах триггера практически совпадают. В этом случае несмотря на точные изме- рения, осуществляемые при помощи счетчика 7, код счетчика 6 может изменяться от раза к разу на единицу. Для исключения этой погрешности прямой выход формирователя 4 импульсов подключен к D-входу триггера 14 через элемент задержки 13, параметры которой выбираются такими, чтобы положительный перепад на D-входе всегда возникал в интервал между положительными перепадами на D- и С-входах триггеров 27 и 28 соответственно.

Эта ситуация будет связана однозначно с возникновением в первом такте импульсов на выходах элемента 32 ИЛИ и соответственно - на выходе элемента 23 ИЛИ-НЕ. Этим импульсом триггер 14 переводится в единичное состояние вне зависимости от его срабатывания по С-входу, что позволяет исключить неоднозначность получаемых результатов измерения.

Преобразователь может быть выполнен в базисе ЭСЛ-технологии 1500 серии.

Таким образом, введение элементов в прототип с соответствующими связями позволило исключить дополнительное измерение в старт-канале и тем самым уменьшить случайную погрешность измерения. Кроме того, результат измерения сразу же фиксируется в регистрах преобразователя и не нуждается в дальнейшей обработке, что повышает его быстродействие.

Формула изобретения

1. Преобразователь время-код, содержащий генератор образцовой частоты, выход которого соединен с первым входом первого генератора опорной частоты, первый формирователь импульсов, вход которого является шиной Старт, второй

формирователь импульсов, вход которого является шиной Стоп, второй генератор опорной частоты, первый и второй счетчики, отличающийся тем, что, с целью повышения точности и быстродействия, в

0 него введены фазовый детектор, два регистра, пять триггеров, элемент ИЛИ, элемент И, два элемента ИЛИ-НЕ, четыре элемента задержки, два инвертора, третий формирователь импульсов, причем прямой выход

5 первого формирователя импульсов соединен со вторым входом первого генератора опорной частоты и первым входом элемента ИЛИ, второй вход которого объединен с первым входом первого элемента задержки,

0 первым входом фазового детектора, S-вхо- дом первого триггера и подключен к прямому выходу второго формирователя импульсов, инверсный выход которого подключен к первому входу элемента И и через

5 второй элемент задержки - к входу занесения первого счетчика, входы предустановки которого объединены с одноименными входами второго счетчика и являются шиной соответствующего потенциала, С-вход вто0 рого счетчика объединен с С-входом второго триггера, вторым входом фазового детектора, входом третьего элемента задержки, первым входом второго генератора опорной частоты, и подключен к выходу первого ин5 вертора, вход которого соединен с выходом первого генератора опорной частоты, третий вход которого объединен с вторым входом элемента И, через четвертый элемент задержки - с входом занесения второго

0 счетчика и подключен к инверсному выходу первого формирователя импульсов, выход элемента ИЛИ соединен с вторым входом второго генератора опорной частоты, третий вход которого соединен с выходом эле5 мента И, а выход через второй инвертор - с третьим входом фазового детектора, входом третьего формирователя импульсов и С-вхо- дами первого счетчика, третьего и четверто . го триггеров, инверсный выход последней. 0 из которых соединен с первым входом первого элемента ИЛИ-НЕ, прямой выход - с первым входом второго элемента ИЛИ-НЕ, D-вход - с прямым выходом третьего триггера, s R-вход - объединен с S-входом пято5 го триггера, R-входом третьего триггера, четвертым входом фазового детектора и подключен к инверсному выходу первого триггера, D-вход которого и D-вход третьего триггера являются шиной нулевого потенциала, а С-вход объединен с С-входом первого регистра и подключен к выходу первого элемента ИЛИ:НЕ, второй вход которого соединен с первым выходом фазового детектора, второй и третий выходы которого соединены с вторым и третьим входами второго элемента ИЛИ-НЕ, выход которого соединен с S-входом второго триггера, D-вход которого соединен с выходом первого элемента задержки, а инверсный выход - с С- входом второго регистра, информационные входы которого соединены с соответствующими выходами второго счетчика, а выходы рвляются первой выходной шиной преобразователя, второй выходной шиной которого являются выходы первого регистра, информационные входы которого соединены с соответствующими выходами первого счетчика, выход старшего разряда которого соединен с пятым входом фазового детектора, шестой вход которого соединен с прямым выходом первого триггера, а седьмой вход - с прямым выходом пятого триггера, седьмой вход - с прямым выходом пятого триггера, С- и D-входы которого соединены соответственно с выходом третьего элемента задержки и выходом третьего формирователя импульсов.

2. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что фазовый детектор выпол- нзн на четырех триггерах, трех элементах ИЛИ-НЕ и трех элементах ИЛИ, причем С- вход первого триггера является вторым входом фазового детектора, D-вход соединен с выходом первого элемента ИЛИ-НЕ, пер- вый вход которого является первым входом фазового детектора, второй вход объединен

10

15

0

5

0

с R-входом второго триггера и является четвертым входом детектора, а третий и четвертый входы соединены с прямыми выходами соответственно второго и третьего триггеров, R-вход последнего из которых является седьмым входом фазового детектора, D- вход - шиной нулевого потенциала, а С-вход соединен с выходом второго элемента ИЛИ- НЕ, первый вход которого соединен с прямым выходом первого элемента ИЛИ, а второй вход объединен с первым входом первого элемента ИЛИ и подключен к инверсному выходу второго элемента ИЛИ, прямой выход которого является третьим выходом фазового детектора и соединен с первым входом третьего элемента ИЛИ, второй-вход которого является вторым выходом фазового детектора, объединен с первым входом второго элемента ИЛИ и подключен к инверсному выходу первого элемента ИЛИ, второй вход которого объединен с первым входом третьего элемента ИЛИ-НЕ и подключен к инверсному выходу четвертого триггера, С- и D-входы которого являются третьим и шестым входами фазового детектора соответственно, а R-вход объединен с R-входом первого триггера и подключен к выходу третьего элемента ИЛИ-НЕ, второй вход которого объединен с вторым входом второго элемента ИЛИ и подключен к инверсному выходу первого триггера, при этом прямой выход третьего элемента ИЛИ является первым выходом фазового детектора, пятым входом которого является С-вход второго триггера, S-вход которого соединен с инверсным выходом третьего элемента ИЛИ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| НОНИУСНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2128853C1 |

| Устройство для измерения временных интервалов | 1988 |

|

SU1553952A1 |

| Цифровой фазометр мгновенных значений | 1988 |

|

SU1553920A1 |

| Синтезатор частоты | 1981 |

|

SU1007202A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство демодуляции телевизионного сигнала системы Секам | 1989 |

|

SU1688458A1 |

| ОБНАРУЖИТЕЛЬ ПЕРЕОТРАЖЕННЫХ СИГНАЛОВ | 1999 |

|

RU2191400C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ НОНИУСНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2127445C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1995 |

|

RU2076458C1 |

Изобретение относится к электроизмерительной технике и может быть использовано в ядерной физике и масс-спектрометрии. Цель изобретения - повышение точности и быстродействия измерения временных интервалов. Преобразователь время-код содержит генератор образцовой частоты, первый и второй ФАПЧ-генераторы, первый, второй и третий формирователи импульсов, первый и второй счетчики, логические элементы ИЛИ и И, первый, второй, третий и четвертый элементы задержки, первый, второй, третий, четвертый и пятый триггеры, фазовый детектор, первый и второй элементы ИЛИ- НЕ, первый и второй регистры с соответствующими связями. Новым в устройстве является использование частоты первого ФАПЧ-генератора в качестве опорной для второго ФАПЧ-генератора, что позволяет исключить измерение в старт-ка«але и уменьшить случайную составляющую погрешности. Кроме того, результат измерения фиксируется непосредственно в выходных регистрах и не нуждается в дополнительной обработке, что повышает быстродействие, 4 ил. (Л С

| Мелешко Е.А | |||

| Наносекундная электроника в экспериментальной физике | |||

| М.: Энергоатомиздат, 1987, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Чу Д., Фергюсон К | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Электроника (Electronies), 1977, № 23, с | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1992-12-30—Публикация

1991-01-14—Подача