(21)4671752/24

(22)22.02.89

(46) 30.04. 91. Бюл. № 16

(72) В.Е.Подтуркин и А.А.Умблия

(53)681.327.12(088.8)

(56)Авторское свидетельство СССР № 1451675, кл. G 06 F 3/05, 1987.

Авторское свидетельство СССР 1425644, кп. G 06 F 3/05, 1986.

(54)УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ

(57)Изобретение относится к вычислительной технике и может быть ис«пользовано в системах автоматизации 4иэическнх исследований для ввода импульсных сигналов, а также в системах отображения импульсных сигналов. Целью изобретения является расширение области применения устройства. Устройство содержит регистр 2, счетчики 6-9, мультиплексоры 4 и 10, триггеры 11-16, блок памяти 3, аналого-цифровой преобразователь 1, - блок сравнения 5, элементы И-ИЛИ 17, 18 и 19, формирователь импульса 24, элементы И 20, 21 и 22. Введение новых элементов обеспечивает буферизацию вывода информации, сжатие информации с привязкой к шкале времени, внешнюю синхронизацию запуска с возможностью программируемого сдвига начала отрезка дискретизации 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

| Устройство для ввода информации | 1983 |

|

SU1164689A1 |

| Способ селективной записи импульсных процессов и устройство для его осуществления | 1988 |

|

SU1636800A1 |

to

СЬ 4.

сл

со

4 iCO

Фиг 1

Изобретение относится к вычисли тельной технике и может быть исполь- зовано для ввода импульсных сигна- лов в системах автоматизации физичес- кого эксперимента, в системах отображения импульсных сигналов.

Целью изобретения является расширение области применения за счет осуществления сжатия вводимой инфор- нации с обеспечением привязки ее к шкале времени

На фиг.I изображена функциональная схема устройства; на фиг.2 - функциональная схема схемы сравнения.

Устройство (фиг.1) содержит аналого-цифровой преобразователь (АЦП) 1, регистр 2, блок 3 памяти, первый мультиплексор 4, блок 5 сравнения, второй 6, первый 7 и третий 8 счетчи- ки, делитель 9 частоты, второй мультиплексор 10, первый 11, четвертый 12, второй 13, третий 14, пятый 15 и шестой 16 триггеры, третий 17, первый 18 и второй 19 элементы И-КЛИ, третий 20, второй 21 и первый 22 элементы И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23, формирователь 24 импульса. На фиг.1 обозначены также входы и выходы 25- 32 устройства.

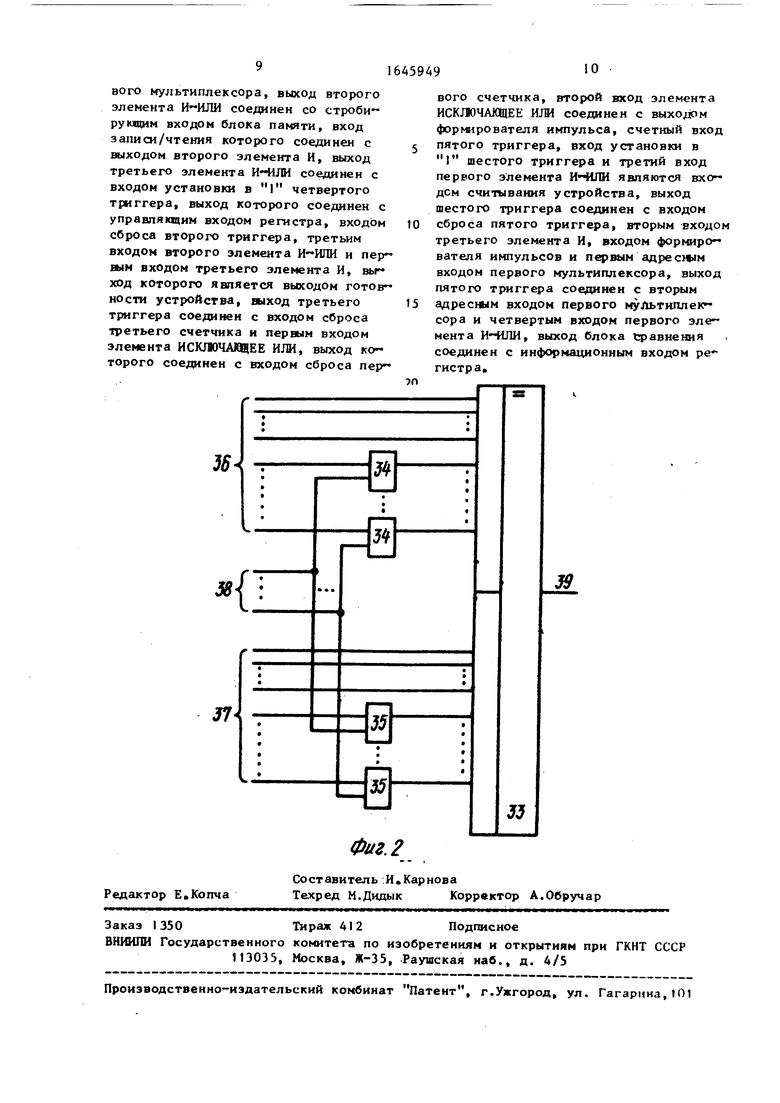

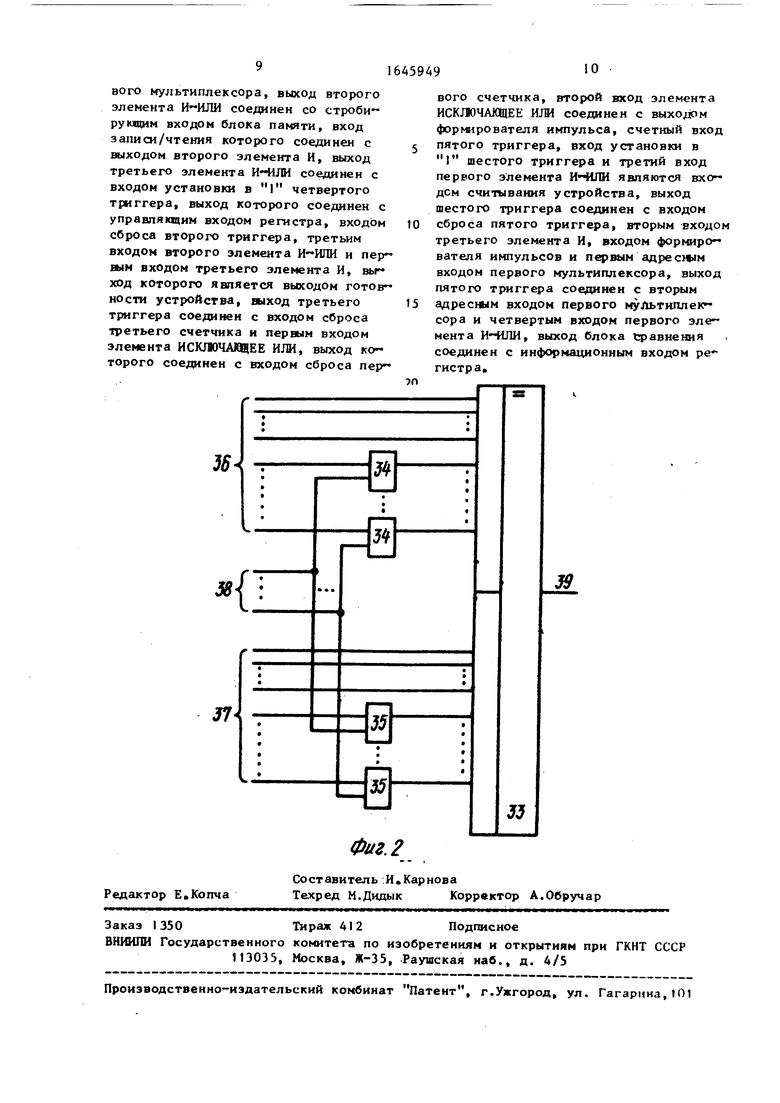

Блок 5 сравнения (фаг.2) содержит цифровой компаратор 33, первую 34 и вторую 35 группы элементов ИЛИ. Стар шие разряды первой 36 и второй 37 групп входов соединены непосредст- венно с соответствующими входами компаратора 33, младшие разряды входов 36 и 37 связаны с соответствую щими входами компаратора 33 че- рез группы элементов ИЛИ 34 и , 35, вторые входы которых попарно объединены и являются входами 38 маскирования. Выход компаратора является .выходом, 39 блока-5 сравнения.

Устройство работает следующим об- разом.

Работа устройства начинается с за пи си в счетчик 6 кода задержки с вхо дов 25. Код записывается по сигналу записи на входе 26. Этим же сигналом устанавливаются в О триггеры И, 12, 14 - 16. При этом в один из разрядов счетчика 6 заносится логическая I. После этого устройство находится в режиме готовности - счетчики 7 и 8 и триггеры 11-16 в состоянии логического О. Импульсы синхронизации через делитель 9 частоты поступают на вход элемента И 22 и на стробирующий вход триггера 13.

По импульсу на входе запуска 27 переключается триггер 11 и импульсы синхронизации с делителя 9 частоты через элемент И 22 начинают поступать на вычитающий вход счетчика 6. После переключения в О выхода счетчика 6 поступление на его вход импульсов блокируется элементом И 22. Кроме того, нулевой уровень поступает на инверсный D-вход триггера 13 и по очередному импульсу синхронизации триггер 13 переключается, разрешая работу мультиплексора 10. В зависимости от кода на входах 29 выбора частоты дискретизации мультиплексор 10 передает на свой импульсы с одного из выходов делителя 9 частоты.

Устройство переходит к режим дискретизации. Оцифрованная информация с выходов АЦП 1 поступает на входы регистра 2 и на входы блока 5 сравнения. Импульсами с выхода мультиплексора 10 значения отсчетов заносятся в регистр.2. При этом занесенное в регистр 2 значение сравнивается с очередным отсчетом с выходов АЦП 1. Сигнал сравнения с выхода блока 5 сравнения также проходит через регистр 2 и поступает на входы элементов 18, 19 и 21. При этом элементы 19 и 21 синхронно формируют соответственно импульсы выборки и импульсы записи для блока 3 памяти. Элемент 18 формирует строби- рующие импульсы, переключающие счетчик 7. Указанные импульсы на входах блока 3 памяти и счетчика 7 формируются- только при поступлении сигнала сравнения с выхода регистра 2. Указанный сигнал формируется блоком 5 сравнения при несовпадении информа ции в регистре и информации на выходах АЦП 1. В то же время импульсы с выхода мультиплексора 10 подсчитываются счетчиком 8. Код с выходов счетчика 8 также, как и код с выходов АЦП I, поступает на входы регистра 2

Таким образом, каждый отсчет с выходов АЦП 1 сопровождается номером с выходов счетчика 8. В блок 3 памяти с выходов регистра 2 значение отсчета также заносится вместе с кодом номера отсчета. При этом запись в блок 3 памяти очередного отсчета...

осуществляется только в случае его отличия от предыдущего Сразу же кос ле записи (по заднему фронту им пуль- са) в регистр 2 заносится новое зна- чение отсчета, а счетчик 7 переклкг- чается в следующее состояние, адресуя в блоке 3 памяти новую ячейку памяти. Разрядность счетчика 8 выби- рается большей или равной разрядное ти счетчика 7. Процесс дискретизации продолжается до заполнения одно го из счетчиков 7 и 8. В нормальной ситуации первым заполняется счетчик 8, альтернативный случай соответствует ситуации переполнения. При заполнении любого из счетчиков 7 и 8 формируется сигнал на выходе, элемента И-ИЛИ 17, переключающий триггер 12. При этом сбрасывается второй триггер 13 Сигналом на входе разрешения третьего состояния отключается регистр 2, сигналом на входе триггера 12 через элемент И-ИЛИ 19 формируется сигнал выборки на входе блока 3 памяти. При этом нулевым уровнем с выхода триггера 13 отключается мультиплексор 10, прекращая синхро- серию на своих выходах Одновременно элемент И 20 формирует на выходе 32 сигнал прерывания, информирующий об окончании цикла дискретизации.

Устройство переходит в режим считывания. Триггеры 15 и 16 находятся по-прежнему в состоянии логического О на выходе. Выходной мультиплексор 4 передает на выходы 31 код числа отсчетов с выхода счетчика 7.Сигнал считывания подается на вход 30. Первым считывается число оцифрованных отсчетов, записанных в блоке 3 памяти, с выходов счетчика 7. По отрицательному фронту сигнала на входе 30 переключается триггер 16. Сигнал с выхода триггера 16 поступает на второй адресный вход мультиплексора и на вход формирователя 24 импульса, который в ответ на положительный импульс формирует короткий отрицательный импульс на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23. При этом последний формирует импульс сброса на входе счетчика 7, обнуляя его. Одновременно единичный уровень поступает на первый вход элемента И 20, прекращая формирование сигнала прерывания на выходе 32. На адресные входы блока 3 памяти поступает нулевой код с выхода счетчика 7, и на

выходы блока 3 памяти выдается значение первого отсчета и его номер. При этом мультиплексор 4 коммутирует на свои выходы 31 код номера отсчета с соответствующих входов- выходов блока 3 памяти. По заднему фронту сигнала считывания на входе 30 переключается счетный триггер 15,

0 переключающий мультиплексор 4 и разрешающий прохождение следующего импульса считывания через элемент И-ИЛИ 18 на вход счетчика 7. Мультиплексор 4 коммутирует на свои выхо-

5 ды 31 значение отсчета с первой

группы входов-выходов блока 3 памяти. По заднему фронту следующего импульса считывания переключается в следующее состояние счетчик 7 и

0 вновь устанавливается в О триггер 15. При этом в блоке 3 памяти выбирается следующая ячейка памяти. Таким образом, каждая пара последующих импульсов на входе 30 считывания

5 обеспечивает считывание очередного номера и значения отсчета.

После считывания всех отсчетов, записанных в блоке 3 памяти, в счет- чик 6 вновь может быть занесен код

0 задержки. При этом вновь все триггеры устройства устанавливаются в О. Нулевой уровень на выходе триггера 14 сброса устанавливает в нулевое состояние счетчики 7 и 8. Установка в 1 триггера 14 и таким образом разблокировка счетчиков 7 и 8 осуществляется первым же импульсом на выходе мультиплексора 10.

Для нормальной работы устройства

о следует синхронизировать работу

АЦП 1 с импульсами на выходе мультиплексора 10.

Таким образом, устройство позволяет по внешнему синхроимпульсу на

5 входе 27 с заданной задержкой начать оцифровку входного аналогового сигнала. Информация заносится в блок 3 памяти. При этом записываются только отсчеты, отличающиеся от предыдущих

0 Каждое записываемое значение отсчета сопровождается своим номером, что обеспечивает его временную привязку. По окончании цикла оцифровки формируется сигнал прерывания. При считы-

5 вании в первую очередь выдается код, численно равный числу отсчетов, записанных в блок 3 памяти, а затем поочередно выдаются код номера отсчета и значение отсчета для всех отсчетов.

5

В качестве первого значения в Ол о к 3 памяти из регистра 2 может за носиться недостоверная информация, при использовании устройства первый считываемой отсчет игнорируется либо необходимо предусмотреть дополнительную цепь тактирования регистра 2 на период ожидания импульса запуска.

Напкчие помех или флуктуации сиг- нала на стационарных участках может приводить к резкому увеличению числа оцифрованных отсчетов и к переполнению счетчика 7. Для предотвращения этих явлений на один или несколько разрядов входов 38 маскирования подаются уровни логической 1. Указанные уролни проходят через соответствующие элементы ИЛИ 34 и 35 на младшие разряды входов цифрового компара- тора 33 и обеспечивают принудительное совпадение логических уровней на них Таким образом маскируются малые изменения входного сигнала.

Использование изобретения позво- ллет расширить функциональные возможности за счет обеспечения буферизации вывода информации, за счет сжатия информации с обеспечением привязки к шкале времени, за счет обеспе- чения внешней синхронизации запуска с возможностью программируемого сдвига начала отрезка дискретизации.

Формула изобретения

. Устройство для ввода информации, содержащее аналого-цифровой преобразователь, блок памяти, первый, второй и третий счетчики, делитель частоты, блок сравнения, первый триггер, первый элемент И, вход аналого-цифрового преобразователя является информационным входом устройства, выходы первого счетчика соедине- i с адресными входами блока памяти, входы-выходы первой группы блока памяти соединены с входами первой группы Олока сравнения, вход установки в 1 первого триггера является входом запуска устройства, выход делителя частоты соединен с первым входом первого элемента И, выход которого соединен со счетным входом второго счетчика, отличающееся

тем, что, с целью расширения области применения за счет осуществления , сжатия вводимой информации с обеспе- чением привязки ее к шкале времени,

в устройство введены первый и второй мультиплексоры, второй, третий, четвертый, пятый и шестой триггеры, второй и третий элементы И, регистр, первый, второй и третий элементы , элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и формирователь импульса, причем выходы аналого-цифрового преобразователя соединены с входами второй группы блока сравнения и информационными входами первой группы регистра, выходы первой и второй групп которого соединены с входами-выходами первой и второй групп блока памяти и информационными входами первой и второй групп первого мультиплексора, выход которого является информационным выходом устройства, входы предустановки второго счетчика являются входами задания кода задержки устройства, вход записи второго счетчика, входы сброса первого, третьего, четвертого и шестого триггеров являются входом записи устройства, выход второго счетчика соединен с информационным входом второго триггера и вторым входом первого элемента И, третий вход которого соединен с выходом первого триггера, вход делителя частоты является синхронизирующим входом устройств, выходы делителя частоты соединены с информационными входами второго мультиплексора, один из выходов делителя частоты соединен с тактовым входом второго триггера, выход которого соединен с управляющим входом второго мультиплексора, адресные входы которого являются входами выбора частоты дискретизации устройства, выход второго мульти плексора соединен с первыми входами первого и второго элементов И-ИЛИ, первым входом второго элемента И, входом установки в 1 третьего триг гера, входом записи регистра и счетным входом третьего счетчика, выходы которого соединены с входами первой группы третьего элемента и информационными входами второй группы регистра, выход которого соединен с вторым входом второго элемента И и вторыми входами первого и второго элементов И-ИЛИ, выход первого элемента И-ИЛИ соединен со счетным входом первого счетчика, выходы которо- го соединены с входами второй группы третьего элемента И-ИЛИ и информационными входами третьей группы пер-

вого мультиплексора, выход второго элемента И-ИЛИ соединен со строби- руклцим входом блока памяти, вход записи/чтения которого соединен с выходом второго элемента И, выход третьего элемента И-ИЛИ соединен с входом установки в I четвертого триггера, выход которого соединен с управлямщим входом регистра, входом сброса второго триггера, третьим входом второго элемента И-ИЛИ и пер- вым входом третьего элемента И, выход которого является выходом готовности устройства, выход третьего триггера соединен с входом сброса третьего счетчика и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом сброса перX{L

37

0

вого счетчика, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом формирователя импульса, счетный вход пятого триггера, вход установки в 1 шестого триггера и третий вход первого элемента И-ИЛИ являются входом считывания устройства, выход шестого триггера соединен с входом сброса пятого триггера, вторым входом третьего элемента И, входом формирователя импульсов и первым адресным входом первого мультиплексора, выход пятого триггера соединен с вторым адресным входом первого мультиплексора и четвертым входом первого элемента И-ИЛИ, выход блока сравнения соединен с информационным входом регистра.

39

JJ

Авторы

Даты

1991-04-30—Публикация

1989-02-22—Подача