Од О)

Изобретение относится к вычислительной технике и может быть использовано для определения значения и аргумента максимума взаимной корреля ционной функции (ВКФ) между случайными сигналами, подвергнутыми взаимному масштабно-временному искажению (МВИ).

Цель изобретения - повышение быст родействия устройства для определения взаимной корреляционной функции между двумя случайными сигналами,подвергнутыми взаимному масштабно-временному преобразованию

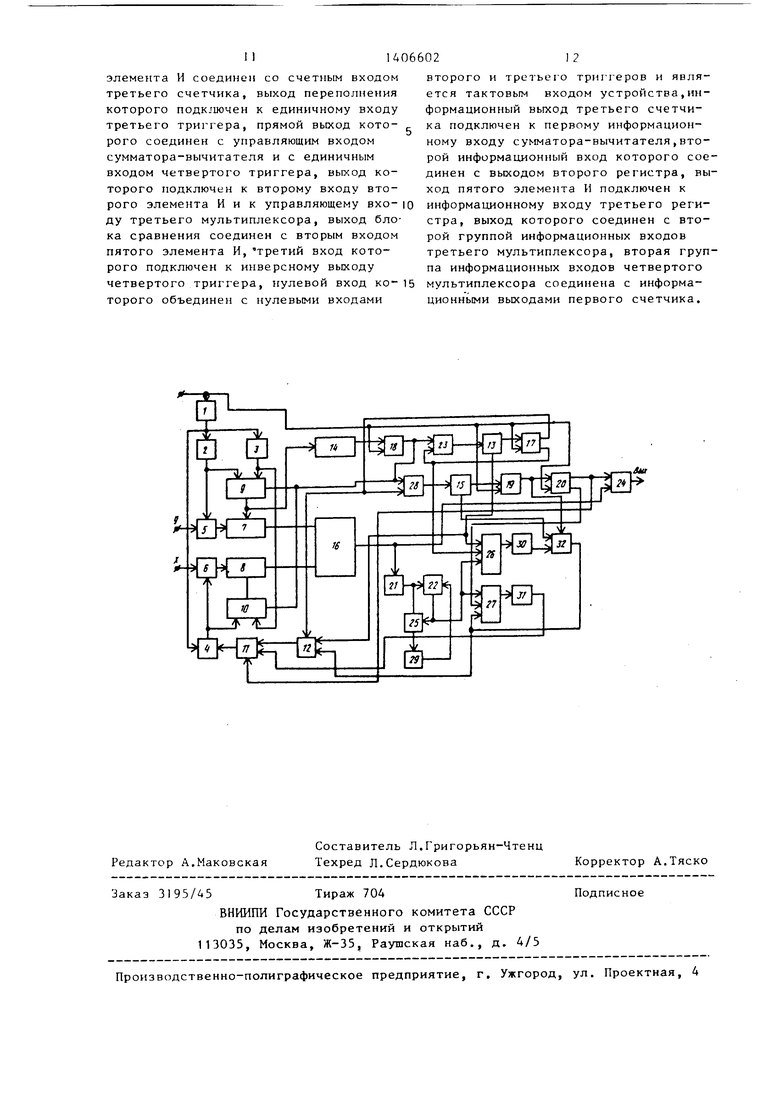

На чертеже представлена блок-схема устройства.

Устройство содержит генератор 1 тактовых импульсов, делители 2 и 3 частоты импульсов с фиксированными различными коэффициентами деления, делитель 4 частоты следования импульсов с управляемым коэффициентом деления, аналого-цифровые преобразователи (АЦП) 5 и 6, блоки 7, 8 памяти, мультиплексоры 9-12, счетчики 13-15 импульсов«коррелятор 16. триггеры 17-20, экстремальный анализатор 21, блок 22 сравнения, элементы И 23-28, регистры 29-31, сумматор-вычита- тель 32.

Принцип работы устройства вытекае из следующих соображений. Нз-за взаимных МВИ входных сигналов х и у, то есть сжатия или растяжения по ос времени одного из сигналов относител но другого, корреляционная связь между сигналами ослабевает, их ВКФ искжается, в частности уменьшается ее максимуме Оценка нормированной ВКФ между сигналами x(t) и y(kt )y(t|.+ + kt) определяется выражением kT 2 p(f,k) -.- J р (-C+ktOdlkt),

kT 2

где К k-1 - коэффициент МВИ;

1 - аргумент ВКФ; Т - время усреднения оценки ВКФ;

р - нормированная ВКФ между сигналами x(t) и

y(t);

t - текущее время. Для упрощения, не умаляя общности рассуждений, положим, что МВИ сводится к сжатию во времени сигнала у.

Положим также, что сигнал у, спектр которого ограничен верхней частотой f , подвергнут дискретизации с частотой fy,2f, В результате дискретизации получается последовательность отсчетов, расположенных с интервалом 1/Гр , из которых можно восстановить исходный процесс

Увеличим частоту дискретизации в (1+k) раЗо Полученную последовательность отсчетов расположим с интервалом 1/f „ Если восстановить теперь непрерывный сигнал, то он будет равномерно растянут по оси времени относительно исходного процесса у в (l+k) разо Таким образом, изменя частоту дискретизации f(+k путем задания различных значений k , а затем располагая полученные отсчеты с интервалом l/fg, можно скомпенсировать МВИо Чем ближе значение kj к неизвестному коэффициенту масштабно-временных искажений сигнала у, тем больше значение максимума ВКФ между сигналами х и у

Процесс определения ВКФ происходит в два этапа. На первом этапе изменяется значение k . с дискретностью J k причем для

с- - каждого значения kj ijk j(i

0,1,..., ri - l) определяется значение максимума соответствующей оценки ВКФ. Наибольшее из значений максимумов оцеуок, полученных на первом этапе, будет отличаться от максимума оценки ВКФ при полной компенсации МВИ не более чем на 3 дБ, Значение коэффициента k . для этой оценки отличается от истинного коэффициента k: МВИ не более чем

1 на

Если полученный результат не удовлетворяет требованиям по точности, то начинается второй этап, на котором происходит уточнение полученных на первом этапе результатов. Коэффициент компенсации МВИ изменяется с дискретностью 4k(4k-j dk ,) . При этом анализируется интервал изменения компенсирующего коэффициента от

Uj -i|i- до (k-ky -i;- -). 3„ачение kj, соответствующее наибольшему из значений максимумов оценок ВКФ, полученных на втором этапе, от-,

личается от истинного не более чем

X /)k J на t ----- .

Выбор частоты дискретизации f(j - 2ff. по условию Котельникова не является обязательным и использован только для наглядности рассуждений В предлагаемом устройстве частота fj выбирается в зависимости от необ

ходимого интервала Л t дискретизации коррелограммы, а при использовании в корреляторе метода некоррелированных выборок - еще и в зависимости от значения интервала корреляции сиг налов X и у.

Устройство для определения взаимной корреляционной функции работает следующим образом.

В исходном состоянии счетчики 13-15, триггеры 17-20 и регистры 29-31 обнулены. При этом мультиплексоры 9-12 подключают выходы делителей 2 и 4 частоты к входам блоков 7 и 8 памяти соответственно, а разрядные выходы счетчика 14, на которых присутствует слово, состоящее из логических нулей, к управляющим входам делителя 4 частоты. Благодаря этому коэффициент деления частоты импульсов делителя 4 равен коэффициету деления делителя 2. Объемы блоков 7, 8 памяти выбирают такими, чтобы в них поместились выборки реализаций входных сигналов х и у, обеспечивающих вычисление коррелограммы с необходимым фактором усреднения. Фиксированный коэффициент деления делителя 3 выбран таким, чтобы за время заполнения импульсами с его выхода счетчика 14 произошло построение коррелограммы коррелятором 16,

Нулевой цикл работы устройства на

выборки входньсх реализаций, необход мой для построения коррелограммы, Тоео равна количеству отсчетов в вы , борке. По окончании записи выборки реализаций в блоки 7 и 8 памяти на вькоде счетчика 14 формируется импульс, который поступает на счетный вход триггера 18 и устанавливает ег в состояние I При этом мультипле соры 9 и 10 подключают выход делите ля 3 частоты к синхронизирующим вхо дам блоков 7 и 8 и к входу счетчика 14, начинается считывание выборки и блоков памяти с частотой, определяе мой ч астотой следования импульсов на выходе делителя 3. Отсчеты реали зации сигналов X и у поступают на входы коррелятора 16, который опред ляет их ВКФ, Выход коррелятора при этом отключен от выхода всего устройства, так как элемент И 24 закры низким потенциалом на прямом выходе триггера 20, Поэтому значения всех ординат коррелограммы поступают тол ко в экстремальный анализатор 21, к торый вьщает код максимальной ординаты на вход блока 22 сравнения,Это блок сравнивает упомянутый код с со держимым регистра 29, Если вновь пос тупившее от экстремального анализатора 21 число превьпиает код, хранящийся в регистре 29, то на выходе блока 22 сравнения возникает импульс который открывает элемент И 25, а также элемент И 26, благодаря присут ствию на одном из входов последнего высокого потенциала с инверсного выхода триггера 17. При этом в регистр 29 записывается новое значение макси мальной ординаты, а в регистр 30 - содержимое счетчика 13, т,е, номер цикла. Таким образом, в нулевом цикл первого этапа блок 22 производит

первом этапе начинается с приходом запускающего импульса на вход устрой- сравнение максимальной ординаты ВКФ ства, который включает тактовый ге- и нулевого содержимого регистра 29, нератор 1 , Тактовые импульсы, проходя через делители 2 и 4 частоты, поступают на синхронизирующие входы ана-На выходе блока 22 появляется им- пульс, открываются элементы И 25 и 26 и в регистр 29 записывается зна чение максимума ВКФ, полученной в нулевом цикле, т.е. при одинаковых частотах дискретизации сигналов х и у (коэффициент компенсации МОИ k| о), В регистр 30 заносится нулевое значение содержимого счетчика 13,

лого-цифровых преобразователей 5 и 6 и блоков 7 и 8 памяти, благодаря чему входные сигналы х и у дискретизи- руются с одинаковой частотой, определяемой фиксированным коэффициентом деления делителя 2, и записываются в блоки 7 и 8 памяти. Запись отсчетов в блоки 7 и 8 памяти продолжается до переполнения счетчика 14, емкость которого определяется объемом

10

20

25

-15

406602

выборки входньсх реализаций, необходимой для построения коррелограммы, Тоео равна количеству отсчетов в вы- , борке. По окончании записи выборки реализаций в блоки 7 и 8 памяти на вькоде счетчика 14 формируется импульс, который поступает на счетный вход триггера 18 и устанавливает его в состояние I При этом мультиплексоры 9 и 10 подключают выход делителя 3 частоты к синхронизирующим входам блоков 7 и 8 и к входу счетчика 14, начинается считывание выборки из блоков памяти с частотой, определяемой ч астотой следования импульсов на выходе делителя 3. Отсчеты реализации сигналов X и у поступают на входы коррелятора 16, который определяет их ВКФ, Выход коррелятора при этом отключен от выхода всего устройства, так как элемент И 24 закрыт низким потенциалом на прямом выходе триггера 20, Поэтому значения всех ординат коррелограммы поступают только в экстремальный анализатор 21, который вьщает код максимальной ординаты на вход блока 22 сравнения,Этот блок сравнивает упомянутый код с содержимым регистра 29, Если вновь поступившее от экстремального анализатора 21 число превьпиает код, хранящийся в регистре 29, то на выходе блока 22 сравнения возникает импульс, который открывает элемент И 25, а также элемент И 26, благодаря присутствию на одном из входов последнего высокого потенциала с инверсного выхода триггера 17. При этом в регистр 29 записывается новое значение максимальной ординаты, а в регистр 30 - содержимое счетчика 13, т,е, номер цикла. Таким образом, в нулевом цикле первого этапа блок 22 производит

30

35

40

- сравнение максимальной ординаты ВКФ и нулевого содержимого регистра 29, сравнение максимальной ординаты ВКФ и нулевого содержимого регистра 29,

-На выходе блока 22 появляется им- . пульс, открываются элементы И 25 и 26 и в регистр 29 записывается значение максимума ВКФ, полученной в нулевом цикле, т.е. при одинаковых частотах дискретизации сигналов х и у (коэффициент компенсации МОИ k| о), В регистр 30 заносится нулевое значение содержимого счетчика 13,

В конце нулевого цикла по окончании считывания выборки из блоков 7 и 8 памяти происходит переполнение

счетчика 15, триггер 18 возпрэ1цаетс:я в нулевое состояние. Импульс с его выхода через элемент И 23, открытый логической единицей I на инверслом выходе триггера 17, поступает на счетчик 13 и устанавливает его в состояние 1, Код этого состояния через мультиплексоры 12 и 11 поступает на управляющий вход делителя 4 частоты, благодаря чему его коэффициент деления становится мепьшиМо Импульсы на синхронизирующий вход АЦП 6 поступает чаще, и частота дискретизации сигнала у становится выше частоты дискретизации сигнала х на величину &f - , В очередном первом цикле работы устройства, как и в нулевом, происходит запись отсчетов реализаций х и у в блоки 7 и 8 памяти с Однако теперь интервал дискретизации процесса х меньше, чем в предыдущем цикле. Считыва}1ие же отсчетов выборки реализаций из блоков 7 и 8 происходит с одинаковой фиксированной частотой, задаваемой делителем 3. Поэтому коррелятор 16 в первом цикле определяет ВКФ между несколько растянутым сигналом у и сигналом X. После окончания определения ВКФ ее максимальная ордината с выхода экстремального анализатора 21 поступает на вход блока 22 сравнения и, если она превышает максимум предьщущей ВКФ, то заносится в регистр 29, а в регистр 30 записывается соответствующий ей номер цикла (в данном случае первый).

В завершение первого цикла на выходе триггера 18 формируется второй от начала работы импульс, который через элемент И 23 проходит на счетчик 1-3, После этого начинается второй , в котором, как и в последующих, работа протекает яналогич- но: изменяется коэффициент деления частоты импульсов делителя 4, частота дискретизации сигнала у увеличивается до значения l (l+;dh,; (i - номер цикла), коррелятор 1Ь определяет ВКФ между сигналом х и еще более растянутыми сигналами х, экстремальный атшлизатор 21 выделяет максимальную ординату очередной ВКФ, а экстремальный анализатор, состоящий из элемента И 25 и блока 22 спанне- ния, заносит в регистр 29 максимальную из множества нычислеушых за (i+l) циклов ординат ВКФ, а в регист

30 - соответствующий номер цикла. Устройство работает в описанном реживыбирается

п

ме г; циклов, причем

из сослношения ().,/ . ,

где

Iмлкс

заранее известный максимальный коэффициент МВИ между входными сигналамие

Таким образом, в течение ti циклов были получены ВКФ между сигналом X и семейством растянутых по оси времени относительно сигнала у сигналов у.. При этом исходное масштабно- временное искажение сиг нала у отно5 сительно х компенсировалось шагами величиной и при некотором k ; J4 k (j k - 1 ) бьшо скомпенсировано с тс чностью до , При этом уровень корреляции между сигналами

0 X и у стал отличаться от истинного не бсхчсе чем на 3 дБ а максимум J-й ВКФ превысил максимум всех остальных ВКФ.

К моменту поступления на вход

5 счетчика 14 п-го импульса от триггера 17 в регистре 29 хранится наибольший из ряда максимумов ВКФ, т.е. максимум ЪКФ цикла, в котором МВИ было скомпенсировано с точность.ю до ,

0 а в регистре 30 - номер этого цикла. При этом номер цикла совпадает с кодом, который управляет перестраиваемым делителем 4 в том же цикле.

Емкость счетчика 13 равна п : По окончании )-го цикла работы от триггера 17 через элемент И 23 поступает импульс, который переполняет счетчик 13о При этом счетчик переходит в нулевое состояние, а сиг0 нал с его выхода устанавливает триггер 17 в состояние 1. Благодаря этому закрывается э:1емент И 23, и последующие импульсы с выхо/ia 1ригге- ра 1В не изменяют состояния счетчика 13. Кроме того, открывается элемент И 28, мультиплексор 12 сигналом с прямого выхода трип-ера 17 переводится в состояние, подключающее к его выходу вь;ход сумматора-вычита- теля 32,, С этого момента начинается второй этап работы устройства.

Па этом этапе производится уточнение значения коэффициента, компенсирующего МВИ, с учетом того, что

g истинный коэффициент МВИ может отличаться от найденного на первом эта- .

пе k I juk, не более чем на

I + ki т---- f уточнение производится ша5

5

0

для чего требуется Как и

таких шагов.

г ;i м и и 1 Л t

, 2 - k2

на первом этапе, поиск значения коэффициента МВИ производится путем изменения коэффициента деления частоты импульсов делителя 4„ При этом частота следования импульсов на его вьгходе изменяется вокруг значения

J4k,f, 2-го этапа

шагами Л g

,Г.

часре 30, в п

раз, Взвешива-

В 1-м цикле

-lil- . . -DJ. 2 .- - - 2

.тота следования импульсов на выходе делителя 4 равна fo(l-t-j4k,+ l/Jk). В сумматоре-вычитателе 32 номер 1 цикла второго этапа, соответствующий коду на выходе счетчика 15, складывается со значением J, хранящимся после первого этапа в регистре 30 Чтобы обеспечить неньший, чем на первом этапе шаг dK, вес кода счетчика 15 меньше веса кода, хранимого в регист Zk

ние кода 1 счетчика 15 производится в сумматоре-вычитателе 32 Емкость счетчика 15 циклов второго этапа равг. г на ---.

Работа устройства на втором этапе, как и на первом, протекает цикла ми В первых Г1-/2 циклах второго этапа по окончании каждого цикла импульс с выхода триггера 18 через элемент И 28 поступает на счетчик 15 Код состояния 1 счетчика 15 с соответствующим весом поступает на вход сумматора-вычитателя 32, работающего в режиме сложения, благодаря поступающему на управляющий вход последнего уровня логической l с прямого выхода триггера 19„ На другой вход сумматора-вычитателя 32 с выхода ре

25

066028

анализатор, состоящий из элемента И 25 и блока 22, заносит в регистр 29 максимальную из множества вычис- g лепных за 1 циклов ординат БКФ, а в регистр 31 через элемент И 28 - код с выхода сумматора-вычитателя 32,

Пт

По окончании первых циклов

10 второго этапа счетчик 15 переполняется импульсами от триггера 18, импульс с его выхода поступает на счетный вход триггера 19, и последний переходит в состояние I Сигнал с

15 его прямого выхода устанавливает

арифметический блок 32 в режим вычи- . Благодаря этому на следующих

щ циклах второго этапа частота

20 следования импульсов на выходе делителя Д изменяется в пределах f„(1 + + j/3k, - /l/dkj). В остальном работа устройства протекает аналогично

П1

первым --циклам второго этапа.

По окончании второго этапа в регистр 3 хранится код, определяющий коэффициент деления частоты следования импульсов, при котором МВИ скомпенсировано с

. ,dk7 точностью ± ---

После

последнего цикла второго этапа счетчик 15 снова переполняется и возвращает триггер 19 в состояние О. Сигнал с выхода триггера 19 поступает на вход установки 1 триггера 20 и устанавливает его в состояние I. Открывается элемент И 24, а мультиплексор 11 переводится в состояние,

при котором выход регистра 31 подключается к управляющему входу делителя 4 частоты. Теперь дискретизация процесса у происходит с той частотой, которая необходима для компенсации

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Разделитель коррелограмм | 1988 |

|

SU1506453A1 |

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

| Разделитель коррелограмм | 1988 |

|

SU1624478A1 |

| Коррелометр | 1979 |

|

SU783799A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Цифровой коррелятор | 1990 |

|

SU1727133A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ДИФФЕРЕНЦИРУЮЩЕЕ И ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2535467C1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

Изобретение относится к вычис лительной технике и может быть использовано для определения значения и аргумента максимума взаимной корреляционной функции между случайными сигналами, подвергнутыми взаимному масштабно-временному искажению. Целью изобретения является повьпаение быстродействия устройства. С этой целью в устройство, содержащее генератор тактовьк импульсов, первый и второй делители частоты, управляемый делитель частоты, первый и второй аналого-цифровые преобразователи, первый триггер, первый, второй, третий и четвертый элементы И, первый счетчик, коррелятор, экстремальный анализатор, блок сравнения, первый и второй регистры, введены первый и второй блоки памяти, первый, второй, третий, четвертый мультиплексоры, второй, третий счетчики, второй, т.ре- тий и четвертый триггеры, пятый и шестой элементы И, третий регистр и сумматор-вычитатель. 1 ил. (Л

гистра 30 поступает код j номера цик- 45 его МВИ,

ла максимальной ВКФ, найденной на пер- Результаты измерения ВКФ поступают теперь от коррелятора 16 на выход устройства через элемент И 24 и могут использоваться для последующего 50 анализа до тех пор, пока значение коэффициента МВИ не изменится. Когда это произойдет, следует подать сигнал Запуск, и устройство в течение П1+П1. циклов настроится на новое 55 значение коэффициента МЕИ,

Устройство может работать и при противоположном знаке МВИ, но тогда следует сигналы х и у поменять местами, а также при неизвестном направвом этапе„ С выхода сумматора-вычитателя 32 код, определяющий коэффициент деления частоты следования импульсов, через мультиплексоры 12 и II поступает на управляющий вход делителя 4 частотЫо Благодаря этому частота дискретизации АЦП 6 становится равной fjj (1+J7) k ,+ /l/4kj). Коррелятор 16 определяет ВКФ выборки входных реализаций, записанных в блоках 7 и 8 памяти. Экстремальный анализатор 21 вьшеляет максимальную ординату очередной ВКФ, а экстремальный

лении МВИ, однако в последнем случае режим настройки продолжается ( п) циклов

Устройство выгодно отличается от известного по быстродействию. Если в предлагаемом устройстве требуется мякс , dki

Z)ki

,

циклов насройки для компенсации МВИ с шагом

,. k/ипкс

uki, то в известном k МО КС

Як 7п чения такого же результата. При

ak

ЦИКЛОВ ДЛЯ полу п 10

предлагаемое устройст15

во работает быстрее в 5 раз Формула изобретения

Устройство для определения взаимной корреляционной функции, содержащее генератор тактовых импульсов, выход которого подключен к входам первого и второго делителей частоты и к входу делимого управляемого делителя частоты, выходы первого делителя частоты и управляемого делителя частоты соединены соответственно с тактовыми входами первого и второго аналого-цифровых преобразователей, первый триггер, инверсный выход которого подключен к первому входу первого элемента И, выход которого соединен со счетным входом первого счетчика импульсов, выход которого подключен к единичному входу первого триггера, нулевой вход которого объединен с входом запуска генератора тактовых импульсов и является тактовым входом устройства, коррелятор, выход которого соединен с первым входом второго элемента И и с входом экстремального анализатора, выход которого подключен к первому входу бло20

мационными входами устройства, выход второго элемента И является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены первый, второй блоки памяти, пе()вый, второй, третий, четвертый мультиплексоры, второй, третий счетчики импуль- 10 сов, второй, третий, четвертый триггеры, пятый, шестой элементы И, третий регистр и сумматор-вычитатель, при этом выход первого делителя частоты подключен к первой группе информационных входов первого мультиплексора, вторая группа информационных входов которого объединена с первой группой информационных входов второго мультиплексора 4 соединена с выходом второго делителя частоты, вторая группа информационных входов второго мультиплексора подключена к выходам управляемого делителя частоты, вход задания коэффициента деления которого соединен с выходом третьего мультиплексора, первая группа информационных входов которого подключена к выходам четвертого мультиплексора, первая группа информационных входов которого объединена с первым входом пятого элемента И и подключена к выходу сумматора-вычитателя, управляющие входы первого, второго мультиплексоров объединены с первым входом шестого элемента И и соединены с прямым выходом второго триггера, вход установки в 1 которого подключен к выходу второго счетчика, счетный вход которого объединен с адресным входом первого блока памяти и соединен с выходом мультиплексора, информационный вход которого подключен к выходу первого аналого-цифрового преобразователя, выход первого

25

30

35

40

ка сравнения и к первому входу третье- блока памяти соединен с первым информационным в ходом коррелятора, второй информационный вход которого подключен к выходу второго блока памяти, информационный вход которого соединен

го элемента И, выход которого соединен с информационным входом первого регистра, выход которого подключен к второму входу блока сравнения, выход которого соединен с вторым входом третьего элемента И и с первым входом четвертого элемента И, второй вход которого подключен к выходу первого счетчика, выход четвертого элемента И соединен с информационным входом второго регистра, информационные входы первого и второго аналого- цифровых преобразователей являются соответственно первым и вторым инфор5

0

мационными входами устройства, выход второго элемента И является выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены первый, второй блоки памяти, пе()вый, второй, третий, четвертый мультиплексоры, второй, третий счетчики импуль- сов, второй, третий, четвертый триггеры, пятый, шестой элементы И, третий регистр и сумматор-вычитатель, при этом выход первого делителя частоты подключен к первой группе информационных входов первого мультиплексора, вторая группа информационных входов которого объединена с первой группой информационных входов второго мультиплексора 4 соединена с выходом второго делителя частоты, вторая группа информационных входов второго мультиплексора подключена к выходам управляемого делителя частоты, вход задания коэффициента деления которого соединен с выходом третьего мультиплексора, первая группа информационных входов которого подключена к выходам четвертого мультиплексора, первая группа информационных входов которого объединена с первым входом пятого элемента И и подключена к выходу сумматора-вычитателя, управляющие входы первого, второго мультиплексоров объединены с первым входом шестого элемента И и соединены с прямым выходом второго триггера, вход установки в 1 которого подключен к выходу второго счетчика, счетный вход которого объединен с адресным входом первого блока памяти и соединен с выходом мультиплексора, информационный вход которого подключен к выходу первого аналого-цифрового преобразователя, выход первого

5

0

5

0

блока памяти соединен с первым информационным в ходом коррелятора, второй информационный вход которого подключен к выходу второго блока памяти, информационный вход которого соединен

с вьсходом второго аналого-цифрового преобразователя, адресный вход второго блока памяти подключен к выходу второго мультиплексора, управляющий вход четвертого мультиплексора объединен с вторым входом шестого элемента И и соединен с прямым выходом первого триггера, инверсный выход которого под1 -лючен к третьему входу четвертого элементу И, выход шестого

111406602

элемента И соединен со счетным входом третьего счетчика, выход переполнения которого подключен к единичному входу третьего триггера, прямой выход которого соединен с управляющим входом сумматора-вычитателя и с единичным входом четвертого триггера, выход которого подключен к второму входу вто12

второго и третьего триггеров и является тактовым входом устройства,информационный вьгход третьего счетчика подключен к первому информационному входу сумматора-вычитателя,второй информационный вход которого сое динен с выходом второго регистра, вы ход пятого элемента И подключен к

рого элемента И и к управляющему вхо- ю информационному входу третьего региду третьего мультиплексора, выход блока сравнения соединен с вторым входом пятого элемента И, третий вход которого подключен к инверсному выходу четвертого триггера, нулевой вход ко-15 торого объединен с нулевьми входами

стра, выход которого соединен с второй группой информационных входов третьего мультиплексора, вторая груп па информационных входов четвертого мультиплексора соединена с информационными выходами первого счетчика.

12

второго и третьего триггеров и является тактовым входом устройства,информационный вьгход третьего счетчика подключен к первому информационному входу сумматора-вычитателя,второй информационный вход которого соединен с выходом второго регистра, выход пятого элемента И подключен к

информационному входу третьего регистра, выход которого соединен с второй группой информационных входов третьего мультиплексора, вторая группа информационных входов четвертого мультиплексора соединена с информационными выходами первого счетчика.

| Устройство для определения взаимной корреляционной функции | 1977 |

|

SU691866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| I | |||

Авторы

Даты

1988-06-30—Публикация

1986-11-17—Подача