U.

QS

О

со со

ю ел

Изобретение относится к информационно-измерительной технике, предназначено для цифровой регистрации однократных высокочастотных электрических сигналов и может быть использовано в информационно-измерительных системах и цифровых осциллографах.

Известно устройство для регистрации информации, содержащее буферный усилитель, аналого-цифровой преобразователь (АЦП), оперативное запоминающее устройство (ОЗУ), регистр, счетчик адреса и генератор тактовых импульсов.

Недостатками указанного регистратора являются низкая точность регистрации, обусловленная ограниченной разрядностью квантования, особенно высокочастотных сигналов, и необходимый большой объем памяти, пропорциональный разрядности.

Известен также регистратор , содержащий буферный усилитель, параллельный АЦП, оперативное запоминающее устройство, счетчик адреса, цифроаналоговый преобразователь (ЦАП).

Однако его точность регистрации (п- кратное повторение числа уровней квантования) ограничена разрешающей способностью компараторов и нелинейностью характеристики преобразования АЦП, а также большой динамической погрешностью преобразования, обусловленной п- кратным повторением квантования. Объем памяти пропорционален числу разрядов и количеству повторений квантования.

Наиболее близким к предлагаемому по технической сущности является устройство для регистрации информации, содержащее буферный усилитель, параллельный АЦП, ОЗУ, ЦАП, генератор тактовых импульсов, счетчик адреса, компаратор кода, триггеры, перестраиваемый делитель частоты.

Недостатком известного устройства являются низкая точность регистрации больших по амплитуде значений сигнала из-за постоя иного числа разрядов во всех автоматически переключаемых поддиапазонах .чувствительности и большой объем памяти, обусловленный необходимостью запоминания текущего поддиапазона.

Точность цифровых регистраторов определяется прежде всего числом разрядов ki, представляющих мгновенное значение входного сигнала. В свою очередь, точность определяет объем памяти, необходимый для записи исследуемого сигнала, причем чем выше точность регистрации, тем больший объем памяти требуется.

С другой стороны, для регистрации высокочастотных сигналов необходимы скоростные АЦП, т.е. параллельные АЦП, Однако эти преобразователи характеризуются ограниченной (до 8-10) разрядностью.

Увеличение разрядности параллельных

АЦП ограничено числом параллельных компараторов (n 2k - 1), определяющим входные параметры (входная емкость, сопротивление) и потреблением мощности, а также сложностью дешифрации унитарного кода в двоичный, сопровождающейся увеличением времени и увеличением потребляемой мощности.

Повышение точности регистрации высокочастотных сигналов в широком динамическом диапазоне и уменьшение объема требующейся при этом памяти может быть обеспечено путем квантования параллельным АЦП приращения (изменения) входного сигнала относительно предыдущего отсчета

и записи цифрового значения этого приращения в память.

Цель изобретения - повышение точности регистрации высокочастотных сигналов

и уменьшение используемого объема памяти.

Поставленная цель достигается тем, что. в устройство для регистрации информации, содержащее буферный усилитель, вход которого является входом устройства, АЦП, ЦАП, блок памяти, к адресному входу которого подключен счетчик адреса, дополнительно введены дифференциальный усилитель, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ НЕ,

два мультиплексора, арифметико-логический блок, два регистра, блок управления и второй буферный усилитель, причем выходы первого и второго буферных усилителей подключены к входам дифференциального

усилителя, выход которого подключен х информационному входу АЦП, выходом соединенного через элемент ИСКЛЮЧАЮЩЕЕ ИЛ И-НЕ, на управляющий вход которого с выхода АЦП подключен старший разряд, с первым информационным входом первого мультиплексора и информационным входом блока памяти, адресный вход которого соединен со счетчиком адреса, а выход подключен к второму информационному входу

первого мультиплексора, выход которого соединен с первым входом арифметико-логического блока, причем старший разряд с выхода мультиплексора подключен к управляющему входу арифметико-логического

блока, выход которого подключен к первому информационному входу второго мультиплексора, второй вход которого подключен к выходу второго регистра, а выход мультиплексора соединен с входом первого регистра, выход которого является выходом

устройства и подключен также к второму входу арифметико-логического блока, к входу второго регистра, к входу блока управления и входу ЦАП, выходом подключенного к входу второго буферного усилителя, кроме того, первый выход блока управления подключен к входу установки счетчика адреса, выход которого соединен с вторым входом блока управления, второй выход которого подключен к стробирующему входу АЦП, третий - к входу блока памяти и первого мультиплексора, четвертый - к входу первого регистра,, пятый - к входу второго мульт- плексора, а шестой - к входу второго регистра.

Кроме того, блок управления содержит компаратор кода, три триггера, формирователь импульсов, генератор тактовых импульсов, перестраиваемый делитель частоты, инвертор, пять логических элементов И, два логических элемента ИЛИ и пульт управления, причем выход Уровень пульта управления подключен к первому входу компаратора кода, второй вход которого является входом информации блока управления, выход Пуск пульта управления подключен к входу формирователя импульсов, выход Частота подключен к перестра- иваемому делителю частоты, выход ЗП/СЧТ подключен к инвертору, первому, второму и третьему элементам И, а также является третьим выходом блока управления, выход формирователя импульсов подключен к входам установки второго и третьего триггера, выход генератора тактовых импульсов соединен с входом перестраиваемого делителя частоты, выход которого подключен к компаратору кода, третьему триггеру, первому, третьему и четвертому элементам И, выход компаратора кода подключен к входам первого триггера, второго .элемента И, выход которого является шестым выходом блока управления, входы сброса второго и первого триггеров объединены и являются вторым входом блока уп- равльния, выход первого триггера соединен с входом первого элемента И, выход второго триггера подключен к первому и четвертому элементам И, прямой выход третьего триггера подключен к одному входу пятого элемента И, другой вход которого объединен с входом четвертого элемента И и подключен к выходу инвертора, выход пятого элемента И подключен к входу первого элемента ИЛИ и является пятым выходом блока управления, выходы первого и четвертого элементов И подключены к входам второго элемента ИЛИ, выход которого является первым выходом блока управления, выход третьего элемента И подключен к входу первого элемента ИЛИ и является вторым выходом блока управления, а выход первого элемента ИЛИ является четвертым выходом блока управления.

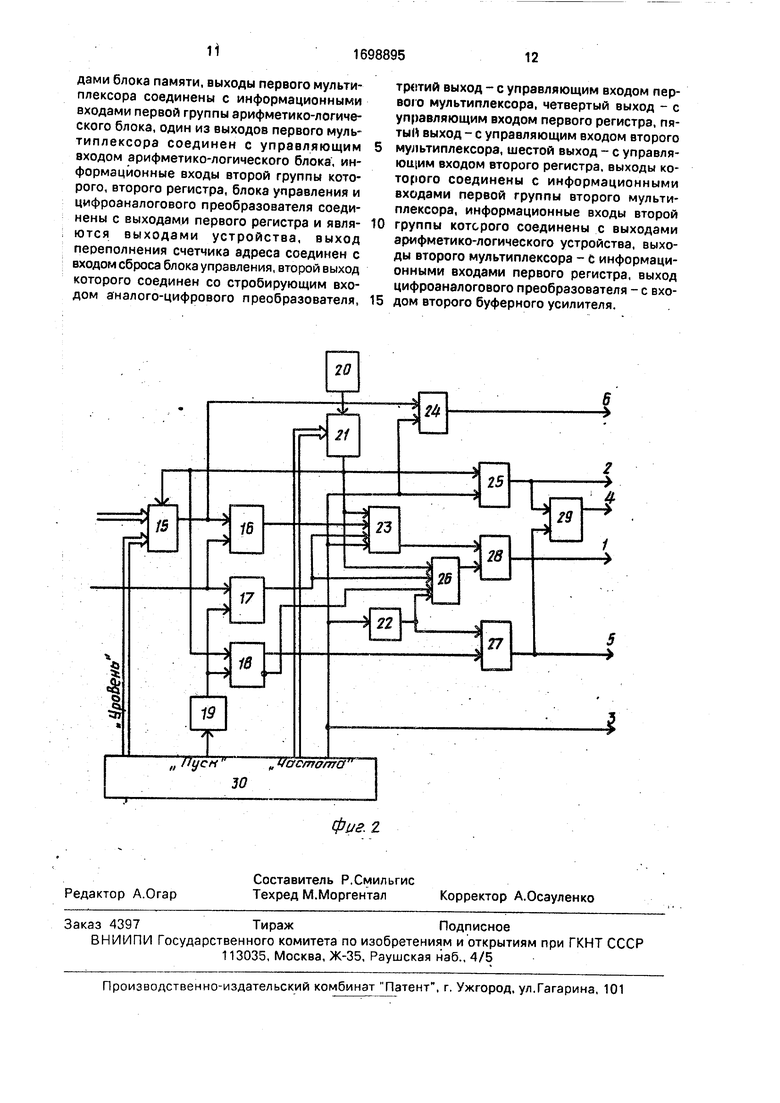

На фиг. 1 представлена функциональная схема устройства для регистрации информации; на фиг. 2 - структурная схема блока управления.

Устройство для регистрации информа0 ции содержит первый буферный усилитель 1, дифференциальный усилитель 2, АЦП 3, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 4, первый мультиплексор 5, арифметико-логический блок 6, второй мультиплексор 7,

5 первый регистр 8, блок 9 управления, второй регистр 10, ЦАП 11, второй буферный усилитель 12, счетчик 13 адреса и блок памяти - ОЗУ 14. Входом устройства является вход буферного усилителя 1. Выходы буфер0 ных усилителей 1 и 12 подключены к входам дифференциального усилителя 2, выход которого подключен к информационному входу параллельного АЦП 3. Выход параллельного АЦП 3 через логический эле5 мент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 4, входом управления которого является старший разряде выхода преобразователя 3, подключен к информационным входам мультиплексора 5 и ОЗУ 14. Адресный вход ОЗУ 14 соединен

0 со счетчиком 13 адреса, а выход подключен к второму информационному входу мультиплексора 5. Выход мультиплексора 5 соединен с первым информационным входом блока 6, к входу управления которого под5 ключей старший разряд с выхода мульти- . плексора 5. Выход блока 6 подключен к первому информационному входу мультиплексора 7, второй информационный вход которого соединен с выходом регистра 10, а

0 выход мультиплексора 7 подключен к входу регистра 8, выход которого подключен к информационным входам ЦАП 11, блока 9 управления, второго регистра 10, второму. входу блока б и является выходом устройст5 ва. Выход ЦАП 11 подключен к входу буферного усилителя 12. Кроме того, второй вход блока 9 управления соединен с выходом счетчика 13 адреса. Первый выход блока 9 управления подключен к входу установки

0 счетчика 13 адреса, второй выход - к стробирующему входу параллельного АЦП 3, третий - к управляющим входам мультиплексора 5 и ОЗУ 14, четвертый - к регистру 8, пятый - к мультиплексору 7, а шестой - к

5 регистру 10.

При этом блок управления содержит компаратор 15 кода, три триггера 16-18, формирователь 19 импульсов, генератор 20 тактовых импульсов, перестраиваемый делитель 21 частоты, инвертор 22, пять логических элементов И 23-27, два логических элемента ИЛИ 28 и 29 1 и пульт 30 управления. Выход Уровень пульта 30 управления подключен к первому входу компаратора 15 кода, второй вход которого является входом информации блока 9 управления. Выход Пуск пульта 9 управления подключен к входу формирователя 19 импульсов, выход Частота подключен к перестраиваемому делителю 21 частоты, выход ЗП/СЧТ под-, ключей к инвертору 22, элементам И 23-25, а также является третьим выходом блока 9 управления. Выход формирователя 19 импульсов подключен к входам установки триггеров 17 и 18. Выход генератора 20 тактовых импульсов соединен с входом перестраиваемого делителя 21 частоты, выход которого подключен к компаратору 15 кода, триггеру 18, элементам И 23, 25 и 26. Выход компаратора 15 кода подключен к входам триггера 16, элемента И 24, выход которого является шестым выходом блока 9 управления. Входы сброса триггеров 16 и 17 объединены и являются вторым входом блока 9 управления. Выход триггера 16 соединен с входом элемента И 23 выход триггера 17 подключен к элементам И 23 и 26, прямой выход триггера 18 подключен к одному входу элемента И 27, другой вход которого объединен с входом элемента И 26 и подключен к выходу инвертора 22. Выход элемента И 27 подключен к первому входу элемента И 29 и является пятым выходом блока 9 управления. Выходы элементов И 23 и 26 подклю- чены к входам элемента И 28, выход которого является первым выходом блока 9 управления. Выход элемента И 25 подключен к входу элемента ИЛИ 29 и является вторым выходом блока 9 управления, а выход элемента ИЛИ 29 является четвертым выходом блока 9 управления.

Устройство работает следующим образом.

В регистраторе для представления входного сигнала Ux в последовательность мгновенных цифровых его значений UQI (отсчеты) используется квантование приращения (изменения) входного сигнала относительно предыдущего отсчета. Входной сигнал Ux через буферный усилитель 1 поступает на один вход дифференциального усилителя 2. Посредством буферного усилителя 1 ограничивается частотный спектр сигнала Ux. На второй вход дифференциального усилителя 2 подается компенсирующее значение напряжения UKIS сформированное ЦАП 11 и буферным усилителем 12 от отсчета, полученного в предыдущем такте преобразования. Разность Up входного

сигнала Ux и компенсирующего напряжения UK выхода усилителя 2 поступает на параллельный АЦП 3 и преобразуется в соответствующий код. Старший разряд этого кода

служит управляющим сигналом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 4, посредством, которого код результата квантования (кроме старшего разряда) инвертируется, если старший разряд равен О, и не инвертируется.еслион равен Г, т.е. результат инвертируется при входном сигнале Ux меньше компенсирующего значения UK и не инвертируется при Ux UK. Текущий отсчет фор- мируется в зависимости от старшего

разряда как добавление или вычитание полученного результата квантования к предыдущему значению отсчета, причем добавляется в случае, когда старший разряд равен Г, и вычитается в случае 0й.

Слежение за сигналом Ux (суммирование - вычитание) осуществляется посредством арифметико-логического блока 6 и регистра 8. Текущее 1-е мгновенное значение UQI преобразуемого сигнала хранится в

регистре 8.

Работу регистратора можно разделить на два режима: режим регистрации информации (запись - ЗП) и режим считывания накопленной информации (СЧТ). Эти режимы выбираются переключателем ЗП/СЧТ на пульте 30 управления, например переключателем с фиксацией типа П2К.

Перед регистрацией и считыванием устанавливаются параметры соответствующего режима: частота преобразования и уровень пуска для режима регистрации и частота считывания для режима считывания. При этом уровень пуска устанавливается кодовым переключателем Уровень на

пульте 30 управления, а частота преобразования или считывания - кодовым переключателем Частота на пульте 30 управления. Могут быть использованы кодовые переключатели, например, типа ПП10-ХВ.

в режиме регистрации выбранная частота преобразования, задаваемая генератором 20 тактовых импульсов и формируемая перестраиваемым делителем 21 частоты, поступает через логический элемент И 25 на

параллельный АЦП 3 и далее через логический элемент ИЛИ 29 на регистр 8, осуществляя представление входного сигнала в последовательность отсчетов UQI. Перестраиваемый делитель 21 частоты может

быть реализован, например, на микросхемах К155ИЕ8. Полученные отсчеты UQI поступают в блок 9 управления и в регистр 10. При нажатии на пульте 30 управления кнопки Пуск формирователь 19 импульсов

вырабатывает один импульс, который устанавливает в единичное состояние триггеры 17 и 18, После превышения входным сигналом выбранного уровня пуска компаратор 15 кода вырабатывает импульс, устанавливающий в единичное состояние триггер 16, записывающий через логический элемент И 24 значение текущего отсчет Ucmr на регистре 10.

Состояние триггеров 16 и 17 обеспечивает прохождение импульсов частоты преобразования через логический элемент И 23 и далее через логический элемент ИЛИ 28 к счетчику 13 адреса, устанавливая адрес ОЗУ 14. Начинается регистрация (запись) приращений со знаком, определяемым старшим разрядом в ОЗУ 14, после заполнения которого счетчик 13 адреса вырабатывает сигнал конца. Этот сигнал сбрасывает триггеры 16и 17 и запрещает прохождение импульсов к сметчику 13 адреса. Регистрация информации прекращается. При этом во время регистрации в ОЗУ 14 накапливается информация только об изменении входного сигнала относительно предыдущего отсчета, а не полностью о всем отсчете UQ, начальныйотсчета UQH запоминается в регистре 10.

В качестве кнопки Пуск может быть использована, например, кнопка типа КМД1-1.

При считывании накопленной информации после нажатия кнопки Пуск на пульте 30 управления формирователь 19.формиру- ет импульс, под воздействием которого в единичное состояние устанавливаются триггеры 17 и 18. В первом такте частоты считывания (задается триггером 18) через логический элемент И 27 посредством мультиплексора 7 в регистр 8 переписывается из регистра 10 предыдущий отсчет начала регистрации UQH. Начиная с второго такта частоты считывания, импульсы выбранной частоты через логический элемент И 26,ло- гический элемент ИЛИ 28 поступают на счетчик 13 адреса, посредством которого формируется адрес ОЗУ 14, с которого считывается последовательность значений записанного в ОЗУ 14 сигнала. Каждый считываемый отсчет через мультиплексор 5 поступает к арифметико-логическому блоку 6, посредством которого в зависимости от старшего разряда суммируется или вычитается из предыдущего отсчета, хранящегося в регистре 8. По окончании считывания счетчик 13 адреса вырабатывает импульс конца, который сбрасывает триггер 17, прекращая считывание.

Введение новых блоков и связей увеличивает точность регистрации высокочастотных сигналов, при этом уменьшается объем хранимой информации, что обеспечивается

за счет того, что параллельным АЦП квантуется только изменение входного сигнала относительно предыдущего его отсчета и значение этого изменения записывается в память. Предлагаемый подход цифровой ре0 гистрации используется в цифровых осциллографах и информационно-измерительных системах при исследовании быстропротека- ющих необратимых процессов.

Предлагаемая структура реализована в

5 регистрирующем системном модуле-макете АЦП-14 М и модуле ОЗУ-64 с разрядностью отсчета 14 бит, разрядностью значения приращения 8 бит, частотой квантования приращения 1 МГц и объемом памяти 65 536

0 девятиразрядных (8 бит и знак приращения) отсчетов. В качестве параллельного АЦП использованы две микросхемы К1107ПВ2 для квантования положительного и отрицательного приращения соответственно.

5 Формула изобретения

Устройство для регистрации информации, содержащее первый буферный усилитель, аналого-цифровой и цифроаналоговый преобразователи, блок памяти, блок управ0 ления, счетчик адреса, первый мультиплексор, первый выход блока управления соединен со счетным входом счетчика адреса, информационные выходы которого соединены с адресными входами блока памяти,

5 третий выход блока управления соединен с входом записи-чтения блока памяти, отличающееся тем, что, с целью повышения точности регистрации высокочастотных сигналов и уменьшения используемого объема

0 памяти, в устройство введены второй буферный и дифференциальный усилители, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, второй мультиплексор, арифметико-логический. блок, первый и второй регистры, вход пер5 вого буферного усилителя является входом устройства, выходы первого и второго буферных усилителей соединены с входами дифференциального усилителя, выход которого соединен с информационным входом

0 аналого-цифрового преобразователя, выходы группы которого соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ- НЕ, вторые входы которых соединены с выходом аналого-цифрового преобразова5 теля, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и аналого-цифрового преобразователя соединены с информационными входами блока памяти и первой группы первого мультиплексора, информационные входы второй группы которого соединены с выходами блока памяти, выходы первого мультиплексора соединены с информационными входами первой группы арифметико-логического блока, один из выходов первого мультиплексора соединен с управляющим входом арифметико-логического блока, информационные входы второй группы которого, второго регистра, блока управления и цифроаналогового преобразователя соединены с выходами первого регистра и являются выходами устройства, выход переполнения счетчика адреса соединен с входом сброса блока управления, второй выход которого соединен со стробирующим входом аналого-цифрового преобразователя,

третий выход - с управляющим входом первого мультиплексора, четвертый выход - с управляющим входом первого регистра, пятый выход-с управляющим входом второго

мультиплексора, шестой выход - с управляющим входом второго регистра, выходы которого соединены с информационными входами первой группы второго мультиплексора, информационные входы второй

группы которого соединены с выходами арифметико-логического устройства, выходы второго мультиплексора - fc информационными входами первого регистра, выход цифроаналогового преобразователя - с входом второго буферного усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ПАРАМЕТРОВ НИСТАГМА | 1992 |

|

RU2069966C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

Изобретение относится к информационно-измерительной технике, предназначено для цифровой регистрации однократных высокочастотных электрических сигналов и может быть использовано в информационно-измерительных системах и цифровых осциллографах. Изобретение позволяет повысить точность регистрации высокочастотных сигналов и уменьшить объем требующейся при этом памяти путем осуществления квантования параллельным АЦП 3 приращения (изменения) входного сигнала относительно предыдущего отсчета и записи цифрового значения этого приращения в память. Устройство содержит два буферных усилителя 1 и 12, дифференциальный усилитель 2, параллельный АЦП 3. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 4. блок 14 памяти, счетчик 13 адреса, два мультиплексора 5 и 7, арифметико-логический блок 6, два регистра 8 и 10 и блок 9 управления. 2 ил. Ё

„ /Гуси„ час/потсГ

30

| Устройство для ввода информации | 1983 |

|

SU1151946A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-15—Публикация

1989-12-29—Подача