ОЭ -U

О

о о

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник многочастотных сигналов | 1991 |

|

SU1775874A1 |

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1984 |

|

SU1841016A1 |

| Устройство приема дискретных частотных сигналов | 1988 |

|

SU1622953A1 |

| Приемник многочастотных сигналов | 1985 |

|

SU1284007A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1995 |

|

RU2096801C1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Акустооптический частотомер | 1988 |

|

SU1626092A1 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| СЕЙСМИЧЕСКОЕ УСТРОЙСТВО ОБНАРУЖЕНИЯ НАРУШИТЕЛЯ | 2004 |

|

RU2262744C1 |

Изобретение относится к радиотехнике и может быть использовано в радиотехнических устройствах различного назначения для выделения сигналов из помех. Цепью изобретения является увеличение отношения мощности полезного сигнала к мощности помех при переменном уровне шумов и прерывистых узкополосных помехах. Устройство подавления узкополосных помех содержит режектор- ный фильтр, первый элемент задержки, выходной сумматор, N частотных каналов, блок формирования сигналов управления тактами, полосовой фильтр, второй элемент задержки, ключ, амплитудный детектор, фильтр нижних частот, компаратор, счетчик, коммутатор, циф- роаналоговый преобразователь, сумматор, второй регистр, олок сравнения кодов, переключатель, первый регистр, блок формирования сигналов управления. Повышение отношения мощности полезного сигнала к мощности помех дос тигается за счет дополнительной селекции сигналов по длительности и предварительного (до прихода полезного сигнала) измерения уровня шума и максимальной длительности огибающей помехи. 3 ил. : i (Л

Изобретение относится к радиотехнике и может быть использовано в радиотехнических устройствах различного назначения для выделения сигналов из помех.

Цель изобретения - увеличение отношения мощности полезного сигнала к мощности помех при переменном уровне шумов и прерывистых узкополосных помехах.

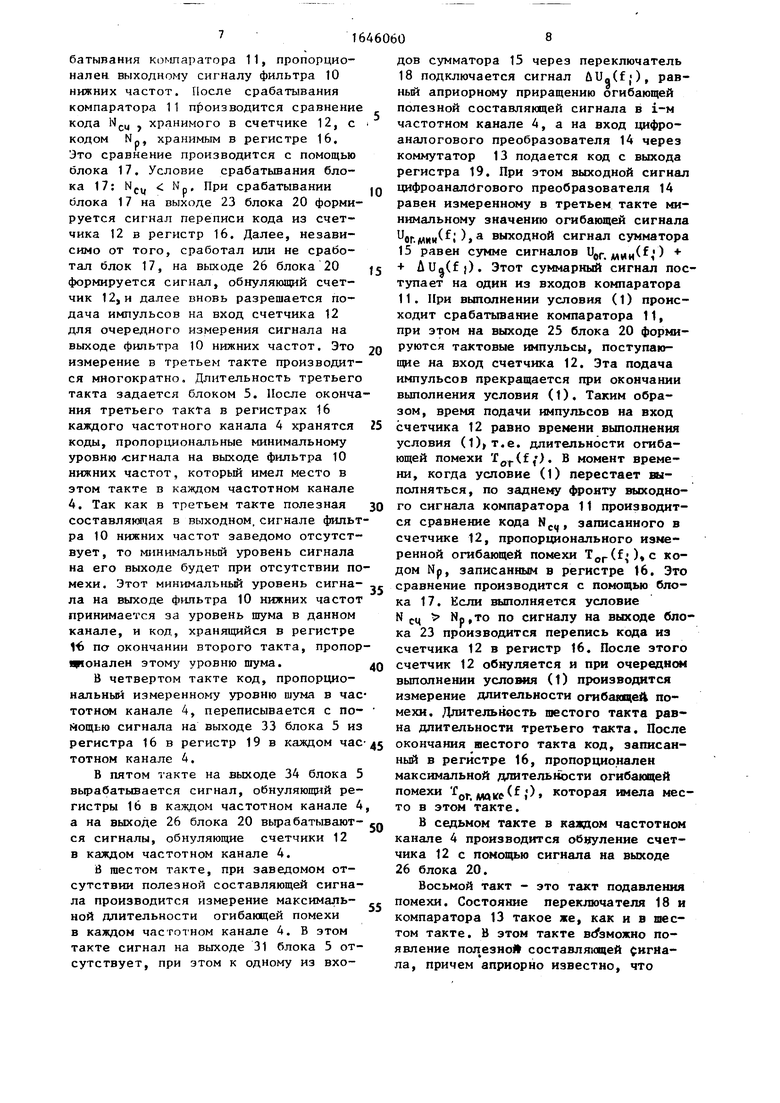

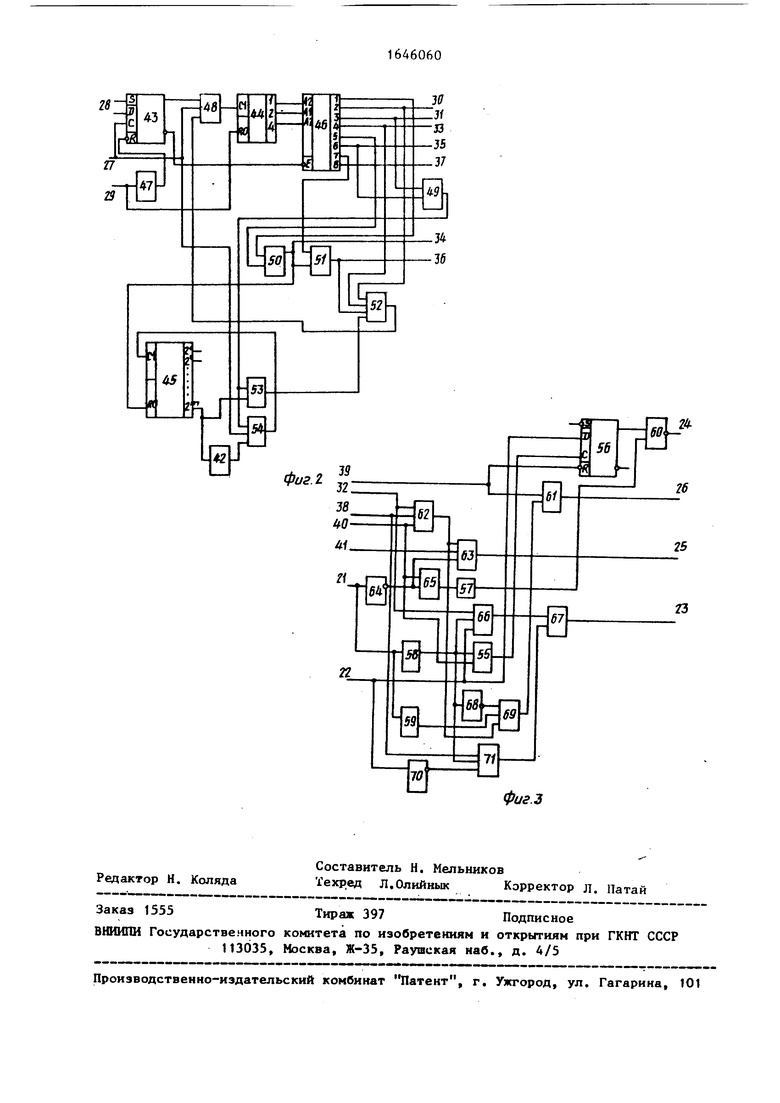

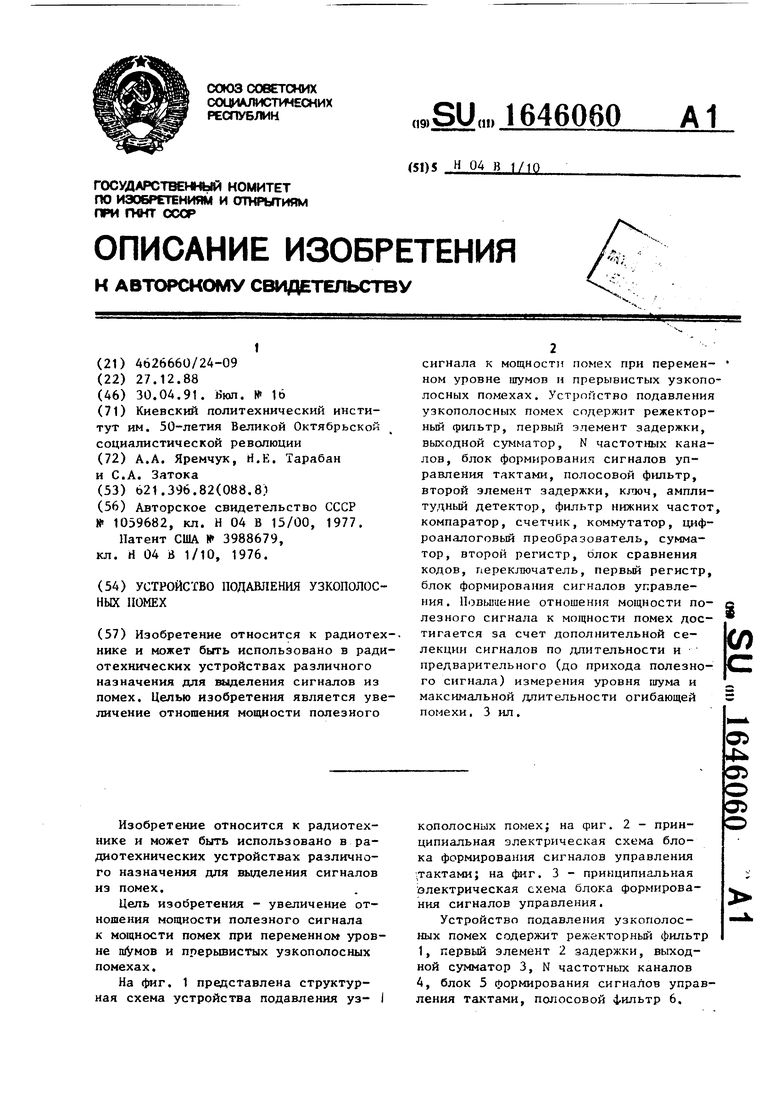

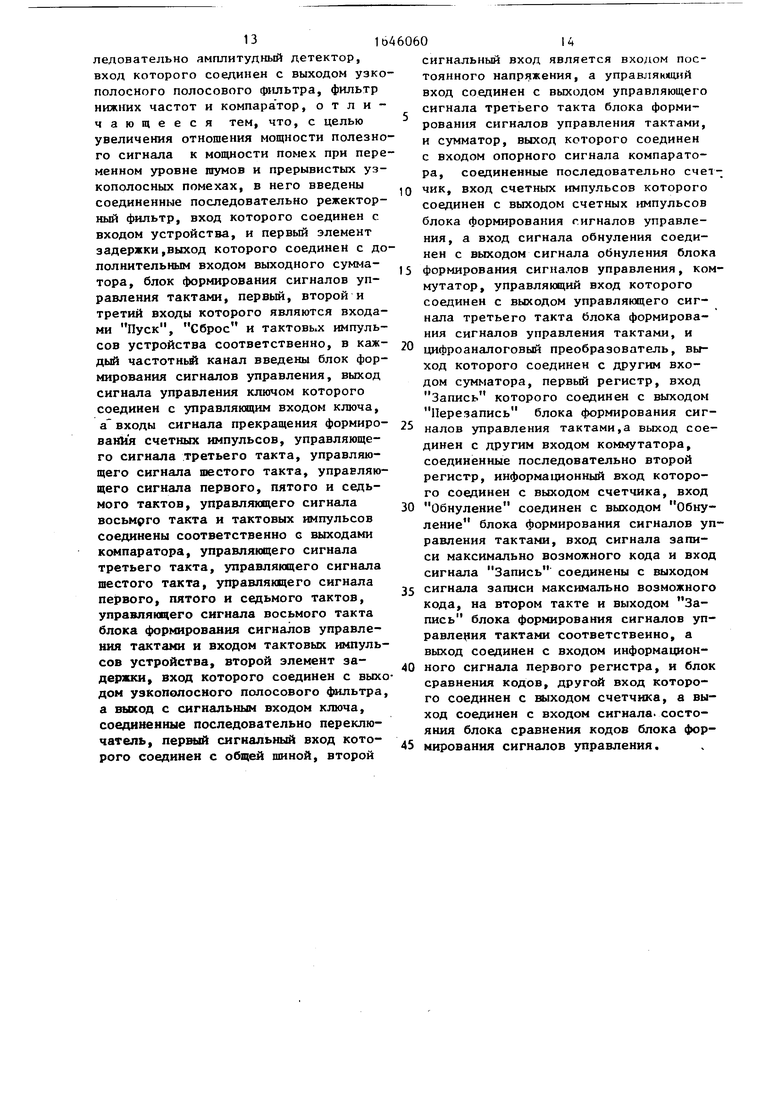

На фиг. 1 представлена структурная схема устройства подавления уз-

кополосных помех; на фиг. 2 - принципиальная электрическая схема блока формирования сигналов управления ;гактами; на фиг. 3 - принципиальная электрическая схема блока формирования сигналов управления.

Устройство подавления узкополосных помех содержит режекторный фильтр 1, первый элемент 2 задержки, выходной сумматор 3, N частотных каналов 4, блок 5 формирования сигналов управления тактами, полосовой фильтр 6.

второй -элемент 7 задержки, ключ 8, амплитудный детектор 9, фильтр 10 нижних частот, компаратор 11, счетчик 12, коммутатор 13, цифроанало-- говый преобразователь 14, сумматор 15, второй регистр 16, блок 17 сравнения кодов, переключатель 18, первый регистр 19, блок 20 формирования сигналов управления. Кроме того, на фиг. 1 обозначены вход 21 сигнала прекращения формирования счетных импульсов, вход 22 Пуск, выход 23 Запись, выход 24 сигнала управления ключом, выход 25 счетных импуль- сов, выход 26 сигнала обнуления блока 20 формирования сигналов управления, вход 27 тактовых импульсов устройства, вход 28 Пуск, вход 29 Сброс, выход 30 Запись, выход 31 управляющего сигнала третьего такта блока 5 формирования сигналов управления тактами, вход 32 управляющего сигнала третьего такта блока 20 формирования сигналов управления, выход 33 Перезапись, выход 34 Обнуление выход 35 управляющего сигнала шестог такта, выход 36 управляющего сигнала первого, пятого и седьмого тактов, выход 37 управляющего сигнала восьмо го тякта блока 5 формирования сигналов управления тактами,вход 38 управляющего сигнала шестого такта, вход 39 управляющего сигнала первого, пятого и седьмого тактов, вход 40 упра ляющего сигнала восьмого такта, вход 41 тактовых импульсов блока 20 формирования сигналов управления.

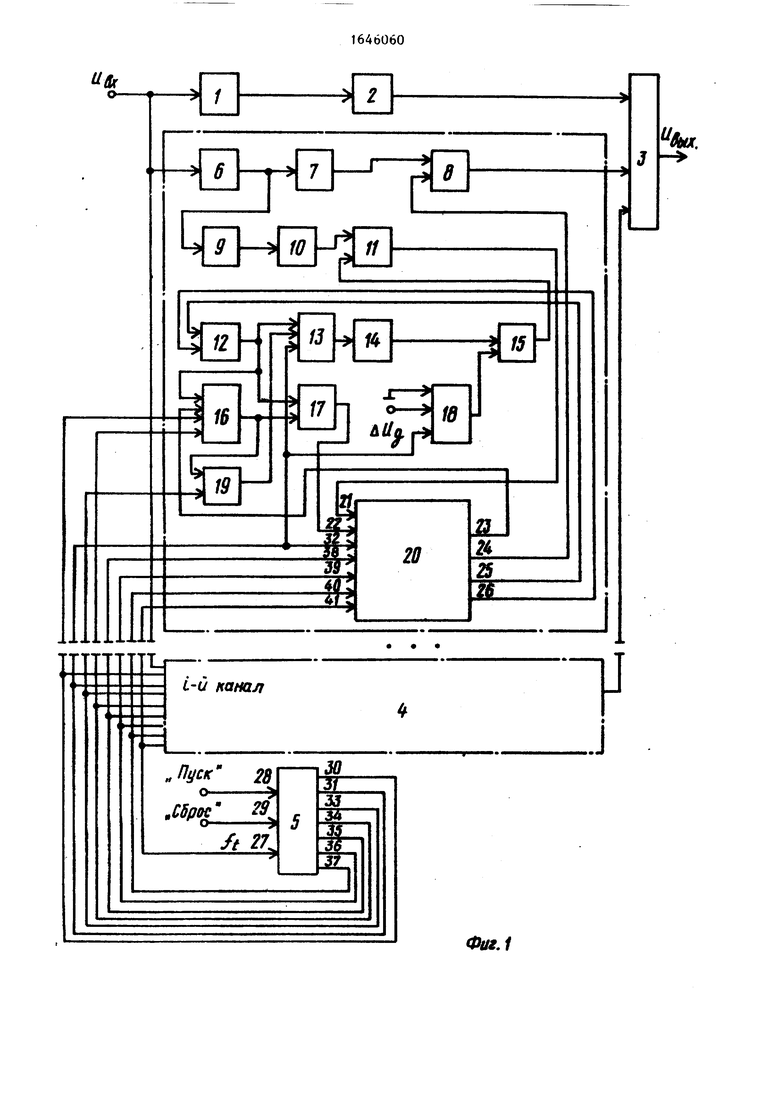

Блок 5 формирования сигналов управления тактами содержит первый эле мент ИЛИ 42, первый триггер 43, второй счетчик 44, третий счетчик 45, первый дешифратор 46, второй элемент ИЛИ 47, первый элемент И 48, третий элемент ИЛИ 49, четвертый элемент ИЛИ 50, пятый элемент ИЛИ 51, тестой элемент ИЛИ 52, второй элемент И 53, третий элемент И 54 и седьмой элемен ИЛИ 55.

Блок 20 формирования сигналов управления содержит второй триггер 56, третий элемент 57 задержки, первый и второй формирователи 58 и 59, элемент И-НЕ 60, седьмой элемент ИЛИ 61 восьмой элемент ИЛИ 62, пятый элемент И 63, девятый элемент ИЛИ 64, шестой элемент И 65, седьмой элемент И 66, десятый элемент ИЛИ 67, одиннадцатый элемент ИЛИ 68, восьмой эле

Q

о

мент И 69, инвертор 70, девятый элемент И 71 .

tla вход устройства могут воздействовать три сигнала: шум Оц,, помеха Ufl и полезный сигнал U. Известно, что длительность огибающей помехи го- раздо меньше длительности полезного сигнала, а амплитуда огибающей помехи гораздо больше амплитуды полезного сигнала. Частотные спектры полезной составляющей сигнала и помехи считаются известными, причем эти спектры перекрываются. Режекторный фильтр 1 имеет полосу пропускания, в которую не входит частотный спектр помехи. Частотный спектр полезной составляющей сигнала, перекрывающийся с частотным спектром помехи, распределяется на диапазоны, число которых N равно числу частотных каналов, а ширина диапазона определяется полосой пропускания полосового фильтра 6 каждого канала. Сигнал с выхода полосового фильтра 6 подается на вход ам- ;- плитудного детектора 9. На выходе фильтра 10 нижних частот, подключенного к выходу амплитудного детектора 9, выделяется огибающая выходного сигнала полосового фильтра 6.

Первоначально при заведомом отсутствии полезной составляющей сигнала производится измерение уровня шума на выходе фильтра 10 нижних частот каждого частотного канала 4. За уровень шума в i-м частотном канале 4 принимается минимальное значение огибающей сигнала Ц,ГАЛИМ(,) на выходе 1-го фильтра 10 нижних частот. Затем при заведомом отсутствии полезной составляющей сигнала в каждом частотном канале 4 производится измерение максимальной длительности огибающей помехи Тогма|(С(Ј ) на выходе 1-го - фильтра 10 нижних частот. Величина of. равна максимальному времени, в течение которого выходной сигнал фильтра 10 нижних частот превышал 0 СУММУ сигналов (f;) и AU.f;)t где UU(f;) - априорное приращение огибающей полезной составляющей сигнала в i-м частотном канале 4. Результаты измерения иогмии(Ј;) и ) в каждом частотном канале 4 запоминаются:

5

Далее, в каждом частотном канале 4 производится сравнение текущего

значения сигнала на выходе фильтра 10

нижних частот U

лов ljor. /иим f : нении условия

фНЧ

(f,) Aiyf-).

с суммой сигна- Ири выиолV f;

+ uVf.)

or, длим

(f;)

(О

начинается измерение длительности огибающей сигнала (t (f,) В момент времени, в который условие (1) перестает выполняться, измерение длительности огибающей прекращается. После этого производится сравнение результата измерения длительностей огибающей Tor(f; ) с величиной

foC. макс ется условие

(f;). Если при этом выполня-

ог

f;

or. MOkc

то это говорит о том, что на выходе фильтра 10 нижних частот имела место помеха. Если же условие (2) не выполняется, то на выходе фильтра 10 нижних частот имела место полезная составляющая сигнала.

Выходом устройства является выход выходного сумматора 3, к одному из входов которого через элемент 2 задержки подключен выход режекторного фильтра 1, а к остальным N входам через элементы 7 задержки и ключи 8 подключены выходы полосовых фильтров 6 соответствующих каналов 4. Ключ 8 в i-м канале предназначен для отключения выхода полосового фильтра 6 от входа выходного сумматора 3 в том случае, когда в данном частотном канале 4 имела место помеха. Время, в течение которого ключ 8 находится в разомкнутом состоянии, равняется измеренной длительности помехи Tor(f; ). Так как результат измерения Tor(f; ) и проверка условия (2) производятся после окончания воздействия помехи, то необходимо задержать прохождение сигнала с выхода полосового фильтра 6 на вход выходного сумматора 3 на время, равное времени измерения длительности огибающей сигнала Tor(f;) и времени проверки выполнения условия (2). Для этой цели в каждом частотном канале 4 имеется элемент 7 задержки, время задержки которого должно быть не менее, чем максимально возможная длительность полезной составляющей сигнала. Точно такое же время задержки должен иметь элемент 2 задержки, включенный между выходом режекторного фильтра 1 и входом выходного сумматора 3, т.е. сигнал с выхода режекторного фильтра 1 должен быть задержан на такое же время, на которое задерживаются сигналы с выходов полосовых фильтров 6.

Ю Синхронизация работы блоков устройства осуществляется с помощью блока 5. Кроме того, в каждом частотном канале 4 имеется блок 20.

Работа устройства распределена на

15 восемь тактов, длительность каждого из которых задается блоком 5.

Первый такт начинается при получении команды Пуск на вход 26 блока 5 В этом такте на выходе 34 блока 5 фор20 мируется сигнал, обнуляющий регистры (f.) (2) 16 во всех частотных каналах 4, а на

выходах 26 блоков 20 - сигналы, обнуляющие счетчики 12.

Во втором такте на выходе 30 блока

25 5 формируется сигнал, записывающий в регистры 16 всех частотных каналов 4 максимально возможный код.

В третьем такте при заведомом отсутствии полезной составляющей сигнаЗо ла производится измерение уровня шума в каждом частотном канале 4. Для этой цели с помощью сигнала на выходе 31 олока 5 через переключатель 18 заземляется один из входов сумматора 15, а через коммутатор 13 к входу цифро- аналогового преобразователя 14 подключается выход счетчика 12. На другой вход сумматора 15 поступает сигнал с выхода цифроаналогового преобразователя 14. Таким образом, выходной сигнал сумматора 15 UQ(f.;) пропорционален коду, записанному в счетчик 12. Этот сигнал поступает на один из входов компаратора 11. На второй вход

д5 компаратора 11 подается сигнал с выхода фильтра 10 нижних частот Uq,M4. При этом также на вход счетчика 12 поступают импульсы постоянной тактовой частоты с выхода 25 блока. При

50 этом на входе компаратора 11 формируется равномерно-ступенчатый сигнал U и сравнивается в компараторе 11

35

40

55

с сигналом UqjHt, (fj). При выполнении условия UcpH4(f;) с U0(f-) компаратор 11 срабатывает, при этом его выходной сигнал поступает на вход 21 олока 20 и поступление импульсов на вход счетчика 12 прекращается. Код, хранящийся в счетчике 12 после ераЗо

35

Зо

40

с сигналом UqjHt, (fj). При выполнении условия UcpH4(f;) с U0(f-) компаратор 11 срабатывает, при этом его выходной сигнал поступает на вход 21 олока 20 и поступление импульсов на вход счетчика 12 прекращается. Код, хранящийся в счетчике 12 после ера71646060

батывания компаратора 11, пропорционален выходному сигналу фильтра 10 нижних частот. После срабатывания компаратора 11 производится сравнение хранимого в счетчике 12, с хранимым в регистре 16.

помощью

блока 17. Условие срабатывания блока 17: Мсц N.. При срабатывании

8

кода Нсц ,

кодом Np,

Это сравнение производится с

10

20

25

30

блока 17 на выходе 23 блока 20 формируется сигнал переписи кода из счетчика 12 в регистр 16. Далее, независимо от того, сработал или не сработал блок 17, на выходе 26 блока 20 формируется сигнал, обнуляющий счетчик 12,и далее вновь разрешается подача импульсов на вход счетчика 12 для очередного измерения сигнала на выходе фильтра 10 нижних частот. Это измерение в третьем такте производится многократно. Длительность третьего такта задается блоком 5. После окончания третьего такта в регистрах 16 каждого частотного канала 4 хранятся коды, пропорциональные минимальному уровню -сигнала на выходе фильтра 10 нижних частот, который имел место в этом такте в каждом частотном канале 4. Так как в третьем такте полезная составляющая в выходном, сигнале фильтра 10 нижних частот заведомо отсутствует , то минимальный уровень сигнала на его выходе будет при отсутствии помехи. Этот минимальный уровень сигна- „ ла на выходе фильтра 10 нижних частот принимается за уровень шума в данном канале, и код, хранящийся в регистре Цэ по окончании второго такта, пропор- фюнален этому уровню шума. 0

В четвертом такте код, пропорциональный измеренному уровню шума в частотном канале 4, переписывается с по- мощью сигнала на выходе 33 блока 5 из регистра 16 в регистр тотном канале 4.

В пятом такте на выходе 34 блока 5 вырабатывается сигнал, обнуляющий регистры 16 в каждом частотном канале 4, а на выходе 26 блока 20 вырабатывают- ,д ся сигналы, обнуляющие счетчики 12 в каждом частотном канале 4.

В тестом такте, при заведомом отсутствии полезной составляющей сигнала производится измерение максимальной длительности огибающей помехи в каждом частотном канале 4. В этом такте сигнал на выходе 31 блока 5 отсутствует, при этом к одному из входов сумматора 15 через переключатель 18 подключается сигнал UU.(f;)f равный априорному приращению огибающей полезной составляющей сигнала в i-м частотном канале 4, а на вход цифро- аналогового преобразователя 14 через коммутатор 13 подается код с выхода регистра 19. При этом выходной сигнал цифроаналбгового преобразователя 14 равен измеренному в третьем такте минимальному значению огибающей сигнала Uor wtm(f; ), а выходной сигнал сумматора 15 равен сумме сигналов Uor. w«M(f,) + 15 + AUn(f j). Этот суммарный сигнал поступает на один из входов компаратора 11. При выполнении условия (1) происходит срабатывание компаратора 11, при этом на выходе 25 блока 20 формируются тактовые импульсы, поступающие на вход счетчика 12. Эта подача импульсов прекращается при окончании выполнения условия (1). Таким образом, время подачи импульсов на вход счетчика 12 равно времени выполнения условия (1)т.е. длительности огибающей помехи Tor(f(. В момент времени, когда условие (1) перестает выполняться, по заднему фронту выходного сигнала компаратора 11 производится сравнение кода NC)J, записанного в счетчике 12, пропорционального измеренной огибающей помехи Tor(f),c кодом Np, записанным в регистре 16. Это сравнение производится с помощью блока 17. Если выполняется условие N сч Np,To по сигналу на выходе блока 23 производится перепись кода из счетчика 12 в регистр 16. После этого счетчик 12 обнуляется и при очередном выполнении условия (1) производится измерение длительности огибающей помехи. Длительность шестого такта равна длительности третьего такта. После

19 в каждом час-Д5 окончания шестого такта код, записанный в регистре 16, пропорционален максимальной длительности огибающей помехи Tor (f;), которая имела место в этом такте.

В седьмом такте в каждом частотном канале 4 производится обнуление счетчика 12 с помощью сигнала на выходе 26 блока 20.

Восьмой такт - это такт подавления 55 помехи. Состояние переключателя 18 и компаратора 13 такое же, как и в шестом такте. В этом такте возможно появление полезно составляющей $игйа- ла, причем априорно известно, что

8

10

0

25

30

„ 0

дов сумматора 15 через переключатель 18 подключается сигнал UU.(f;)f равный априорному приращению огибающей полезной составляющей сигнала в i-м частотном канале 4, а на вход цифро- аналогового преобразователя 14 через коммутатор 13 подается код с выхода регистра 19. При этом выходной сигнал цифроаналбгового преобразователя 14 равен измеренному в третьем такте минимальному значению огибающей сигнала Uor wtm(f; ), а выходной сигнал сумматора 15 равен сумме сигналов Uor. w«M(f,) + 5 + AUn(f j). Этот суммарный сигнал поступает на один из входов компаратора 11. При выполнении условия (1) происходит срабатывание компаратора 11, при этом на выходе 25 блока 20 формируются тактовые импульсы, поступающие на вход счетчика 12. Эта подача импульсов прекращается при окончании выполнения условия (1). Таким образом, время подачи импульсов на вход счетчика 12 равно времени выполнения условия (1)т.е. длительности огибающей помехи Tor(f(. В момент времени, когда условие (1) перестает выполняться, по заднему фронту выходного сигнала компаратора 11 производитдлительность огибающей помехи гораздо меньше длительности огибающей полезной составляющей сигнала, а амплитуда огибающей помехи значительно превыша- , ет амплитуду огибающей полезной составляющей сигнала. В восьмом такте производится непрерывная проверка выполнения условия (1). При его выполнении начинается измерение времени ю выполнения условия (1), аналогично тому, как это производилось в шестом такте. В момент прекращения выполнения условия (1) происходит проверка выполнения условия (2) путем сравнения кодов, записанных в счетчике 12 и регистре 16. Если условие (2) выполняется, т.е. имела место помеха, то на выходе 24 блока 20 вырабатывается сигнал, закрывающий ключ 8 в i-м час- 20 тотном канале 4 и запрещающий прохождение сигнала с выхода полосового фильтра 6 на выход устройства в течение времени, равного длительности помехи.

Сигнал, закрывающий ключ 8, форми- .руется с задержкой, равной времени задержки элемента 7. Если ЖР условие (2) не выполняется, то имела место полезная составляющая сигнала, при этом ключ 8 не закрывается, и сигнал с выхода полосового фильтра 6 поступает на выход устройства. Восьмой такт длится до тех пор, пока на вход 29 блока 5 не будет подан сигнал Сброс.

Блок 5 работает следующим образом.

Триггер 43 совместно с элементом ИЛИ 47 обеспечивает запуск устройства. При подаче сигнала Пуск на вход 28 триггера 43 последний устанавливается в единицу передним фронтом ближайшего тактового импульса, поступившего на вход 27. Установка триггера 43 в нуль

числу тактов работы устройства. Длительность первого, второго, четвертого, пятого и седьмого тактов равна одному периоду тактовой частоты, что обеспечивается разрешением, поступающим на один из входов элемента 48 через элементы ИЛИ 50 - 52. Длительность третьего и шестого тактов рав- , где TT - период тактона Тг 2

чика 45. Счетчик 45 обнуляется в первом и пятом тактах работы сигналом с выхода элемента ИЛИ 50. Подача такто15 вых импульсов на вход счетчика 45 раз решается в третьем и шестом тактах с помощью элементов 49,54,42 и прекращается в момент появления сигнала на выходе старшего (2 ; разряда счетчика 45 с момента подачи тактовых импульсов на вход счетчика 44 с помощью элементов 49, 53, 42 и 48. При появлении сигнала на выходе старшего (2 ) разряда счетчика 45 запрет на подачу

25 тактовых импульсов на вход счетчика 44 снимается.

На выходе 34 блока 5 формируется сигнал в первом и пятом тактах, который поступает в регистры 16 и произ30 водит их обнуление,

На выходе 36 блока 5 формируется сигнал в первом,пятом и седьмом тактах, который поступает в блоки 20 на вход 39, где формируется сигнал 26

35 (сброса счетчиков 12.

Сигнал на выходе 30 блока 5 формируется во втором такте и служит для записи в регистр 16 максимально возможных кодов.

Сигнал на выходе 31 блока 5 формируется в третьем такте, поступает на управляющие входы переключателей 18 в каждом канале, обеспечивая подключе40

производится сигналом Сброс, посту- 45 ние °ДНОГО из входов сумматора 15 к пившим на вход 29. Счетчик 44 совмест- нулевой шине. Этот же сигнал поступа- но с дешифратором 46 формируют сигнал на выходе блока 5 в определенной последовательности. Счетчик 44 обнуляет50

ся сигналом Сброс на входе 29, .При установке триггера 43 в единицу по одному из выходов открывается элемент И 48, разрешая подачу . тактовых импульсов с входа 27 на вход счетчика 44. Одновременно при установке триггера 43 в единицу с его инверсного выхоДа подается сигнал разрешения на управляющий вход Е дешифратора 46. Число выходов дешифратора 46 равно

55

ет на управляющие входы коммутаторов 13, обеспечивая подключение к входам цифроаналоговых преобразователей 14 выходов счетчика 12. Этот же сигнал поступает на входы 32 блоков 20, где на выходе 25 формируются сигналы разрешения подачи тактовых импульсов на входы счетчиков 12, на выходе 23 сигналы переписи кодов из регистров 16 в регистры 19, а на выходе 26 - сигналы сброса счетчиков.12.

Сигнал на выходе 33 блока 5 формируется в четвертом такте, и проиэвочислу тактов работы устройства. Длительность первого, второго, четвертого, пятого и седьмого тактов равна одному периоду тактовой частоты, что обеспечивается разрешением, поступающим на один из входов элемента 48 через элементы ИЛИ 50 - 52. Длительность третьего и шестого тактов рав- , где TT - период тактона Тг 2

чика 45. Счетчик 45 обнуляется в первом и пятом тактах работы сигналом с выхода элемента ИЛИ 50. Подача тактовых импульсов на вход счетчика 45 разрешается в третьем и шестом тактах с помощью элементов 49,54,42 и прекращается в момент появления сигнала на выходе старшего (2 ; разряда счетчика 45 с момента подачи тактовых импульсов на вход счетчика 44 с помощью элементов 49, 53, 42 и 48. При появлении сигнала на выходе старшего (2 ) разряда счетчика 45 запрет на подачу

тактовых импульсов на вход счетчика 44 снимается.

На выходе 34 блока 5 формируется сигнал в первом и пятом тактах, который поступает в регистры 16 и производит их обнуление,

На выходе 36 блока 5 формируется сигнал в первом,пятом и седьмом тактах, который поступает в блоки 20 на вход 39, где формируется сигнал 26

(сброса счетчиков 12.

Сигнал на выходе 30 блока 5 формируется во втором такте и служит для записи в регистр 16 максимально возможных кодов.

Сигнал на выходе 31 блока 5 формируется в третьем такте, поступает на управляющие входы переключателей 18 в каждом канале, обеспечивая подключе

ние °ДНОГО из входов сумматора 15 к нулевой шине. Этот же сигнал поступа-

ет на управляющие входы коммутаторов 13, обеспечивая подключение к входам цифроаналоговых преобразователей 14 выходов счетчика 12. Этот же сигнал поступает на входы 32 блоков 20, где на выходе 25 формируются сигналы разрешения подачи тактовых импульсов на входы счетчиков 12, на выходе 23 сигналы переписи кодов из регистров 16 в регистры 19, а на выходе 26 - сигналы сброса счетчиков.12.

Сигнал на выходе 33 блока 5 формируется в четвертом такте, и проиэво16416

днтся перепись кодов из регистров в регистры 19 в каждом такте. Сигнал на выходе 35 блока 5 формируется в шестом такте и поступает на выходы 38 блоков 20, где на выходе 25 форми- руются сигналы разрешения подачи тактовых импульсов на входы счетчиков 12, на выходе 23 - сигналы переписи кодов из регистров 16 в регистры 19, на выходе 26 - сигналы сброса счетчиков 12.

Сигнал на выходе 37 блока 5 формируется в восьмом такте и поступает на входы 40 блоков 20, где на выходе 25 формируются сигналы разрешения подачи тактовых импульсов на входы счетчиков 12, на выходе 2ь - сигналы сброса счетчиков 12 и на выходе 24 - сигналы управления ключами 8.

Блок 20 работает следующим образом.

ti третьем, шестом и восьмом так

веннЈ на входы 32, 30 и 40, на выходе элемента ИЛИ 62 возникает сигнал, разрешающий прохождение тактовых импульсов с входа 41 на выход 25 при условии отсутствия сигнала на входе 21, подключенном к выходу компаратора 11. Выход 25 соединен с входом счетчика 12. При срабатывании компаратора 11 на входе 21 появляется сигнал, запрещающий прохождение тактовых импульсов на выход 25. Одновременно по переднему фронту сигнала на входе 21 формирователи Ь& и 59 формируют два импульса длительностью соответственно t,и t,причем t тг 7 tm.Импульс с выхода формирователя 58 в третьем такте через элементы И 6t и ИЛИ 67 поступает на выход 23 в том случае, если в данный момент времени на входе 22, подключенном к выходу блока 17, имеется сигнал., А .шестом такте импульс с выхода формирователя 58 через элементы И 71 и ИЛИ 67 поступает на выход 23 в том случае, если на входе 22 отсутствует сигнал. Сигнал с выхода 23 производит перепись кода из счетчика 12 в регистр 16. В восьмом такте выходной импульс формирователя 56 через элемент И 72 производит запись сигнала на входе 22 (сигнал состояния схемы блока 17 в момент срабатывания компаратора 11) в триггер 56.

По заднему фронту выходного импульса формирователя 58 на выходе элемента И 69 формируется импульс,

длительность которого равна

ЈФ2

12

0

Этот импульс проходит через элемент ИЛИ 61 и поступает на выход 26, осуществляя сброс счетчика 12. Кроме того, сброс счетчика 12 производится в

0

первом, пятом и седьмом тактах при прохождении сигнала с входа 39 через элемент ИЛИ 61 на выход 26.

В восьмом такте с помощью сигнала на выходе 24 производится управление ключом 8. Выход 24 подключен к выходу элемента И-НЕ 60.К одному из входов элемента И-НЕ 60 подключен выход триггера 56 ,а второй вход соединен с выходом эле5 мента 57. К входу элемента 57 в восьмом такте через элемент И 65 подключается инвертированный с помощью элемента ИЛИ-НЕ 64 сигнал на входе 21. Таким образом, на входе элемента 67 в восьмом такте существует сигнал в течение времени выполнения условия (1), а в триггере 56 хранится информация о состоянии блоха 17 в момент окончания выполнения условия (1), при5 чем на выходе триггера 56 будет иметь место логическая единица в том случае, если в момент окончания выполнения условия (1) было выполнено условие (2), т.е. имела место помеха. В этом слу0 чае через время, равное времени задержки элемента 57, прекратится выдача сигнала с выхода 24 на время, равное времени выполнения условия (1), при этом в данном частотном канале 4

5 закроется ключ 8 и произойдет подавление помехи на входе выходного сумматора 3 и выходе всего устройства. Если же условие (2) не было выполнено, то на выходе триггера 56 будет иметь мес0 то логический нуль и отключение данного частотного канала 4 от входа выходного сумматора 3 производиться не будет.

Таким образом, устройство поэволя5 ет повысить коэффициент подавления. помехи.

Формула изобретения Устройство подавления узкополосных

0 помех, содержащее выходной сумматор и N частотных каналов, входы которых ЯБ-. ляются входом устройства, выход каждо-i го частотного канала соединен с одним . из N входов выходного сумматора, каж5 дый частотный канал содержит узкополосный полосовой фильтр, вход которого является входом частотного канала, ключ, выход которого является выходом , частотного канала, и соединенные пос

13

ледовательно амплитудный детектор, вход которого соединен с выходом узкополосного полосового фильтра, фильтр нижних частот и компаратор, отличающееся тем, что, с целью увеличения отношения мощности полезного сигнала к мощности помех при переменном уровне шумов и прерывистых узкополосных помехах, в него введены соединенные последовательно режектор- ный фильтр, вход которого соединен с. входом устройства, и первый элемент задержки,выход которого соединен с дополнительным входом выходного сумматора, блок формирования сигналов управления тактами, первый, второй и третий входы которого являются входами Пуск, Сброс и тактовых импульсов устройства соответственно, в каждый частотный канал введены блок формирования сигналов управления, выход сигнала управления ключом которого соединен с управляющим входом ключа, а входы сигнала прекращения формирования счетных импульсов, управляющего сигнала третьего такта, управляющего сигнала шестого такта, управляющего сигнала первого, пятого и седьмого тактов, управляющего сигнала восьмого такта и тактовых импульсов соединены соответственно с выходами компаратора, управляющего сигнала третьего такта, управляющего сигнала шестого такта, управляющего сигнала первого, пятого и седьмого тактов, управляющего сигнала восьмого такта блока формирования сигналов управления тактами и входом тактовых импульсов устройства, второй элемент задержки, вход которого соединен с выхо дом узкополосного полосового фильтра, а выход с сигнальным входом ключа, соединенные последовательно переключатель, первый сигнальный вход кото- рого соединен с общей шиной, второй

1t

10

20

,с

6060|4

сигнальный вход является входом постоянного напряжения, а управляющий вход соединен с выходом управляющего сигнала третьего такта блока формирования сигналов управления тактами, и сумматор, выход которого соединен с входом опорного сигнала компаратора, соединенные последовательно счетчик, вход счетных импульсов которого соединен с выходом счетных импульсов блока формирования сигналов управления, а вход сигнала обнуления соединен с выходом сигнала обнуления блока 15 формирования сигналов управления, коммутатор, управляющий вход которого соединен с выходом управляющего сигнала третьего такта блока формирования сигналов управления тактами, и циФроаналоговый преобразователь, выход которого соединен с другим входом сумматора, первый регистр, вход Запись которого соединен с выходом Перезапись блока формирования сигналов управления тактами,а выход соединен с другим входом коммутатора, соединенные последовательно второй регистр, информационный вход которого соединен с выходом счетчика, вход Обнуление соединен с выходом Обнуление блока формирования сигналов управления тактами, вход сигнала записи максимально возможного кода и вход сигнала Запись соединены с выходом сигнала записи максимально возможного кода, на втором такте и выходом Запись блока формирования сигналов управления тактами соответственно, а выход соединен с входом информационного сигнала первого регистра, и блок сравнения кодов, другой вход которого соединен с выходом счетчика, а выход соединен с входом сигнала, состояния блока сравнения кодов блока формирования сигналов управления.

25

30

35

40

lib о10

LH

L

12

1

/J

3

/5

/7

4

t-t/ дга/лгл

Пуск о-

5рос

28

-Я

#

// 7,

JO

Ж.

35

34

I

51

г

В

Й

15

4//

Ю

#

#

л

J

J

Фиг.1

я-f -

- дч i- с A3 Н

щ

if Iе-Э

48

Ш

US

53

фиг. I

f(

Jff

3f

-зз

-35 -37

.34 36

56

61

60

lit26

25

1W

65

57

66

a

56

55

68

| Устройство подавления гармонической случайной помехи в речевом сигнале | 1980 |

|

SU1059682A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Патент США № 3988679, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-04-30—Публикация

1988-12-27—Подача