Фиг.1

Изобретение относится к области электросвязи и может быть использовано в системах телемеханики и передачи данных.

Известен приемник многочастотных сигналов, содержащий входной усилитель, к выходу которого подсоединены N частотных каналов, имеющих последовательно соединенные полосовой фильтр, детектор огибающей и вентиль, элемент ИЛИ, ко входам которого подключены входы детекторов огибаюш,их и анализатор длительности сигналов, вход которого подсоединен к выходу элемента ИЛИ, а выход к управляющим входам вентилей N частотных каналов. Недостатком этого устройства является слабая помехозащищенность при входном речевом сигнале и сигнале миогочастотного кода.

Наиболее близким по технической сути к предлагаемому изобретению является приемник многочастотных сигналов, содержащий входной усилитель, к выходу которого подсоединены N параллельных частотных каналов, каждый из которых содержит последовательно соединенные полосовой фильтр, детектор огибающей и элемент И, причем выходы детекторов подсоединены ко входам элемента ИЛИ, выход последнего соединен со входом блока контроля числа принимаемых частот и блоком анализа длительности сигнала, выходы которых подключены ко входам элемента И, выход элемента И подключен к оставшимся входам элементов И N частотных каналов.

Однако этот приемник обладает низкой помехоустойчивостью. В приемнике-прототипе запуск блока анализа длительности сигнала и блока контроля числа принимаемых частот происходит при появлении положительного импульса на выходе схемы ИЛИ, общей для всех N частотных каналов. Сигнал на выходе ИЛИ появляется в том случае, когда на выходе одного или более детекторов огибающих формируются сигналы положительной полярности. После появления импульса на выходе элемента ИЛИ количество импульсов, поступающих на его вход с детекторов огибающих, может измениться, а сигнал на выходе элемента ИЛИ будет остаоаться неизменным. Это приведет к тому, что не произойдет перезапуск блока анализа длительности сигналов, в результате чего возможно прохождение ошибочно принятых сигналов, а также запрет прохождения на выход правильной комбинации. Кроме того, при последовательном опросе N частотных каналов блоком контроля числа принимаемых частот возможна ситуация, когда изменение сигнала о , ... Ы, канале, произошедшее после опроса этого канала, не будет зафиксировано,

что приведет к принятию ложной информации.

Цель изобретения - повысить помехоустойчивость приема сигналов многочастотного кода.

Поставленная цель достигается тем, что в предлагаемом изобретении в отличие от прототипа входная информация по всем каналам одновременно анализируется в тече0 ние всего значащего интервала времени, для чего система, содержащая входной усилитель, к выходу которого подсоединены IM параллельных частотных каналов, каждый из которых содержит последовательно сое5 диненные полосовой фильтр, детектор огибающей, выходы частотных каналов подключены к соответствующим входам блока контроля числа принимаемых частот, соответствующие выходы которого подклю0 чены ко входам блока анализа длительности сигнала, дополнительно содержит N+1-й полосовой фильтр, устройство выделения и формирования синхроимпульсов и блок буферных элементов, причем вход N+1-ro по5 лосового фильтра подключен ко входу устройства выделения и формирования синхроимпульсов, выходы которого подключены к соответствующим входам блока контроля числа принимаемых частот и блока

0 анализа длительности сигнала, оставшиеся выходы блока контроля числа принимаемых частот подсоединены ко входам блока буферных элементов, к оставшемуся входу которого подключен выход блока анализа

5 длительности сигнала. При этом блок контроля числа принимаемых частот содержит дешифратор, регистр, элемент И, схему сравнения, триггер, одновибратор, генератор тактовых импульсов и линию задержки,

0 причем информационными входами блока контроля числа принимаемых частот являются параллельно соединенные соответствующие входы запоминающего устройства, регистра и схемы сравнения, выходы реги5 стра подключены к соответствующим входам схемы сравнения, выход дешифратора подключен ко входу одновибратора, к оставшимся входам которого подключен выход триггера, вход которого подключен к соот0 ветствующему выходу одновибратора, оставшийся выход одновибратора подключен к соответствующим входам регистра, тактовый вход регистра подключен к выходу генератора тактовых импульсов, к оставшемуся

5 входу регистра подключен выход линии задержки, входом связи блока контроля числа принимаемых частот с устройством выделения и формирования синхроимпульсов являются соединенные соответствующий вход триггера и вход линии задержки, входы элементов И подключены к выходам схемы сравнения и генератора тактовых импульсов, выходом блока контроля числа принимаемых частот, связанным с блоком анализа длительности сигнала, является вы- ход элемента И, информационными выходами блока контроля числа принимаемых частот являются выходы регистра. Блок анализа длительности сигнала содержит последовательно соединенные счетчик и схему сравнения, причем входом блока анализа длительности сигнала является вход счетчика, а выходом - выход схемы сравнения.

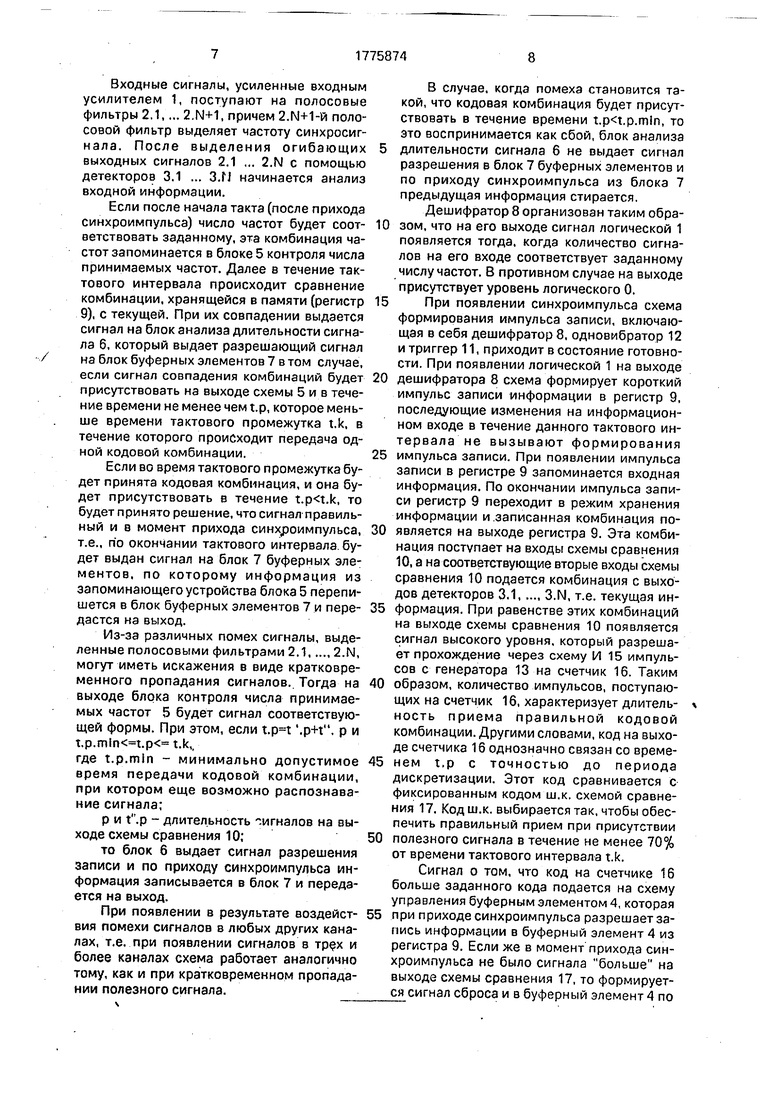

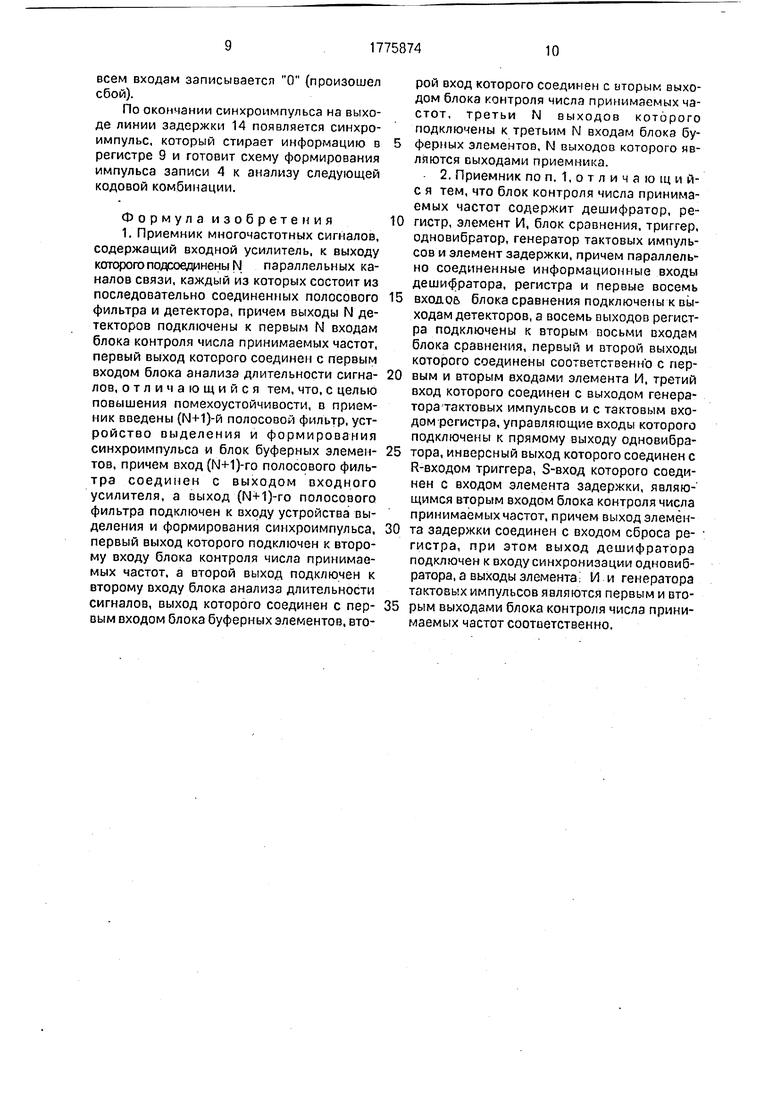

На фиг. 1 приведена структурная схема заявляемого устройства; на фиг. 2 изобра- жена функциональная схема блока контроля числа принимаемых частот; на фиг. 3 приведена функциональная схема блока анализа длительности сигналов.

Приемник содержит входной усилитель

1, N+1 полосовых фильтров 2.1 2.N, N

детекторов 3.1, .... 3.N, устройство выделения и формирования синхроимпульса 4, блок контроля числа принимаемых частот 5, блок анализа длительности сигналов 6 и блок буферных элементов 7, причем выход входного усилителя подключен ко входам всех полосовых фильтров 2.12.N, выходы полосовых фильтров 2.12.N подключены ко входам соответствующих детекторов 3.1, ..., 3.N, выход полосового фильтра 2 подключен ко входу устройства выделения и формирования синхроимпульсов, выходы детекторов 3.13.N подключены к информационным входам блока контроля числа принимаемых частот 5, выход которого подключен ко входу блока анализа длительности сигнала 6, оставшиеся выходы блока 5 контроля числа, принимаемых частот подключены ко входам блока буферных элементов 7, к оставшимся входам блока контроля числа принимаемых частот 5 и блока анализа длительности сигнала 6 подключен выход блока выделения и формирования синхроимпульсов 4, выходами устройства являются выходы блока буферных элементов 7.

На фиг. 2 приведена функциональная схема блока контроля числа принимаемых частот 5, которая содержит дешифратор 8, регистр 9, схему сравнения 10, триггер Л, одновибратор 12, генератор тактовых импульсов 13, линию задержки 14, элемент И 15, причем входами блока контроля числа принимаемых частот 5 являются параллель- но соединенные соответствующие входы дешифратора 8, регистра 9 и схемы сравнения 10, выход триггера 11 подключен ко входу одновибраторз 12, соответствующий выход которого подсоединен ко входу триггера 11, к оставшемуся входу одновибрзто- ра 12 подключен выход дешифратора 8, оставшийся выход одновибрзтор а 12 подсоединен к соответствующему входу регистра 9, выходы которого подключены к оставшимся входам схемы сравнения 10, к соответствующему входу регистра 9 подключен выход генератора тактовых импульсов 13, к оставшемуся входу регистра 9 подсоединен выход линии задержки 14, входы элемента И 15 подключены к выходу схемы сравнения 10 и генератора тактовых импульсов 13, входом синхронизации блока контроля числа принимаемых частот 5 являются соединенные вход линии задержки 14 и оставшийся вход т риггера 11, информационными выходами блока контроля числа принимаемых частот 5 являются выходы регистра 9, оставшимся выходом блока 5 является выход элемента И 15.

Элементы блока 5 контроля числа принимаемых частот, представленного на фиг. 2, могут быть реализованы следующим образом.

Функции дешифратора 8 может выполнять микросхема 541РТ1,

Регистр 9 может быть выполнен на микросхеме К155ИР13.

Схема сравнения 10 при может быть выполнена на двух микросхемах К531СП1.

Триггер 11 может быть реализован на микросхеме К555ТМ2.

Одновибратор 12 может быть представлен микросхемой К155АГ1.

Генератор тактовых импульсов 3 выполнен по одной из схем, приведенных в Колс-мбет Е.А. Таймеры. - М.: Радио и связь, 1983.-с. 35-64.

Функции линии задержки может выполнять микросхема К555АГЗ.

Элемент И 15 выполнен на микросхеме К555ЛИ4.

Функциональная схема блока анализа длительности сигналов б приведена на фиг. 3 и содержит счетчик 16 и схему сравнения 17, причем входом блока б, связанным с блоком 5, является вход счетчика 16. С блоком 7 блок 6 связан остальными входами счетчика 16, причем выходы счетчика 16 подключены ко входам схемы сравнения 17, соответствующий выход Которой является выходом блока анализа длительности сигналов 6.

В качестве счетчика 16 можно использовать микросхему К155ИЕ2.

Функции схемы 17 сравнения может выполнять микросхема К531СП1.

Устройство работает следующим образом.

Входные сигналы, усиленные входным усилителем 1, поступают на полосовые фильтры 2.1,... 2.N+1, причем 2.М+1-Й полосовой фильтр выделяет частоту синхросигнала. После выделения огибающих выходных сигналов 2.1 ... 2.N с помощью детекторов 3.1 ... З.П начинается анализ входной информации.

Если после начала такта (после прихода синхроимпульса) число частот будет соответствовать заданному, эта комбинация частот запоминается в блоке 5 контроля числа принимаемых частот. Далее в течение тактового интервала происходит сравнение комбинации, хранящейся в памяти (регистр 9), с текущей. При их совпадении выдается сигнал на блок анализа длительности сигнала 6, который выдает разрешающий сигнал на блок буферных элементов 7 втом случае, если сигнал совпадения комбинаций будет присутствовать на выходе схемы бив течение времени не менее чем t.p, которое меньше времени тактового промежутка t.k, в течение которого происходит передача одной кодовой комбинации.

Если во время тактового промежутка будет принята кодовая комбинация, и она будет присутствовать в течение t..k, то будет принято решение, что сигнал правильный и в момент прихода синхроимпульса, т.е., по окончании тактового интервала будет выдан сигнал на блок 7 буферных элементов, по которому информация из запоминающего устройства блока 5 перепишется в блок буферных элементов 7 и передастся на выход.

Из-за различных помех сигналы, выделенные полосовыми фильтрами 2.1,..., 2.N, могут иметь искажения в виде кратковременного пропадания сигналов. Тогда на выходе блока контроля числа принимаемых частот 5 будет сигнал соответствующей формы. При этом, если t. .p+t, p и t.p..p t.k,,

где t.p.min - минимально допустимое время передачи кодовой комбинации, при котором еще возможно распознавание сигнала;

р и t.p - длительность сигналов на выходе схемы сравнения 10;

то блок б выдает сигнал разрешения записи и по приходу синхроимпульса информация записывается в блок 7 и передается на выход.

При появлении в результате воздействия помехи сигналов в любых других каналах, т.е. при появлении сигналов в трех и более каналах схема работает аналогично тому, как и при кратковременном пропадании полезного сигнала.

В случае, когда помеха становится такой, что кодовая комбинация будет присутствовать в течение времени t..p.min, то это воспринимается как сбой, блок анализа

длительности сигнала б не выдает сигнал разрешения в блок 7 буферных элементов и по приходу синхроимпульса из блока 7 предыдущая информация стирается.

Дешифратор 8 организован таким обра0 зом, что на его выходе сигнал логической 1 появляется тогда, когда количество сигналов на его входе соответствует заданному числу частот. В противном случае на выходе присутствует уровень логического 0.

5 При появлении синхроимпульса схема формирования импульса записи, включающая в себя дешифратор 8, одновибратор 12 и триггер 11, приходит в состояние готовности. При появлении логической 1 на выходе

0 дешифратора 8 схема формирует короткий импульс записи информации в регистр 9, последующие изменения на информационном входе в течение данного тактового интервала не вызывают формирования

5 импульса записи. При появлении импульса записи в регистре 9 запоминается входная информация. По окончании импульса записи регистр 9 переходит в режим хранения информации и записанная комбинация по0 является на выходе регистра 9. Эта комбинация поступает на входы схемы сравнения 10, а на соответствующие вторые входы схемы сравнения 10 подается комбинация с выходов детекторов 3.1,..., 3.N, т.е. текущая ин5 формация. При равенстве этих комбинаций на выходе схемы сравнения 10 появляется сигнал высокого уровня, который разрешает прохождение через схему И 15 импульсов с генератора 13 на счетчик 16. Таким

0 образом, количество импульсов, поступающих на счетчик 16, характеризует длитель- ность приема правильной кодовой комбинации. Другими словами, код на выходе счетчика 16 однозначно связан со време5 нем t.p с точностью до периода дискретизации. Этот код сравнивается с фиксированным кодом ш.к. схемой сравнения 17. Код ш.к. выбирается так, чтобы обеспечить правильный прием при присутствии

0 полезного сигнала в течение не менее 70% от времени тактового интервала t.k.

Сигнал о том, что код на счетчике 16 больше заданного кода подается на схему управления буферным элементом 4, которая

5 при приходе синхроимпульса разрешает запись информации в буферный элемент 4 из регистра 9. Если же в момент прихода синхроимпульса не было сигнала больше на выходе схемы сравнения 17, то формируется сигнал сброса и в буферный элемент 4 по

всем входам записывается О (произошел сбой).

По окончании синхроимпульса на выходе линии задержки 14 появляется синхроимпульс, который стирает информацию в регистре 9 и готовит схему формирования импульса записи 4 к анализу следующей кодовой комбинации.

Формула изобретения 1. Приемник многочастотных сигналов, содержащий входной усилитель, к выходу которого подсоединены N параллельных каналов связи, каждый из которых состоит из последовательно соединенных полосового фильтра и детектора, причем выходы N детекторов подключены к первым N входам блока контроля числа принимаемых частот, первый выход которого соединен с первым входом блока анализа длительности сигналов, отличающийся тем, что, с целью повышения помехоустойчивости, в приемник введены (N+1)-u полосовой фильтр, устройство выделения и формирования синхроимпульса и блок буферных элементов, причем вход (N-M)-ro полосового фильтра соединен с выходом входного усилителя, а выход (N+1)-ro полосового фильтра подключен к входу устройства выделения и формирования синхроимпульса, первый выход которого подключен к второму входу блока контроля числа принимаемых частот, а второй выход подключен к второму входу блока анализа длительности сигналов, выход которого соединен с первым входом блока буферных элементов, второй вход которого соединен с ыторым выходом блока контроля числа принимаемых частот, третьи N выходов которого подключены к третьим N входам блока буферных элементов, N выходов которого являются выходами приемника.

- 2. Приемник по п. 1, о т л и ч а ю щ и й- с я тем, что блок контроля числа принимаемых частот содержит дешифратор, регистр, элемент И, блок сравнения, триггер, одновибратор, генератор тактовых импульсов и элемент задержки, причем параллельно соединенные информационные входы дешифратора, регистра и первые восемь

входое, блока сравнения подключены к выходам детекторов, а восемь выходов регистра подключены к вторым восьми входам блока сравнения, первый и второй выходы которого соединены соответственно с первым и вторым входами элемента И, третий вход которого соединен с выходом генератора тактовых импульсов и с тактовым входом регистра, управляющие входы которого подключены к прямому выходу одновибратора, инверсный выход которого соединен с R-входом триггера, S-вход которого соединен с входом элемента задержки, являющимся вторым входом блока контроля числа принимаемых частот, причем выход элемеита задержки соединен с входом сброса регистра, при этом выход дешифратора подключен к входу синхронизации одновиб- ратора, а выходы элемента, И и генератора тактовых импульсов являются первыми вторым выходами блока контроля числа принимаемых частот соответственно.

Г

&ta S |

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник многочастотных сигналов | 1990 |

|

SU1838894A3 |

| Система передачи и приема информации | 1987 |

|

SU1411795A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Установка для акустико-эмиссионного контроля | 1986 |

|

SU1452316A1 |

| Устройство для акустических исследований скважин в процессе бурения | 1982 |

|

SU1108196A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для регистрации карьерного транспорта | 1989 |

|

SU1700572A1 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2008 |

|

RU2383103C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1998 |

|

RU2131612C1 |

| Устройство подавления узкополосных помех | 1988 |

|

SU1646060A1 |

Изобретение относится к электросвязи и может быть использовано в телемеханике, передаче данных и в системах телефонной связи для приема многочастотного набора номера. Цель изобретения - повышение помехоустойчивости приема сигналов многочастотного кода. Устройство содержит: 1 входной усилитель (1), N+1 полосовых фильтров (2i-2N+i); N детекторов (31-Зы); 1 устройство выделения и формирования синхроимпульса (4); 1 блок контроля числа принимаемых частот (5); 1 блок анализа длительности сигналов (6); 1 блок буферных элементов (7). Устройство отличается тем, что входная информация по всем каналам одновременно анализируется в течение всего значащего интервала времени, осуществляется фильтрация кратковременных помех в остальных частотных каналах. 1 з.п. ф-лы, 3 ил.

Г

I

Редактор

Составитель В. Гетьман Техред М.Моргентал

Блок 6

I

Фиг.3

Корректор Л. Филь

| Приемник многочастотных сигналов | 1983 |

|

SU1124455A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-11-15—Публикация

1991-05-27—Подача