Изобретение относится к вычислительной технике и может найти применение в электронных вычислительных машинах и быстродействующих процессорах обработки потоков дискретной информации .

Цель изобретения - расширение функциональных возможностей за счет выполнения операции параллельного суммирования ()-х N-разрядных чисел.

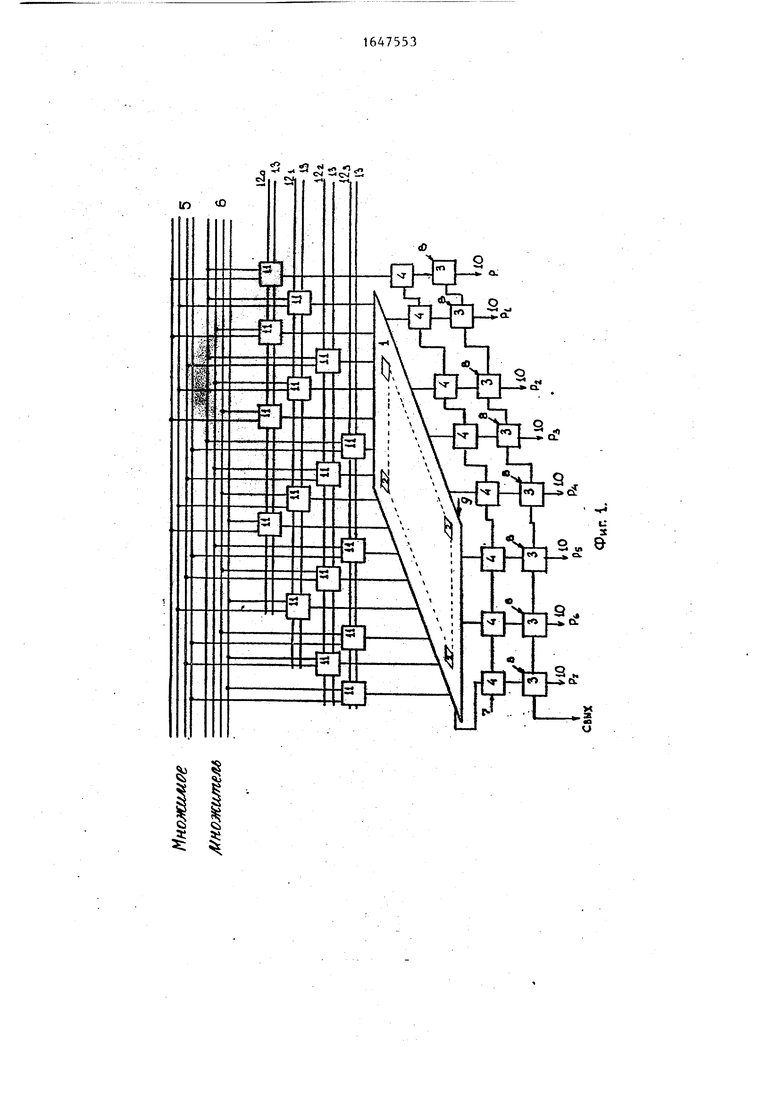

На фиг. 1 представлена функциональная схема четырехразрядного вычислительного устройства; на фиг. 2 - функциональная схема сумматоров; на фиг. 3 - функциональная схема блока формирования разрядных слагаемых; на фиг. 4 - структурная схема, иллюстрирующая работу устройства.

Вычислительное устройство содержит (фиг. 1) матрицу 1 Nx(N-1) полных одноразрядных сумматоров 2, 2Л-ряэрядный сумматор 3, 2N элементов 4 памяти, входы множимого 5 и множителя 6 устройства, вход 7 записи устройства, вход 8 суммирования устройства, вход 9 округления устройства, выходы 10 результата устройства, матрицу 11 NxN блоков формирования разрядных слагаемых, входы 120-12 разрядного среза слагаемых устройства, вход 13 выбора режима работы устройства.

Каждый блок 11 формирования разрядных слагаемых (фиг. 3) содержит элемент ИЛИ 14, счетный триггер 15, элемент НЕ 16, элементы И 17 и 18, входы 19 - 22 блока, выходы 23 и 24 блока. Вычислительное устройство, выполненное в виде модулей (фиг. 4), состоит из модулей 25 - 28 и регистра 29.

Реализация устройства может быть выполнена в виде МОДУЛЯ. В матрице блоков 11 формируются разряди чястичных произведений или двоичных кодов содержимого разрядных срезов, а в матрице 1 сумматоров 2 непосредственно вычисляется результат. 2М-разрядный сумматор 3 может быть либо включен в состав вычислительного устройства при его реализации в виде ВИС с целью исключения дополнительного оборудовав ния при объединении модулей, либо ВЕЛ- делен из БИС с целью экономии выводов. Введение элементов 4 памяти в сочета™ нии с размещением дополнительных входов по краям матрицы 1 позволяет легко осуществить конвейерный режим вы- числения при объединении модулей с целью расширения разрядной сетки операндов и количества слагаемых.

Вычислительное устройство может работать в двух режимах; а) режим ум- ножения двух N-разрядных сомножителей; б) режим сложения N-разрядных слагаемых, причем их количество может достигать 2N-1.

Задание режима работы вычислитель- ного устройства осуществляется по входу 13, при этом логическая 1 на данном входе определяет режим сложения, а О - умножение двух сомножителей,

Рассмотрим работу вычислительного

устройства при умножении двух четырехразрядных сомножителей (фиг, 1). Csxd- дов 5 и 6 множимого и множителя на входы 19 и 20 блоков 11 поступают соответствующие разряды множимого и множителя. Логический О на входе 21 блока 1, являющийся сигналом выбора режима работы устройства, после инвертирования на элементе НЕ 16 разрешает получение на- выходе первого элемента И 17 конъюнкции разрядов множимого и множителя, запрещая выдачу информации с выхода счетного триггера 15. После этого в матрице 1 сумматоров 2 выпол- няется поразрядное сложение разрядов частичных, произведений, поступающих с выходов 24 блоков 11, и распространение сигнала переноса вдоль матрицы 1 за время, равное 2(N-1)Ј, где Ј - время распространения сигнала в сумматоре 2. Для случая это составит 6 Ј.

По сигналу, поступающему на вход 7, полученное произведение запомнится в элементах 4 памяти. С выходов элементов 4 памяти произведение поступи- ет на 21 -разрядкый сумматор 3, на ходах 10 которого формируется результат умножения. Сигнал переноса в старшем разряде сумматора 3 в данном случае отсутствует.

При расширении разрядной сетки выполняется объединение вычислительных модулей (фиг. 4), которое позволяет осуществлять конвейерный режим вычислений. Объединение модулей осуществляется подключением выходов 10 старших разрядов результата модуля 25 к входам 8 2М-разрядиого сумматора 3 модуля 28. Выходы 10 модуля 26 подсоединены к входам 8 модуля 27 и аналогично для следующих модулей.

Работа вычислительного устройства в конвейерном режиме осуществляется следующим образом. На входы сомножителей модуля 25 поступают разряды Х.о множителя и разряды Y,o множимого, на входы сомножителей модуля 26 - з-о на входы сомножителей модуля 27 - Хгои , на входы сомножителей модуля 28 - Х7 4 и В каждой матрице модулей 25-28 выполняется перемножение поступивших четырехразрядных составляющих сомножителей. По первому такту, поступающему на входы 7, полученные пр оизведе2 г 2#С 27 8

ния , , , запоминаются в элементах 4 памяти. С выходов элементов 4 памяти произведения поступают на соответствующие входы сумматора 3 со сдвигом влево частичных произведений, обусловленным алгоритмом умножения.

В сумматоре 3 модуля 27 при сложении частичных произведений образуется сигнал переноса, который подается на вход 8 сумматора 3 модуля 28. Сигнал переноса на выходе модуля 26 отсутствует, так как в нем производится сложение старшей части произведения, сформированной модулем 25, и младшей части произведения, формируемой модулем 26.

По второму такту результат вычисления в виде шестнадцатиразрядного произведения запоминается в регистре 29. При поступлении новых операндов с темпом, равным одному такту работы устройства, полный цикл вычисления повторяется.

Рассмотрим работу вычислительного устройства в режиме параллельного, сложения (2 -1)-х N-разрядных слагаемых (для случая число слагаемых может достигать 15).

516475536

Параллельное сложение N-разрялных16-разрядной суммы запоминается в регистре 29.

операндов выполняется в два этапа. Первый этап заключается в параллельном подсчете количества единиц в каждом разрядном срезе. К i-му разрядному срезу относятся 1-е разряды всех операндов. Второй этап заключается в параллельном сложении полученных регистре 29.

Формула изобретения

Вычислительное устройство, содержащее матрицу N(N-1) полных одноразрядных сумматоров (где N - разрядность зультатов в соответствии с их весами, ю сомножителей), 2К-разрядкый сумматор учет которых выполняется сдвигом вле- и 2N элементов памяти, причем выход во на один разряд разрядной сетки ре- переноса (i,j)-ro полного однораз16-разрядной суммы запоминается в регистре 29.

Формула изобретения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для умножения | 1991 |

|

SU1803914A1 |

| Матричное устройство для умножения чисел (его варианты) | 1983 |

|

SU1160398A1 |

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Матричное устройство для умножения чисел по модулю 2 @ -1 | 1985 |

|

SU1254471A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке высокопроизводительных устройств обработки потоков дискретной информации. Цель изобретения - расширение функциональных возможностей за счет выполнения операции параллельного суммирования (2 -1)-х N-разрядных чисел. Новым в устройстве, содержащем матрицу N х (Ы-1)полньк одноразрядных сумматоров, 2М-разрядный сумматор, 2N элементов памяти, является введение матрицы NxN блоков формирования разрядных слагаемых. 4 ил.

зультата подсчета i-го разрядного среза относительно разрядной сетки результата (i-l)-ro разрядного среза С входов разрядных срезов 12{ поступают разрядные срезы слагаемых на соответствующие входы 22 первых блоков 11 в каждой строке матрицы бло20

рядного сумматора матрицы, где первая переменная обозначает номер стро- ic ки-j а вторая переменная - номер строки + номер позиции сумматора в этой строке (где ,...,N-2, ,...,M-2, где (N-1) соединен соответственно с входом переноса (i+1, j+1)-ro полного одноразрядного сумматора матрицы, выход суммы (а,Ь)-го полного одноразрядного сумматора матрицы (где ,...,N-1, ,...,M-1) соединен соответственно с входом первого слаков 11, причем соответствует разрядный срез младших разрядов операндов.

В каждой строке матрицы блоков 11 в счетных триггерах 15 блоков 11, образующих двоичный счетчик, выполняет- 25 гаемого (а+1, Ь)-го полного однораэ- ся подсчет количества единиц каждого рядного сумматора матрицы, выход пе- разрядного среза. Сигнал логической реноса (N-1, с)-го полного одноразрядного сумматора матрицы соединен соответственно с входом второго ела- счетного триггера 15 на выход 24. За- 30 гаемого (N, с+1)-го полного однораз- тем выполняется суммирование результа- рядного сумматора матрицы (где , тов подсчета количества единиц в каж- ...,М-1), выход переноса (N,j)-ro дом разрядном срезе в матрице 1. По полного одноразрядного сумматора такту, поступившему на вход 7, полу- рицы соединен с входом переноса (N, ченное значение суммы операндов фикси-эс J + O полного одноразрядного суммато- руется на элементах 4 памяти, а затем

1 на входах 13 определяет переход каждого блока 11 к выдаче содержимого

через сумматор 3 подается на выход 10 результата устройства.

ра матрицы соответственно, выход суммы (N,d)-ro полного одноразрядного сумматора матрицы (,...,M) соединен соответственно с информационным

Объединение модулей (фиг. 4) позво-40 входом К-го элемента памяти (,..., ляет увеличить разрядность и количест- 2N-1), выходы 2N элементов памяти со- во слагаемых (например, для случая единены соответственно с входами пер- количество слагаемых может дости- вого слагаемого ZN-разрядного сумма- гать 255).тора, входы второго слагаемого коНа входы разрядных срезов 120-123 45 Т°Р°ГО соединены с входом суммирова- модуля 25 поступают младшие четыре ния Устройства, а выходы - с выходами результата устройства, вход округ- ления которого соединен с входом пеПо первому такту, поступающему реноса (N, М/2+1)-го полного одно50 разрядного сумматора матрицы, выход переноса (N, е)-го полного одноразрядного сумматора матрицы соединен соответственно с входом переноса (N, памяти. С выходов элементов 4 памяти е+1)-го полного одноразрядного сум- полученные результаты поступают на co-cj матора матрицы (e M/2+1),fM-1), выход ,ответствующие входы сумматоров 3 со переноса (N, М)-го полного однораз- сдвигом влево частичных сумм, обус- рядного сумматора матрицы соединен ловленным алгоритмом сложения. По вто- с информационным входом 2N-ro элемен- рому такту результат сложения в виде та памяти, входы записи 2N элементов

разрядных среза слагаемых, а на входы модуля 27 - старшие разряды.

Ј

ды 7, полученные суммы РТ-О

27 18 , PY-O Фиксируются в элементах 4

рядного сумматора матрицы, где первая переменная обозначает номер стро- ки-j а вторая переменная - номер строки + номер позиции сумматора в этой строке (где ,...,N-2, ,...,M-2, где (N-1) соединен соответственно с входом переноса (i+1, j+1)-ro полного одноразрядного сумматора матрицы, выход суммы (а,Ь)-го полного одноразрядного сумматора матрицы (где ,...,N-1, ,...,M-1) соединен соответственно с входом первого слагаемого (а+1, Ь)-го полного однораэ- рядного сумматора матрицы, выход пе- реноса (N-1, с)-го полного одноразрядного сумматора матрицы соединен соответственно с входом второго ела- гаемого (N, с+1)-го полного однораз- рядного сумматора матрицы (где , ...,М-1), выход переноса (N,j)-ro полного одноразрядного сумматора рицы соединен с входом переноса (N, J + O полного одноразрядного суммато-

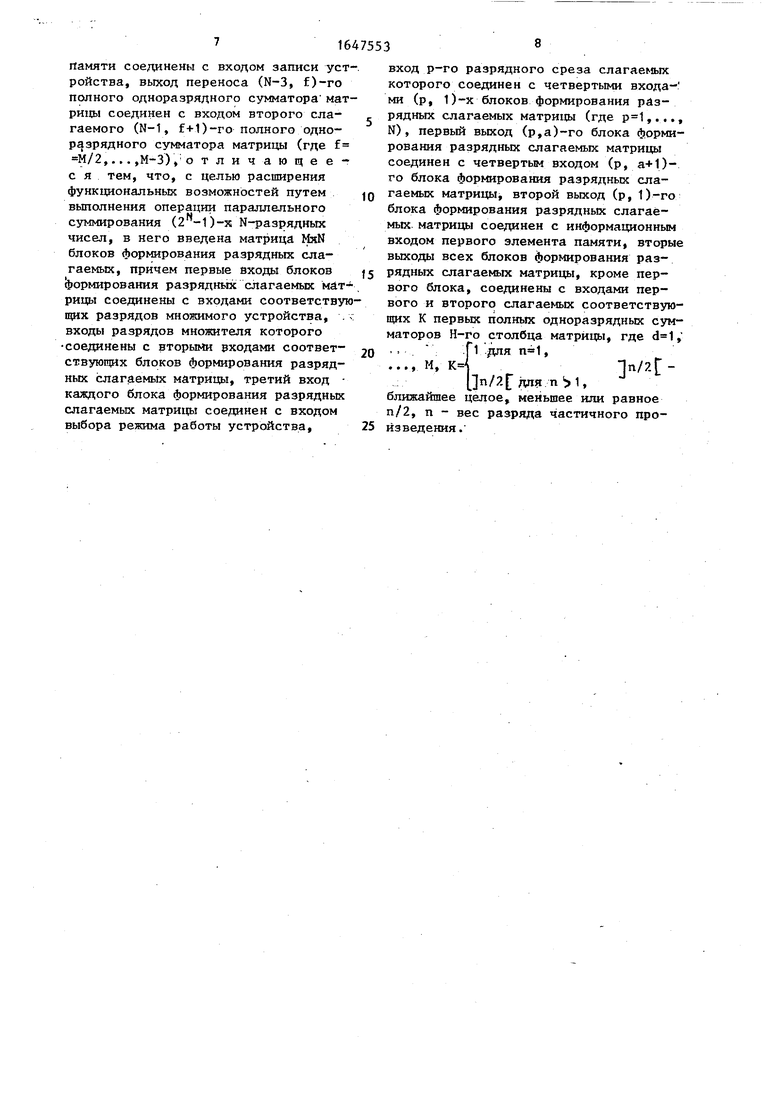

памяти соединены с входом записи устройства, выход переноса (N-3, f)-ro полного одноразрядного сумматора матрицы соединен с входом второго ела- гаемого (N-1, f+1)-ro полного одноразрядного сумматора матрицы (где f М/2,...,М-3) отличающее- с я тем, что, с целью расширения функциональных возможностей путем выполнения операции параллельного суммирования (2 -1)-х N-разрядных чисел, в него введена матрица MxN блоков формирования разрядных слагаемых, причем первые входы блоков формирования разрядных слагаемых матрицы соединены с входами соответствующих разрядов множимого устройства, входы разрядов множителя которого соединены с вторыми входами соответ- ствующих блоков формирования разрядных слагаемых матрицы, третий вход каждого блока формирования разрядных слагаемых матрицы соединен с входом выбора режима работы устройства,

вход р-го разрядного среза слагаемых которого соединен с четвертыми входа- ми (р, 1)-х блоков формирования разрядных слагаемых матрицы (где ,..., N), первый выход (р,а)-го блока формирования разрядных слагаемых матрицы соединен с четвертым входом (р, а+1)- го блока формирования разрядных слагаемых матрицы, второй выход (р, 1)-го блока формирования разрядных слагаемых матрицы соединен с информационным входом первого элемента памяти, вторые выходы всех блоков формирования разрядных слагаемых матрицы, кроме первого блока, соединены с входами первого и второго слагаемых соответствующих К первых полных одноразрядных сумматоров Н-го столбца матрицы, где , . . 1 для , ..., М,

,

ближайшее целое, меньшее или равное n/2, n - вес разряда частичного произведения.

Множимое /икожшпелб

ю Р

PI

Ю

Ра

Р

свых

Фиг. {.

:

М

I

| Патент США № 3914589, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-07—Публикация

1988-07-21—Подача