a,bp(ap)qK(br1qK((ar)qK)((bt,)qK)K Пр Кор

(+2/8) (-4/8)0.010Х1 . .101x0. .110100+0. .111000 (-8/64)

| название | год | авторы | номер документа |

|---|---|---|---|

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство умножения булевых матриц | 1980 |

|

SU959063A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

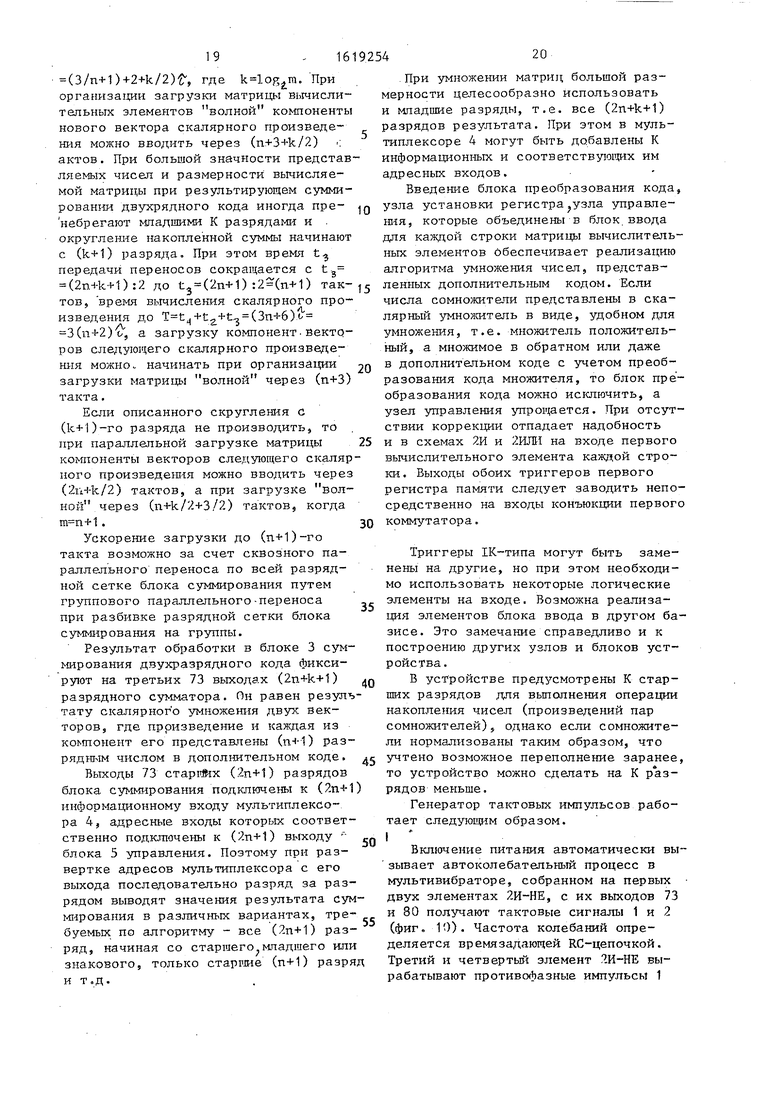

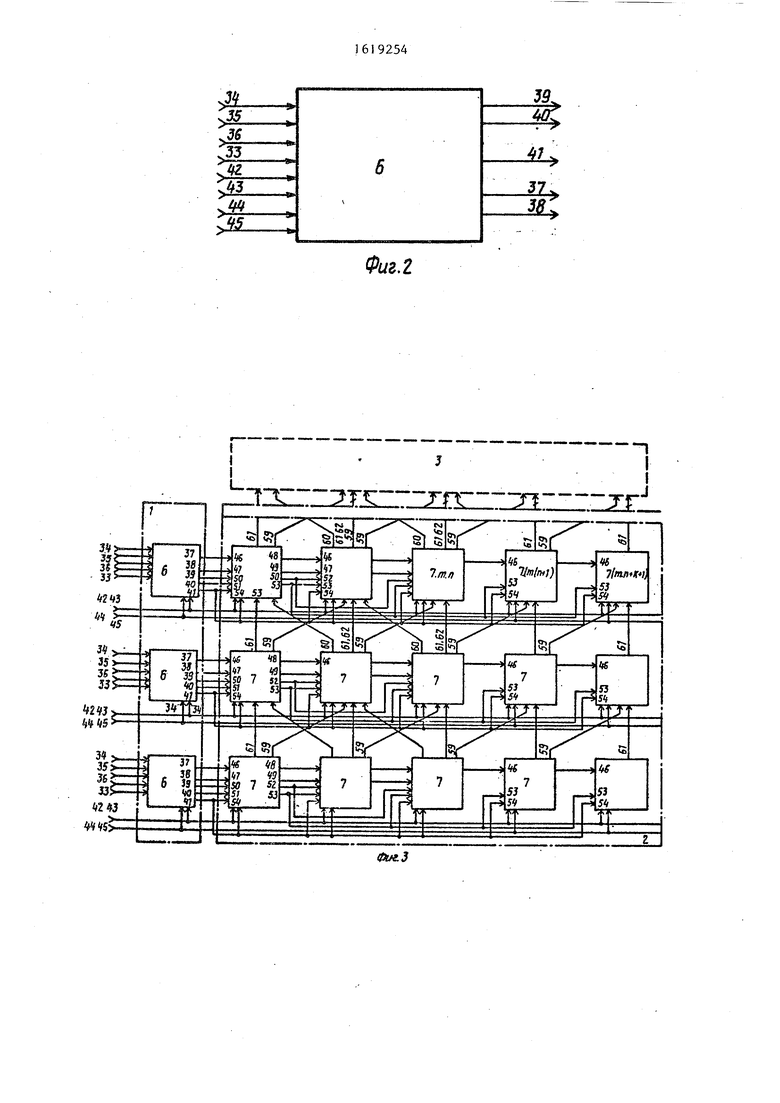

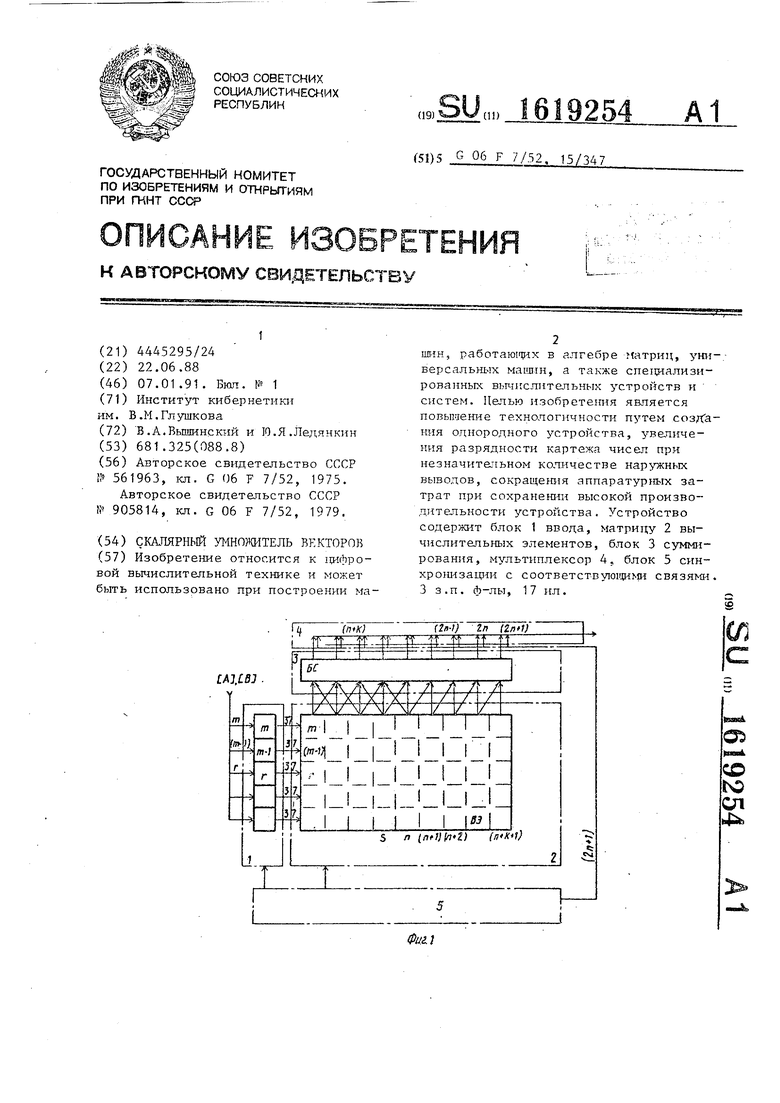

Изобретение относится к цифр о- вой вычислительной технике и может быть использовано при построении машин, работаюпих в алгебре матриц, универсальных машин, а также специализированных вычислительных устройств и систем. Целью изобретения является повышение технотогнчности путем создания однородного устройства, увеличения разрядности картежя чисел при незначительном количестве наружных выводов, сокращения аппаратурных затрат при сохранении высокой производительности устройства. Устройство содержит блок 1 ввода, матрицу 2 вычислительных элементов, блок 3 суммирования, мультиплексор 4, блок 5 синхронизации с соответствующими связями. 3 з.п. ф-лы, 17 ил.

Таким образом г-я строка (,m) матрицы вычислительных элементов позволяет выполнять операцию умножения двоичных чисел в дополнительных кодах с интерпретацией знаковых разрядов как числовых при одной корректирующей операции. Она состоит в прибавлении кода множителя, полученного после преобразования его в дополнительный, если исходный сомножитель был отрицательный. При этом по структуре блока ввода корректирующий код множителя к моменту коррекции в требуемом виде находится во вторых триггерах первого регистра памяти вычислительных элементов r-й строки матрицы.

В умножителе для выполнения операции умножения всех пар сомножителей, которые вводятся последовательно,

г)

0001-0

0011 -00

1110-100

1101-0100

разряд за разрядом, для (п+1)-го разряда требуется (п+1) такт (01 и 2), так как частичные произведения и псевдопроизведения формируются параллельным способом за тот же (п+1) такт, один такт необходим для анализа зна- ков сомножителей и установки триггеров, хранящих значения кода множимого, один такт необходим для выполнения коррекции псевдорезультата. После чего получают двухрядный код результата и переносов. В результате за (п+1+2) такта ( Ј, и Ј2 ) в каждой г-й строке (,га) матриц: формируют частичные произведения га пар сомножите

лен arbp.

Каждое частичное произведение коммутируют на первый вход сумматора каждого вычислительного элемента из пер- jBpro регистра памяти через первый

коммутатор. Одновременно через второй и третий коммутаторы поступает двухрядный код значений переноса и результата на второй и третий входы сумматора. Он поступает с выходов триггеров четвертого и пятого регистров памяти предыдущей (г-1)-й (,га) строки матрицы.Каждый из пяти регистров ПаМЯТИ СОСТОИТ ИЗ ДВУХ ТрИГГерОВ, JQ

причем первые три регистра находятся на входе сумматора (по числу входов его), а четвертый и пятый - на входе сумматора по числу выходов его. В нечетных триггерах регистров памяти 3-х 5 (, (n+k+1)) вычислительных элементов хранятся частичные произведения, формируемые кодом (а,) множимого (первый регистр памяти), а также значения переноса и результата, которые вырабатывает множимое в предыдущей (г-1)-й (, m) строке. С этой целью используют второй и третий регистры памяти на входе сумматора и четвертый

5

с пятым регистры на выходе сумматора В четных триггерах регистров памяти (, та) вычислительных элемент тов хранятся частичные произведения, формируемые кодом (Ь,,) множителя (первый регистр памяти),.а также значения переноса и результата, которые вырабатываются на предыдущей строке кодом множителя. С этой целью те же регистры находятся на входе и выходе сумматора. Раздельная тактировка дву- ,с мя фазами позволяет сэкономить аппаратуру сумматоров. При этом в нечетные триггеры первых трех регистров памяти r-й строки, в которые.в свою очередь они были записаны из нечетных 40 триггеров четвертого и пятого регистров памяти (г-1)-й строки на такте с/ , переписывают значения переноса

вый 55 и третий 57 соответственно информационный вход (S-M)-ro (, (n+k+1) и (S-го, , (n+k+1)) вычислительного элемента r-й строки матрицы вычислительных элементов.

Аналогично значение переноса (результата которое получено в S-м (, (п-1)) и (, п) соответственно вычислительном элементе в качестве частичного произведения ( ) информативно кодом множителя в (г-1)-й (,m) строке матрицы с второго 60 и четвертого 62 соответственно информационного выхода вычислительного элемента 7, поступает на второй 56 и четвертый 58 соответственно информацией11 ВХ°Д (S+1), (,п) и S-ro (,n) соответственно вычислительного элемента r-й строки матрицы вычислительных элементов.

Такое построение вычислительных элементов в скалярном умножителе при двухфазной тактировке в устройстве позволяет сэкономить на сумматорах, одни и те же комбинационные трехвхо- довые сумматоры с коммутацией на вхо - де и двухразрядными регистрами на их входе и выходе используют вначале для од суммирования одной, старшей, части частичного произведения, сформированной от кода множимого, а затем для суммирования другой, младшей части

20

его, сформированной кодом множителя.

В S-x (S n+k+1) вычислительных элементах, начиная с , формируют значения переносов и результата суммирования только от кода множимого. Частичное произведение от кода множимого на k (k log2m) больше, чем от кода множителя. Это связано в основном с организацией накопления сумм га пар сомножителей. Увеличение разрядной сетки происходит автоматически

и результата произведения предыдущей

1} , В чет-AS B кажД°й строке скалярного умножителя, ные триггеры регистров памяти COOT- B матрицу оба сомножителя поступают

пары сомножителей на такте t.

одинаковой значности - (п+1)-й разряд, где п - число информационных разрядов, и один дополнительный знаковый разряд числа, представляемого в дополнительном коде.

ветствующие значения записывают наобоЛ

с , а в четверрот - в первые три на тый и пятый на .

Значение переноса (результат), которое получено в (, (n+k)) или (, (n+k+1)) соответственно вычислительном элементе в качестве частичного произведения (а., bp. f ) кода множителя и множимого соответст50

55

венно (г-1)-й (,га) строки матрицы с первого 59 и третьего 61 соответственно информационного выхода вычислительного элемента 7, поступает на перJQ

5

5

,с 40925412

вый 55 и третий 57 соответственно информационный вход (S-M)-ro (, (n+k+1) и (S-го, , (n+k+1)) вычислительного элемента r-й строки матрицы вычислительных элементов.

Аналогично значение переноса (результата которое получено в S-м (, (п-1)) и (, п) соответственно вычислительном элементе в качестве частичного произведения ( ) информативно кодом множителя в (г-1)-й (,m) строке матрицы с второго 60 и четвертого 62 соответственно информационного выхода вычислительного элемента 7, поступает на второй 56 и четвертый 58 соответственно информацией11 ВХ°Д (S+1), (,п) и S-ro (,n) соответственно вычислительного элемента r-й строки матрицы вычислительных элементов.

Такое построение вычислительных элементов в скалярном умножителе при двухфазной тактировке в устройстве позволяет сэкономить на сумматорах, одни и те же комбинационные трехвхо- довые сумматоры с коммутацией на вхо - де и двухразрядными регистрами на их входе и выходе используют вначале для од суммирования одной, старшей, части частичного произведения, сформированной от кода множимого, а затем для суммирования другой, младшей части

20

его, сформированной кодом множителя.

В S-x (S n+k+1) вычислительных элементах, начиная с , формируют значения переносов и результата суммирования только от кода множимого. Частичное произведение от кода множимого на k (k log2m) больше, чем от кода множителя. Это связано в основном с организацией накопления сумм га пар сомножителей. Увеличение разрядной сетки происходит автоматически

B кажД°й строке скалярного умножителя, B матрицу оба сомножителя поступают

одинаковой значности - (п+1)-й разряд, где п - число информационных разрядов, и один дополнительный знаковый разряд числа, представляемого в дополнительном коде.

Регистр сдвига, организованный первыми триггерами первых регистров памяти 3-х (, (n+k+1)) вычислительных элементов r-й (,m) строки, по установочному 54 входу устанавливают в 1 или О в начале умножения. В процессе ввода новых текущих значений кода множимого в младшие разряды старшие разряды естественно остаются в состоянии нх начальной установки. Это происходит в вычислительных элементах, начиная с первого до (п+1)-го, т.е. до момента, когда они будут заменены соответствующим разрядом множимого, сдвинутым из блока 1 ввода. Но k старших разрядов остаются в состоянии начальной установки. Это соответствует , правилу умножения чисел в дополнительном коде, когда старшие разряды частичного произведения заполняют по правилу арифметического сдвига.

Операцию умножения чисел а, и br в r-й строке выполняют следующим образом.

Вводят знаковый С06 разряд кода множителя аг и на тактовом импульсе /u его значение запоминается в тригге ре узла управления блока ввода. На тактовом импульсе вводят знаковый разряд COft- Прямой и инверсный выходы триггера узла управления блока ввода управляют коммутацией знакового раз- ряда (Од (а затем и информационных разрядов) кода множимого через первый элемент 2И-2И-2ИЛИ в прямом или обратном коде на первый вход S-го () вычислительного элемента. Но знаковый разряд СОд с помощью узла установки регистра блока ввода по его выходу 41 устанавливает в 1 или О все первые триггеры первых регистров памяти вычислительных элементов г-и строки. Поскольку при умножении COg 0 всегда (по алгоритму), то установка в 1 или О первых триггеров первых рё гк- стров памяти S-x (, (n+k+1)) вычислительных элементов r-й строки ( равносильно тому, что на первом тактовом импульсе Ј( и осуществлен ввод знаковых разрядов кодов сомножителей в (k+D-й разряд. Дальнейшей обработке подлежат оставшиеся n информационных разрядов кодов сомножителей.

Положим для определенности, что г строка скалярного умножителя обрабатывает два сомножителя ар и Ьр, ко торые взяты из примера, приведенного выше

(+2/8)(-4/8)0.. .101 0..110100+0..111000(-8/64

На первом тактовом импульсе J, триггер узла управления блока ввода устанавливают в 1 с дальнейшим преобразованием в дополнительный код, т.е, (Ь), а ар - в обратный, т.е. а

,

C0fl 1 с

следующим образом. На установочного выхода 41 блока ввода потенциал уровня единичного сигнала устанавливает в 1 все первые триггеры первых регистров памяти S-x (, (n+k+1)) вычислительных элементов г-и (,и) строки, что соответствует (n, n+k+О) разрядам частичного произведения (включая знаковый).

и

На втором тактовом импульсе с-, LI через блок ввода в первый и

5

0

5 п.

35

45

0

5

второй триггеры первого регистра памяти записывают значения младгаего заряда множителей (Ьг) равное О, в дополнительном коде и старший разряд множимого, равный 1 в обратном коде, сомножителей Ьг и а,,. На четвертом управляющем входе вычислительных элементов установлен высокий потенциал единичного уровня. Он разрешает коммутацию значений вторых триггеров первых регистров памяти S-x (, (n-1)) вычислит an ьных элементов на входы сумматоров, значения результата и переноса с которых на тактовом сигнале г запишутся во вторые триггеры четвертого и пятого регистров памяти. Единичные значения первых триггеров первых: регистров памяти S-x (S 1, (n+k+1)) вычислитапьных элементов не скоммутируют в сумматор. Учитывая, что нет совпадения текущих разрядов, в сумматор S-ro () вычислительного элемента через первый коммутатор поступит О. В результате в первые триггеры четвертого и пятого регистров памяти на тактовом сигнале Ј, запишутся нули. При этом по второму и третьему входам сумматора с предыдущей (г-1)-й строки вычислительных элементов поступают нули. Это равносильно старшей части частичного произведения ВИДЗ 0000. В итоге полное частичное произведение равно 0000000.

На третьем тактовом импульсе 6, и (/ вводят аналогичные значения информационных разрядов кодов сомножителей. Второе частичное произведение будет также аналогично 00000000.

На четвертом тактовом импульсе Ј( и Ј2 вводят третий информационный (со стороны младших) разряд множителя, равный 1, и третий информационный (со стороны старших) разряд множимого, равный О. На четвертом и третьем управляющих входах устанаапивают потенциал нулевого и единичного соответственно уровня, т.е. во вторые триггеры четвертого и пятого регистА

пульсе (/„

г.

ров памяти пишут нули 000

(частичное произведение, формируемое кодом множителя} и 1110 (частичное произведение, формируемое кодом множимого)s а также 0 в S-м () вычислительном элементе, что дает

а в итоге на таковом им- и (,, во вторые и первые ,трпггеры четвертого и пятого регист- ров памяти запишут очередное частичное произведение вида 1110000.

На пятом тактовом импульсе и о вводят четвертый информационный (со стороны младших) разряд множителя равный 0 % это знаковый разряд множителя и по алгоритму он всегда равен О, и четвертый информационный (со стороны старших) разряд множимого, равный 1. Потенциалы на четвертом и третьем управляющих входах равны соответственно 1 и О1, поэтому код 0100 множителя, сдвинутый во вторые триггеры первых регистров памяти за предыдущее такты, скоммутируют в сумматор и далее запишут во вторые триггеры четвертого и пятого регистров памяти. Код 1101 с выходов первых триггеров первых регистров памяти в сумматоры вычислительных элементов не коммутируют. В результате пятого такта будет сформировано частичное произведение вида 0000100.

На шестом тактовом импульсе с,, и из блока синхронизации поступает импульс УЗ длительностью Ј t,, + k2. При этом с первого 39 и второго 40 управляющих выходов блока 1 ввода по- .ступают сигналы управления, которые независимо от значений первого и вто- рого триггеров первого регистра памяти S-го () вычислительного элемента строки установит на третьем и четвертом управляющих входах S-x (, (rHk+1)) и (,n) соответственно потенциалы низкого и высокого уровня, что означает запрет ввода кода множимого и разрешение коммутации корректи рующего кода множителя (Кор.А) и (Кор. В) соответственно. Это равно- сильно новому частичному произведению 0000100.

Легко проверить, что суммирование частичных произведений, полученных выше, дает правильный результат

0.000000 ЧПэн.

0.000000 ЧП 1

0

5

Q

5 0

5 0 5 0

0.00010) ЧП 3

0.000100 Кор.

На четвертом тактовом импульсе Ј, и в первый и второй триггеры первого регистра памяти коммутируют третий разряд со стороны младших разрядов кода множителя, равный 1 и третий разряд кода множимого со стороны старших, который равен О. Первоначально (до подачи б, ) оба триггера (основной и дополнительный) в регистре находятся соответственно в состоянии 11 и 00. После тактового импульса Ј, их состояние изменится с учетом входных значений на 11 и 10, а после /2 - на 01 и 01 соответственно. И лишь на инверсном значении синхроимпульса оба (основной и дополнительный) триггера будут в состоянии 00 и 11. Отсюда видно, что синхронизация реализации конъюнкции на входах первого коммутатора S-ro () вычислительного элемента строки с выходов первого и второго триггеров первого регистра памяти возможна, если использовать выходы только основного и дополнительного триггеров. В противном случае ошибки неизбежны. Анализ потакт- ной работы устройства показывает, что операция умножения выполняется за время (n-H) тактов, где п - информационных разрядов, один знаковый. Это следует из того, что по методу умножения знаковые разряда обрабатывают аналогично информационным за (п-Н) - и такт. Кроме этого требуется один такт для установки разрядов множимого по его знаку, а также один такт для выполнения коррекции.

При организации параллельной загрузки матрицы все одинаковые разряды чисел векторов скалярного умножителя формируют частичные произведения одинаковой значности и в целом за п+3 такта они будут сформированы во всех строках устройства. Это означает наличие значений результата и переноса во всех (n+k+1) вычислительных элементах, т.е. в (2n+k-H) разряде двухрядного хода произведения. Для получения однорядного кода результата с распространенными переносами выполняют m тактов (), в течение которых переносы из первой строки передают в m-ю. Отсюда видно, что время Tj загрузки и очистки матрицы от перекосов,

1716

вычислительных элеменвозникающих в тах, равно

1((п+3)+тп)Ј(2п+3)с при .

При организации работы матрицы волной вычислительный элемент г-й строки загружается, а затем и выгружается (освобождается от переносов) на один такт ( С, и ) ань ие, чем в (г+1)-й строке матрицы. При гп() за время Ц(п+5)1/ полной загрузки первой строки в последнюю строку поступает первый разряд частичного произведения сомножителей я .и Ъ,„. Еще через t- (n+3) С значения переносов и результата суммирования в первой строке поступают в m-ю () строку Отсюда следует, что через t(n4-3)

такта от начала загрузки матрицы ска- 20 матора на четяертый вход 70 (S+l)-ro

лярного умножителя компонентами текущего вектора ее первую строку можно загружать компонентами следующего гек- тора. Организация загрузки волной дает при массовой загрузке векторами экономию во времени на (n+З) такта по сравнению с параллельной загрузкой 0 матрицы.

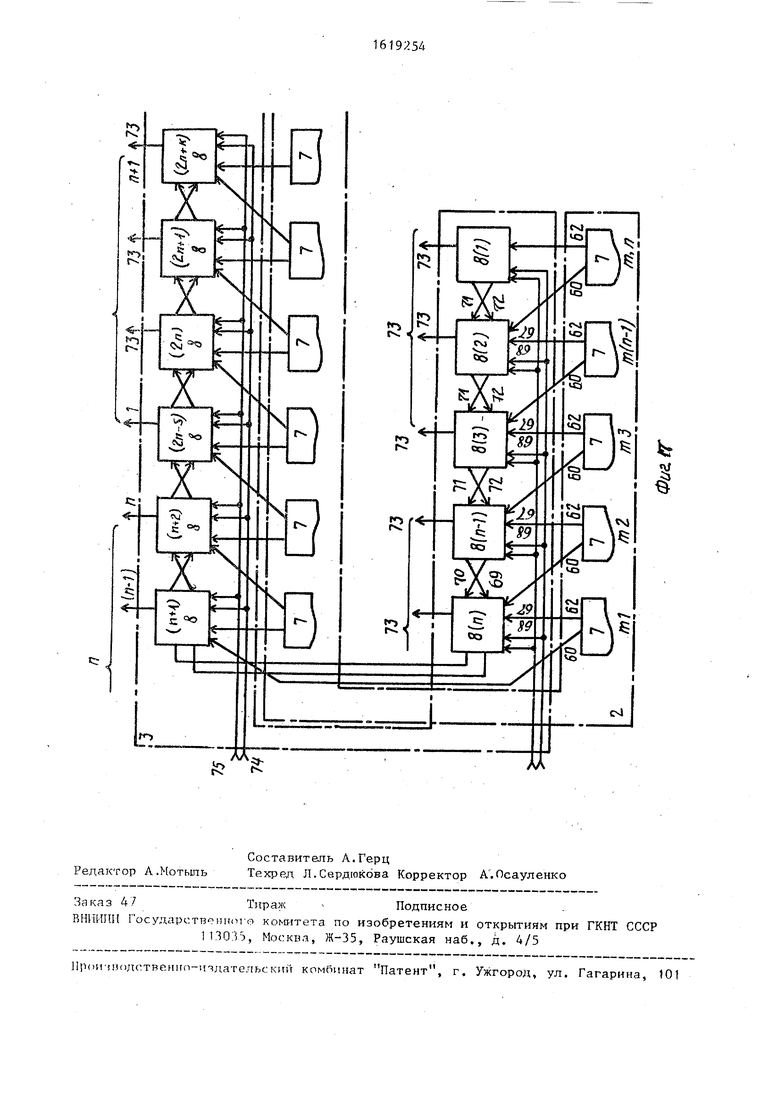

Лвухрядный код, полученный в матрице, с информационных выходов последнейзо лительных элементов, а в третий по m-й строки обрабатывают в блоке сумми- входу 69 - значение переноса с выхода рованйя следующим образом.

71 сумматоров второго яруса () вы числительного элемента. Значение ре- |3ультата и переноса в S/-M (S (n+1 (2n+k+1) и S(n+1), (2n+k) соответственно) сумматоре первого яруса на тактовом импульсе б1, записьшают в триггеры второго яруса: в первый S-го сумматора, во второй (S +1)-го по шинам связи с второго выхода 72 S-ro сумматора на четвертый вход 38 (S + +1)-го сумматора соответственно, в третий переписывают значение триггера результата s -ro разрядного сумматора .

3

4

Первый и четвертый информационные выходы S-x (, (n+k+1)) вычислительных элементов r-й () строки соеди- нены с входами S -тс (S 1, (2n+k+1)) соответствующих сумматоров 8 блока суммирования так, что второй и чет- вертый,информационные выходы S-x (. ,гГ) вычислительных элементов подключены к, первым и вторым входам S -x (Sr ) сумматоров 8 блока суммирования связями 60-62 и 62-68, а первый и тре- тий информационные выходы S-x (, (n+k+1)) вычислительных элементов под- ключ вторым входам s -x (S (n+1), (2n+k+O) сумматоров 8 блока суммирования связями 27-35 и 61-68. Каждому разряду двухрядного кода частичных произведений, которые накоплены построчным суммированием r-х частичных произведений в (n+k+1)-м вычислительном элементе каждой r-й (,m) строки матрицы, соответствует свой сумматор уже в (2n+k+1)-M разрядном сумматоре 8 блока 3 суммирования,

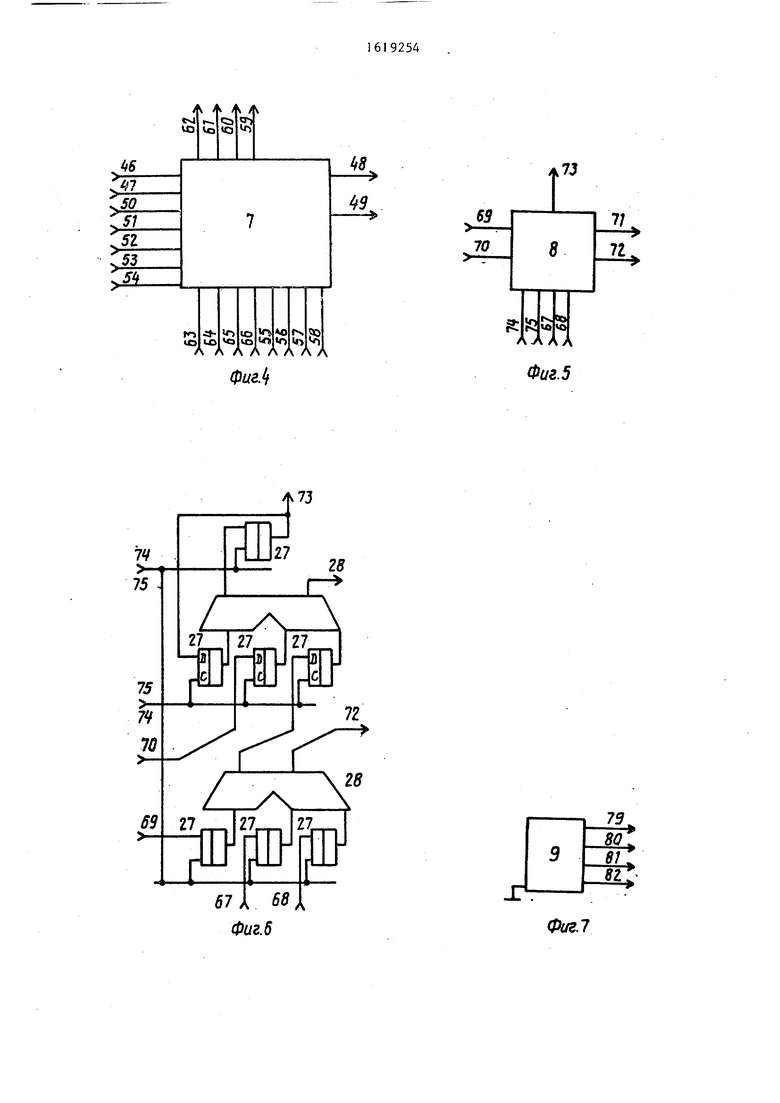

Сумматор 8 блока суммирования работает следующим образом.

5

5

S

На такте 0, в первый и второй триггеры первого чруса s -x (,n) вычислительных элементов по первому 67 и второму 68 входам сумматоров за- пнсьпзают значения двухрядного кода из m-й строки матрицы вычислительных элементов, а в третий по входу 69 - значение переноса с выхода 71 комбинационного сумматора второго яруса (S -1)-го вычислительного элемента значение результата и переноса, кото- ро е выработано в S-м (S 1,n и S 1,(п-1) соответственно) комбинационном сумматоре первого яруса на тактовом сигнале записьшают в триггеры второго яруса: в первый S- го сумматора, во второй (S -И)-го по гаи нам связи с второго 72 с S-ro выхода S-ro сумсумматора соответственно, в третий переписывают значение триггера результата S-ro сумматора.

На такте о% в первый и второй

триггеры первого яруса S -x (s (n+1), (2n+k+1)) вычислительных элементов по первому 67 и второму 68 входам сумматоров записывают значение двухрядного кода из m строки матрицы вычисо лительных элементов, а в третий по входу 69 - значение переноса с выхода

5

71 сумматоров второго яруса () вычислительного элемента. Значение ре- |3ультата и переноса в S/-M (S (n+1), (2n+k+1) и S(n+1), (2n+k) соответственно) сумматоре первого яруса на тактовом импульсе б1, записьшают в триггеры второго яруса: в первый S-го сумматора, во второй (S +1)-го по шинам связи с второго выхода 72 S-ro сумматора на четвертый вход 38 (S + +1)-го сумматора соответственно, в третий переписывают значение триггера результата s -ro разрядного сумматора .

Предлагаемая структура блока суммирования и его связей в два раза ускоряет передачу переносов из первого разряда блока суммирования в (2п+ Нс-Н) сумматор, так как сложение производят одновременно во всех младших (1+п) и старших (n+1)-(2n+k+1) сумматорах на каждом втором сигнале.i Время t, передачи переносов из младшего в старши; ; (2n+k+1)-ft разряд рав- (2n+k+1)

-32

лярного произведения двух векторов А и Б размерности равно T tf+teL+ts

но t.

А общее время Т ска19 , 1619254

(3/n+1)+2+k/2)f, где ,,m. При организации загрузки матрицы вычислительных элементов волной компоненты нового вектора скалярного произведения можно вводить через (n+3+k/2) актов. При большой значности представляемых чисел и размерности вычисляемой матрицы при результирующем суммировании двухрядного кода иногда пре- д небрегают младшими К разрядами и округление накопленной суммы начинают с (k+1) разряда. При этом время t передачи переносов сокращается с

20

При умножении матриц большой размерности целесообразно использовать и младшие разряды, т.е. все (2n+k+1) разрядов результата. При этом в мультиплексоре 4 могут быть добавлены К информационных и соответствующих им адресных входов.

Введение блока преобразования кода, узла установки регистра узла управления, которые объединены в блок ввода

ts

для каждой строки матрицы вычислительных элементов обеспечивает реализацию алгоритма умножения чисел, представ (2rn-kH):2 до t3(2n+1) :2 (n+1) так- ленных дополнительным кодом. Если

числа сомножители представлены в скатов, время вычисления скалярного про

изведения до ,,+t (3n+6) А

лярный умножитель в виде, удобном для 3(п+2)/о. а загрузку компонент векто- умножения, т.е. множитель положитель

ров следующего скалярного произведения можно, начинать при организации загрузки матрицы волной через (п+3) такта.

Если описанного скругления с (k-H)-ro разряда не производить, то при параллельной загрузке матрицы компоненты векторов следующего скалярного произведения можно вводить через (2n+k/2) тактов, а при загрузке волной через (n+k/2+3/2) тактов, когда .

Ускорение загрузки до (п-М)-го такта возможно за счет сквозного параллельного переноса по всей разрядной сетке блока суммирования путем группового параллельного-переноса при разбивке разрядной сетки блока суммирования на группы.

Результат обработки в блоке 3 суммирования двухразрядного кода фиксируют на третьих 73 выходах (2n+k+1) разрядного сумматора. Он равен результату скалярного умножения двух векторов, где произведение и каждая из компонент его представлены (n-И) разрядным числом в дополнительном коде.

Выходы 73 старших (2п+1) разрядов блока суммирования подключены к (2п+1 информационному входу мультиплексора 4, адресные входы которых соответственно подключены к (2п+1) выходу - блока 5 управления. Поэтому при развертке адресов мультиплексора с его выхода последовательно разряд за разрядом выводят значения результата суммирования в различных вариантах, тре

буемых по алгоритму - все (2п+1) разряд, начиная со старшего,,младшего или знакового, только старшие (п+1) разряд

и т.д.

4

20

При умножении матриц большой размерности целесообразно использовать и младшие разряды, т.е. все (2n+k+1) разрядов результата. При этом в мультиплексоре 4 могут быть добавлены К информационных и соответствующих им адресных входов.

Введение блока преобразования кода узла установки регистра узла управления, которые объединены в блок ввода

для каждой строки матрицы вычислительных элементов обеспечивает реализацию алгоритма умножения чисел, представный, а множимое в обратном или даже в дополнительном коде с учетом преобразования кода множителя, то блок преобразования кода можно исключить, а узел управления упрощается. При отсутствии коррекции отпадает надобность и в схемах 2И и 2ИЛИ на входе первого вычислительного элемента каждой строки. Выходы обоих триггеров первого регистра памяти следует заводить непосредственно на входы конъюкции первого коммутатора.

5

0

5

Триггеры IK-типа могут быть заменены на другие, но при этом необходимо использовать некоторые логические элементы на входе. Возможна реализация элементов блока ввода в другом базисе. Это замечание справедливо и к построению других узлов и блоков устройства.

В устройстве предусмотрены К старших разрядов для выполнения операции накопления чисел (произведений пар сомножителей) однако если сомножители нормализованы таким образом, что 5 учтено возможное переполнение заранее, то устройство можно сделать на К рядов меньше.

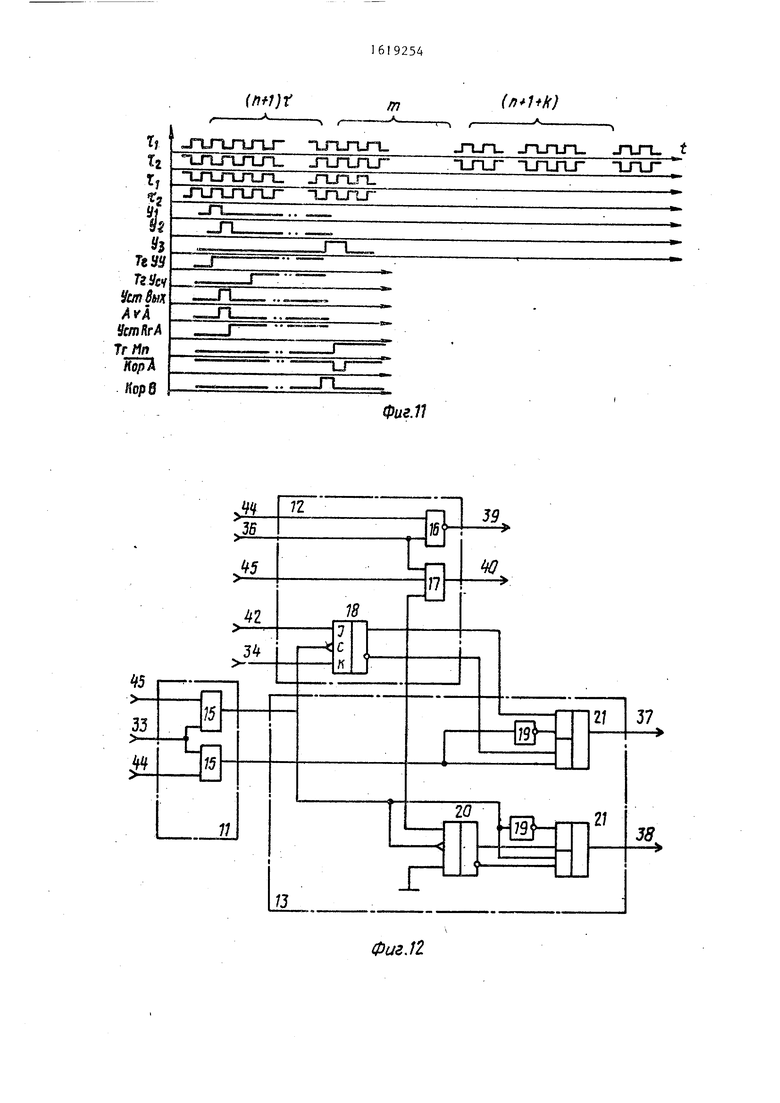

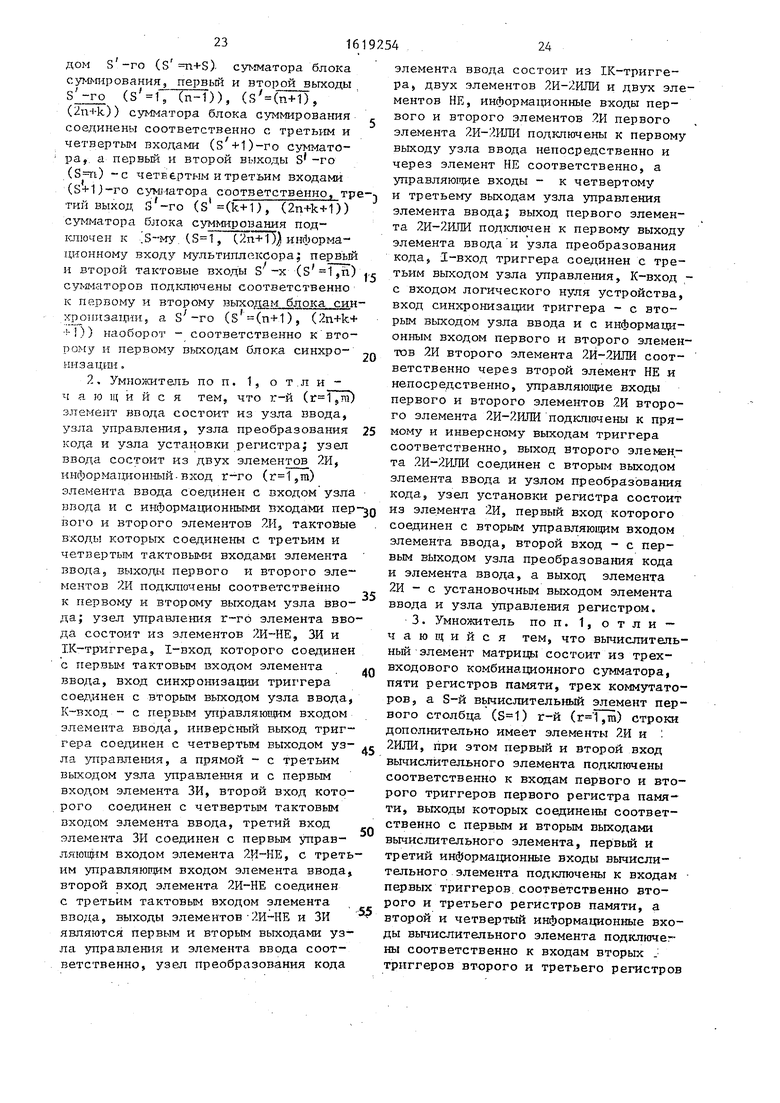

Генератор тактовых импульсов работает следующим образом. I

Включение питания автоматически вызывает автоколебательный процесс в мультивибраторе, собранном на первых двух элементах 2И-НЕ, с их выходов 73 и 80 получают тактовые сигналы 1 и 2 (фиг. 10). Частота колебаний определяется времязадающей RC-цепочкой. Третий и четвертый элемент 2И-НЕ вырабатывают противофазные импульсы 1

и 2, которые снимают с выходов 81 и 28.

Выработка сигналов управления У1, У2, УЗ узлом 10 управления коррекцией обеспечивает выполнение операции умножения чисел в дополнительном коде и коррекцию (по знаку множимого) в конце операции. Временная диаграмма (фиг. 11) определяет временную последовательность управляюпдих сигналов и их привязку к тактовым импульсам.

Формула изобретения

ходами (S-1)-ro вычислительного элемента, в S-x (S(n+1), (n+k-H)) вычислительных элементах первый вход

to

15

0 25 30 40 45 0

5

S-ro вычислительного элемента соединен с первым выхо;;ом (S-1)-ro, установочные входы все;: рычислительных элементов г-и ( ,m) строки подключены к установочному выходу т-го (г 1,га) элемента ввода; второй и четвертый информационные выходы S-го () .вычислительного элемента r-й (, (т-Т)) строки соединены соответственно с вторым информационным входом (S-1)-ro и четвертым информационным входом S-го вычислительного элемента (г+1)-й строки, первый информацион- ный выход S-го (, (n+k)) вычисли- тельного элемента г-и ((m+1)) строки соединен с первым информационным входом (S+1)-ro вычислительного элемента (г+1)-й строки, а третий выход S-го ( (n+k+1)) внчисли- тельного элемента г-и (, (m-1)) строки - с третьим информационным входом S-го вычислительного элемента (г-М)-й ( (m-1}) строки; во всех вычислительных элементах матрицы первый, второй, третий и четвертый тактовые входы соединены соответственно с первым, вторым, третьим и четвертым выходами блока синхронизации; первый и второй управляющие входы S-x () вычислительных элементов r-й (,го) строки подключены соответственно к первому и второму управляющим выходам

r-го (, п) элемента ввода, в г-й (,m) строке третий управляющий вход S-x (, (m+k+0) вычислительных элементов подключен к третьему управляющему входу S-го () вычислительного элемента, а четвертый управляющий вход S-x (,п) вычислительных элементов - к четвертому управляющему входу S-го () вычислительного элемента; первый, второй, третий и четвертый тактовые входы элементов ввода подключены к соответствующим выходам блока синхронизации, второй и четвертый информационные выходы S-го (,n) вычислительного элемента га-й строки матрицы соединены соответственно с первым входом S-ro (S n-S+2) сумматора и с вторым входом s -ro (s n-S+1) сумматора блока суммирования, а первый и третий инфор- мационные выходы S-го (, (n+k)) и , (n+k+1) вычислительного элемента го-й строки матрицы соединены соответственно с первым входом S-ro (S n+S+t)сумматора и с вторым входом S -го () сумматора блока суммирования, первый и второй выходы s -ro ( Cn-1)), (S (n+1), (2nn-k)) сумматора блока суммирования соединены соответственно с третьим и четвертым входами (s +1)-ro сумматора, а первый и второй выходы S -го

элемента ввода состоит из 1К-тригге- ра, двух элементов 2И-/-ИЛИ и двух элементов НЕ, информационные входы первого и второго элементов 2И первого элемента 2И-2ИЛИ подключены к первому выходу узла ввода непосредственно и через элемент НЕ соответственно, а управляющие входы - к четвертому

() -с четвертым и третьим входамиJ..r,..,

( сумматора соответственно, тре-j и третьему выходам узла управления

-.-„.у. .... /ч .. / 1 .4 ч/ о . ч . , л Ч

гай выход S -го (S (k+1), (2n+k+1)) сумматора блока суммирования подключен к .3-му (., (2ii+T)J информационному входу мультиплексора; первый

элемента ввода; выход первого элемента 2И-2ИЛИ подключен к первому выходу элемента ввода и узла преобразования кода, 1-вход триггера соединен с треи второй тактовые входы S -x (,n) jr тьим выходом узла управления, К-вход сумматоров подключены соответственно к первому ч второму выходам |блока си.н уропизацин, a S;-го (s (n+1), (2n+k+ -Р) наоборот - соответственно к второму и первому выходам блока синхронизации .

ввода и с информационными входами из элемента 2И, первый вход которого

35

вого и второго элементов 2ИЭ тактовые входы которых соединены с третьим и четвертым тактовыми входами элемента ввода, выходы первого и второго элементов 2И подключены соответственно к первому и второму выходам узла ввода; узел управления r-го элемента ввода состоит из элементов 2И-НЕ, ЗИ и ТК-триггера, 1-вход, которого соединен с первым тактовым входом элемента Q

ввода, вход синхронизации триггера соединен с вторым выходом узла ввода, К-вход - с первым управляющим входом элемента ввода, инверсный выход триг-

соединен с вторым управляющим входом элемента ввода, второй вход - с первым выходом узла преобразования кода и элемента ввода, а выход элемента 2И - с установочным выходом элемента ввода и узла управления регистром.

гера соединен с четвертым выходом уз- -с 2ИЛИ, при этом первый и второй вход

ла управления, а прямой - с третьим выходом узла управления и с первым входом элемента ЗИ, второй вход которого соединен с четвертым тактовым входом элемента ввода, третий вход элемента ЗИ соединен с первым управляющим входом элемента 2И-НЕ, с третьим управляющим входом элемента ввода второй вход элемента 2И-НЕ соединен с третьим тактовым входом элемента ввода, выходы элементов 2И-НЕ и ЗИ являются первым и вторым выходами узла управления и элемента ввода соответственно, узел преобразования кода

50

55

вычислительного элемента подключены соответственно к входам первого и вто рого триггеров первого регистра памяти, выходы которых соединены соответственно с первым и вторым выходами вычислительного элемента, первый и третий информационные входы вычислительного элемента подключены к входам первых триггеров соответственно второго и третьего регистров памяти, а второй и четвертый информационные вхо ды вычислительного элемента подключены соответственно к входам вторых . триггеров второго и третьего регистро

элемента ввода состоит из 1К-тригге- ра, двух элементов 2И-/-ИЛИ и двух элементов НЕ, информационные входы первого и второго элементов 2И первого элемента 2И-2ИЛИ подключены к первому выходу узла ввода непосредственно и через элемент НЕ соответственно, а управляющие входы - к четвертому

J..r,..,

элемента ввода; выход первого элемента 2И-2ИЛИ подключен к первому выходу элемента ввода и узла преобразования кода, 1-вход триггера соединен с третьим выходом узла управления, К-вход 0

5

с входом логического нуля устройства, вход синхронизации триггера с вторым выходом узла ввода и с информационным входом первого и второго элементов 2И второго элемента 2И-2ИЛИ соответственно через второй элемент НЕ и непосредственно, управляющие входы первого и второго элементов 2И второго элемента 2И-2ИЛИ подключены к прямому и инверсному выходам триггера соответственно, выход второго элемента 2И-2ИЛИ соединен с вторым выходом элемента ввода и узлом преобразования кода, узел установки регистра состоит

5

Q

соединен с вторым управляющим входом элемента ввода, второй вход - с первым выходом узла преобразования кода и элемента ввода, а выход элемента 2И - с установочным выходом элемента ввода и узла управления регистром.

0

5

вычислительного элемента подключены соответственно к входам первого и второго триггеров первого регистра памяти, выходы которых соединены соответственно с первым и вторым выходами вычислительного элемента, первый и третий информационные входы вычислительного элемента подключены к входам первых триггеров соответственно второго и третьего регистров памяти, а второй и четвертый информационные входы вычислительного элемента подключены соответственно к входам вторых . триггеров второго и третьего регистров

20

25

амяти; выходы первых триггеров втоого и третьего регистров памяти соеинены соответственно с первыми инормационными входами второго и реть- его коммутаторов, вьрсоды вторых тпиг- геров второго и третьего регистров паяти - соответственно с вторыми информационными входами второго и третьего коммутаторов, первые управляющие вхо- д ды второго и третьего коммутаторов соединены с четвертым тактовым входом, а вторые управляющие входы - с третьм тактовым входом вычислительного элемента, первый, второй и третий вхо- ы комбинационного сумматора соответственно соединены с выходами первого, второго и третьего коммутаторов, выход переноса комбинационного сумматора соединен с входами обоих триггеров четвертого регистра памяти, выход резуль тата комбинационного сумматора - с входами обоих триггеров пятого регистра памяти, выходы первого и второго триггеров четвертого регистра памяти соответственно соединены с первым и вторым информационными выходами вычислительного элемента, а выходы первого и второго триггеров пятого регистра памяти - с третьим и четвертым п информационными выходами вычислительного элемента, в 3-х ( (n+k+D)

вычислительных элементах третий управляющий вход элемента соединен с первым управляющим входом первого коммутатора, в 3-х (, п.) вычислительных элементах четвертый управляющий вход элемента соединен с вторым управляющим входом первого коммутатора, в S-x () вычислительных элементах r-й (,та) строки выходы первого и второго триггеров первого регистра памяти соединены с первыми входами элементов 2ИЛИ и 2И соответственно, в 3-х вычислительных элементах (, (n+k+1)) выход первого триггера соединен с первым информационным входом первого коммутатора, в 3-х вычислп- тельных элементах ((n+k+1)) выход

35

40

45

второго триггера первого регистра памяти соединен с вторым информационным входом первого коммутатора, в S-x (,п) вторые входы элементов.2И и 2ИЛИ соединены соответственно с первым и вторым управляющими входами

0

5

д

п

5

0

5

0

5

вычислительного элемента, а выходы элементов 2И--ШЛИ подключены к входам первого коммутатора, первый вход элемента 2ИЛИ соединен с выходом основного триггера первого регистра памяти, а первый вход элемента 2И соединен с выходом дополнительного триггера . первого регистра памяти, входы синхронизации у нечетных и четных триггеров каждого из трех первых регистров памяти вычислительного элемента подключены соответственно к второму и первому тактовым входам, а в четвертом и пятом регистрах памяти у четных и нечетных триггеров - к второму и первому тактовым входам соответственно.

ft/8.2

фиг.}

I

8

Ц

ю

ч

Фиг. 5

Фаг.7

vj- in CM OS

o

itf

r

1П fsl

o

I

л t

b

i

1

..г|с&1

4i &1

n

g

S

1

tr

д

57 LJ/5

Iш

Фие.13

Ы

24 S

Ј

В

Л С

77 С

22

Б С

D С

59

«L

5/.

52

0яв.;

fa

66 52 53

54 64

66 51

гц

ч

I

В

6364

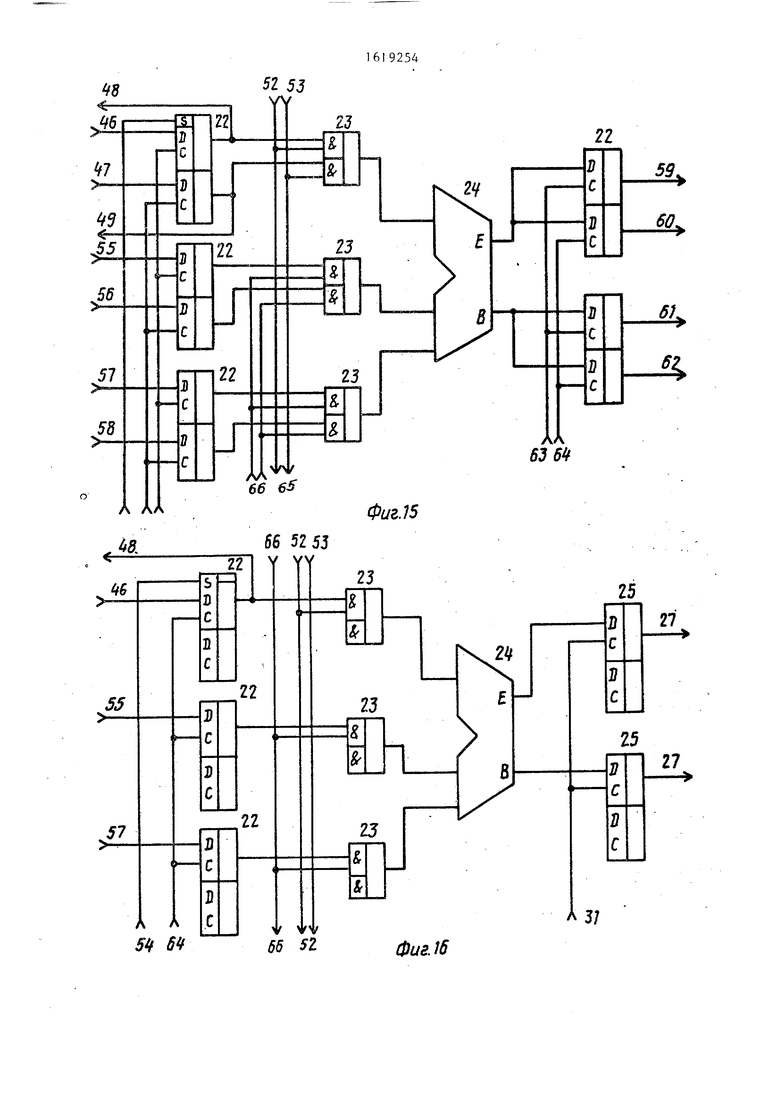

Фиг.15

гч

X

я в

Фиг. 16

«г f«-

ItNl -

щ

«S1

о

ГЪ t

«

csj «О

Ч

Е

И

см «о

4

м

л

ш

BF

| Устройство для вычисления сумм произведений | 1975 |

|

SU561963A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1988-06-22—Подача