, Изобретение относится к автоматике и вычислительтюй технике и может быть использовано в системах обработки данных для управления обменом между внешним устройством и микропроцессорной ЭВМ.

Цель изобретения - расширение класса решаемых задач за счет обеспечения дополнительнЕЛХ режимов работы устройства.

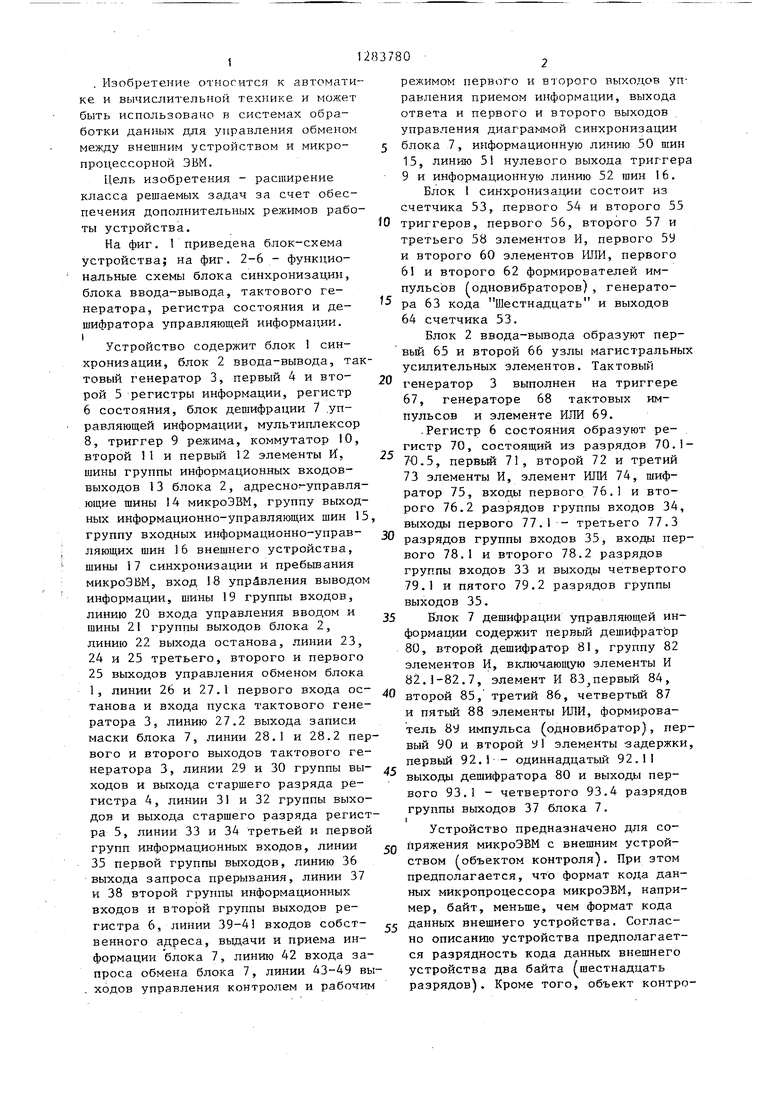

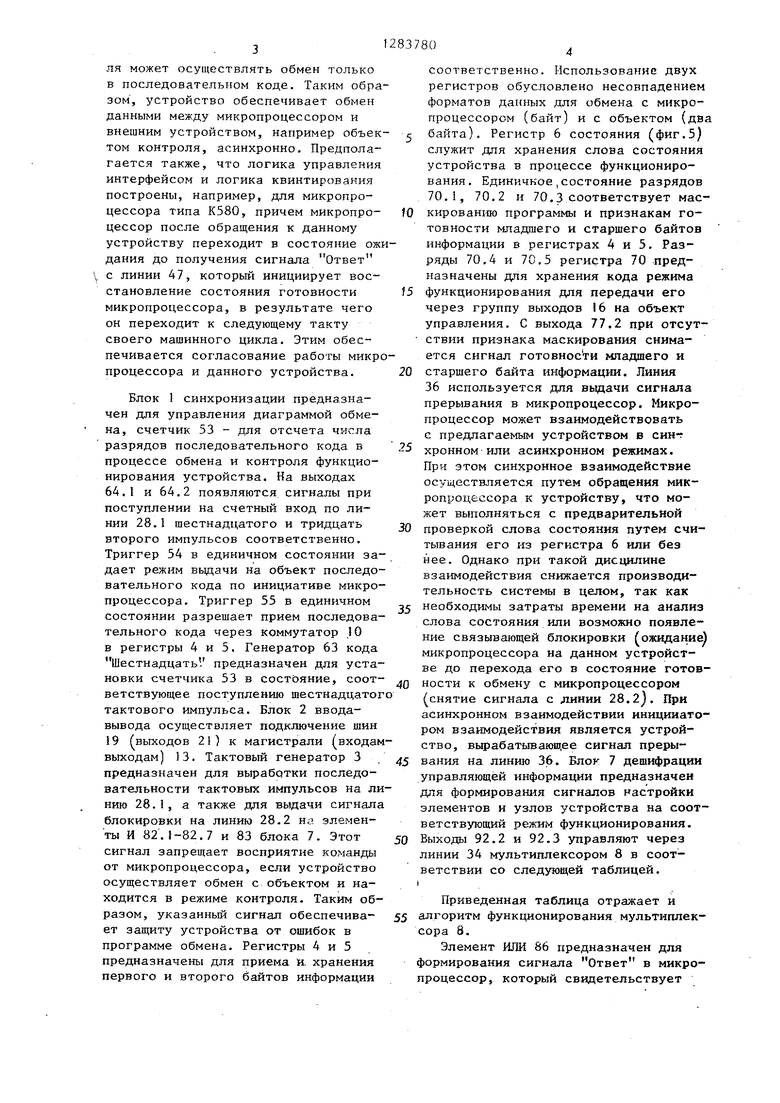

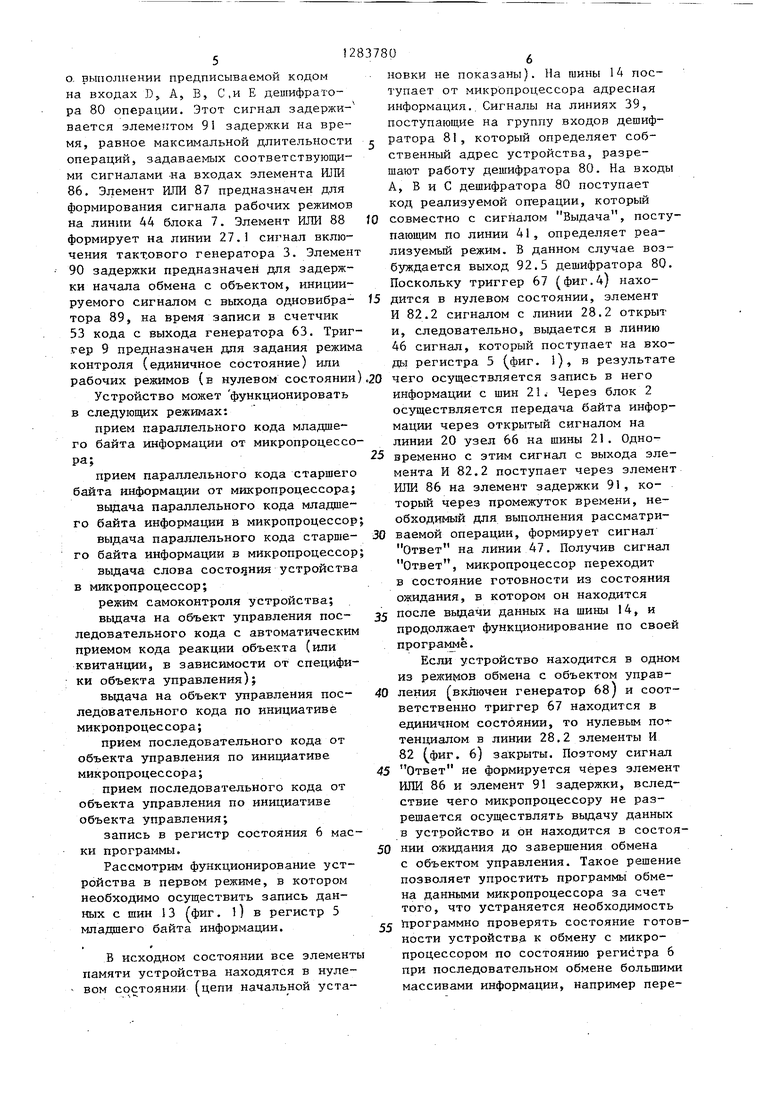

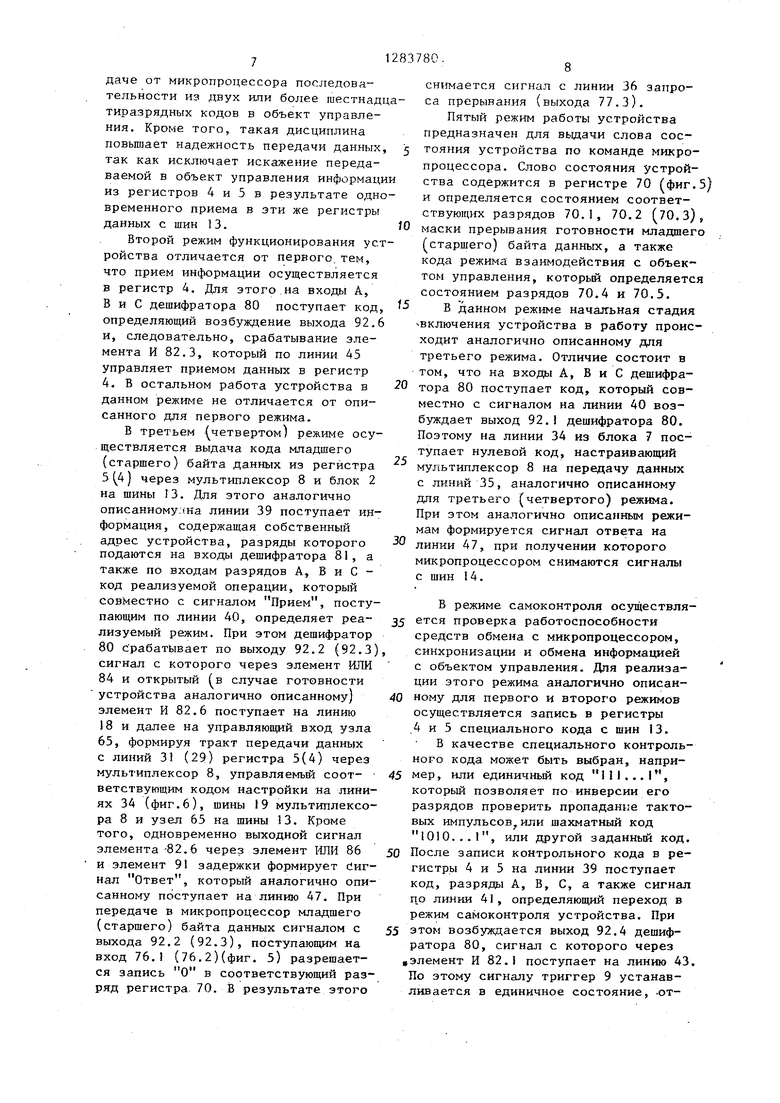

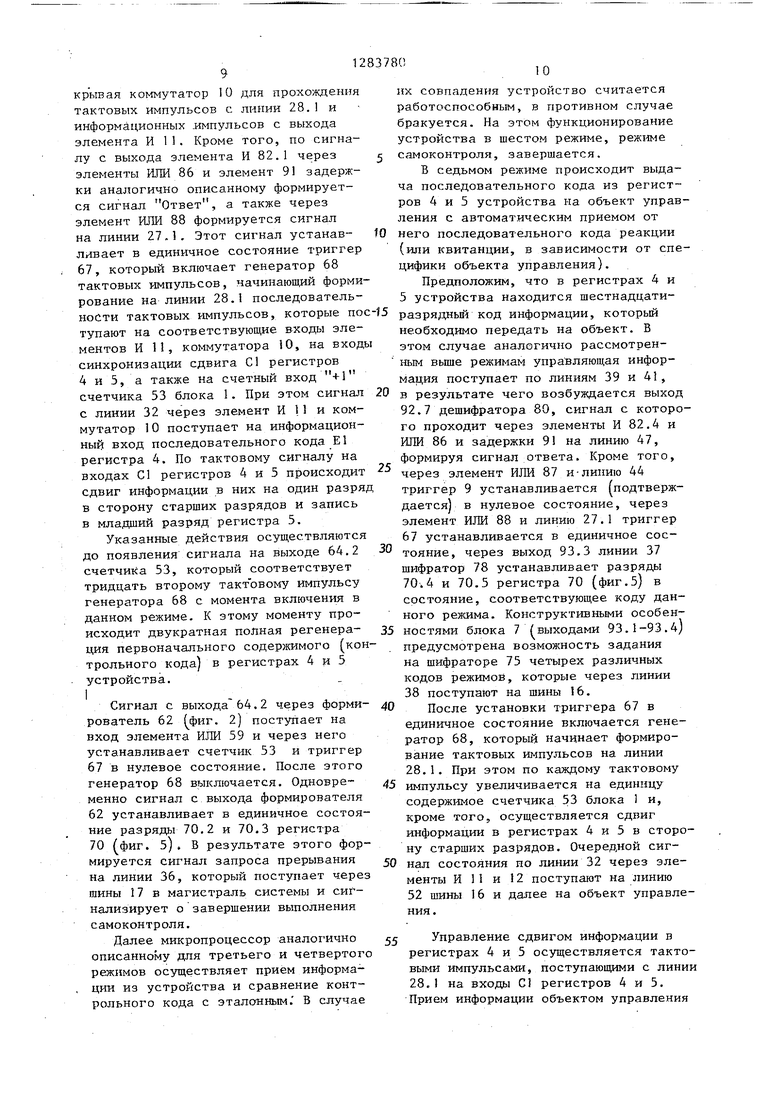

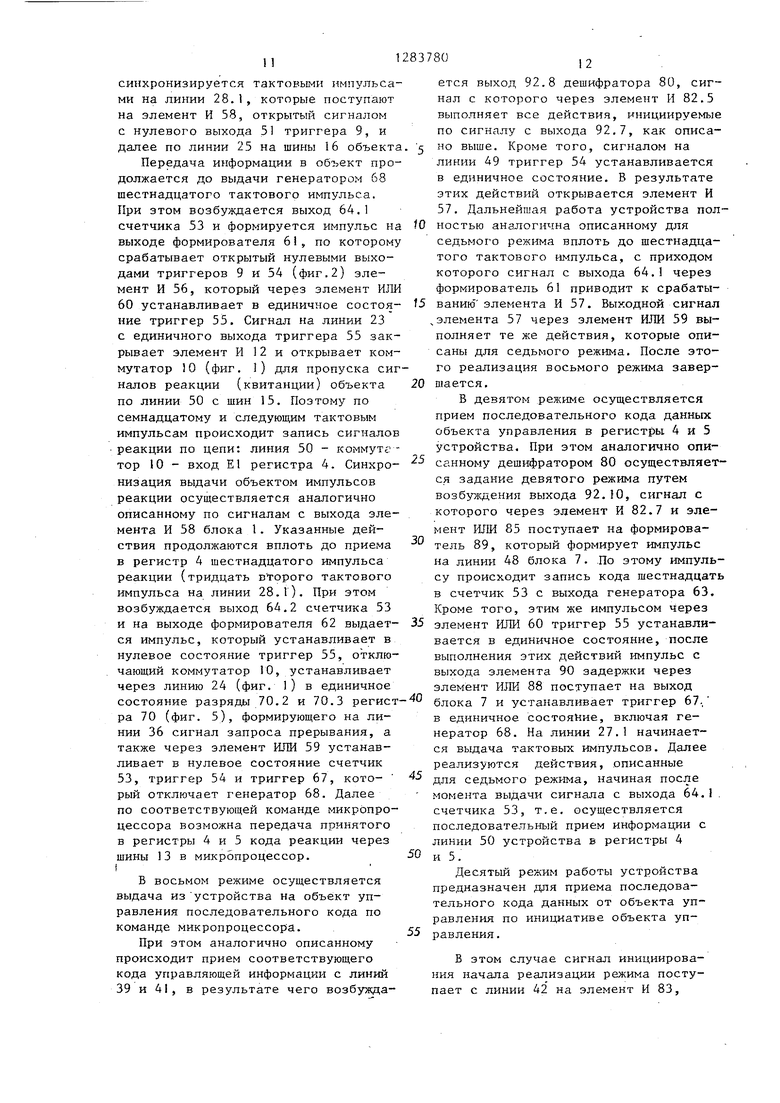

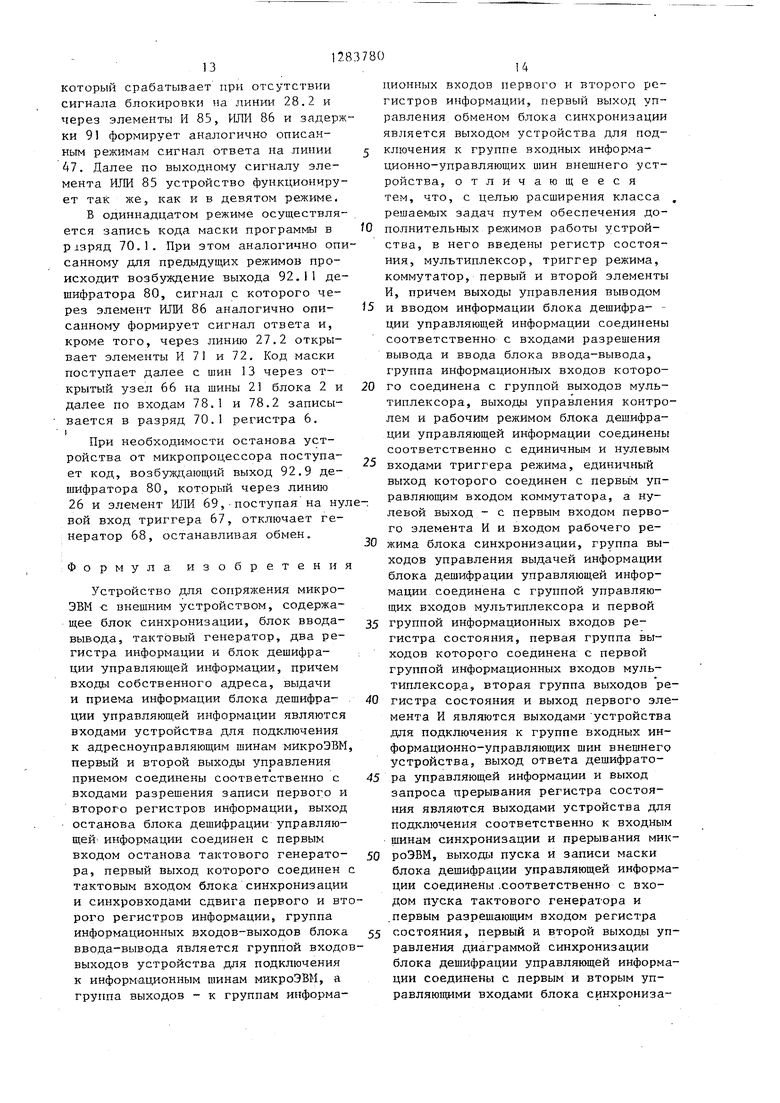

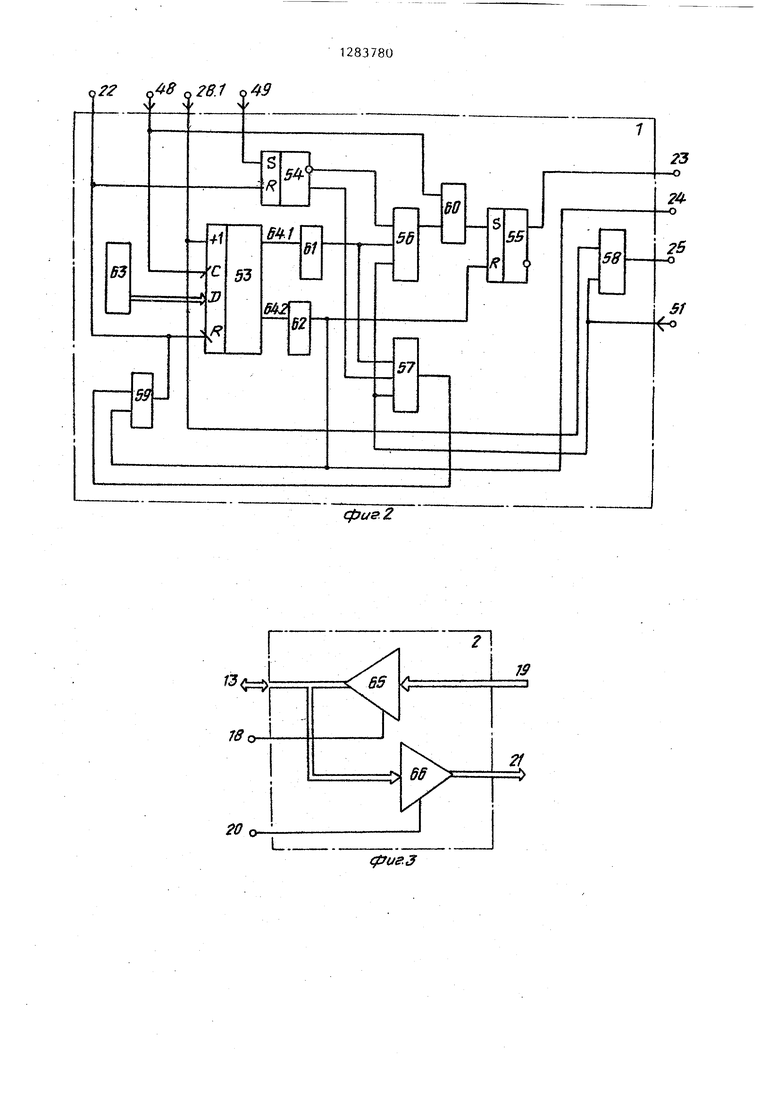

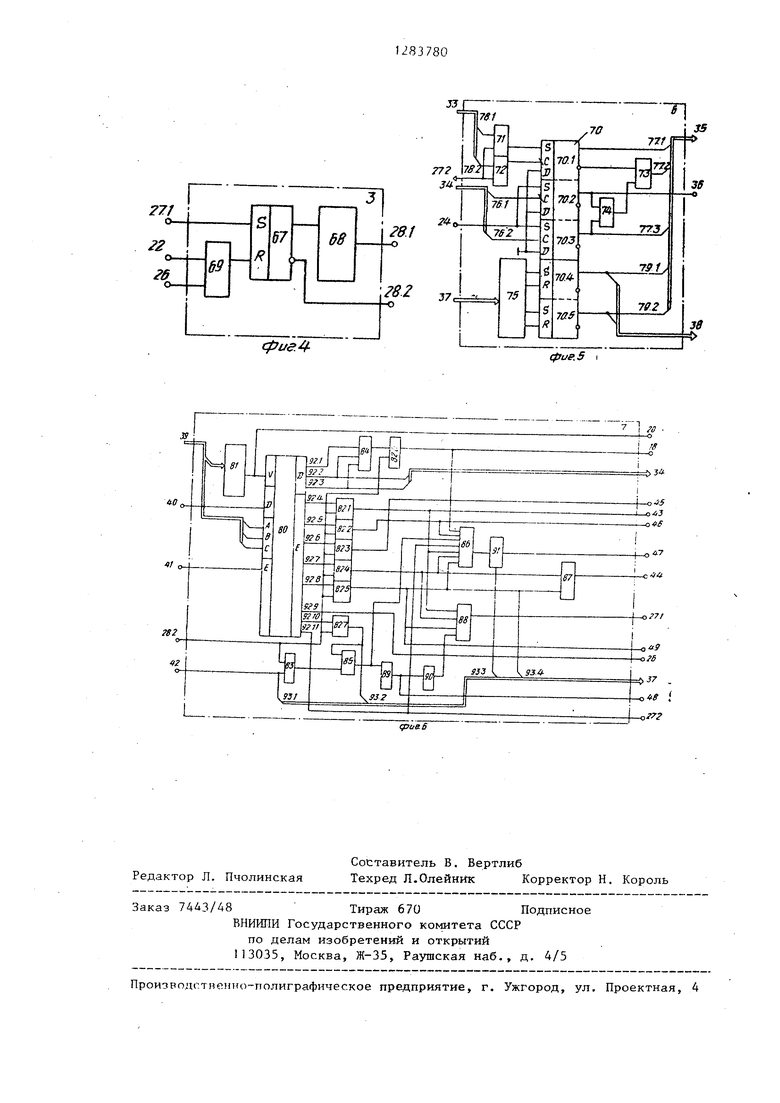

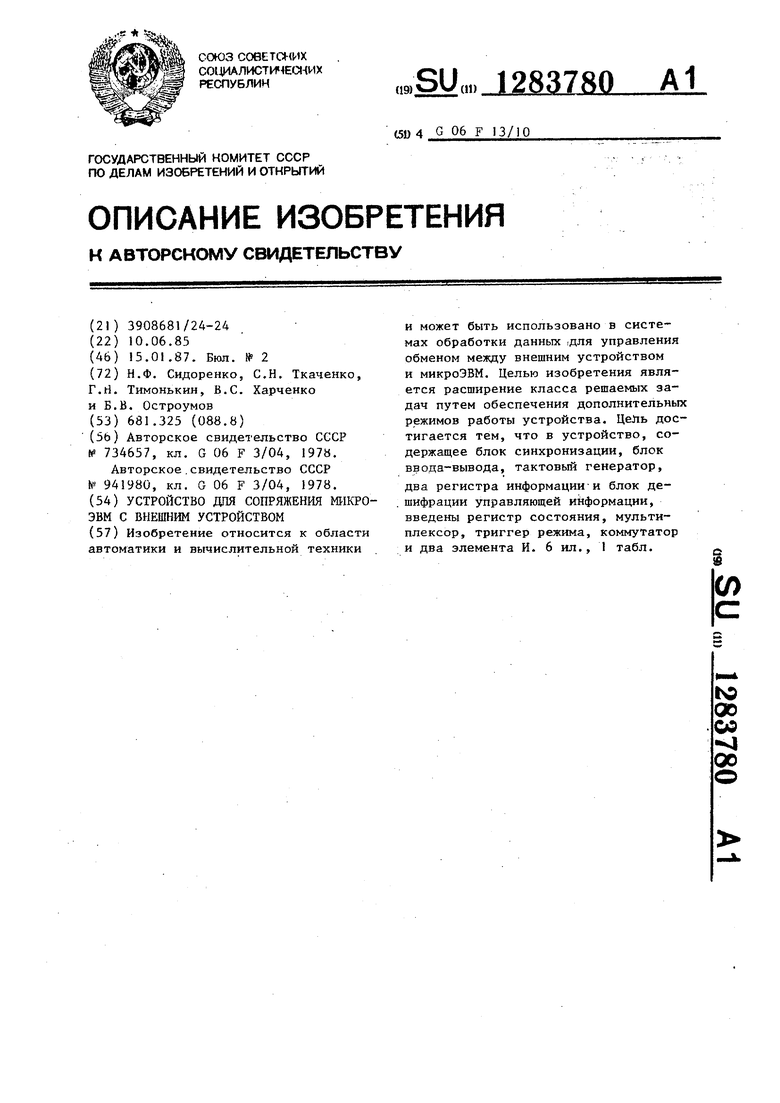

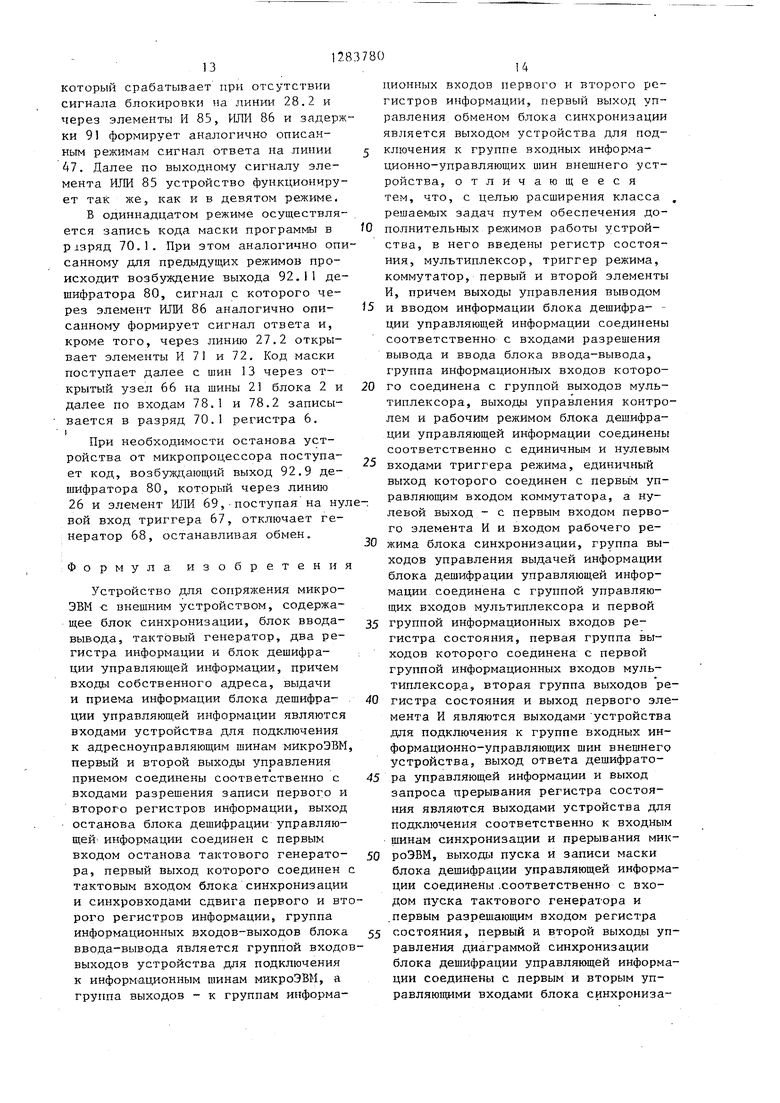

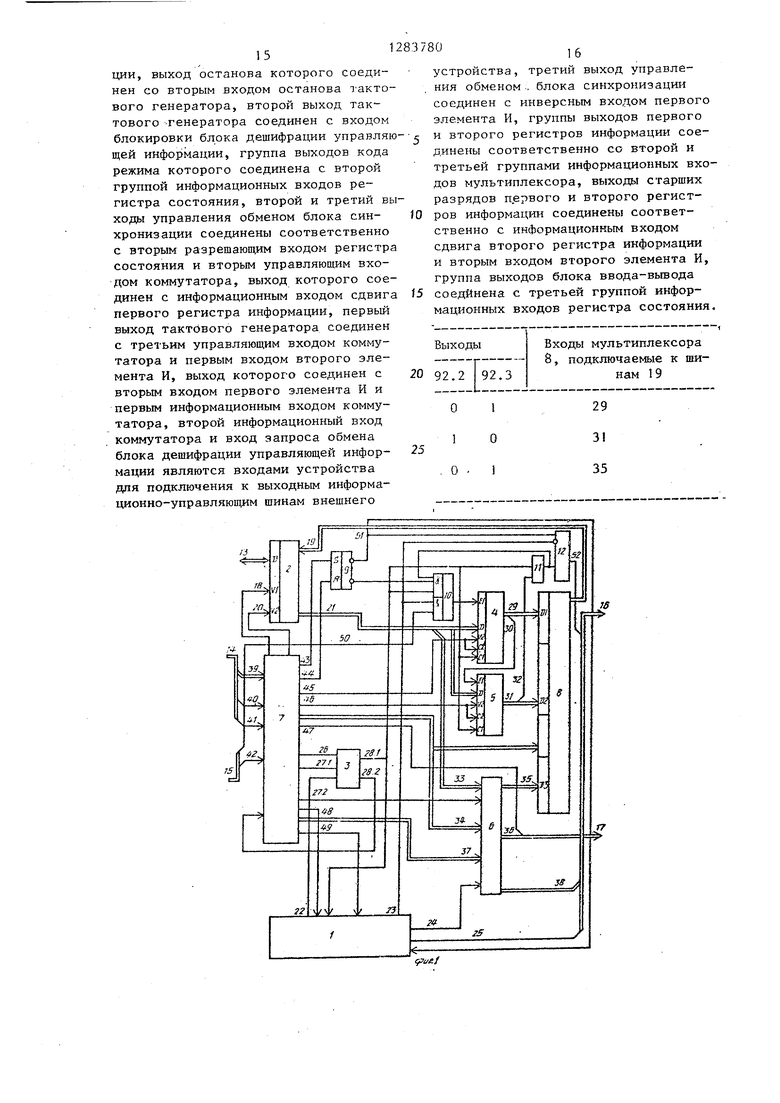

На фиг, 1 приведена блок-схема устройства; на фиг. 2-6 - функциональные схемы блока синхронизации, блока ввода-вывода, тактового генератора, регистра состояния и дешифратора управляющей информации.

Устройство содержит блок 1 синхронизации, блок 2 ввода-вывода, тактовый генератор 3, первый 4 и вто- рой 5 регистры информации, регистр 6 состояния, блок дешифрации 7 .управляющей информации, мультиплексор 8, триггер 9 режима, коммутатор 10, второй 11 и первый 12 элементы И, шины группы информационных входов- выходов 13 блока 2 , адресно -управля- ющие шины 14 микроЭВМ, группу выходных информационно-управляюш,их шин 15 группу входных информационно-управ- ляюш,их шин 16 внешнего устройства, шины 17 синхронизации и пребьюания микроэвм, вход 18 управления выводом информации, шины 19 группы входов, линию 20 входа управления вводом и шины 21 группы выходов блока 2, линию 22 выхода останова, линии 23,

24и 25 третьего, второго и первого

25выходов управления обменом блока 1, линии 26 и 27.1 первого входа останова и входа пуска тактового генератора 3, линию 27.2 выхода записи маски блока 7, линии 28.1 и 28.2 первого и второго выходов тактового генератора 3, линии 29 и 30 группы вы- ходов и выхода старшего разряда регистра 4, линии 31 и 32 группы выходов и выхода старшего разряда регистра 5, линии 33 и 34 третьей и первой групп информационных входов, линии 35 первой группы выходов, линию 36 выхода запроса прерывания, линии 37

и 38 второй группы информационных входов и второй группы выходов регистра 6, линии 39-41 входов собст- венного адреса, вьщачи и приема информации блока 7, линию 42 входа запроса обмена блока 7, линии 43-49 вы , ходов управления контролем и рабочим

0

5

0 5 о

0

5

0

режимом первого и второго выходов управления приемом информации, выхода ответа и первого и второго выходов управления диаграммой синхронизации блока 7, информационную линию 50 шин 15, линию 5 нулевого выхода триггера 9 и информационную линию 52 шин 16.

Блок 1 синхронизации состоит из счетчика 53, первого 54 и второго 55 триггеров, первого 56, второго 57 и третьего 58 элементов И, первого 5У и второго 60 элементов ИЛИ, первого 6 и второго 62 формирователей импульсов /одновибраторов), генератора 63 кода Шестнадцать и выходов 64 счетчика 53.

Блок 2 ввода-вывода образуют первый 65 и второй 66 узлы магистральных усилительных элементов. Тактовый генератор 3 выполнен на триггере 67, генераторе 68 тактовых импульсов и элементе ИЛИ 69.

-Регистр 6 состояния образуют регистр 70, состоящий из разрядов 70.1- 7€.5, первый 71, второй 72 и третий 73 элементы И, элемент ИЛИ 74, шифратор 75, входы первого 76.1 и второго 76.2 разрядов группы входов 34, выходы первого 77.1 - третьего 77.3 разрядов группы входов 35, входы первого 78.1 и второго 78.2 разрядов группы входов 33 и выходы четвертого 79.1 и пятого 79.2 разрядов группы выходов 35.

Блок 7 дешифрации управляющей информации содержит первый дешифратор 80, второй дешифратор 81, группу 82 элементов И, включающую элементы И 82.1-82.7, элемент И 83 первый 84, второй 85, третий 86, четвертый 87 и пятый 88 элементы ИЛИ, формирователь 89 импульса (одновибратор), первый 90 и второй У элементы задержки, первый 92.1 - одиннадцатый 92.11 выходы дешифратора 80 и выходы первого 93.1 - четвертого 93.4 разрядов

группы выходов 37 блока 7. I

Устройство предназначено для соЦряжения микроэвм с внешним устройством (объектом контроля). При этом предполагается, что формат кода данных микропроцессора микроЭВМ, например, байт, меньше, чем формат кода данных внешнего устройства. Согласно описанию устройства предполагается разрядность кода данных внешнего устройства два байта шестнадцать разрядов). Кроме того, объект контроля может осуществлять обмен только в последовательном коде. Таким образом , устройство обеспечивает обмен данными между микропроцессором и внешним устройством, например объектом контроля, асинхронно. Предполагается также, что логика управления интерфейсом и логика квинтирования построены, например, для микропроцессора типа К580, причем микропроцессор после обращения к данному устройству переходит в состояние ожидания до получения сигнала Ответ с линии 47, который инициирует восстановление состояния готовности микропроцессора, в результате чего он переходит к следующему такту своего машинного цикла. Этим обеспечивается согласование работы микропроцессора и данного устройства.

Блок 1 синхронизации предназначен для управления диаграммой обмена, счетчик 53 - для отсчета числа разрядов последовательного кода Б процессе обмена и контроля функционирования устройства. На выходах 64.1 и 64.2 появляются сигналы при поступлении на счетный вход по линии 28.1 шестнадцатого и тридцать второго импульсов соответственно. Триггер 54 в единичном состоянии задает режим выдачи на объект последовательного кода по инициативе микропроцессора. Триггер 55 в единичном состоянии разрешает прием последовательного кода через коммутатор 10 в регистры 4 и 5. Генератор 63 кода Шестнадцать . предназначен для установки счетчика 53 в сост&яние, соответствующее поступлению шестнадцатого тактового импульса. Блок 2 ввода- вывода осуществляет подключение шин }9 (выходов 21) к магистрали (входам- выходам) 13. Тактовый генератор 3 предназначен для выработки последовательности тактовых импульсов на линию 28.1, а также для выдачи сигнала блокировки на линию 28.2 на элементы И 82.1-82.7 и 83 блока 7. Этот сигнал запрещает восприятие команды от микропроцессора, если устройство осуществляет обмен с объектом и находится в режиме контроля. Таким образом, указанный сигнал обеспечивает защиту устройства от ошибок в программе обмена. Регистры 4 и 5 предназначены для приема и. хранения первого и второго байтов информации

5

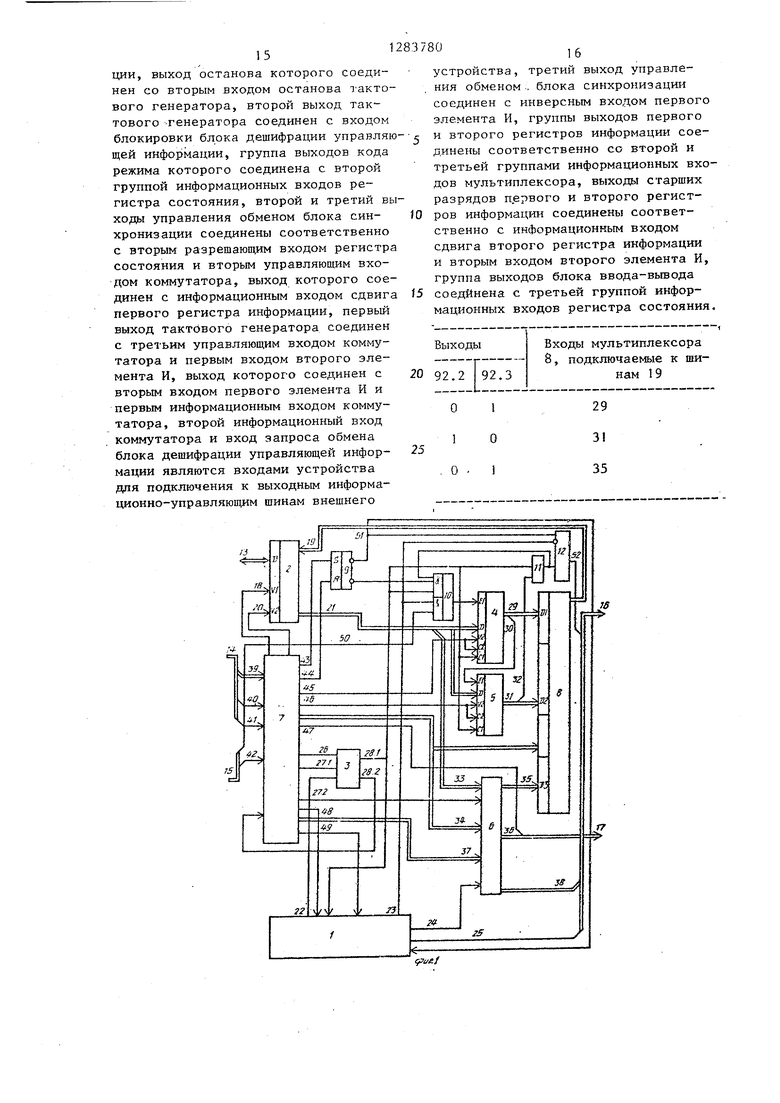

соответственно. Использование двух регистров обусловлено несовпадением форматов данных для обмена с микропроцессором (байт) и с объектом (два 5 байта). Регистр 6 состояния (фиг.5) служит для хранения слова состояния устройства в процессе функционирования . Единичное,состояние разрядов 70.1, 70.2 и 70.3 соответствует мас- 10 кированию программы и признакам готовности младшего и старшего байтов информации в регистрах 4 и 5. Разряды 70.4 и 70.5 регистра 70 предназначены для хранения кода режима 15 функционирования для передачи его через группу выходов 16 на объект управления. С выхода 77,2 при отсут- ствии признака маскирования снимается сигнал готовнос ти мпадшего и 0 старшего байта информации. Линия 36 используется для вьщачи сигнала прерывания в микропроцессор. Микропроцессор может взаимодействовать с предлагаемым устройством в син-г хронном или асинхронном режимах. При этом синхронное взаимодействие осуществляется путем обращеиия микропроцессора к устройству, что может выполняться с предварительной 0 проверкой слова состояния путем считывания его из регистра 6 или без нее. Однако при такой дисцилиие взаимодействия снижается производительность системы в целом, так как 5 необходимы затраты времени на анализ слова состояния или возможно появление связывающей блокировки (ожидание микропроцессора на данном устройстве до перехода его в состояние готов- 0 ности к обмену с микропроцессором (снятие сигнала с линии 28.2}. ПрИ асинхронном взаимодействии иницииато- ром взаимодействия является устройство, вырабатывающее сигиал преры- 5 вания на линию 36. Блок 7 дешифрации управляющей информации предназиачен для формирования сигиапов настройки элементов и узлов устройства на соответствующий режим функционирования. 0 Выходы 92.2 и 92.3 управляют через линии 34 мультиплексором 8 в соответствии со следующей таблицей. I

Приведенная таблица отражает и 5 алгоритм функционирования мультиплексора 8.

Элемент ИЛИ 86 предназначен для формирования сигнала Ответ в микропроцессор, который свидетельствует

о, выполнении предписываемой кодом на входах D, А, В, С,и Е дешифратора 80 операции. Этот сигнал задержи- вается элементом 91 задержки на время, равное максимальной длительности операций, задаваемых соответствующими сигналами -на входах элемента ШШ 86, Элемент ИЛИ 87 предназначен для формирования сигнала рабочих режимов на линии 44 блока 7. Элемент РШИ 88 W формирует на линии 27.1 сигнал включения тактового генератора 3. Элемент 90 задержки предназначен для задержки начала обмена с объектом, инициируемого сигналом с выхода одновибра- 15 тора 89, на время записи в счетчик 53 кода с выхода генератора 63. Триггер 9 предназначен для задания режима контроля (единичное состояние) или

рабочих режимов (в нулевом состоянии) .20 чего осуществляется запись в него Устройство может функционировать информации с шин 21. Через блок 2

новки не показаны). На шины 14 пос тупает от микропроцессора адресная информация.. Сигналы на линиях 39, поступающие на группу входов дешиф ратора 81, который определяет собственный адрес устройства, разрешают работу дешифратора 80. На вхо А, В и С дешифратора 80 поступает код реализуемой операции, который совместно с сигналом Выдача, пос пающим по линии 41, определяет реа лизуемый режим. В данном случае во буждается выход 92.5 дешифратора Поскольку триггер 67 фиг.4) находится в нулевом состоянии, элемен И 82.2 сигналом с линии 28.2 откры и, следовательно, выдается в линию 46 сигнал, который поступает на вх ДЬ1 регистра 5 (фиг. 1), в результ

в следующих режимах:

прием параллельного кода младшего байта информации от микропроцессора;

прием параллельного кода старшего байта информации от микропроцессора;

выдача параллельного кода младшего байта информации в микропроцессор

выдача параллельного кода старшего байта информации в микропроцессор

выдача слова состояния устройства в микропроцессор;

режим самоконтроля устройства;

вьщача на объект управления последовательного кода с автоматическим приемом кода реакции объекта (или квитан1щи, в зависимости от специфики объекта управления);

выдача на объект управления последовательного кода по инициативе микропроцессора;

прием последовательного кода от объекта управления по инициативе микропроцессора;

прием последовательного кода от объекта управления по инициативе объекта управления;

запись в регистр состояния 6 маски программы.

Рассмотрим функционирование устройства в первом режиме, в котором необходимо осуществить запись данных с шин 13 (фиг. 1) в регистр 5 младшего байта информации.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии (цепи начальной устачего осуществляется запись в него информации с шин 21. Через блок 2

новки не показаны). На шины 14 поступает от микропроцессора адресная информация.. Сигналы на линиях 39, поступающие на группу входов дешифратора 81, который определяет собственный адрес устройства, разрешают работу дешифратора 80. На входы А, В и С дешифратора 80 поступает код реализуемой операции, который совместно с сигналом Выдача, поступающим по линии 41, определяет реализуемый режим. В данном случае возбуждается выход 92.5 дешифратора 80. Поскольку триггер 67 фиг.4) находится в нулевом состоянии, элемент И 82.2 сигналом с линии 28.2 открыт и, следовательно, выдается в линию 46 сигнал, который поступает на вхо- ДЬ1 регистра 5 (фиг. 1), в результате

осуществляется передача байта информации через открытый сигналом на линии 20 узел 66 на шины 21. Одно5 временно с этим сигнал с выхода элемента И 82.2 поступает через элемент ИЛИ 86 на элемент задержки 91, который через промежуток времени, необходимый для выполнения рассматри0 ваемой операции, формирует сигнал Ответ на линии 47. Получив сигнал Ответ, микропроцессор переходит в состояние готовности из состояния ожидания, в котором он находится после вьщачи данных на шины 14, и продолжает функционирование по своей программе.

Если устройство Находится в одном из режимов обмена с объектом управления (включен генератор 68) и соответственно триггер 67 находится в единичном состоянии, то нулевым пo тенциалом в линии 28.2 элементы И 82 (фиг. б) закрыты. Поэтому сигнал

5 Ответ не формируется через элемент ИЛИ 86 и элемент 91 задержки, вследствие чего микропроцессору не разрешается осуществлять выдачу данных в устройство и он находится в состоя0 НИИ ожидания до завершения обмена с объектом управления. Такое решение позволяет упростить программы обмена данными микропроцессора за счет того, что устраняется необходимость

5 программно проверять состояние готовности устройства к обмену с микропроцессором по состоянию регистра 6 при последовательном обмене большими массивами информации, например пере5

0

даче от микропроцессора последовательности из двух И.ПИ более шестнадтиразрядных кодов в объект управления. Кроме того, такая дисциплина повьш1ает надежность передачи данных так как исключает искажение передаваемой в объект управления информац из регистров 4 и 5 в результате однвременного приема в эти же регистры данных с шин 13.

Второй режим функционирования усройства отличается от первого.тем, что прием информации осуществляется в регистр 4. Для этого на входы А, В и С дешифратора 80 поступает код определяющий возбуждение выхода 92. и, следовательно, срабатывание элемента И 82.3, который по линии 45 управляет приемом данных в регистр 4. В остальном работа устройства в данном режиме не отличается от описанного для первого режима.

В третьем (четвертом) режиме осуществляется выдача кода младшего (старшего) байта данных из регистра 5 (4) через мультиплексор 8 и блок 2 на шины 13. Для этого аналогично описанному.ша линии 39 поступает информация, содержащая собственный адрес устройства, разряды которого подаются на входы дешифратора 81, а также по входам разрядов А, В и С - код реализуемой операции, который совместно с сигналом Прием, поступающим по линии 40, определяет реализуемый режим. При этом дешифратор 80 с рабатывает по выходу 92.2 (92.3 сигнал с которого через элемент ИЛИ

84 и открытый (в случае готовности

-

устройства аналогично описанному;

элемент И 82.6 поступает на линию 18 и далее на управляющий вход узла 65, формируя тракт передачи данных с линий 31 (29) регистра 5(4) через мультиплексор 8, управляемый соот- ветствующим кодом настройки на линиях 34 (фиг.6), шины 19 мультиплексора 8 и узел 65 на шины J3. Кроме того, одновременно выходной сигнал элемента-82.6 через элемент ЮТИ 86 и элемент 91 задержки формирует йиг- нал Ответ, который аналогично описанному поступает на линию 47, При передаче в микропроцессор младшего (старшего) байта данных сигналом с выхода 92.2 (92.3), поступающим на вход 76.1 (76.2)(фиг. 5) разреюает

ся запись О в соответствующий разряд регистра 70. В результате этого

5

0

5

50

0

сн1тается сигнал с линии 36 запроса прерывания (выхода 77.3).

Пятый режим работы устройства предназначен для выдачи слова состояния устройства по команде микропроцессора. Слово состояния устройства содержится в регистре 70 (фиг.5) и определяется состоянием соответ- ствующ1 х разрядов 70.1, 70.2 (70.3), маски прерывания готовности младшего (старшего) байта данных, а также кода режима: взаимодействия с объектом управления, которьй определяется состоянием разрядов 70.4 и 70.5.

В данном режиме начальная стадия включения устройства в работу происходит аналогично описанному для третьего режима. Отличие состоит в том, что на входы А, В и С дешифратора 80 поступает код, который совместно с сигналом на линии 40 возбуждает выход 92.1 дешифратора 80. Поэтому на линии 34 из блока 7 поступает нулевой код, настраивающий мультиплексор 8 на передачу данных с линий 35, аналогично описанному для третьего (четвертого) режима. При этом аналогично описанным режимам формируется сигнал ответа на линии 47, при получении которого микропроцессором снимаются сигналы с шин 14.

0

5

0

5

В режиме самоконтроля осзтцествля- 5 ется проверка работоспособности средств обмена с микропроцессором, синхронизации и обмена информацией с объектом управления. Для реализации этого режима аналогично описанному для первого и второго режимов осуществляется запись в регистры .4 и 5 специального кода с шин 13.

В качестве специального контрольного кода может быть выбран, например, или единичный код П1...1, который позволяет по инверсии его разрядов проверить пропадание тактовых импульсов,или шахматный код 1010..., или другой заданный код. После записи контрольного кода в регистры 4 и 5 на линии 39 поступает код, разряда А, В, С, а также сигнал до линии 41, определяющий переход в режим самоконтроля устройства. При этом возбуждается выход 92.4 дешифратора 80, сигнал с которого через ,элемент И 82.1 поступает на линию 43. По этому сигналу триггер 9 устанавливается в единичное состояние, -открывая коммутатор 10 для прохождения тактовых импульсов с линии 28.1 и информационных лмпульсов с выхода элемента И 11. Кроме того, по сигналу с выхода элемента И 82.1 через элементы ИЛИ 86 и элемент 91 задержки аналогично описанному формируется сигнал Ответ, а также через элемент ИЛИ 88 формируется сигнал на линии 27.1. Этот сигнал устанавливает в единичное состояние триггер 67, который включает генератор 68 тактовых импульсов, начинающий формирование на линии 28.1 последователь10

их совпадения устройство считается работоспособным, в противном случа бракуется. На этом функционировани устройства в шестом режиме, режиме самоконтроля, завершается.

В седьмом режиме происходит выд ча последовательного кода из регис ров 4 и 5 устройства на объект упр ления с автоматическим приемом от него последовательного кода реакци (или квитанции, в зависимости от с цифики объекта управления).

Предположим, что в регистрах 4 5 устройства находится шестнадцати

ности тактовых импульсов, которые пос-15 разрядаьш код информации, который

тупают на соответствующие входы элементов И 11, коммутатора 10, на вход синхронизации сдвига С1 регистров 4 и 5, а также на счетный вход ч-Г счетчика 53 блока 1. При этом сигнал с линии 32 через элемент И 11 и коммутатор 10 поступает на информационный вход последовательного кода Е1 регистра 4. По тактовому сигналу на входах С1 регистров 4 и 5 происходит сдвиг информации в них на один разря в сторону старших разрядов и запись в младший разряд регистра 5.

Указанные действия осуществляются до появления сигнала на выходе 64.2 счетчика 53, который соответствует тридцать второму тактЪвому импульсу генератора 68 с момента включения в данном режиме. К этому моменту происходит двукратная полная регенерация первоначального содержимого (контрольного кода) в регистрах 4 и 5 устройства.

I

Сигнал с выхода 64.2 через формирователь 62 (фиг. 2) поступает на вход элемента ИЛИ 59 и через него устанавливает счетчик 53 и триггер 67 в нулевое состояние. После этого генератор 68 выключается. Одновременно сигнал с выхода формирователя 62 устанавливает в единичное состояние разряды 70,2 и 70.3 регистра 70 фиг. 5). В результате этого формируется сигнал запроса прерывания на линии 36, который поступает через шины 17 в магистраль системы и сигнализирует о завершении выполнения самоконтроля.

Далее микропроцессор аналогично описанному для третьего и четвертого режимов осуществляет прием информации из устройства и сравнение контрольного кода с эталонньм. В случае

их совпадения устройство считается работоспособным, в противном случае бракуется. На этом функционирование устройства в шестом режиме, режиме самоконтроля, завершается.

В седьмом режиме происходит выдача последовательного кода из регистров 4 и 5 устройства на объект управления с автоматическим приемом от него последовательного кода реакции (или квитанции, в зависимости от специфики объекта управления).

Предположим, что в регистрах 4 и 5 устройства находится шестнадцати5

0

необходимо передать на объект. В этом случае аналогично рассмотренным вьш1е режимам управляющая информация поступает по линиям 39 и 41,

0 в результате чего возбуждается выход 92.7 дешифратора 80, сигнал с которого проходит через элементы И 82.4 и ИЛИ 86 и задержки 91 на линию 47, формируя сигнал ответа. Кроме того, через элемент ИЛИ 87 и-линию 44 триггер 9 устанавливается (подтверждается в нулевое состояние, через элемент ИЛИ 88 и линию 27.1 триггер 67 устанавливается в единичное состояние, через выход 93.3 линии 37 шифратор 78 устанавливает разряды 70.4 и 70.5 регистра 70 (фиг.5) в состояние, соответствующее коду данного режима. Конструктивными особен5 ностями блока 7 (выходами 93.1-93.4) предусмотрена возможность задания на шифраторе 75 четырех различных кодов режимов, которые через линии 38 nocTynaioT на шины 16,

0 После установки триггера 67 в

единичное состояние включается генератор 68, который начинает формирование тактовых импульсов на линии 28.1. При этом по каждому тактовому

5 импульсу увеличивается на единицу содержимое счетчика 53 блока 1 и, кроме того, осуществляется сдвиг информации в регистрах 4 и 5 в сторону старших разрядов. Очередной сиг0 нал состояния по линии 32 через элементы И 11 и 12 поступают на линию 52 шины 16 и далее на объект управления.

5 Управление сдвигом информации в регистрах 4 и 5 осуществляется тактовыми импульсами, поступающими с линии 28,1 на входы С1 регистров 4 и 5. Прием информации объектом управления

синхронизируется тактовыми импульсами на линии 28.1, которые поступают на элемент И 58, открытый сигналом с нулевого выхода 51 триггера 9, и далее по линии 25 на шины 16 объекта Передача информации в объект продолжается до выдачи генератором 68 шестнадцатого тактового имнульса. При этом возбуждается выход 64.1 счетчика 53 и формируется имнульс на выходе формирователя 61, по которому срабатывает открытый нулевыми выходами триггеров 9 и 54 (фиг.2) элемент И 56, который через элемент ИЛИ 60 устанавливает в единичное состояние триггер 55. Сигнал на линии 23 с единичного выхода триггера 55 закрывает элемент И 12 и открывает коммутатор 10 (фиг. 1) для пропуска сигналов реакции (квитанции) объекта но линии 50 с шин 15. Поэтому по семнадцатому и следующим тактовым импульсам происходит запись сигналов реакции по цепи: линия 50 - коммутг- тор 10 - вход Е1 регистра 4. Синхронизация выдачи объектом импульсов реакции осуществляется аналогично описанному по сигналам с выхода элемента И 58 блока I. Указанные действия продолжаются вплоть до приема в регистр 4 шестнадцатого импульса реакции (тридцать в торого тактового импульса на линии 28.1). При этом возбуждается выход 64.2 счетчика 53 и на выходе формирователя 62 выдается импульс, который устанавливает в нулевое состояние триггер 55, отключающий коммутатор 10, устанавливает через линию 24 (фиг. 1) в единичное состояние разряды 70.2 и 70.3 регистра 70 (фиг. 5), формирующего на линии 36 сигнал запроса прерывания, а также через элемент ИЛИ 59 устанавивает в нулевое состояние счетчик 53, триггер 54 и триггер 67, который отключает генератор 68. Далее по соответствующей команде микропроцессора возможна передача принятого в регистры 4 и 5 кода реакции через

ины 13 в микропроцессор.

Б восьмом режиме осуществляется ыдача из устройства на объект упавления последовательного кода по оманде микропроцессора.

При этом аналогично описанному роисходит прием соответствующего ода управляющей информации с линий 9 и 41, в результате чего возбуждается выход 92.8 дешифратора 80, сигнал с которого через элемент И 82.5 выполняет все действия, инициируемые по сигналу с выхода 92.7, как описа- 5 но выше. Кроме того, сигналом на

линии 49 триггер 54 устанавливается в единичное состояние. В результате этих действий открывается элемент И 57. Дальнейшая работа устройства пол- 10 ностью аналогична описанному для

седьмого режима вплоть до шестнадцатого тактового импульса, с приходом которого сигнал с выхода 64.1 через формирователь 61 приводит к срабаты- 15 ванию элемента И 57. Выходной сигнал элемента 57 через элемент ИЛИ 59 выполняет те же действия, которые описаны для седьмого режима. После этого реализация восьмого режима завер- 20 шается.

В девятом режиме осуществляется прием последовательного кода данных объекта управления в регистры 4 и 5 устройства. При этом аналогично опи- 2-5 санному дешифратором 80 осуществляется задание девятого режима путем возб окдения выхода 92. 10, сигнал с которого через элемент И 82.7 и элемент ИЛИ 85 поступает на формирова- тель 89, который формирует имнульс на линии 48 блока 7. Ло этому импульсу происходит запись кода шестнадцать в счетчик 53 с выхода генератора 63. Кроме того, этим же импульсом через 35 элемент ИЛИ 60 триггер 55 устанавливается в единичное состояние, после выполнения этих действий импульс с выхода элемента 90 задержки через элемент ИЛИ 88 поступает на выход блока 7 и устанавливает триггер 67., в единичное состояние, включая генератор 68. На линии 27.1 начинается выдача тактовых импульсов. Далее реализуются действия, описанные для седьмого режима, начиная после момента выдачи сигнала с выхода 64.1. счетчика 53, т.е. осуществляется последовательный прием информации с линии 50 устройства в регистры 4 0 и 5.

Десятый режим работы устройства предназначен для приема последовательного кода данных от объекта управления по инициативе объекта уп5

равления.

Б этом случае сигнал инициирования начала реализации режима поступает с линии 42 на элемент И 83,

который срабатывает при отсутствии сигнала блокировки на линии 28.2 и через элементы И 85, РШИ 86 и задержки 91 формирует аналогично описанным режимам сигнал ответа на линии 47. Далее по выходному сигналу элемента HIM 85 устройство функционирует так же, как и в девятом режиме.

В одиннадцатом режиме осуществляется запись кода маски программы в Р13РЯД 70.1. При этом аналогично описанному для предыдущих режимов происходит возбуждение выхода 92.11 дешифратора 80, сигнал с которого через элемент HJM 86 аналогично описанному формирует сигнал ответа и, кроме того, через линию 27.2 открывает элементы И 71 и 72. Код маски поступает далее с шин 13 через открытый узел 66 на шины 21 блока 2 и далее по входам 78.1 и 78.2 записывается в разряд 70.1 регистра 6. I

При необходимости останова устройства от микропроцессора поступает код, возбуждающий выход 92.9 дешифратора 80, который через линию 26 и элемент ИЛИ 69,поступая на нувой вход триггера 67, отключает генератор 68, останавливая обмен.

Формула изобретения

Устройство для сопряжения микро- ЭВМ ; внешним устройством, содержащее блок синхронизации, блок ввода- вывода, тактовый генератор, два регистра информации и блок дешифрации управляющей информации, причем входы собственного адреса, выдачи и приема информации блока дешифра- ции управляющей информации являются входами устройства для подключения к адресноуправляющим шинам микроЭВМ первый и второй выходы управления приемом соединены соответственно с входами разрешения записи первого и второго регистров информации, выход останова блока дешифрации управляю- щей информации соединен с первым входом останова тактового генератора, первый выход которого соединен тактовым входом блока синхронизации и синхровходами сдвига первого и втрого регистров информации, группа информационных входов-выходов блока ввода-вывода является группой входо выходов устройства для подключения к информационным шинам микроЭВМ, а группа выходов - к группам информа

5

0

5

0

5

0

5

5

0

ционных входов первого и второго регистров информации, первый выход управления обменом блока синхронизации является выходом устройства для подключения к группе входных информационно-управляющих шин внешнего устройства, отличающееся тем, что, с целью расширения класса , решаемых задач путем обеспечения дополнительных режимов работы устройства, в него введены регистр состояния, мультиплексор, триггер режима, коммутатор, первый и второй элементы И, причем выходы управления выводом и вводом информации блока дешифра- - ции управляющей информации соединены соответственно с входами разрешения вывода и ввода блока ввода-вывода, группа информационных входов которого соединена с группой выходов мультиплексора, выходы управления контролем и рабочим режимом блока дешифрации управляющей информации соединены соответственно с единичным и нулевым входами триггера режима, единичный выход которого соединен с первь1м управляющим входом коммутатора, а нулевой выход - с первым входом первого элемента И и входом рабочего режима блока синхронизации, группа выходов управления выдачей информации блока дешифрации управляющей информации соединена с группой управляющих входов мультиплексора и первой группой информационных входов регистра состояния, первая группа выходов которого соединена с первой группой информационных входов мультиплексора, вторая группа выходов регистра состояния и выход первого элемента И являются выходами устройства для подключения к группе входных информационно-управляющих шин внешнего устройства, выход ответа дешифратора управляющей информации и выход запроса прерывания регистра состояния являются выходами устройства для подключения соответственно к входным шинам синхронизации и прерывания микроЭВМ, выходы пуска и записи маски блока дешифрации управляющей информации соединены .соответственно с входом пуска тактового генера7 ора и .первым разрешающим входом регистра состояния, первый и второй выходы управления диаграммой синхронизации блока дешифрации управляющей информации соединены с первым и вторым управляющими входами блока синхронизации, выкод останова которого соединен со вторым входом останова 1 акто- вого генератора, второй выход тактового генератора соединен с входом блокировки блока дешифрации управляющей информации, группа выходов кода режима которого соединена с второй группой информационных входов регистра состояния, второй и третий выходы управления обменом блока синхронизации соединены соответственно с вторым разрешающим входом регистра состояния и вторым управляющим входом коммутатора, выход которого соединен с информационным входом сдвига первого регистра информации, первый выход тактового генератора соединен с третьим управляющим входом коммутатора и первым входом второго элемента И, выход которого соединен с вторым входом первого элемента И и первым информационным входом коммутатора, второй информационный вход коммутатора и вход запроса обмена блока дешифрации управляющей информации являются входами устройства для подключения к выходным информа- ционно-управляюпщм шинам внешнего

и

устройства, третий выход управления обменом . блока синхронизации соединен с инверсным входом первого элемента И, группы выходов первого и второго регистров информации соединены соответственно со второй и третьей группами информационных входов мультиплексора, выходы старших разрядов первого и второго регистров информации соединены соответственно с информационным входом сдвига второго регистра информации и вторым входом второго элемента И, группа выходов блока ввода-вьшода соединена с третьей группой информационных входов регистра состояния.

Выходы

92.2 I 92.3

Входы мультиплексора 8, подключаемые к шинам 19

29

25

31

35

fue/

22

В ..28.1 о49

фиг 2

0

L..

В5

JS

д6

21

(uff.3

69

R

57

58

сриеЛ

пг

272

га/

8.2

о

cfjue.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля | 1985 |

|

SU1293739A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах обработки данных .для управления обменом между внешним устройством и микроэвм. Целью изобретения является расширение класса решаемых задач путем обеспечения дополнительных режимов работы устройства. ЦеЛь достигается тем, что в устройство, содержащее блок синхронизации, блок врода-вывода, тактовый генератор, два регистра информации-и блок дешифрации управляющей информации, введены регистр состояния, мультиплексор, триггер режима, коммутатор и два элемента И. 6 ил., 1 табл. to 00 со 00

3S

-7 го

. о«# .

г

дзиеВ

Редактор Л. Пчолинская

Заказ 74АЗ/48Тираж 670Подписное

ВНИИПИ Государственного KONOiTeTa СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производстнемио-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель В. Вертлиб

Техред Л.Олейнйк Корректор Н. Король

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена управляющей ЭВМ с объектами контроля | 1980 |

|

SU941980A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-06-10—Подача