V

К-0

о

ю

Jb о

00

Изобретение относится к электроизмерительной технике и может быть использовано в системах автоматического контроля параметров элементов электрических цепей и измерительных приборах универсального и специального назначения.

Целью изобретения является повышение точности.

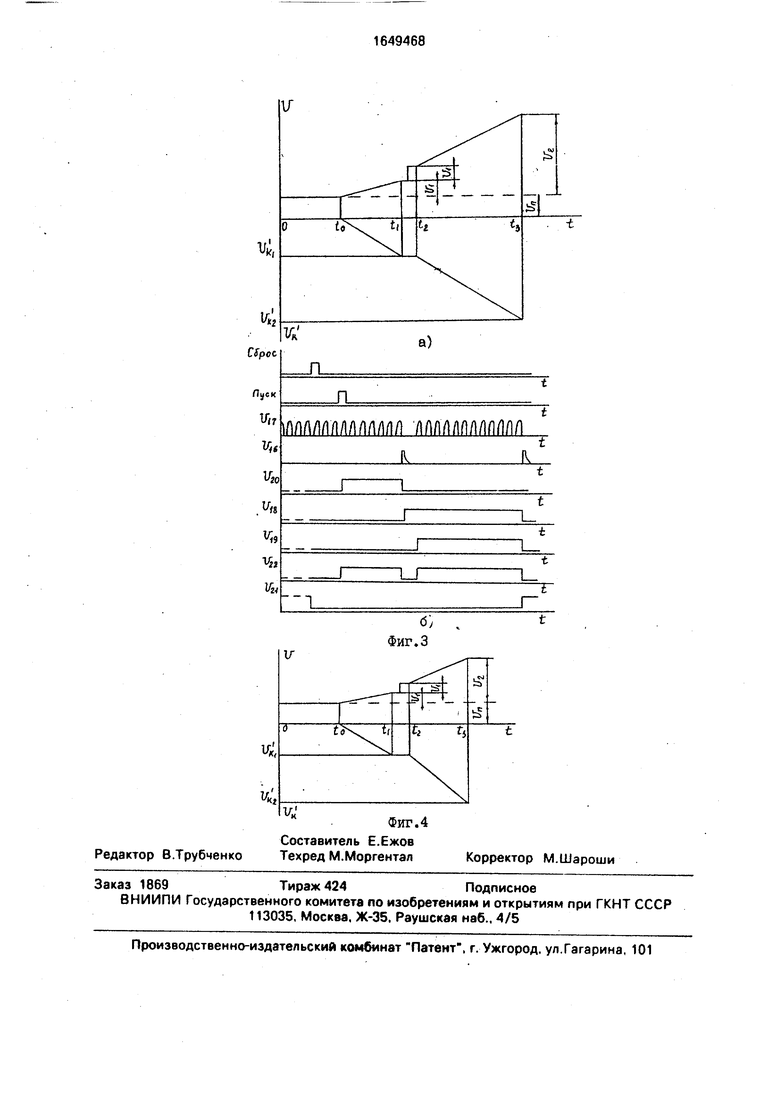

На фиг. 1 приведена структурная электрическая схема устройства для измерения сопро- тивления; на фиг. 2 - структурная электрическая схема блока управления; на фиг. 3, 4 - временные диаграммы, поясняющие работу устройства для измерения сопротивления,

Устройство для измерения сопротивления (фиг. 1) содержит генераторный пороговый блок 1 (например, генератор гармонических колебаний) с заданным порогом срабатывания Un. обеспечивающим его самовозбуждение, резистивный делитель 2 напряжения (состоящий из образцового R0 и измеряемого RX) резисторов, управляемый делитель 3 напряжения, интегратор 4, инвертор 5, блок б управления, первый ключ 7, первый счетчик 8, источник 9 опорного напряжения Uo. второй ключ 10, третий ключ 11, второй счетчик 12, цифровой делительный блок 13, сумматор 14, переключатель 15, причем выход интегратора 4 соединен с входом управляемого делителя 3 напряжения, через инвертор 5 - со средней точкой резистивного делителя 2 напряжения и входом генераторного порогового блока 1, выход 16 формирования импульсов команд которого соединен с первым входом блока 6 управления, а информационный выход 17 - с вторым входом блока 6 управления, через ключ 11 - с информационным входом счетчика 12 и через ключ 10 - с информационным входом счетчика 8, источник 9 опорного напряжения соединен с первым входом сумматора 14, второй вход которого соединен с выходом переключателя 15, а выход через ключ 7 - с входом интегратора 4,выход управляемого делителя 3 напряжения соединен с резистивным делителем 2 напряжения, а управляющий вход - с первым управляющим входом переключателя 15 и выходом 18 блока 6 управления, выходы 19 и 20 которого соединены с управляющими входами ключей 10 и 11, выходы счетчиков 12 и 8 соединены с входами делимого и делителя цифрового делительного блока 13, вход разрешения деления которого соединен с выходом 21 блока управления, выход 22 которого соединен с управляющим входом ключа 7, клемма Пуск устройства соединена с третьим входом блока 6 управления, четвертый вход которого

0

5

0

5

0

5

0

5

0

5

соединен с обнуляющими входами счетчиков 8 и 12, обнуляющим входом интегратора 4 и клеммой Сброс устройства, первый вход переключателя 15 соединен с клеммой для подключения измеряемого напряжения Ux. второй вход - с общей шиной устройства, а второй управляющий вход - с клеммой 23 выбора измеряемого параметра, вывод образцового резистора R0 резистивного делителя 2 напряжения соединен с общей шиной устройства.

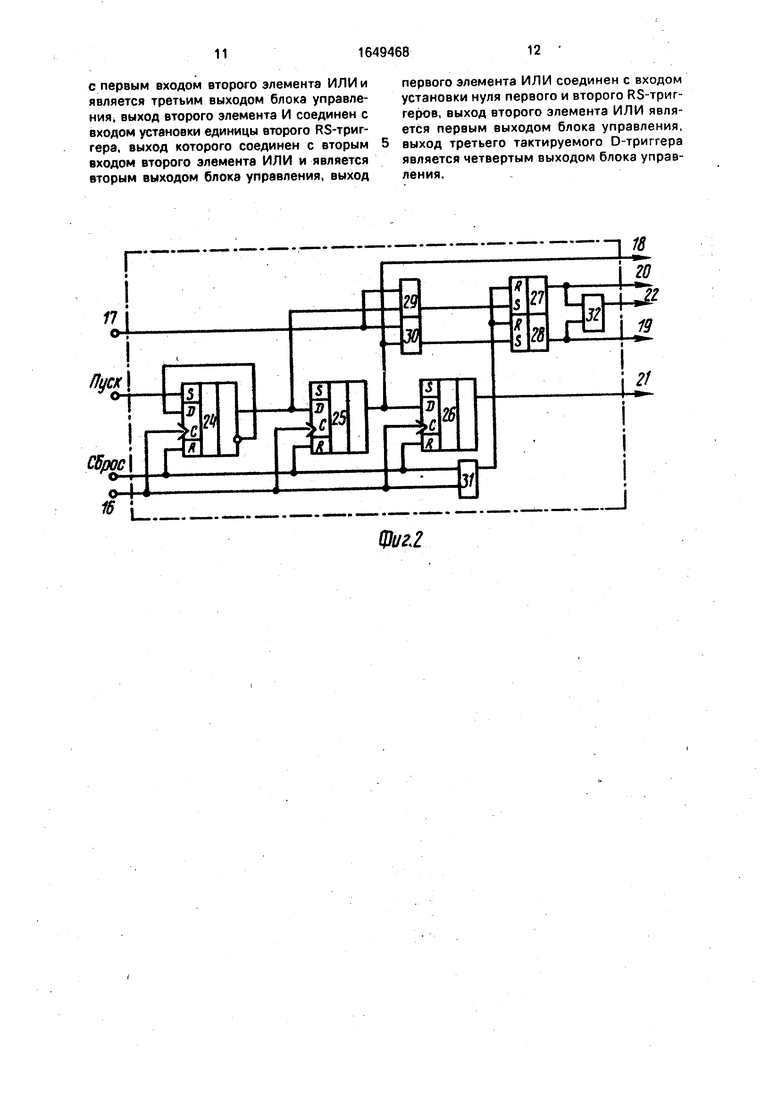

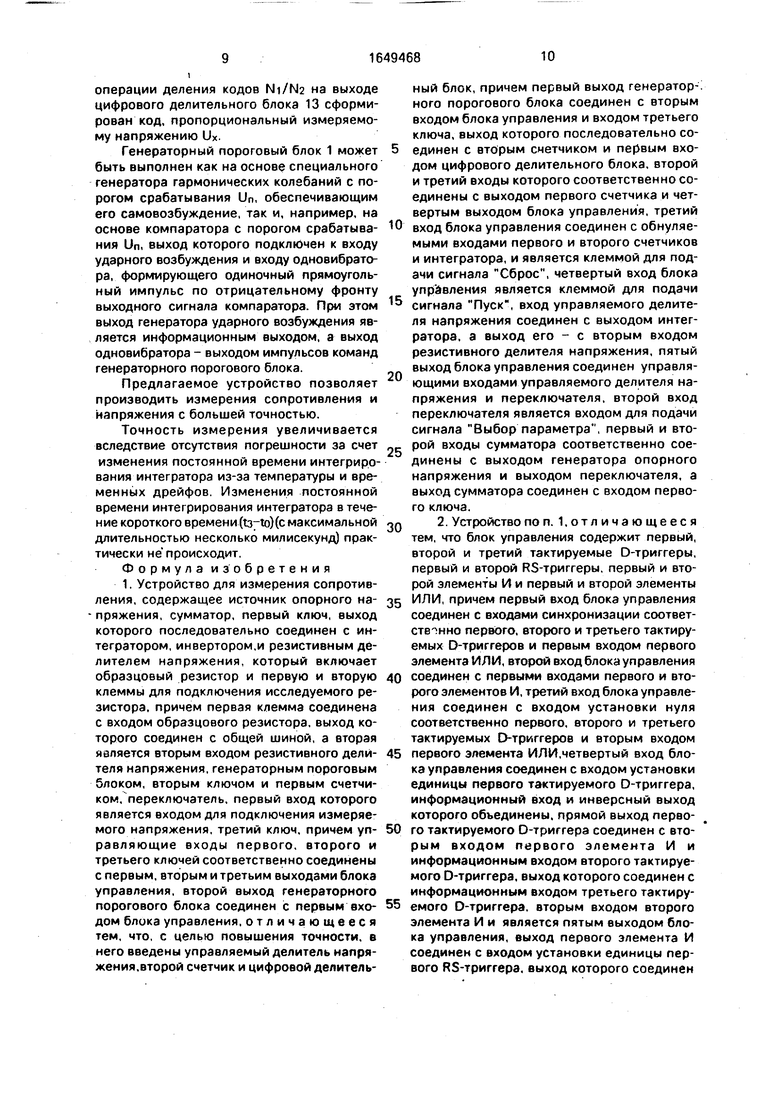

На фиг. 2 представлена схема одного из возможных вариантов блока 6 управления. Блок 6 управления содержит первый, второй и третий тактируемые D-триггеры 24, 25 и 26, первый и второй RS-триггеры 27 и 28, первый и второй элементы И 29 и 30, первый и второй элементы ИЛИ 31 и 32.

Устройство для измерения сопротивления работает следующим образом.

Измерение сопротивления осуществляется следующим образом.

По команде Сброс производится обнуление счетчиков 8, 12 и интегратора 4, Одновременно (фиг. 2) на прямых выходах триггеров 24-28 устанавливается логический О. Управляемый делитель 3 напряжения при этом включается на коэффициент деления 1/2. Генераторный пороговый блок 1 находится в режиме самовозбуждения.

При измерении сопротивления второй вход сумматора 14 через переключатель 15 постоянно соединен с общей шиной устройства, так как на второй управляющий вход переключателя 15 через клемму 23 выбора измеряемого параметра постоянно подан логический О.

По команде Пуск на прямом выходе триггера 24 устанавливается логическая 1, которая открывает элемент И 29 для импульсов с выхода 17 генераторного порогового блока 1 на S-вход триггера 27.

Первый импульс устанавливает на выходе триггера 27 логическую 1 (фиг. 3,6), замыкая ключ 11 для прохождения счетных импульсов с выхода 17 генераторного порогового блока 1 на информационный вход счетчика 12. Одновременно сигнал с выхода триггера 27 через элемент ИЛИ 32 замыкает ключ 7. При этом опорное напряжение U0 с выхода источника 9 опорного напряжения через сумматор 14 поступает на вход интегратора 4. Линейно-изменяющееся напряжение с выхода интегратора 4 через управляемый делитель 3 напряжения поступает на вход-резистивного делителя 2 напряжения и через инвертор 5 на среднюю точку резистивного делителя 2 напряжения (фиг. З.а).

В момент срабатывания генераторного порогового блока 1 происходит срыв колебаний на его информационном выходе 17 (т, ti, фиг. 3,а) и одновременно импульс команды с выхода 16 генераторного порогового блока 1, соответствующий моменту ti срыва колебаний, поступает в блок 6 управления, устанавливая на прямом выходе триггера 24 логический О, который запирает элемент И 29. Одновременно на выходе триггера 27 устанавливается логический О, который через выход 20 блока 6 управления поступает на управляющий вход ключа 11, прекращая поступление счетных импульсов в счетчик 12. Логический О с выхода триггера 27 через элемент ИЛИ 32-поступает на управляющий вход ключа 7, отключая источник 9 опорного напряжения от входа интегратора 4.

При этом имеет место соотношение 1Гк1 +Un+Ui 0,0)

где напряжение на средней точке резистив- ного делителя 2 напряжения

и, - R° I/ Uo ( t Ч к t ГСх + RQ} ( B РРГ раз меньше напряжения на выходе инвертора 5 U KI - UK1 - KUo( ti -to).

Un - порог срабатывания генераторного порогового блока 1. ,

В счетчике 12 фиксируется код Nt, пропорциональный интервалу времени ().

В тот же момент времени ti импульс с выхода 16 генераторного порогового блока 1 устанавливает на выходе триггера 25 логическую 1, которая открывает элемент И 30 для импульсов с выхода 17 генераторного порогового блока 1 и через выход 18 блока 6 управления устанавливает коэффи- циент деления управляемого делителя 3 напряжения равным 1/1. Напряжение на входе резистивного делителя 2 напряжения увеличивается на величину

$(„-,).

равенство (1) нарушается, генераторный пороговый блок 1 само возбуждается и на его информационном выходе 17 появляются импульсы.

Первый из серии импульсов (т. tz, фиг. 3,6) устанавливает на выходе триггера 28 логическую 1, замыкая ключ 10 для прохождения счетныхимпульсовс выхода 17 генераторного порогового блока 1 на информационный вход счетчика 8. Одновременно сигнал с выхода триггера 28 через элемент ИЛИ 32 замыкает ключ 7. При этом опорное напряжение Uo с выхода источника 9 опорного напряжения снова поступает на вход интегратора 4. На

выходе интегратора 4 вновь начинается линейное изменение напряжения UK.

В момент второго срабатывания генераторного порогового блока 1 (т, т.з, фиг. 3,6) происходит срыв колебаний,на его информационном выходе 17 и одновременно импульс команды с выхода 16, соответствующий моменту гз срыва колебаний, поступает в блок 6 управления, устанавливая на выходе триггера 25 логический О. Сигнал с выхода триггера 25 закрывает элемент И 30 и устанавливает коэффициент деления управляемого делителя 3 напряжения равным 1/2. Одновременно на выходе триггера 28 устанавливается логический О, который поступает на управляющий вход ключа 7, прекращая поступление счетных импульсов в счетчик 8. Сигнал с выхода триггера 28 через элемент ИЛ И 32 поступает на управляющий вход ключа 7, отключая источник 9 опорного напряжения от входа интегратора 4.

При этом имеет место соотношение

LTK2 +Un ,

где напряжение на средней точке резистивного делителя 2 напряжения

+р R°a KU0(t3-t2)

Кх т Ко

напряжение на выходе инвертора 5

U K2 UK2 U KI + - I Uo ( t3 -tZ )

В счетчике 8 фиксируется код N2, пропорциональный интервалу времени (). U KZ + Un+U2-(U KI+Un+Ui)0 U KI -KUo(t3-t2)-f Un+2Ui +

+ (t3- )-, -U Ki -Un-Ui 0

KU,

°((1-рГ)

Re

RX +RC

K(ti-to)

ft, -t74-MR +R0)(ti-t0)

( t2J{ R. + Rc

(R

72R

5

(ti -to) 2RX .N1 2RX (t3 -12 ) Ro N2 Ro

В момент времени гз (фиг. 3,6) на выходе триггера 26 устанавливается логическая единица, которая поступает на вход разрешения деления цифрового делительного блока 13. После выполнения операции деления кодов Ni/N2 на выходе цифрового делительного блока 13 сформирован код, пропорциональный сопротивлению измеряемого резистора Rx.

Данное устройство может измерять напряжение.

При измерении напряжения на второй управляющий вход переключателя 15 через клемму 23 выбора измеряемого параметра постоянно подана логическая Г. При этом управление переключателем 15 осуществляется с выхода 18 блока 6 управления. Вместо резистора Rx подключается эталонный резистор RST.

На первом этапе устройство работает аналогично.

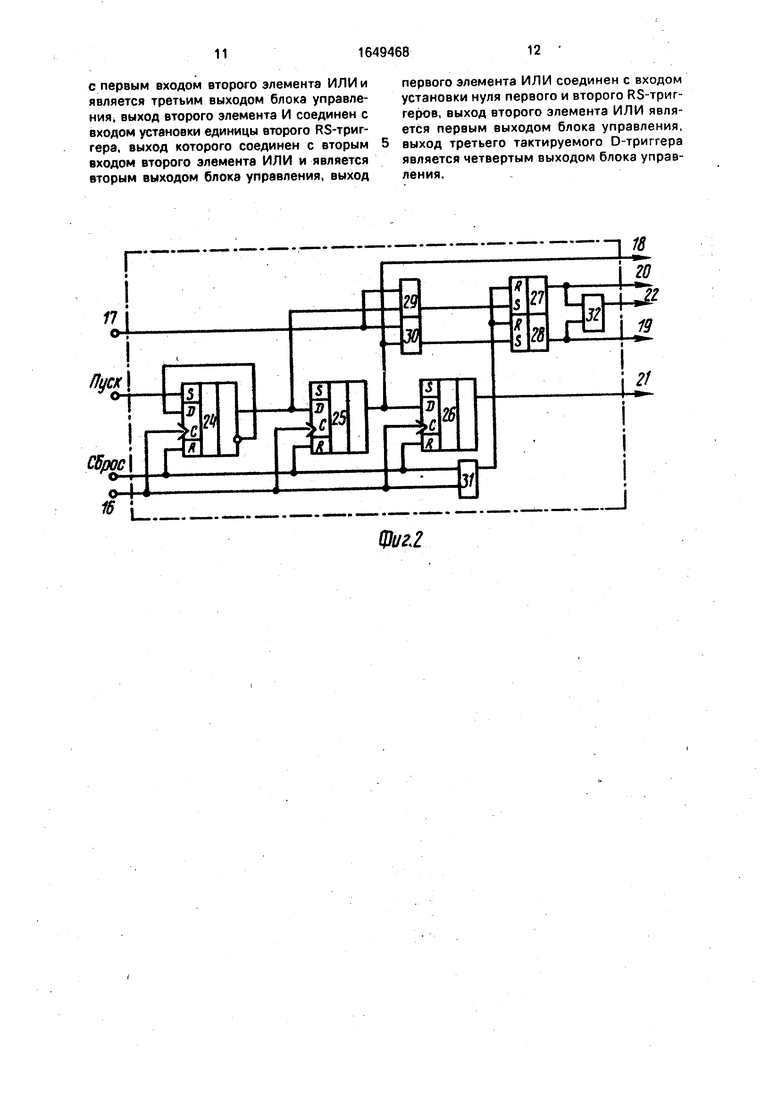

После подачи команд Сброс и Пуск управляемый делитель 3 напряжения включается на коэффициент деления 1/2, Первый из серии импульсов с выхода 17 генераторного порогового блока 1 устанавливает на выходе триггера 27 логическую Г, замыкая ключ 11 для прохождения счетных импульсов с выхода 17 блока 1 на информационный вход счетчика 12. Одновременно замыкается ключ 7 и опорное напряжение Ко с выхода источника 9 опорного напряжения через сумматор 14 поступает на вход интегратора 4. Второй вход сумматора 14 через переключатель 15 соединен с общей шиной устройства. Линейно-изменяющееся напряжение UK KUot с выхода интегратора 4 через управляемый делитель 3 напряжения поступает на вход резистиеного делителя 2 напряжения и через инвертор 5 на среднюю точку резистивного делителя 2 напряжения (фиг. 4).

В момент срабатывания генераторного порогового блока 1 происходит срыв колебаний на его информационном выходе 17.

При этом имеет место соотношение

U Ki+Un+Ui 0(2) .

где напряжение на средней точке делителя 2 напряжения

()

п2( W0

раз меньше напряжения на выходе инвертора 5 -KU0 (ti-to).

В счетчике 12 фиксируется код NI, пропорциональный интервалу времени (ti-to).

В момент времени ti на выходе триггера 25 устанавливается логическая Г, которая открывает элемент И 30 для импульсов с выхода 17 генераторного порогового блока 1 и через выход 18 блока 6 управления устанавливает коэффициент деления управляемого делителя напряжения 3 равным 1/1, а через переключатель 15 подключает иэме0

5

0

5

0

ряемое напряжение Ux к второму входу сумматора 14. Напряжение Ux должно иметь ту же полярность, что и напряжение U0. Напряжение на выходе реэистивного делителя 2 напряжения увеличивается на величину К

Y (ti-to) равенство (2) нарушается, генераторный пороговый блок 1 самовозбуждается и на его информационном выходе 17 появляются импульсы.

Первый из серии импульсов устанавливает на выходе триггера 28 логическую Г, замыкая ключ 10 для прохождения импульсов с выхода 17 генераторного порогового блока 1 на информационный вход счетчика 8. Одновременно сигнал с выхода триггера 28 через элемент ИЛИ 32 замыкает ключ 7. При этом напряжение (Uo+ Ux) с выхода сумматора 14 поступает на вход интегратора 4. На выводе интегратора 4 вновь начнется линейное изменение напряжения UK.

В момент второго срабатывания генераторного порогового блока 1 (т. ta, фиг. 4) происходит срыв крлебаний на его информационном выходе 17.

При этом имеет место соотношение

и кз + Un + U2 0 ,

где напряжение на средней точке резистивного делителя 2 напряжения

1)2 2Lh +

Rc

K(U0+Ux)(t3-t2);

Rat b Ro

напряжение на выходе интегратора 5 U K2 -UK2- U Ki + - К( Ц + Ux ) х (t3-T2)J.

В счетчике 8 фиксируется код N2, пропорциональный интервалу времени (ts-t2). 1Гк2 + Un + U2 - ( U KI + Un + Ui ) О

U M -K(U +Ux)(t3-t2) + Un + 2U1 +

+ (U +U Xt3-t2)- -U Ki-Un-Ui 0

K(U+UxXt3-t2)(l-R) v UpRo f K 2( RST + Ro ) ( t1 t0

11 -to „RST fUx , ,

ta-U Ro Uo

5

Если принять R3T -Ј. то

l -to t3 t2

П -to Ux . . . Ni Ux , .

pi Т , ; - 71 i i .

U0N2 U0

В момент времени is на выходе триггера 26 устанавливается логическая 1, которая через выход 21 блока 6 управления поступает на вход разрешения деления цифрового делительного блока 13. После выполнения

операции деления кодов Ni/N2 на выходе цифрового делительного блока 13 сформирован код, пропорциональный измеряемому напряжению Ux.

Генераторный пороговый блок 1 может быть выполнен как на основе специального генератора гармонических колебаний с порогом срабатывания Un, обеспечивающим его самовозбуждение, так и, например, на основе компаратора с порогом срабатыва- ния Un, выход которого подключен к входу ударного возбуждения и входу одновибрато- ра, формирующего одиночный прямоугольный импульс по отрицательному фронту выходного сигнала компаратора. При этом выход генератора ударного возбуждения является информационным выходом, а выход одновибратора - выходом импульсов команд генераторного порогового блока.

Предлагаемое устройство позволяет производить измерения сопротивления и напряжения с большей точностью.

Точность измерения увеличивается

вследствие отсутствия погрешности за счет

изменения постоянной времени интегрирования интегратора из-за температуры и временных дрейфов. Изменения постоянной времени интегрирования интегратора в течение короткого времени (t37to)(c максимальной длительностью несколько милисекунд) практически не происходит.

Формула изобретения 1. Устройство для измерения сопротивления, содержащее источник опорного на- пряжения, сумматор, первый ключ, выход которого последовательно соединен с интегратором, инвертором,и резистивным делителем напряжения, который включает образцовый резистор и первую и вторую клеммы для подключения исследуемого резистора, причем первая клемма соединена с входом образцового резистора, выход которого соединен с общей шиной, а вторая является вторым входом резистивного дели- теля напряжения, генераторным пороговым блоком, вторым ключом и первым счетчиком, переключатель, первый вход которого является входом для подключения измеряемого напряжения, третий ключ, причем уп- равляющие входы первого, второго и третьего ключей соответственно соединены с первым, вторым и третьим выходами блока управления, второй выход генераторного порогового блока соединен с первым вхо- дом блика управления, отличающееся тем, что, с целью повышения точности, в него введены управляемый делитель напряжения,второй счетчик и цифровой делитель0

0

5

5 0 5 0 5

ный блок, причем первый выход генератор-, ного порогового блока соединен с вторым входом блока управления и входом третьего ключа, выход которого последовательно соединен с вторым счетчиком и первым входом цифрового делительного блока, второй и третий входы которого соответственно соединены с выходом первого счетчика и четвертым выходом блока управления, третий вход блока управления соединен с обнуляемыми входами первого и второго счетчиков и интегратора, и является клеммой для подачи сигнала Сброс, четвертый вход блока управления является клеммой для подачи сигнала Пуск, вход управляемого делителя напряжения соединен с выходом интегратора, а выход его - с вторым входом резистивного делителя напряжения, пятый выход блока управления соединен управляющими входами управляемого делителя напряжения и переключателя, второй вход переключателя является входом для подачи сигнала Выбор параметра, первый и второй входы сумматора соответственно соединены с выходом генератора опорного напряжения и выходом переключателя, а выход сумматора соединен с входом первого ключа.

2. Устройство по п. 1,отличающееся тем, что блок управления содержит первый, второй и третий тактируемые D-триггеры, первый и второй RS-триггеры, первый и второй элементы И и первый и второй элементы ИЛИ, причем первый вход блока управления соединен с входами синхронизации соответ- ств-жно первого, второго и третьего тактируемых 0-триггеров и первым входом первого элемента ИЛИ, второй вход блока управления соединен с первыми входами первого и второго элементов И, третий вход блока управления соединен с входом установки нуля соответственно первого, второго и третьего тактируемых D-триггерое и вторым входом первого элемента ИЛИ,четвертый вход блока управления соединен с входом установки единицы первого тактируемого D-триггера, информационный вход и инверсный выход которого объединены, прямой выход первого тактируемого D-триггера соединен с вто- рым входом первого элемента И и информационным входом второго тактируемого D-триггера. выход которого соединен с информационным входом третьего тактируемого D-триггера, вторым входом второго элемента И и является пятым выходом блока управления, выход первого элемента И соединен с входом установки единицы первого RS-триггера. выход которого соединен

с первым входом второго элемента ИЛИ и является третьим выходом блока управления, выход второго элемента И соединен с входом установки единицы второго RS-триг- гера, выход которого соединен с вторым входом второго элемента ИЛИ и является вторым выходом блока управления, выход

первого элемента ИЛИ соединен с входом установки нуля первого и второго RS-триг- геров, выход второго элемента ИЛИ является первым выходом блока управления, выход третьего тактируемого D-триггера является четвертым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения сопротивления | 1979 |

|

SU847225A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Устройство для измерения напряжения | 1981 |

|

SU945985A1 |

| Устройство для измерения сопротивления | 1990 |

|

SU1812522A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Частотный аналого-цифровой преобразователь | 1989 |

|

SU1702528A1 |

| Устройство для определения степени затухания измерительных магнитоэлектрических преобразователей | 1988 |

|

SU1628028A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

Изобретение относится к электроизмерительной технике и может быть использовано для измерения сопротивления, а также напряжения, Целью изобретения является повышение точности. Отличием изобретения является подача сигнала на исследуемый разистор через управляемый делитель напряжения и использование для обработки сигнала второго счетчика и цифрового делительного блока. Работа устройства основана на преобразовании измеряемого параметра в интервал времени путем подачи на измерительную цепь линейно-измеряющегося напряжения. Устройство содержит гене раторный пороговый блок 1, делитель 2 напряжения, управляемый делитель 3 напряжения, интегратор 4, инвертор 5, блок 6 управления, ключи 7, 10, 11, счетчики 8, 12, источник 9 опорного напряжения, цифровое делительное устройство 13, сумматор 14, пере- .ключатель 15. формирователь 16 импульсов команд. Точность измерения увеличивается вследствие устранения погрешности за счет изменения постоянной времени интегрирования интегратора из-за температуры и временных дрейфов. 1 з.п. ф-лы, 4 ил. сл с

Щиг2

| Устройство для измерения сопротивления | 1979 |

|

SU847225A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-05-15—Публикация

1988-10-24—Подача