величиной и соответствующего повышения f0, если при этом возникающие динамические погрешности не превышают величины кванта АЦП равного

А -гг 1 .При и f qf0 и coNoхранится Ux

При и No . N

j- результат

Х

qU

m

Ti

Т о

U X

буде получен

за время , т.е. время на получение X сократилось в q раз, но оно остается большим, это является недостатком данного АЦП.

Этот недостаток устранен R АЦП совмещенного интегрирования.

Прототип АЦП совмещенного интегрирования содержит интегратор, вход которого соединен с выходами первого и второго ключей, информационные входы которых являются соответственно шинами опорного и входного напряжений, выход интегратора подключен к первым входам порогового элемента и компаратора, второй вход последнего из которых является общей шиной, счетчик, выходы которого являются выходной шиной, вход установки нуля - шиной пуска, блок управления и блок формирования времени интегрирования опорного напряжения, выход которого соединен с управляющим входом первого ключа и первым входом элемента И, второй вход которого соединен с первым выходом блока управления, а выход - со счетным входом счетчика, первый вход блока управления является шиной пуска, второй выход - соединен с управляющим входом второго ключа, трзгий выход - с первым входом блока фор- мирогания времени интегрирования опорного напряжения, второй вход которого объединен со вторым входом блока управления и подключен к выходу компаратора, информационный вход и выход третьего ключа подключены соответственно к входу и выходу интегратора, а управляющий вход - является шиной готовности результата преобразования и,подключен к четвертому выходу блока управления, пятый выход которого соединен с первым входом триггера, а первый вход-объединен с первым входом элемента ИЛИ и с третьим входом блока формирования времени интегрирования опорного напряжения, четвертый вход которого объединен с вторым входом элемента ИЛИ и подключен к выходу порогового элемента, второй вход которого соединен с выходами интегрирующего элемента и переключателя, первый и второй информационные входы которого подключены соот

Q

5

0

5

0

5

О

5

0

5

ветстзенно к выходам делителя напряжения и источника тока, входы которых являются шиной опорного напряжения, а упрэвпяю- щий вход переключателя - подключен к единичному выходу триггера, второй вход которого соединен с выходом элемента ИЛИ, вход интегрирующего элемента является общей шиной.

Блок формирования времени интегрирования опорного напряжения выполнен на триггере, формирователе импульсов, элементе И, первом и втором элементах ИЛИ, причем выход триггера является выходом блока, а единичный и нулевой входы соединены соответственно с выходами элемента И и первого элемента ИЛИ, первый вход которого является третьим входом блока, а второй вход подключен к выходу формирователя импульсов, вход которого является вторым входом блока и объединен с первым входом элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, первый и второй входы которого являются соответственно перпым и четсертым входами блока.

Блок управления выполнен на счетчике, генераторе импульсов, триггере, формирователе импульсов, инверторе, элементах И и ИЛИ, причем первым входом блока является единичный вход триггера и вход установки нуля счетчика, счетный вход которого подключен к выходу генератора импульсов, являющегося первым выходом блока, выход переполнения счетчика подключен к нулевому входу триггера и является третьим выходом блока, а выходы старших разрядов счетчика подключены к соответствующим входам элемента И, выход которого подключен к входу формирователя импульсов, выход которого является пятым выходом блока, четвертым выходом которого является выход инвертора, ьход которого объединен с управляющим входом генератора импульсов и подключен к выходу элемента ИЛИ, первый и второй входы которого являются соответственно вторыми входами и выходом блока, а прямой выход триггера подключен к второму входу элемента ИЛИ.

В АЦП - прототипе, благодаря формированию напряжения специальной формы Uc(t) и сравнению его с напряжением Un(t) на выходе интегратора в процессе интегрирования входного сигнала, определяется момент начала совмещенного интегрирования Т21 до окончания Ti - времени интегрирования входного сигнала и тем самым существенно уменьшаются по сравнению с аналогами за ;раты времени Т22. которые необходимы мля получения результата преобразования после окончания Ti.

Однако, прототип обладает недостатком, состоящим в том, что время Jz2 принимает различные значения в зависимости от уровня входного сигнала и Tz2 может быть равно нулю теоретически, т.е. без учета по- грешностей элементов, определяющих начало Т21, только для двух значений и .

Если же учитывать эти погрешности, а также дополнительные погрешности в Un(t), возникающее от помех, наложенных на Ux, и которые в момент определения началаТ21 до окончания Ti еще не скомпенсированы, то они приведут к ошибкам определения начала Tai и к соответствующему увеличе- нию времени Т22, которое может иметь значительную величину.и все это снижает быстродействие АЦП.

Кроме того этот недостаток приводит к тому, что из-за наличия времени Таа после окончания очередного интегрирования входного сигнала в течение Ti дальнейшее интегрирование входного сигнала до начала следующего замера прерывается на время Т22 и его значение за это время теряется. ГТоэтому стоит задача по устранению этих дополнительных затрат времени и получению результатов преобразования, соответствующих непрерывному интегрированию входного сигнала.

Данное предложение направлено на решение этой задачи и на устранение недостатка прототипа, оно имеет своей целью повышение быстродействия АЦП совмещенного интегрирования.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь совмещенного интегрирования, выполненный по схеме заявки № 4768037 от 1.11.89 г. (положительное решение от 30.05.90), до- полнительно введены второй интегрирующий элемент, четвертый ключ, резистивный элемент и второй переключатель, управляющий вход которого объединен с одноименным входом второго ключа, первый и второй информационные входы подсоединены соответственно к шине входного напряжения и к входу интегратора а выход через рези- стивный элемент- к входу второго интегрирующего элемента и к выходу четвертого ключа, соответственно выход и вход которых соединены с общей шиной, управляющий вход последнего подсоединен к первому входу блока управления, четвертый выход которого соединен с третьим входом элемента ИЛИ, а пятый выход - с входом установки исходного состояния счетчика

При этом блок управления выполнен на счетчике, генераторе импульсов, триггере двух формирователях импульсов элементах

И и ИЛИ, причем первым входом блока является первый вход первого элемента ИЛИ и входы установки в исходное состояние счетчика и генератора импульсов, счетный вход первого из котор ых соединен с выходом второго и является первым выходом блока, выход переполнения счетчика подключен к нулевому входу триггера и является третьим выходом блока, а выходы старших разрядов счетчика подсоединены к соответствующим входам элемента И, выход которого соединен с входом первого формирователя импульсов, выход которого является пятым выходом блока, четвертым выходом которого является выход первого элемента ИЛИ, который объединен с единичным входом триггер , выход которого является вторым выходом блока и соединен с первым входом второго элемента ИЛИ, второй вход которого является вторым входом блока, а выход через второй формирователь импульсов подсоединен к второму входу первого элемента ИЛИ.

При анализе аналогов и поиске прототипа не были обнаружены технические решения, которые содержат при§на к Ссходные с отличительнымй ЧГрШн кам и Заявляемого технического решений.

В предлагаемом АЦП задача по устранению недостатка прототипа решается путем выполнения интегрирования входного сигнала после окончания очередного такта Ti его измерения в течение Т22 с помощью дополнительного интегрирующего элемента и дальнейшей передачи полученной величины этого интеграла интегратору, осуществляющему интегрирование входного сигнала в следующем такте Ti его измерения. Благодаря этому необходимые дополнительные затраты времени Таг после TI для получения результата преобразования в каждом такте измерения входного сигнала не оказывают влияние на процесс его интегрирования, которое выполняется для каждого такта измерения в течение Ti, и результаты преобразования будут соответствовать интегралам входного сигнала за эти такты без каких-либо пропусков между ними, что обеспечивает повышение быстродействия АЦП совмещенного интегрирования.

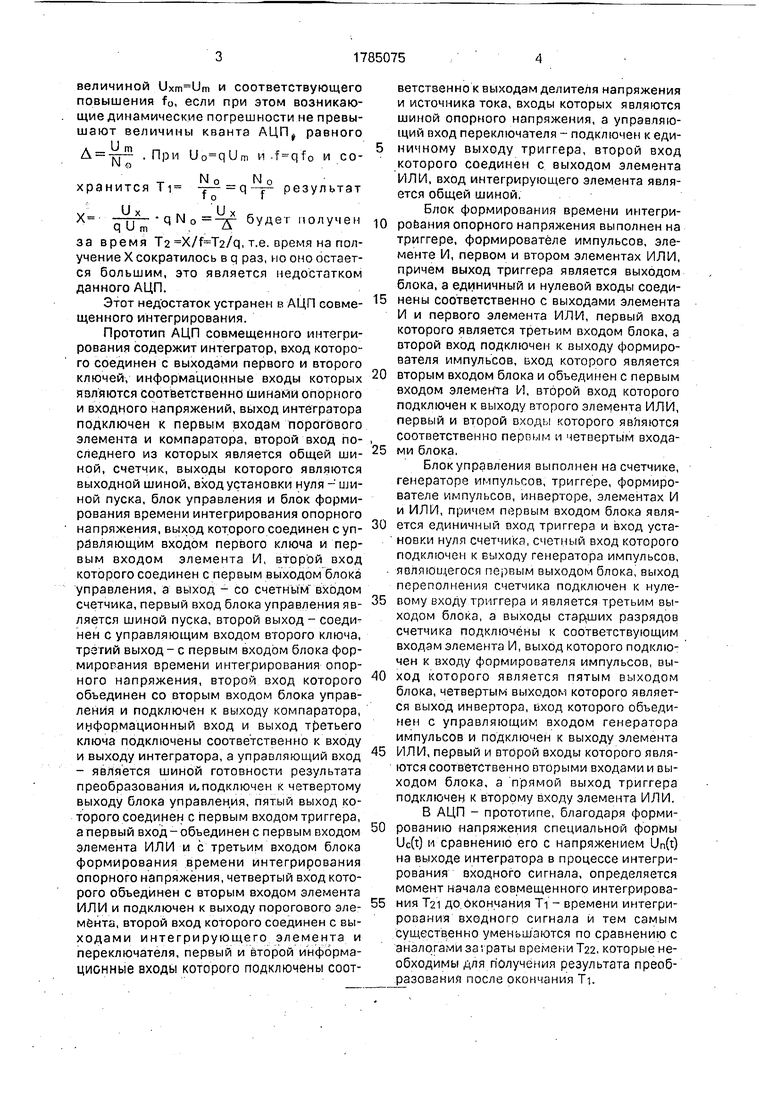

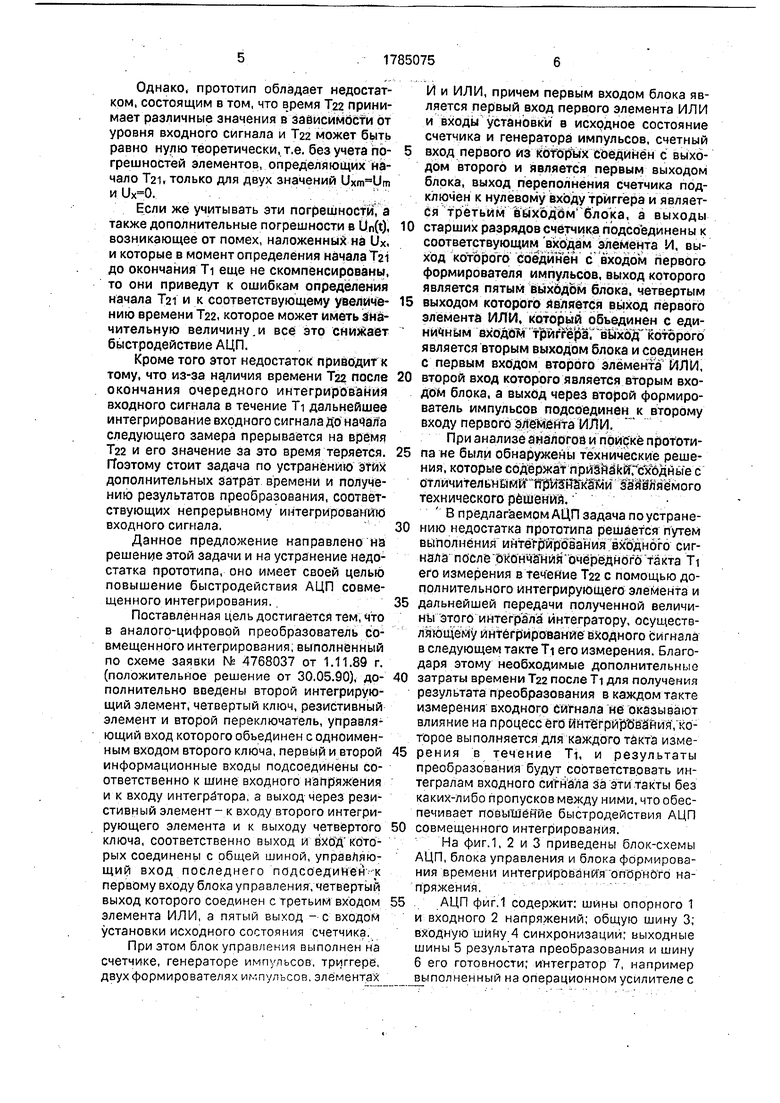

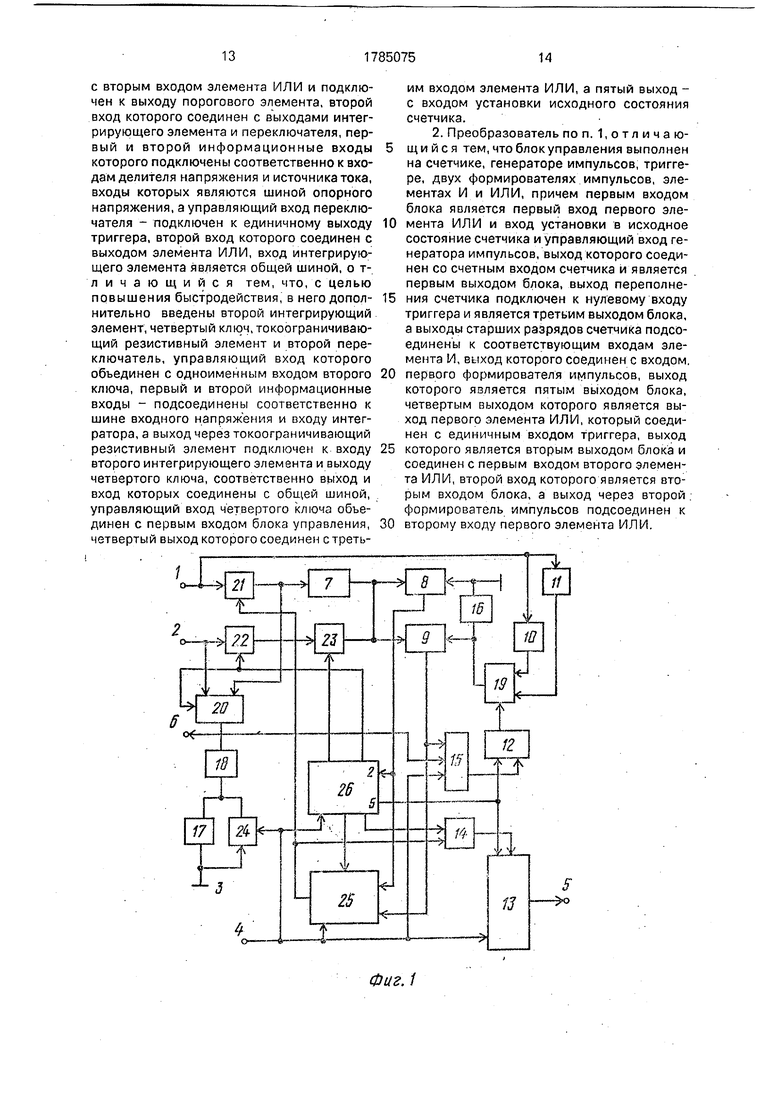

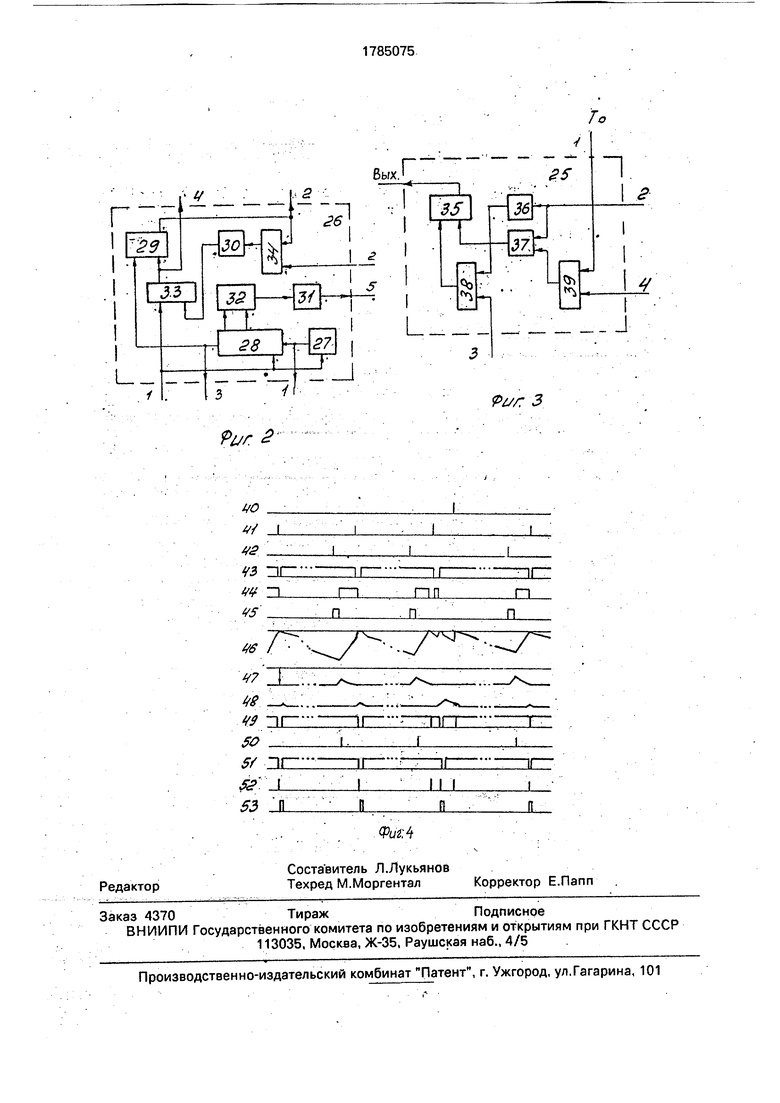

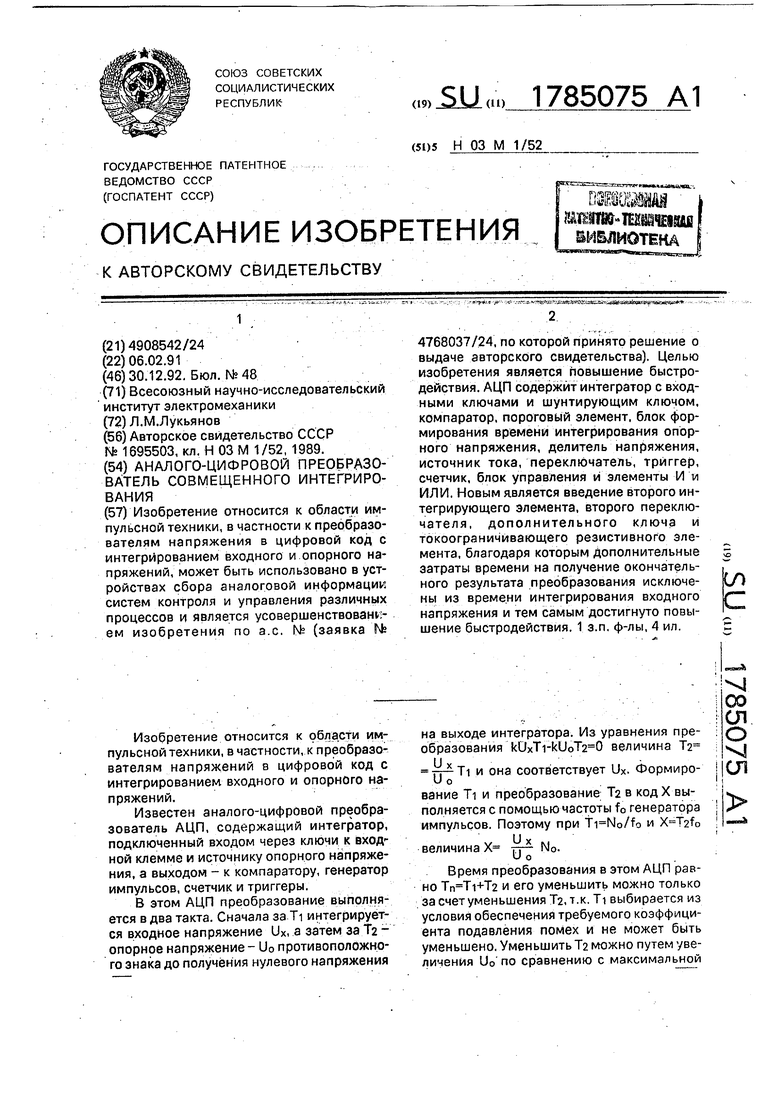

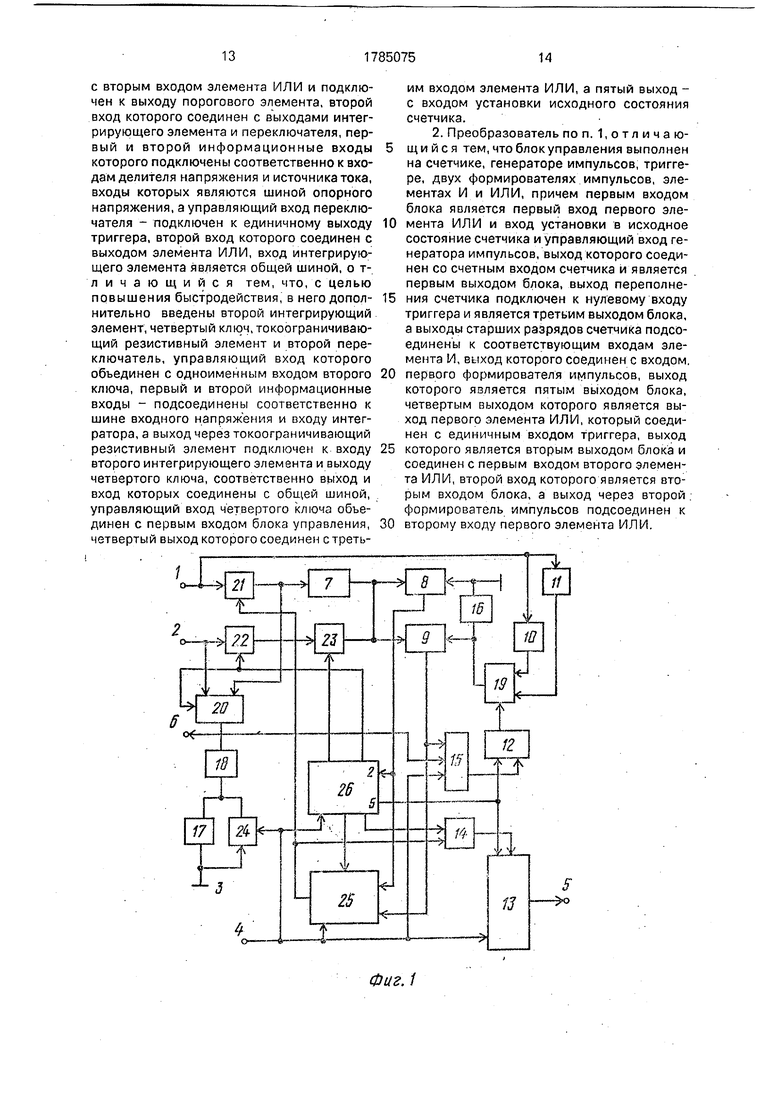

На фиг.1, 2 и 3 приведены блок-схемы АЦП, блока управления и блока формирования времени интегрирования опорного напряжения

АЦП фиг 1 содержит: шины опорного 1 и входного 2 напряжений, общую шину 3, входную шину 4 синхронизации1 выходные шины 5 результата преобразования и шину 6 его готовности; интегратор 7, например выполненный на операционном усилителе с

конденсатором в цепи обратной связи; компаратор 8 и пороговый элемент 9; источник тока 10 и делитель напряжения 11; триггер 12 и счетчик 13; элементы И 14 и ИЛИ 15; интегрирующие элементы 16 и.17, например выполненный на конденсаторах, резистив- ный элемент 18; переключатели 19 и 20, у которых при отсутствии сигнала на управляющем входе замкнуты первый вход и вы- хбд, а при его наличии замкнуты второй вход и выход; ключи 21, 22, 23 и 24, первые два из которых имеют резисторы.каждый из них при йа личии с игнала на управляющем входе замкнут, а при его отсутствии разомкнут; блок 25 формирования времени интегрирования опорного напряжения и блок управления 26.

Блок 26, фиг.2, содержит: генератор импульсов 27, счетчик 28, триггер 29, формирователи импульсов 30 и 31, элементы И 32 и ИЛИ 33 и 34.

. Блок 25, фиг.З, содержит: триггер 35, формирователь импульсов 36, элементы И 37 и ИЛИ 38 и 39.

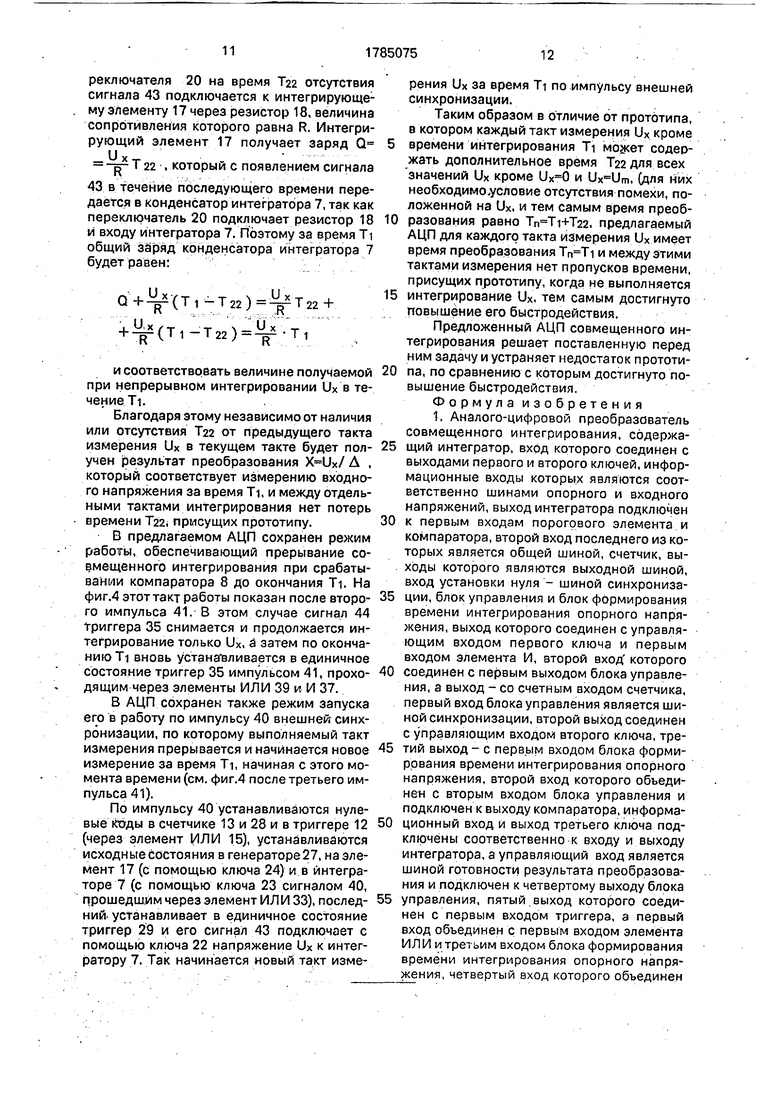

На временной диаграмме фиг.4 обозначены: 40 - импульс синхронизации; 41 и 42

-импульсы переполнения счетчика 28 и формирователя 31; 43, 44 и 45 - сигналы на выходах триггеров 29, 35 и 12; 46, 47 и 48 - сигналы на выходах интегратора 7, интегрирующих элементов 16 и 17; 49, 50 и 51 - выходные сигналы компаратора 8, порогового элемента 9 и элемента ИЛИ 34; 52 и 53

-импульсы формирователей 36 и 30 (последний - готовность результата преобразования).

В АЦП шина 1 соединена с входами ключа 21, источника тока 10 и делителя 11, шина 2-е входом ключа 22.и первым входом переключателя 20, шина 3-е входом и выходом элементов 16 и 17, ключа 24 и с вторым входом компаратора 8, шина 4 - с управляющим входом ключа 24, с первыми входами блока 26 и элемента ИЛИ 15, с третьим входом блока 25 и с входом установки нулевого кода счетчика 13, шина 5 - с выходами последнего, счетный вход которого подсоединен к выходу элемента И 14, шина 6 - с управляющим входом ключа 23, с третьим входом элемента ИЛИ 15 и с четвертым выходом блока 26, второй выход которого подсоединен к управляющим входам ключа 22 и переключателя 20, первый выход

-к второму входу элемента И 14, третий выход - к первому входу блока 25, пятый выход - к единичному входу триггера и к входу установки исходного состояния счетчика 13, второй вход- к выходу компаратора 8 и к второму входу блока 25, выход которого соединен с первым входом элемента И

с управляющим входом ключа 21, четвертый вход - с выходом элемента 9 и с вторым входом элемента ИЛИ 15, выход которого подсоединен к нулевому входу триггера, выход которого соединен с управляющим входом переключателя 19, первый и второй входы которого подсоединены к выходам делителя 11 и источника тока 10, а выход - к выходу элемента 16 и к второму входу

элемента 9, первый вход которого соединен с первым входом компаратора 8 и с выходами ключа 23 и интегратора 7, вход которого подсоединен к входу ключа 23, к выходам ключей 21 и 23 и к второму входу переключателя 20, выход которого через элемент 18 соединен с выходами элемента 17 и выходом ключа 24.

В блоке 26 первым входом является первый вход элемента ИЛИ 33 и входы установки в исходное состояние счетчика 28 и генератора 27, счетный вход первого из которых соединен с выходом второго и является первым выходом блока, выход переполнения счетчика 28 подключен к нулевому входу триггера 29 и является третьим выходом блока, а выходы старших разрядов счетчика 28 подсоединены к входам элемента И 32, выход которого соединен с входом формирователя 31, выход

которого является пятым выходом блока, четвертым входом которого является выход элемента ИЛИ 33, который объединен с единичным входом триггера 29, выход которого является вторым выходом блока и соединен с первым входом элемента ИЛИ 34,

второй вход которого является вторым вхо, дом блока, а выход через формирователь 30

подсоединен к второму входу элемента

ИЛИ 33.

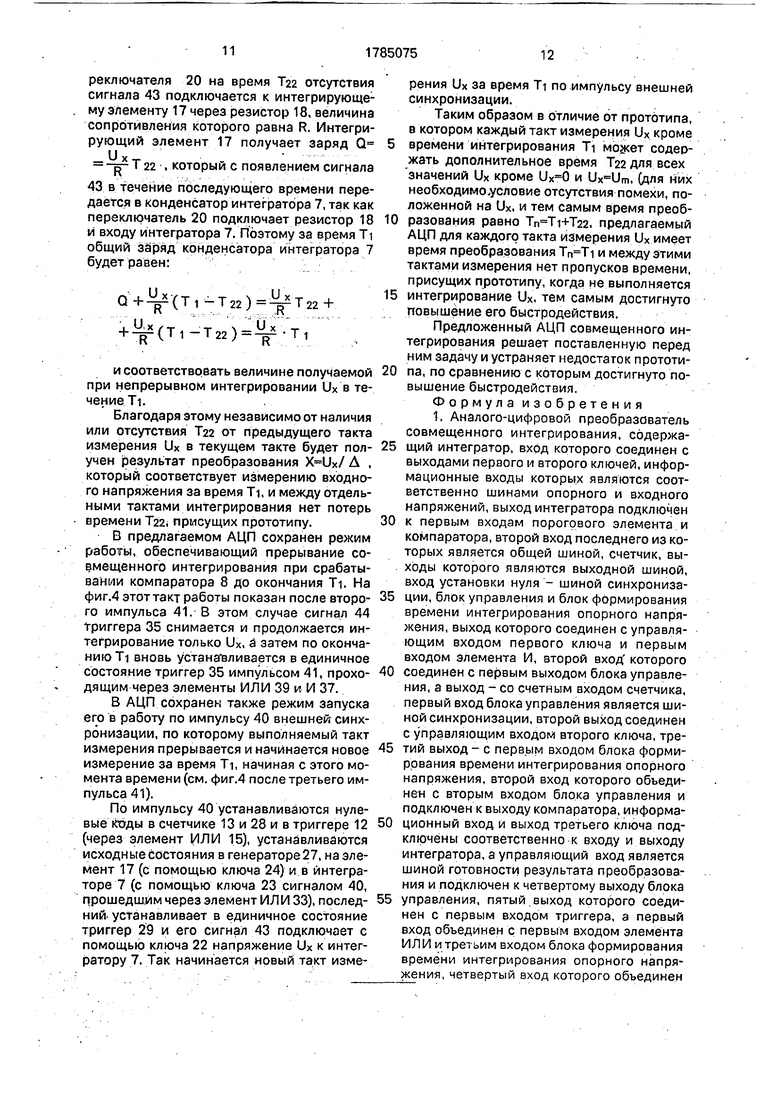

Предлагаемый АЦП работает следующим образом. Как и в прототипе интегрирование входного напряжения Ux выполняется в течение времени Ti, которое формируется с помощью счетчика 28 по импульсам частоты f генератора 27.

Емкость счетчика 28 равна qN0, где

q rr2- и° опорное напряжение, Um - и m

максимальное значение Ux- и импульсы 41 его переполнения возникают через Ti qN0/f. По этим импульсам выполняются такты измерения Ux, в течение которых Ux проходит через ключ 22, замкнутый сигналом 43 и преобразующий напряжение Ux в

U х

ток 1Х -к- Ток Тх интегрируется интегратором, который устанавливается в нулевое состояние с помощью ключа 23, шунтирующего его конденсатор, по сигналу 53 готовности результата преобразования прошедшего такта измерения Ux.

В текущем такте Ti на выходе интегратора 7 появляется напряжение 46, равное Un(t)TxT, а на выходе компаратора 8 появится сигнал 49. Напряжение 47 на элементе 16 и на втором входе порогового элемента 9 будет равно Uc(t)-UA, где 1)д - напряжение делителя 11, выход которого подключен к элементу 16 с помощью переключателя 19, в течение времени Тот до появления импульса 42 формирователя 31, срабатывающего при смене определенного кода в старших разрядах счетчика 28,

Величина этого времени выбирается равной:

loi l-lTi(1--i)Ti, а величина напряжения

(l-)0-±).

Импульс 42 устанавливает в единичное состояние триггер 12, его сигнал 45 с помощью переключателя 19 подключает к элементу 16 источник тока 10, напряжение 47 на котором начинает изменяться по линейному закону со скоростью V:UCn(t)-Ufl(1-Vt). Величина V выбирается из условия, чтобы к окончанию Ti UCn(Ti)0, иона обеспечивается соответствующими величинами тока источника 10 и емкости элемента 16.

Этому условию соответствует величина V:

.. Um /А 1 Uo/ч 1

V 7fr-q(1--)-W(1-q)

При через время Toi на выходе интегратора 7, благодаря выбору соответствующего коэффициента интегрирования,

1 ч

образуется напряжение Un(Toi)-Um(1- - ),

т.е. напряжение, равное -1)д, и произойдет срабатывание порогового элемента 9. Для других значения Ux это произойдет позже при равенстве Un(t)Ucn(t).

С выхода элемента 9 сигнал 50 установит через элемент ИЛИ 15 в нулевое состояние триггер 12 и через элементы ИЛИ 39 и И 37 в единичное состояние триггера 35. Снятие сигнала 45 в триггере 12 отключает источник тока 10 от элемента 16, на котором восстанавливается напряжение -UA. С появлением сигнала 44 на выходе триггера 35 подключается к интегратору 7 с помощью

1 ч

10

20

45

ключа 21 опорное напряжение U0, преобразованное им в ток . Так начинается совмещенное интегрирование токов (I х-1 о) Ux-Uo R

Одновременное с этим см/нал 44 разрешает работу элемента И 14, через который импульсы f генератора 27 поступают на счетный вход счетчика 13, где формируется новый код X результата преобразования после установки его в исходное состояние импульсом 42.

Совмещенное интегрирование продолжается в течение времени Т21 до оконЧё ия 15 Ti, когда по снятию сигнала 43 напряжение Ux отключается от интегратора 7, оставшееся напряжение на котором разынтегрирует- ся до нуля напряжением Do за время Т22. В течение этого времени, как и в Tai, в счетчик 13 будут поступать импульсы f и в нем будет сформирован окончательный результат преобразования f, где Т2(Т2+Т22)°- время, равное длительности сигнала 44. Это время Т2 заканчивается по снятию сигнала 49 в 25 компараторе 8, по которому формируется формирователем 36 импульс 52, который устанавливает через элемент ИЛИ 38 нулевое состояние в триггере 35.

Снятие сигнала 49 или сигнала 43, если на выходе компаратора 8 к окончанию TI имеет место нулевой уровень сигнала 49, в элементе ИЛИ 34 запускает формирователь 30. Длительность его импульса 53 превышает длительность импульса 52 и этот импульс 35 информирует по шине 6 с готовности нового результата преобразования X в счетчике 13 и на шине 5, Он же используется для установки в нулевое состояние интегратора 7 (с помощью ключа 23) и триггера 12 (через элемент ИЛИ 15).

Если в выполняемом такте измерения интегрирование Ux началось сразу с начала Ti, т.е. в предыдущем такте , то заряд конденсатора в интеграторе 7 от Ux за время Ti скомпенсирован зарядом от U0 за время

,iL°

R R

30

40

Т2, откуда Т 2 0, ИСПОЛЬN

зуя значения Ti q -г- и , получим

f

50

Х

где А

При наличии в предыдущем такте измерения времени Т22, которое уже относится к началу выполняемого нового такта измерения, входное напряжение Ux с помощью переключателя 20 на время Т22 отсутствия сигнала 43 подключается к интегрирующему элементу 17 через резистор 18, величина сопротивления которого равна R. Интегрирующий элемент 17 получает заряд Q

Ux-r -к- Т 22 , который с появлением сигнала

43 в течение последующего времени передается в конденсатор интегратора 7, так как переключатель 20 подключает резистор 18 и входу интегратора 7. Поэтому за время Ti общий заряд конденсатора интегратора 7 будет равен:

U

-T22) +

R

+ ТГ Т1-т22)

и соответствовать величине получаемой при непрерывном интегрировании Ux в течение Ti.

Благодаря этому независимо от наличия или отсутствия Т22 от предыдущего такта измерения Ux в текущем такте будет получен результат преобразования A , который соответствует измерению входного напряжения за время Ti, и между отдельными тактами интегрирования нет потерь времени Т22, присущих прототипу.

В предлагаемом АЦП сохранен режим работы, обеспечивающий прерывание совмещенного интегрирования при срабатывании компаратора 8 до окончания TL На фиг,4 этот такт работы показан после второго импульса 41. В этом случае сигнал 44 триггера 35 снимается и продолжается интегрирование только Ux, а затем по окончанию TI вновь устанавливается в единичное состояние триггер 35 импульсом 41, проходящим через элементы ИЛИ 39 и И 37.

В АЦП сохранен также режим запуска его в работу по импульсу 40 внешней синхронизации, по которому выполняемый такт измерения прерывается и начинается новое измерение за время TL начиная с этого момента времени (см. фиг.4 после третьего импульса 41).

По импульсу 40 устанавливаются нулевые коды в счетчике 13 и 28 и в триггере 12 (через элемент ИЛИ 15), устанавливаются исходные состояния в генераторе 27, на элемент 17 (с помощью ключа 24) и в интеграторе 7 (с помощью ключа 23 сигналом 40, прошедшим через элемент ИЛ И 33), последний устанавливает в единичное состояние триггер 29 и его сигнал 43 подключает с помощью ключа 22 напряжение Ux к интегратору 7. Так начинается новый такт измерения Ux за время TI по импульсу внешней синхронизации.

Таким образом в отличие от прототипа, в котором каждый такт измерения Ux кроме

времени интегрирования Ti может содержать дополнительное время Т22 для всех значений Ux кроме и , (для них необходимоусловие отсутствия помехи, положенной на их, и тем самым время преоб0 разования равно Tn Ti+T22, предлагаемый АЦП для каждого такта измерения Ux имеет время преобразования и между этими тактами измерения нет пропусков времени, присущих прототипу, когда не выполняется

5 интегрирование Ux, тем самым достигнуто повышение его быстродействия.

Предложенный АЦП совмещенного интегрирования решает поставленную перед ним задачу и устраняет недостаток прототи0 па, по сравнению с которым достигнуто повышение быстродействия.

Формула изобретения 1. Аналого-цифровой преобразователь совмещенного интегрирования, содержа5 щий интегратор, вход которого соединен с выходами первого и второго ключей, информационные входы которых являются соответственно шинами опорного и входного напряжений, выход интегратора подключен

0 к первым входам порогового элемента и компаратора, второй вход последнего из которых является общей шиной, счетчик, выходы которого являются выходной шиной, вход установки нуля - шиной синхрониза5 ции, блок управления и блок формирования времени интегрирования опорного напряжения, выход которого соединен с управляющим входом первого ключа и первым входом элемента И, второй вход которого

0 Соединен с первым выходом блока управления, а выход - со счетным входом счетчика, первый вход блока управления является шиной синхронизации, второй выход соединен с управляющим входом второго ключа, тре5 тий выход - с первым входом блока формирования времени интегрирования опорного напряжения, второй вход которого объединен с вторым входом блока управления и подключен к выходу компаратора, информа0 ционный вход и выход третьего ключа подключены соответственно к входу и выходу интегратора, а управляющий вход является шиной готовности результата преобразования и подключен к четвертому выходу блока

5 управления, пятый выход которого соединен с первым входом триггера, а первый вход объединен с первым входом элемента ИЛИ и трет оим входом блока формирования времени интегрирования опорного напряжения, четвертый вход которого объединен

с вторым входом элемента ИЛИ и подключен к выходу порогового элемента, второй вход которого соединен с выходами интегрирующего элемента и переключателя, первый и второй информационные входы которого подключены соответственно к входам делителя напряжения и источника тока, входы которых являются шиной опорного напряжения, а управляющий вход переключателя - подключен к единичному выходу триггера, второй вход которого соединен с выходом элемента ИЛИ, вход интегрирующего элемента является общей шиной, о т- личающийся тем, что, с целью повышения быстродействия, в него допол- нительно введены второй интегрирующий элемент, четвертый ключ, токоограничиваю- щий резистивный элемент и второй переключатель, управляющий вход которого объединен с одноименным входом второго ключа, первый и второй информационные входы - подсоединены соответственно к шине входного напряжения и входу интегратора, а выход через токоограничивающий резистивный элемент подключен к входу второго ин гегрирующего элемента и выходу четвертого ключа, соответственно выход и вход которых соединены с общей шиной, управляющий вход четвертого ключа объединен с первым входом блока управления, четвертый выход которого соединен с третьим входом элемента ИЛИ, а пятый выход - с входом установки исходного состояния счетчика.

2. Преобразователь по п. отличающийся тем, что блок управления выполнен на счетчике, генераторе импульсов, триггере, двух формирователях импульсов, элементах И и ИЛИ, причем первым входом блока является первый вход первого элемента ИЛИ и вход установки в исходное состояние счетчика и управляющий вход генератора импульсов, выход которого соединен со счетным входом счетчика и является первым выходом блока, выход переполнения счетчика подключен к нулевому входу триггера и является третьим выходом блока, а выходы старших разрядов счетчика подсоединены к соответствующим входам элемента И, выход которого соединен с входом, первого формирователя импульсов, выход которого является пятым выходом блока, четвертым выходом которого является выход первого элемента ИЛИ, который соединен с единичным входом триггера, выход которого является вторым выходом блока и соединен с первым входом второго элемента ИЛИ, второй вход которого является вторым входом блока, а выход через второй формирователь импульсов подсоединен к второму входу первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Интегрирующий аналого-цифровой преобразователь | 1984 |

|

SU1314457A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

Фиг. 1

Pur 2

46

7

Авторы

Даты

1992-12-30—Публикация

1991-02-06—Подача