Изобретение относится к импульсной технике, в частности к преобразователям напряжений в цифровой код с интегрированием входного и опорного напряжений. Изобретение может быть использовано в устройствах сбора аналоговой информации систем контроля и управления технологическими процессами на основе средств вычислительной техники.

Известны аналого-цифровые преобразователи АЦП совмещенного интегрирования [1] в которых преобразование выполняется в два такта. Сначала за Т1 интегрируется входное напряжение Uх, а затем за Т2 оно разынтегрируется опорным напряжением Uо противоположного знака до получения нулевого напряжения на выходе интегратора. Из уравнения преобразования kUxT1 kUoT2 0 величина Т2 Т1 и она соответствует Uх. Формирование Т1 и преобразование Т2 в код х выполняется с помощью частоты f генератора импульсов. Поэтому при T1

Т1 и она соответствует Uх. Формирование Т1 и преобразование Т2 в код х выполняется с помощью частоты f генератора импульсов. Поэтому при T1 и х Т2f величина х

и х Т2f величина х  Nо.

Nо.

В этих АЦП временные интервалы Т1 и Т2 частично совмещаются благодаря началу разынтегрирования до окончания Т1, это уменьшает промежутки времени между отдельными тактами измерения Т1 и повышает точность представления информации о величине преобразуемого напряжения.

Более высокие точностные характеристики, достигнутые за счет исключения упомянутых промежутков времени между отдельными Т1, имеет АЦП [2] принятый в качестве прототипа.

Этот АЦП совмещенного интегрирования содержит интегратор, вход которого соединен с выходами первого ключа и первого токоограничивающего резистивного элемента и объединен с информационным входом второго ключа, выход которого объединен с выходом интегратора и соединен с первыми входами порогового элемента и компаратора, второй вход которого подключен к выходу третьего ключа и является шиной нулевого потенциала, а через первый интегрирующий элемент объединен со вторым входом порогового элемента и подключен к выходу первого переключателя, первый и второй информационные входы которого соединены соответственно с выходами делителя напряжения и источника тока, входы котоpых объединены с информационным входом первого ключа и являются шиной опорного напряжения, а управляющий вход первого переключателя соединен с выходом триггера, нулевой вход которого соединен с выходом элемента ИЛИ, а единичный вход с первым выходом блока управления и объединен с входом установки нулевого кода счетчика, выходы которого являются выходной шиной результата преобразования, а вход установки исходного состояния объединен с первыми входами блока управления, блока формирования времени интегрирования опорного напряжения и элемента ИЛИ и является шиной синхронизации, счетный вход счетчика соединен с выходом элемента И, первый вход которого соединен соединен с вторым выходом блока управления, а второй вход объединен c входом управления первого ключа и соединен с выходом блока формирования времени интегрирования опорного напряжения, второй вход которого соединен с выходом порогового элемента и объединен с вторым входом элемента ИЛИ, третий вход соединен с третьим выходом блока управления, четвертый вход с выходом компаратора и объединен с вторым входом блока управления, четвертый выход которого соединен с управляющим входом второго переключателя, а пятый выход с входом управления второго ключа, с третьим входом элемента ИЛИ и является выходной шиной готовности результата преобразования, второй интегрирующий элемент включен между выходом и инфоpмационным входом третьего ключа, последний из которых объединен с входом первого токоограничивающего резистивного элемента, а управляющий вход третьего ключа соединен с первым входом бока управления, четвертый выход которого соединен с управляющим входом четвертого ключа, выход которого соединен с входом интегратора, а информационный вход объединен с вторым информационным входом второго переключателя и является шиной входного напряжения.

В АЦП-прототипе в течение времени Т22 окончания разынтегрирования, которое необходимо для получения результата преобразования после окончания Т1, выполняется интегрирование входного напряжения с помощью дополнительного интегрирующего элемента, а затем величина этого интервала передается в основной интегратор, осуществляющий интегрирование входного напряжения в следующем Т1 такте его измерения. Благодаря этому результаты преобразования соответствуют интегралам входного напряжения такты Т1 работы АЦП без каких-либо пропусков между ними.

Исключение этих временных пропусков и прерываний интегрирования входного напряжения между тактами работы АЦП совмещенного интегрирования обеспечивает повышенную точность его работы.

Однако имеет недостаток на точность результата преобразования известного АЦП оказывают влияние три составляющие погрешности. Во-первых, погрешность δ1 ключа, осуществляющего отключение входного напряжения от интегратора. Эта погрешность обусловлена динамическими ошибками переключения напряжения и остаточным сопротивлением замкнутого ключа.

Во-вторых, погрешность δ2 переключателя, осуществляющего подключение входного напряжения к дополнительному интегрирующему элементу. Эта погрешность аналогична δ1 ключа.

В-третьих, погрешность δ3 дополнительного интегрирующего элемента, который выполнен в видe RC-цепи и имеет выходное напряжение Uc U 1-e

1-e , где τ= RC.

, где τ= RC.

Накопленный в нем за время Т22 заряд Qсп U 1-e

1-e

будет отличаться от заряда, который был бы получен в основном интеграторе за это время: Qи=

будет отличаться от заряда, который был бы получен в основном интеграторе за это время: Qи=  Т22. Разность этих зарядов определяет величину погрешности Qδп:

Т22. Разность этих зарядов определяет величину погрешности Qδп:

Qδп= Qи-Qсп=  T22-

T22- 1-e

1-e

.

.

С учетом, что в прототипе τ= Т1, а величина Т22 составляет Кп часть от Т1, получим:

Qδп=  T

T Kп-1+e

Kп-1+e .

.

Заряд основного интегратора при интегрировании Uх за время Т1 будет равен Q1 Т1, относительно которого Qδп будет иметь погрешность δ3=

Т1, относительно которого Qδп будет иметь погрешность δ3=  = (Кп 1 + e-Kn). Эта погрешность входит в результат преобразования и совместно с погрешностями δ1 и δ2 снижает точность работы АЦП.

= (Кп 1 + e-Kn). Эта погрешность входит в результат преобразования и совместно с погрешностями δ1 и δ2 снижает точность работы АЦП.

Устранение или уменьшение этих погрешностей задача данного предложения, при осуществлении которого может быть получен технический результат, состоящий в повышении точности работы АЦП совмещенного интегрирования.

Этот технический эффект достигается тем, что в аналого-цифровой преобразователь совмещенного интегрирования, содержащий интегратор, вход которого соединен с выходами первого ключа и первого токоограничивающего резистивного элемента и объединен с информационным входом второго ключа, выход которого объединен с выходом интегратора и соединен с первыми входами порогового элемента и компаратора, второй вход которого подключен к выходу третьего ключа и является шиной нулевого потенциала, а через первый интегрирующий элемент объединен с вторым входом порогового элемента и подключен к выходу первого переключателя, первый и второй информационные входы которого соединены соответственно с выходами делителя напряжения и источника тока, входы которых объединены с информационным входом первого ключа и являются шиной опорного напряжения, а управляющий вход первого переключателя соединен с выходом триггера, нулевой вход которого соединен с выходом элемента ИЛИ, а единичный вход с первым выходом блока управления и объединен с входом установки нулевого кода счетчика, выходы которого являются выходной шиной результата преобразования, а вход установки исходного состояния объединен с первыми входами блока управления, блока формирования времени интегрирования опорного напряжения и элемента ИЛИ и является шиной синхронизации, счетный вход счетчика соединен с выходом элемента И, первый вход которого соединен с вторым выходом блока управления, а второй вход объединен с входом управления первого ключа и соединен с выходом блока формирования времени интегрирования опорного напряжения, второй вход которого соединен с выходом порогового элемента и объединен с вторым входом элемента ИЛИ, третий вход соединен с третьим выходом блока управления, четвертый вход с выходом компаратора и объединен с вторым входом блока управления, четвертый вход с выходом компаратора и объединен с вторым входом блока управления, четвертый выход которого соединен с управляющим входом второго переключателя, а пятый выход с входом управления второго ключа, с третьим входом элемента ИЛИ и является выходной шиной готовности результата преобразования, второй интегрирующий элемент, введены второй токоограничивающий pезистивный элемент и управляемый напряжением источник тока, вход которого является шиной входного напряжения и объединен с входом первого токоограничивающего резистивного элемента, а выход соединен с информационным входом третьего ключа и с первым информационным входом второго переключателя, второй информационный вход которого соединен через второй токоограничивающий резистивный элемент с шиной нулевого потенциала, выход через второй интегрирующий элемент с входом интегратора, а управляющий вход объединен с управляющим входом третьего ключа.

Блок формирования времени интегрирования опорного напряжения выполнен на триггере, формирователе импульсов, элементе И, первом и втором элементах ИЛИ, причем выход триггера является выходом блока, а единичный и нулевой входы соединены соответственно с выходами элемента И и первого элемента ИЛИ, первый вход которого является первым входом блока, а второй вход подключен к выходу формирователя импульсов, вход которого является четвертым входом бока и объединен с первым входом элемента И, второй вход которого подключен к выходу второго элемента ИЛИ, первый и второй входы которого являются соответственно вторым и третьим входами блока.

Блок управления выполнен на счетчике, генераторе импульсов, триггере, двух формирователях импульсов, элементах И и ИЛИ, причем первым входом блока является первый вход первого элемента ИЛИ и входы установки в исходное состояние счетчика и генератора импульсов, счетный вход первого из которых соединен с выходом второго и является вторым выходом блока, выход переполнения счетчика подключен к нулевому входу триггера и является третьим выходом блока, а выходы старших разрядов счетчика подсоединены соответствующим входам элемента И, выход которого соединен с входом первого формирователя импульсов, выход которого является первым выходом блока, пятым выходом которого является выход первого элемента ИЛИ, который объединен с единичным входом триггера, выход которого является четвертым выходом блока и соединен с первым входом второго элемента ИЛИ, второй вход которого является вторым входом блока, а выход через второй формирователь импульсов подсоединен к второму входу первого элемента ИЛИ.

При выборе и поиске аналогов и прототипа среди просмотренных технических решений не были обнаружены признаки, которые сходны с отличительными признаками заявляемого технического решения.

В предлагаемом техническом решении задача по устранению недостатка прототипа решается путем формирования тока Iу с помощью управляемого напряжения источника втекающего тока и подключения его на время Т22 к основному интегратору. Благодаря этому в течение Т22 ток Ix=

с помощью управляемого напряжения источника втекающего тока и подключения его на время Т22 к основному интегратору. Благодаря этому в течение Т22 ток Ix= , который получается в результате преобразования Uх с помощью входного резистора интегратора, компенсируется током Iy, что эквивалентно его отключению от интегратора, и ключ, выполняющий в прототипе эту функцию, не требуется. Ток Iy поступает на вход интегратора через интегрирующий элемент, в котором за время Т22накапливается заряд Qс Iy ˙T22

, который получается в результате преобразования Uх с помощью входного резистора интегратора, компенсируется током Iy, что эквивалентно его отключению от интегратора, и ключ, выполняющий в прототипе эту функцию, не требуется. Ток Iy поступает на вход интегратора через интегрирующий элемент, в котором за время Т22накапливается заряд Qс Iy ˙T22 T22.

T22.

Заряд Qс в отличие от прототипа не имеет составляющую погрешности Qδп и он затем передается в интегратор, дополняя общий заряд его конденсатора до величины Q1 Т1, в которой погрешность, присущая прототипу, отсутствует. Это обеспечивает повышение точности АЦП совмещенного интегрирования.

Т1, в которой погрешность, присущая прототипу, отсутствует. Это обеспечивает повышение точности АЦП совмещенного интегрирования.

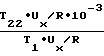

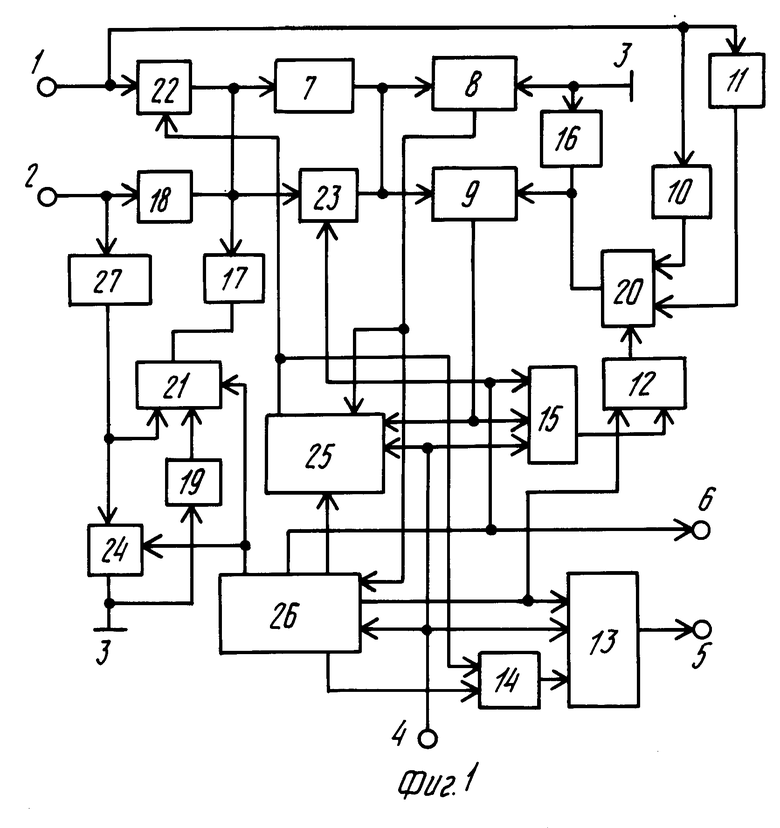

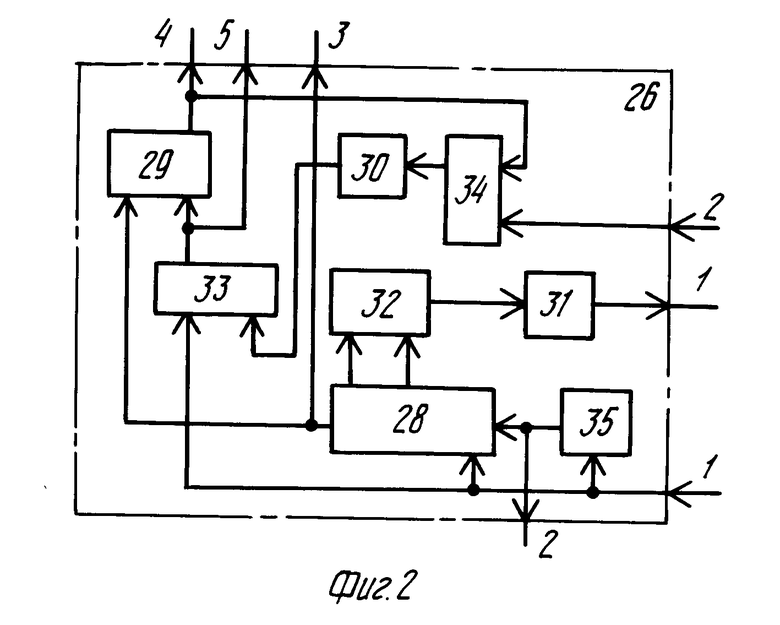

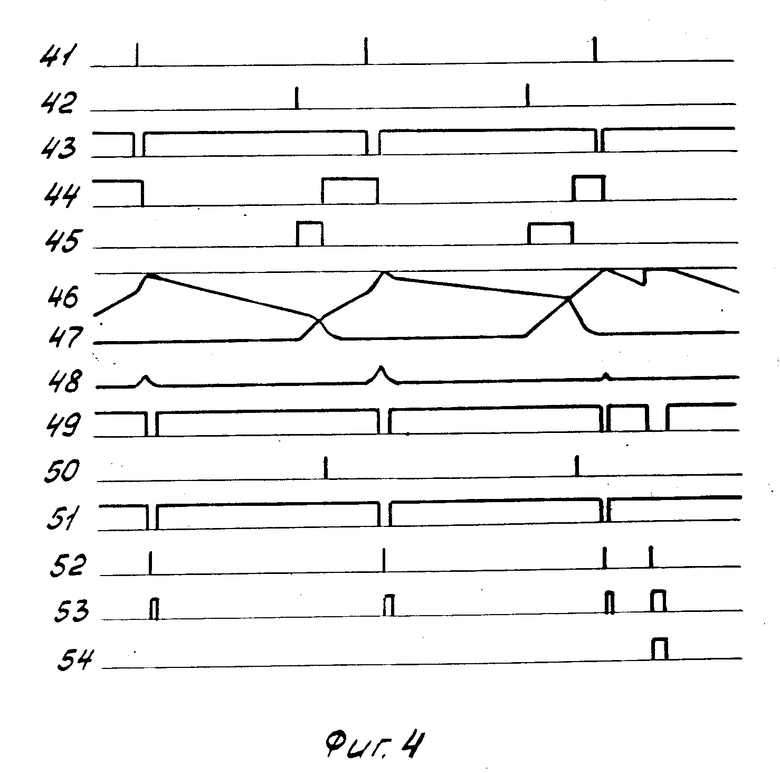

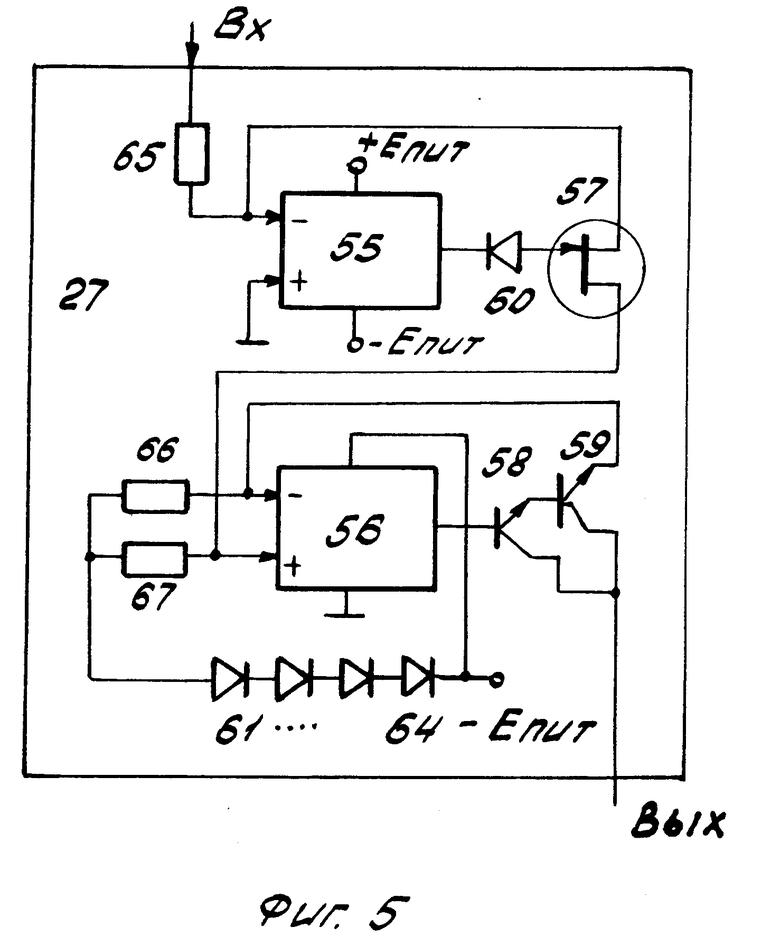

На фиг.1, 2 и 3 приведены блок-схемы АЦП, блока управления и блока формирования времени интегрирования опорного напряжения; на фиг.4 временная диаграмма их работы; на фиг.5 схема управляемого напряжением источника тока.

АЦП (фиг.1) содержит шины опорного 1 и входного 2 напряжений, общую шину 3, входную шину 4 синхронизации, выходные шины 5 результата преобразования и шину 6 его готовности, интегратор 7, например, выполненный на операционном усилителе с конденсатором в цепи обратной связи, компаратор 8 и пороговый элемент 9, источник тока 10 и делитель напряжения 11, триггер 12 и счетчик 13, элементы И 14 и ИЛИ 15, интегрирующие элементы 16 и 17, например, выполненные на конденсаторах, резистивные элементы 18 и 19, переключатели 20 и 21, у которых при отсутствии сигнала на управляющем входе замкнуты первый вход и выход, а при его наличии второй вход и выход; ключи 22, 23 и 24, первый из которых имеет резистор, каждый из них при наличии сигнала на управляющем входе замкнут, а при его отсутствии разомкнут; блок 25 формирования времени интегрирования опорного напряжения; блок 25 формирования времени интегрирования опорного напряжения; блок управления 26 и управляемый напряжением источник 27 втекающего тока.

Блок управления 26 (фи.2) содержит счетчик 28, триггер 29, формирователи импульсов 30 и 31, элементы И 32 и ИЛИ 33 и 34, генератор импульсов 35.

Блок 25 формирования времени интегрирования (фиг.3) содержит формирователь импульсов 36, элементы И 37 и ИЛИ 38 и 39, триггер 40.

На временной диаграмме фиг.4 обозначены: 41 и 42 импульсы переполнения счетчика 28 и формирователя 31; 43, 44 и 45 сигналы на выходах триггеров 29, 40 и 12; 46 и 47 сигналы на выходах интегратора 7 и интегрирующего элемента 16; 48 заряд в интегрирующем элементе 9 и элемента ИЛИ 34; 52 импульс формирователя 36; 53 импульсы готовности результата преобразования, 54 импульс синхронизации работы АЦП.

Источник 27 втекающего тока содержит операционные усилители 55,56, транзисторы 57, 58, 59, первый из них полевой транзистор; диоды 60-64; резисторы 65, 66, 67.

В АЦП шина 1 соединена с информационным входом ключа 22 и через делитель 11 и источник тока 10 соответственно с первым и вторым входами переключателя 20, шина 2 через первый токоограничивающий резистивный элемент 18 с входом интегратора 7, информационным входом ключа 23, с входом второго интегрирующего элемента 17 и с выходом ключа 22 и через источник тока 27 с информационным входом ключа 24 и с первым информационным входом переключателя 21, шина 3 с выходом ключа 24, с вторым входом компаратора 8, через элемент 19 с вторым информационным входом переключателя 21 и через элемент 16 с вторым входом порогового элемента 9 и с выходом переключателя 20, шина 4 с первыми входами блоков 25, 26 и элемента ИЛИ 15 и с входом установки исходного состояния счетчика 13, шина 5 с выходами счетчика 13, шина 6 с пятым выходом блока 26, с третьим входом элемента ИЛИ 15 и с управляющим входом ключа 23, выход которого соединен с выходом интегратора 7 и с первыми входами компаратора 8 и порогового элемента 9, выход компаратора 8 соединен с вторым входом блока 26 и с четвертым входом блока 25, а выход элемента 9 с вторыми входами элемента ИЛИ 15 и блока 25, третий вход которого соединен с третьим выходом блока 26, а выход с управляющим входом ключа 22 и с вторым входом элемента И 14, первый вход которого соединен с вторым выходом блока 26, а выход со счетным входом счетчика 13, вход установки нулевого кода которого соединен с первым выходом блока 26 и с единичным входом триггера 12, нулевой вход которого соединен с выходом элемента ИЛИ 15, а выход с управляющим входом переключателя 20, выход элемента 17 объединен с выходом переключателя 21, управляющий вход которого соединен с одноименным входом ключа 24 и с четвертым выходом блока 26.

Предлагаемый АЦП работает следующим образом. Как и в прототипе, интегрирование входного напряжения Uх выполняется в течение времени Т1, которое формируется с помощью счетчика 28 по импульсам частоты f генератора 35.

Емкость счетчика 28 равна q Nо, где q , Uo опорное напряжение, Um максимальное значение Ux, и импульсы 41 его переполнения возникают через I1 q

, Uo опорное напряжение, Um максимальное значение Ux, и импульсы 41 его переполнения возникают через I1 q . По этим импульсам выполняются такты измерения Uх. Напряжение Uх проходит через первый токоограничивающий резистивный элемент 18, преобразующий напряжение Uх в ток Iх

. По этим импульсам выполняются такты измерения Uх. Напряжение Uх проходит через первый токоограничивающий резистивный элемент 18, преобразующий напряжение Uх в ток Iх . Ток Iх интегрируется интегратором 7, который устанавливается в нулевое состояние с помощью ключа 23, шунтирующего его конденсатор, по сигналу 53 готовности результата преобразования прошедшего такта измерения Uх.

. Ток Iх интегрируется интегратором 7, который устанавливается в нулевое состояние с помощью ключа 23, шунтирующего его конденсатор, по сигналу 53 готовности результата преобразования прошедшего такта измерения Uх.

В текущем такте Т1 на выходе интегратора 7, у которого τ= RC, появляется напряжение 46, равное Uп(t) U , а на выходе компаратора 8 появится сигнал 49. На выходе элемента 16 и на втором входе порогового элемента 9 напряжение 47 будет равно Uс(t) Uд, где Uд напряжение делителя 11, выход которого подключен к элементу 16 с помощью переключателя 20 в течение времени Т01 до появления импульса 42 формирователя 31, срабатывающего при смене определенного кода в старших разрядах счетчика 28.

, а на выходе компаратора 8 появится сигнал 49. На выходе элемента 16 и на втором входе порогового элемента 9 напряжение 47 будет равно Uс(t) Uд, где Uд напряжение делителя 11, выход которого подключен к элементу 16 с помощью переключателя 20 в течение времени Т01 до появления импульса 42 формирователя 31, срабатывающего при смене определенного кода в старших разрядах счетчика 28.

Величина этого времени выбирается равной: Т01 (1  ) Т1, а величина напряжения

) Т1, а величина напряжения  U

U

1

1  Um=

Um=  1

1

.

.

Импульс 42 устанавливает в единичное состояние триггер 12, его сигнал 45 с помощью переключателя 20 подключает к интегрирующему элементу 16 источники тока 10, напряжение 47 на котором начинает изменяться по линейному закону со скоростью V: Uсп(t) -Uд(1-Vt). Величина V выбирается из условия, чтобы к окончанию Т1 Uсп(T1) 0, и она обеспечивается соответствующими величинами тока источниками 10 и емкости элемента 16.

Этому условию соответствует величина V:

V  q

q 1

1

1

1  .

.

При Ux Um через время Т01 на выходе интегратора 7 благодаря выбору соответствующего коэффициента интегрирования образуется напряжение Uп(Т01) Um (1  ), т.е. напряжение, равное Uд, и произойдет срабатывание порогового элемента 9. Для других значений Uхэто произойдет позже при Uп(t) Uсп(t), и в эти моменты времени будет формироваться сигнал 50.

), т.е. напряжение, равное Uд, и произойдет срабатывание порогового элемента 9. Для других значений Uхэто произойдет позже при Uп(t) Uсп(t), и в эти моменты времени будет формироваться сигнал 50.

Сигнал 50 установит через элемент ИЛИ 15 в нулевое состояние триггер 12 и через элементы ИЛИ 39 и И 37 в единичное состояние триггер 40. Снятие сигнала 45 в триггере 12 отключает источник тока 10 от элемента 16, на котором восстанавливается напряжение Uд. С появлением сигнала 44 на выходе триггера 40 к интегратору 7 с помощью ключа 22, имеющего резистор R, подключается опорное напряжение -Uо, которое преобразуется в ток -Iо . Так начинается совмещенное интегрирование суммарного тока

. Так начинается совмещенное интегрирование суммарного тока

(Ix-Io)  (Ux-Uo).

(Ux-Uo).

Одновременно с этим сигнал 44 разрешает работу элемента И 14, через который импульсы f генератора 35 поступают на счетный вход счетчика 13, где формируется новый код Х результата преобразования после установки его в исходное состояние импульсом 42.

Совмещенное интегрирование продолжается в течение времени Т21 до окончания Т1, когда по снятию сигнала 43 ключ 24 размыкается, а переключатель 21 подключает ток с выхода источника тока 27 через элемент 17 к входу интегратора 7. Источник тока 27 на выходе формирует втекающий ток величиной Iy .

.

Поэтому суммирование тока от Uх, протекающего через элемент 18 и равного Iх , с током Iу, равным по величине Iх, приводит к тому, что в интегратор 7 дополнительно к току Iо тока не поступает. С этого момента в последнем выполняется разынтегрирование оставшегося напряжения до нуля током Iо

, с током Iу, равным по величине Iх, приводит к тому, что в интегратор 7 дополнительно к току Iо тока не поступает. С этого момента в последнем выполняется разынтегрирование оставшегося напряжения до нуля током Iо за время Т22. В течение этого времени, как и в Т21, в счетчик 13 будут поступать импульсы f и в нем будет сформирован окончательный результат преобразования X Т2˙f, где T2 (T21 + T22) время, равное длительности сигнала 44. Это время Т2заканчивается по снятию сигнала 49 в компараторе 8, по которому формируется формирователем 36 импульс 52, который устанавливает через элемент ИЛИ 38 нулевое состояние в триггере 40.

за время Т22. В течение этого времени, как и в Т21, в счетчик 13 будут поступать импульсы f и в нем будет сформирован окончательный результат преобразования X Т2˙f, где T2 (T21 + T22) время, равное длительности сигнала 44. Это время Т2заканчивается по снятию сигнала 49 в компараторе 8, по которому формируется формирователем 36 импульс 52, который устанавливает через элемент ИЛИ 38 нулевое состояние в триггере 40.

После снятия в элементе ИЛИ 34 сигнала 49 или сигнала 43, если на выходе компаратора 8 к окончанию Т1 имеет место нулевой уровень сигнала 49, по сигналу 51 запускается формирователь 30. Длительность его импульса 53 превышает длительность импульса 52 и этот импульс информирует по шине 6 о готовности нового результата преобразования Х в счетчике 13 и на шине 5. Он же используется для установки в нулевое состояние интегратора 7 (с помощью ключа 23) и триггера 12 (через элемент ИЛИ 15).

Если в выполняемом такте измерения интегрирование Uх началось сразу с Т1, т.е. в предыдущем такте Т22 0, то заряд конденсатора в интеграторе 7 от Uх за время Т1 скомпенсирован зарядом от Uо за время Т2, откуда  T1-

T1-  T2= 0. Используя значения Т1 q

T2= 0. Используя значения Т1 q и Т2 x/f, получим x

и Т2 x/f, получим x  ·qNo=

·qNo=  ·No=

·No=  где Δ

где Δ  квант АЦП.

квант АЦП.

При наличии в предыдущем такте измерения времени Т22, которое уже относится к началу выполняемого нового такта измерения, ток -Iу от источника 27 заряжает элемент 17, в котором накопится заряд 48, равный Qc Iy ˙T22 T22. Этот заряд с появлением сигнала 43 в течение последующего времени передается в конденсатор интегратора 7, так как переключатель 21 отключает от элемента 17 ток Iх и подключает к нему резистор 19, соединенный с общей шиной. Во время действия сигнала 43 ключ 24 замкнут и ток Iх от источника 27 течет в общую шину, поддерживая выходное напряжение близким к нулю.

T22. Этот заряд с появлением сигнала 43 в течение последующего времени передается в конденсатор интегратора 7, так как переключатель 21 отключает от элемента 17 ток Iх и подключает к нему резистор 19, соединенный с общей шиной. Во время действия сигнала 43 ключ 24 замкнут и ток Iх от источника 27 течет в общую шину, поддерживая выходное напряжение близким к нулю.

Поэтому за время Т1 общий заряд конденсатора интегратора 7 будет соответствовать величине, получаемой при непрерывном интегрировании Uхв течение Т1 действительно, этот заряд будет равен:

Qc+  (T1-T22)

(T1-T22)  ·T22+

·T22+  (T1-T22)

(T1-T22)  ·T1

·T1

Благодаря этому независимо от наличия или отсутствия Т22 от предыдущего такта измерения Uх в текущем такте будет получен результат преобразования X  , который соответствует измерению входного напряжения за время Т1, и между отдельными тактами интегрирования нет потерь информации о Uх в течение времени Т22.

, который соответствует измерению входного напряжения за время Т1, и между отдельными тактами интегрирования нет потерь информации о Uх в течение времени Т22.

В предлагаемом АЦП имеется режим работы, обеспечивающий прерывание совмещенного интегрирования при срабатывании компаратора 8 до окончания Т1. В этом случае сигнал 44 снимается и продолжается интегрирование только Uх, а затем по окончании Т1 вновь устанавливается в единичное состояние триггер 40 импульсом 41, проходящим через элементы ИЛИ 39 и И 37.

В АЦП имеется также режим запуска его в работу по импульсу 54 внешней синхронизации, по которому выполняемый такт измерения прерывается и начинается новое измерение за время Т1, начиная с этого момента времени. По импульсу 54 устанавливаются нулевые коды в счетчиках 13 и 23 и в триггере 12 (через элемент ИЛИ 15), устанавливаются исходные состояния в генераторе 35 и интеграторе 7 с помощью ключа 23, устанавливается в единичное состояние триггер 29, а его сигнал 43 с помощью ключа 22 и переключателя 21 обеспечивает исходный режим работы источника 27 и цепи, состоящей из элементов 17 и 19. Так начинается новый такт измерения Uх за время Т1 по импульсу внешней синхронизации.

При реализации предлагаемого АЦП управляемый напряжением источник втекающего тока может быть выполнен, например, по схемам управляемых источников, приведенным на рис.1,26,а и б), в книге Шило В.Л. Функциональные аналоговые интегральные микросхемы. М. Радио и связь, 1982, стр.46. Вторая из этих схем имеет более высокую точность, погрешность ее работы не превышает 0,1%

Аналогичная ей схема, которую целесообразно использовать в предлагаемом АЦП, приведена на фиг. 5. В ней с помощью резистора 65 с величиной сопротивления R входное напряжение Uх преобразуется в ток Iх , который поступает на инвертирующий вход операционного усилителя 55 с выходным каскадом на полевом транзисторе 57, включенном в цель отрицательной обратной связи этого усилителя. На выходе транзистора 57 поддерживается ток Iх, независимо от величины напряжения, которое образуется от этого тока на сопротивлении нагрузки. В качестве последней используется резистор 67, включенный между неинвертирующим входом операционного усилителя 56 и напряжением питания, которое подается от -Епит и уменьшено на падение напряжения на четырех диодах 61 64. Между этим же питанием и инвертирующим входом усилителя 56 включен резистор 66, через который протекает ток выходного каскада на составном транзисторе 58 и 59, включенном в цепь отрицательной обратной связи. При равенстве величин сопротивлений резисторов 66 и 67 (например, их величина равна R) выходной ток будет поддерживаться равным Iу

, который поступает на инвертирующий вход операционного усилителя 55 с выходным каскадом на полевом транзисторе 57, включенном в цель отрицательной обратной связи этого усилителя. На выходе транзистора 57 поддерживается ток Iх, независимо от величины напряжения, которое образуется от этого тока на сопротивлении нагрузки. В качестве последней используется резистор 67, включенный между неинвертирующим входом операционного усилителя 56 и напряжением питания, которое подается от -Епит и уменьшено на падение напряжения на четырех диодах 61 64. Между этим же питанием и инвертирующим входом усилителя 56 включен резистор 66, через который протекает ток выходного каскада на составном транзисторе 58 и 59, включенном в цепь отрицательной обратной связи. При равенстве величин сопротивлений резисторов 66 и 67 (например, их величина равна R) выходной ток будет поддерживаться равным Iу , благодаря обеспечению усилителем 56 равенства напряжений на резисторах 66 и 67. Выходной каскад усилителя 56 на транзисторах 58 и 59 определяет характеристику источника тока, при этом его выходной ток является втекающим и допускает работу на нагрузку, подключенную к общей шине, что и требуется в схеме предлагаемого АЦП.

, благодаря обеспечению усилителем 56 равенства напряжений на резисторах 66 и 67. Выходной каскад усилителя 56 на транзисторах 58 и 59 определяет характеристику источника тока, при этом его выходной ток является втекающим и допускает работу на нагрузку, подключенную к общей шине, что и требуется в схеме предлагаемого АЦП.

При наличии в управляемом напряжением источнике втекающего тока погрешности преобразования Uх в ток Iу, равной 0,1% в заряде Qс будет возникать погрешность Qδ=  Т22˙10-3, которая приведет к погрешности относительно заряда Q1 интегратора δ

Т22˙10-3, которая приведет к погрешности относительно заряда Q1 интегратора δ

Kп˙10-3. В прототипе эта погрешность была равна δ3=(Kn-1+e-Kn), поэтому она уменьшена в αраз, где α

Kп˙10-3. В прототипе эта погрешность была равна δ3=(Kn-1+e-Kn), поэтому она уменьшена в αраз, где α

· 10-3.

· 10-3.

Наибольшие величины Т22 возникают из-за наличия помехи, наложенной на входной сигнал Uх, и они могут составлять 5-10 от Т1, т.е. Kп 0,05 0,1. Для этих значений Кп величина α будет равна α 12-48 или погрешность δ3 прототипа для этого диапазона изменения Кп уменьшается от 12 до 48 раз.

Погрешность δ1 прототипа полностью исключена, так как отключение напряжения Uх от интегратора не выполняется.

Погрешность δ2 переключателя напряжения Uх в цепи формирования заряда Qс прототипа значительно уменьшена, так как в предлагаемом АЦП этот переключатель работает в режиме переключения токов, что позволяет снизить его динамические ошибки и исключить ошибки от остаточных сопротивлений между замкнутыми входами и выходом.

Таким образом, благодаря как исключению, так и существенному уменьшению погрешностей прототипа, в заявляемом АЦП совмещенного интегрирования решается поставленная задача: устраняется недостаток прототипа и повышается точность работы АЦП.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012132C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2037267C1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| СПОСОБ УПРАВЛЕНИЯ M-ФАЗНЫМ ЭЛЕКТРОДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА С 2M-ТИРИСТОРНЫМ КОММУТАТОРОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2092965C1 |

Изобретение относится к импульсной технике, в частности к преобразователям напряжения в цифровой код с интегрированием входного и опорного напряжений, и может быть использовано в устройствах сбора аналоговой информации систем контроля и управления различных процессов. В изобретении решается задача повышения точности преобразователя за счет исключения погрешностей. АЦП содержит интегратор, три ключа, компаратор, пороговый элемент, делитель напряжения, источник тока, два интегрирующих элемента, токоограничивающий резистивный элемент, два переключателя, счетчик, триггер, элементы И и ИЛИ, блок формирования времени интегрирования опорного напряжения и блок управления. Новым является введение управляемого напряжением источника тока и второго токоограничивающего резистивного элемента, а также изменение взаимосвязей между другими элементами, благодаря которым дополнительные погрешности в результате преобразования уменьшены или вообще исключены и тем самым достигнут технический эффект по повышению точности работы АЦП совмещенного интегрирования. 5 ил.

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ, содержащий интегратор, вход которого соединен с выходами первого ключа и первого токоограничивающего резистивного элемента и объединен с информационным входом второго ключа, выход которого объединен с выходом интегратора и соединен с первыми входами порогового элемента и компаратора, второй вход которого подключен к выходу третьего ключа и является шиной нулевого потенциала, а через первый интегрирующий элемент объединен с вторым входом порогового элемента и подключен к выходу первого переключателя, первый и второй информационные входы которого соединены соответственно с выходами делителя напряжения и источника тока, входы которых объединены с информационным входом первого ключа и являются шиной опорного напряжения, управляющий вход первого переключателя соединен с выходом триггера, нулевой вход которого соединен с выходом элемента ИЛИ, а единичный вход с первым выходом блока управления и объединен с входом установки нулевого кода счетчика, выходы которого являются выходной шиной результата преобразования, а вход установки исходного состояния объединен с первыми входами блока управления, блока формирования времени интегрирования опорного напряжения и элемента ИЛИ и является шиной синхронизации, счетный вход счетчика соединен с выходом элемента И, первый вход которого соединен с вторым выходом блока управления, а второй вход объединен с входом управления первого ключа и соединен с выходом блока формирования времени интегрирования опорного напряжения, второй вход которого соединен с выходом порогового элемента и объединен с вторым входом элемента ИЛИ, третий вход соединен с третьим выходом блока управления, четвертый вход - с выходом компаратора и объединен с вторым входом блока управления, четвертый выход которого соединен с управляющим входом второго переключателя, а пятый выход с входом управления второго ключа, с третьим входом элемента ИЛИ и является выходной шиной готовности результата преобразования, второй интегрирующий элемент, отличающийся тем, что в него введены второй токоограничивающий резистивный элемент и управляемый напряжением источник тока, вход которого является шиной входного напряжения и объединен с входом первого токоограничивающего резистивного элемента, а выход соединен с информационным входом третьего ключа и с первым информационным входом второго переключателя, второй информационный вход которого соединен через второй токоограничивающий резистивный элемент с шиной нулевого потенциала, выход - через второй интегрирующий элемент с входом интегратора, а управляющий вход объединен с управляющим входом третьего ключа.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-05-27—Публикация

1992-04-17—Подача